Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | A/D 10x12b                                                                |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc774t-i-l |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16C77X

#### 2.2.2.7 PIR2 REGISTER

Γ

This register contains the CCP2, SSP Bus Collision, and Low-voltage detect interrupt flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# FIGURE 2-9: PIR2 REGISTER (ADDRESS 0Dh)

| R/W-0    | U-0                                               | U-0         | U-0                     | R/W-0                    | U-0         | U-0         | R/W-0                     |                                                                                       |

|----------|---------------------------------------------------|-------------|-------------------------|--------------------------|-------------|-------------|---------------------------|---------------------------------------------------------------------------------------|

| LVDIF    | _                                                 | _           | _                       | BCLIF                    | _           | _           | CCP2IF                    | R = Readable bit                                                                      |

| bit7     |                                                   |             |                         |                          |             |             | bitO                      | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7:   | 1 = The s                                         | upply volta | age has fa              |                          |             |             |                           | be cleared in software)                                                               |

| bit 6-4: | Unimpler                                          | nented: R   | ead as '0               |                          |             |             |                           |                                                                                       |

| bit 3:   | BCLIF: Bu<br>1 = A bus<br>(must be o<br>0 = No bu | collision h | ias occurr<br>software) |                          | ne SSP mo   | dule confi  | gured in I <sup>2</sup> C | Master was transmitting                                                               |

| bit 2-1: | Unimpler                                          | nented: R   | ead as '0               |                          |             |             |                           |                                                                                       |

| bit 0:   | CCP2IF: (                                         | CCP2 Inte   | rrupt Flag              | bit                      |             |             |                           |                                                                                       |

|          | <u>Capture M</u><br>1 = A TMF<br>0 = No TM        | R1 registe  |                         |                          | nust be cle | eared in sc | oftware)                  |                                                                                       |

|          |                                                   | R1 registe  |                         | e match oc<br>re match o | · ·         | st be clea  | red in softw              | are)                                                                                  |

|          | <u>PWM Moo</u><br>Unused                          | <u>de</u>   |                         |                          |             |             |                           |                                                                                       |

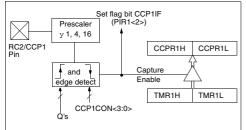

#### 7.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as:

- · every falling edge

- · every rising edge

- · every 4th rising edge

- every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 7.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 is configured as an out-     |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

# FIGURE 7-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 7.1.2 TIMER1 MODE SELECTION

Timer1 must be running in timer mode or synchronized counter mode for the CCP module to use the capture feature. In asynchronous counter mode, the capture operation may not work.

#### 7.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in operating mode.

#### 7.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in capture mode, the prescaler counter is cleared. This means that any reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 7-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

### EXAMPLE 7-1: CHANGING BETWEEN CAPTURE PRESCALERS

CLRF CCP1CON ;Turn CCP module off MOVLW NEW\_CAPT\_PS ;Load the W reg with ; the new prescaler ; mode value and CCP ON MOVWF CCP1CON ;Load CCP1CON with this : value

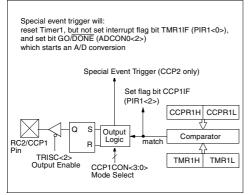

#### 7.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- driven High

- driven Low

- · remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

# FIGURE 7-3: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 7.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force       |

|-------|------------------------------------------------|

|       | the RC2/CCP1 compare output latch to the       |

|       | default low level. This is not the data latch. |

#### 7.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 7.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 7.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special trigger output of CCP2 resets the TMR1 register pair, and starts an A/D conversion (if the A/D module is enabled).

Note: The special event trigger from the CCP2 module will not set interrupt flag bit TMR1IF (PIR1<0>).

# TABLE 7-3 REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address               | Name    | Bit 7                | Bit 6     | Bit 5        | Bit 4       | Bit 3         | Bit 2      | Bit 1       | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|-----------------------|---------|----------------------|-----------|--------------|-------------|---------------|------------|-------------|--------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE      | TOIE         | INTE        | RBIE          | TOIF       | INTF        | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup> | ADIF      | RCIF         | TXIF        | SSPIF         | CCP1IF     | TMR2IF      | TMR1IF | 0000 0000                | 0000 0000                       |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup> | ADIE      | RCIE         | TXIE        | SSPIE         | CCP1IE     | TMR2IE      | TMR1IE | 0000 0000                | 0000 0000                       |

| 87h                   | TRISC   | PORTC Da             | ata Dire  | ction Regis  | ster        |               |            |             |        | 1111 1111                | 1111 1111                       |

| 0Eh                   | TMR1L   | Holding reg          | gister fo | or the Least | Significant | Byte of the   | 16-bit TMF | R1 register |        | xxxx xxxx u              | uuu uuuu                        |

| 0Fh                   | TMR1H   | Holding reg          | gister fo | or the Most  | Significant | Byte of the 1 | 16-bit TMR | 1 register  |        | xxxx xxxx u              | uuu uuuu                        |

| 10h                   | T1CON   | _                    | _         | T1CKPS1      | T1CKPS0     | T1OSCEN       | T1SYNC     | TMR1CS      | TMR1ON | 00 0000                  | uu uuuu                         |

| 15h                   | CCPR1L  | Capture/Co           | ompare    | /PWM regi    | ster1 (LSB) |               |            |             |        | xxxx xxxx u              | uuu uuuu                        |

| 16h                   | CCPR1H  | Capture/Co           | ompare    | /PWM regi    | ster1 (MSB) | )             |            |             |        | xxxx xxxx u              | uuu uuuu                        |

| 17h                   | CCP1CON | —                    | —         | CCP1X        | CCP1Y       | CCP1M3        | CCP1M2     | CCP1M1      | CCP1M0 | 00 0000                  | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin, always maintain these bits clear.

#### FIGURE 8-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

| R/W-0    | R/W-0                     | R/W-0                            | R/W-0       | R/W-0        | R/W-0            | R/W-0          | R/W-0                     |                                              |  |  |

|----------|---------------------------|----------------------------------|-------------|--------------|------------------|----------------|---------------------------|----------------------------------------------|--|--|

| WCOL     | SSPOV                     | SSPEN                            | CKP         | SSPM3        | SSPM2            | SSPM1          | SSPM0                     | R = Readable bit                             |  |  |

| bit7     |                           |                                  |             |              |                  |                | bit0                      | W = Writable bit<br>- n = Value at POR reset |  |  |

| b.it 7.  | WCOL                      | VCOL: Write Collision Detect bit |             |              |                  |                |                           |                                              |  |  |

| bit 7:   | Master Mo                 |                                  | on Detect   | DIT          |                  |                |                           |                                              |  |  |

|          |                           |                                  | PBUF reg    | jister was a | attempted        | while the l    | I <sup>2</sup> C conditio | ns were not valid for a                      |  |  |

|          |                           | ion to be st                     | arted       |              |                  |                |                           |                                              |  |  |

|          | 0 = No col                |                                  |             |              |                  |                |                           |                                              |  |  |

|          | Slave Mod<br>1 = The S    |                                  | uister is w | ritten while | e it is still tr | ansmitting     | g the previou             | us word                                      |  |  |

|          |                           | cleared in s                     |             |              |                  |                | ,                         |                                              |  |  |

|          | 0 = No col                | llision                          |             |              |                  |                |                           |                                              |  |  |

| bit 6:   |                           | Receive Ove                      | erflow Ind  | icator bit   |                  |                |                           |                                              |  |  |

|          | In SPI mo                 |                                  | while       |              | RIF rogiet       | or ic ctill bo | lding the pr              | evious data. In case of overflow,            |  |  |

|          |                           | -                                |             |              | -                |                |                           | e mode, the user must read the               |  |  |

|          |                           |                                  |             |              |                  |                |                           | ter mode, the overflow bit is not            |  |  |

|          |                           |                                  | eception (  | and transr   | nission) is      | initiated b    | y writing to              | the SSPBUF register. (Must be                |  |  |

|          | cleared in $0 = No over$  | software).                       |             |              |                  |                |                           |                                              |  |  |

|          | $\ln l^2 C \mod l^2$      |                                  |             |              |                  |                |                           |                                              |  |  |

|          |                           |                                  |             |              |                  | still holding  | g the previou             | us byte. SSPOV is a "don't care"             |  |  |

|          | in transmit $0 = No over$ | t mode. (M                       | ust be cle  | ared in sol  | tware).          |                |                           |                                              |  |  |

|          |                           |                                  |             |              | L. 11            |                |                           |                                              |  |  |

| bit 5:   |                           | Synchronou<br>odes when          |             |              |                  | oroperly c     | onfigured as              | s input or output.                           |  |  |

|          | In SPI mo                 |                                  | ,           |              |                  |                | <u>-</u>                  |                                              |  |  |

|          |                           | •                                |             | •            |                  |                |                           | ource of the serial port pins                |  |  |

|          | 0 = DisabiIn I2C mod      | les serial po<br>de              | ort and co  | onfigures tr | iese pins a      | as I/O port    | pins                      |                                              |  |  |

|          |                           |                                  | al port and | d configure  | s the SDA        | and SCL        | pins as the               | source of the serial port pins               |  |  |

|          | 0 = Disabl                | es serial po                     | ort and co  | onfigures th | nese pins a      | as I/O port    | pins                      |                                              |  |  |

| bit 4:   |                           | ck Polarity S                    | Select bit  |              |                  |                |                           |                                              |  |  |

|          | In SPI mo                 |                                  | k io o hiał |              |                  |                |                           |                                              |  |  |

|          |                           | ate for cloc<br>ate for cloc     | •           |              |                  |                |                           |                                              |  |  |

|          | In I <sup>2</sup> C slav  |                                  |             |              |                  |                |                           |                                              |  |  |

|          |                           | ise control                      |             |              |                  |                |                           |                                              |  |  |

|          | 1 = Enable<br>0 = Holds   | e clock<br>clock low (           | clock stre  | tch) (Used   | to ensure        | data setu      | n time)                   |                                              |  |  |

|          | In I <sup>2</sup> C mas   |                                  |             | , (          |                  |                | p                         |                                              |  |  |

|          |                           | this mode                        |             |              |                  |                |                           |                                              |  |  |

| bit 3-0: |                           | SPM0: Syr                        |             |              |                  | elect bits     |                           |                                              |  |  |

|          |                           | PI master n<br>PI master n       | ,           |              |                  |                |                           |                                              |  |  |

|          |                           | PI master n                      |             |              |                  |                |                           |                                              |  |  |

|          |                           | PI master n                      |             |              |                  |                |                           |                                              |  |  |

|          |                           | PI slave mo                      |             |              |                  |                |                           | an be used as I/O pin                        |  |  |

|          |                           | C slave mo                       |             |              | . 00 pin 0       |                |                           |                                              |  |  |

|          | $0111 = I^2$              | C slave mo                       | de, 10-bit  | address      |                  |                |                           |                                              |  |  |

|          |                           | C master r                       | node, clo   | ck = Fosc    | / (4 * (SSF      | ADD+1))        |                           |                                              |  |  |

|          | 1xx1 = Re<br>1x1x = Re    |                                  |             |              |                  |                |                           |                                              |  |  |

|          |                           |                                  |             |              |                  |                |                           |                                              |  |  |

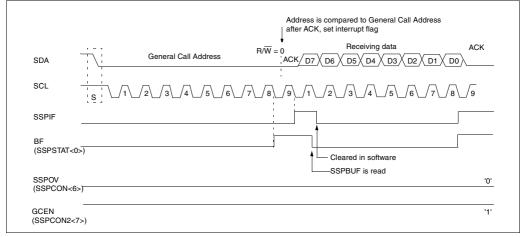

#### 8.2.2 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the START condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all 0's with R/W = 0

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> is set). Following a start-bit detect, 8-bits are shifted into SSPSR and the address is compared against SSPADD, and is also compared to the general call address, fixed in hardware. If the general call address matches, the SSPSR is transfered to the SSPBUF, the BF flag is set (eighth bit), and on the falling edge of the ninth bit ( $\overline{ACK}$  bit) the SSPIF flag is set.

When the interrupt is serviced. The source for the interrupt can be checked by reading the contents of the SSPBUF to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match, and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when GCEN is set while the slave is configured in 10-bit address mode, then the second half of the address is not necessary, the UA bit will not be set, and the slave will begin receiving data after the acknowledge (Figure 8-16).

FIGURE 8-16: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE (7 OR 10-BIT MODE)

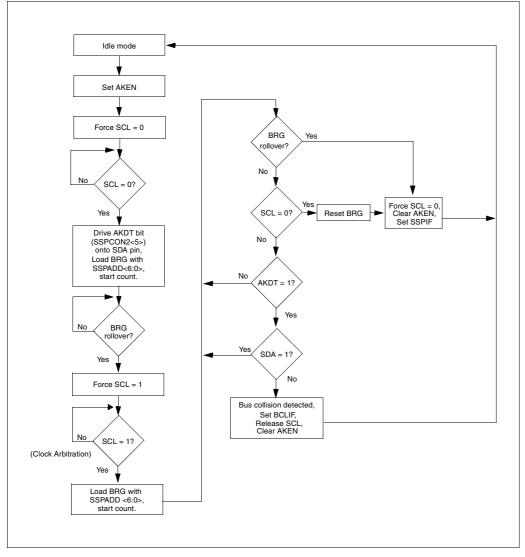

# FIGURE 8-30: ACKNOWLEDGE FLOWCHART

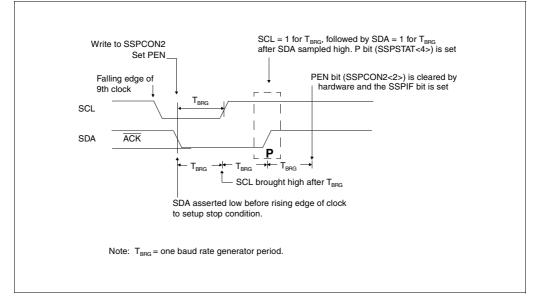

#### 8.2.14 STOP CONDITION TIMING

A stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit PEN (SSPCON2<2>). At the end of a receive/transmit the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low . When the SDA line is sampled low, the baud rate generator is reloaded and counts down to 0. When the baud rate generator times out, the SCL pin will be brought high, and one T<sub>BRG</sub> (baud rate generator rollover count) later, the SDA pin is sampled high

while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later the PEN bit is cleared and the SSPIF bit is set (Figure 8-31).

Whenever the firmware decides to take control of the bus, it will first determine if the bus is busy by checking the S and P bits in the SSPSTAT register. If the bus is busy, then the CPU can be interrupted (notified) when a Stop bit is detected (i.e. bus is free).

#### 8.2.14.14 WCOL STATUS FLAG

If the user writes the SSPBUF when a STOP sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 8-31: STOP CONDITION RECEIVE OR TRANSMIT MODE

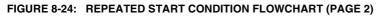

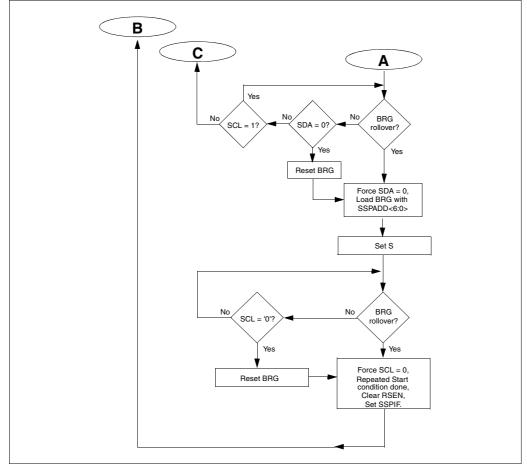

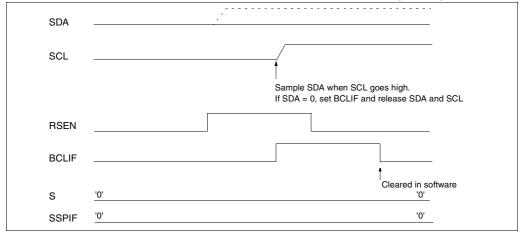

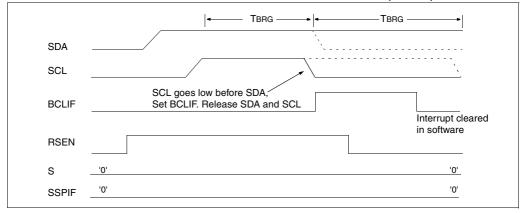

# 8.2.18.16 BUS COLLISION DURING A REPEATED START CONDITION

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user de-asserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0>, and counts down to 0. The SCL pin is then deasserted, and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e. another master is attempting to transmit a data '0'). If however SDA is sampled high then the BRG is reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs, because no two masters can assert SDA at exactly the same time.

If, however, SCL goes from high to low before the BRG times out and SDA has not already been asserted, then a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition.

If at the end of the BRG time out both SCL and SDA are still high, the SDA pin is driven low, the BRG is reloaded, and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete (Figure 8-38).

FIGURE 8-38: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### FIGURE 8-39: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

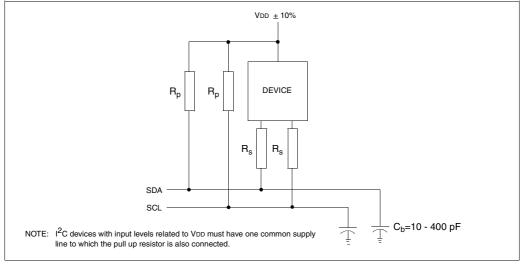

#### 8.3 <u>Connection Considerations for I<sup>2</sup>C</u> Bus

For standard-mode  $I^2C$  bus devices, the values of resistors  $\mathbf{R_p} \mathbf{R_s}$  in Figure 8-42 depends on the following parameters

- Supply voltage

- Bus capacitance

- Number of connected devices (input current + leakage current).

The supply voltage limits the minimum value of resistor  $R_p$  due to the specified minimum sink current of 3 mA at VoL max = 0.4V for the specified output stages. For

example, with a supply voltage of VDD =  $5V\pm10\%$  and VoL max = 0.4V at 3 mA, R<sub>p min</sub> = (5.5-0.4)/0.003 = 1.7 k: VDD as a function of **R**<sub>p</sub> is shown in Figure 8-42. The desired noise margin of 0.1VDD for the low level limits the maximum value of **R**<sub>s</sub>. Series resistors are optional and used to improve ESD susceptibility.

The bus capacitance is the total capacitance of wire, connections, and pins. This capacitance limits the maximum value of  $R_p$  due to the specified rise time (Figure 8-42).

The SMP bit is the slew rate control enabled bit. This bit is in the SSPSTAT register, and controls the slew rate of the I/O pins when in  $I^2C$  mode (master or slave).

# FIGURE 8-42: SAMPLE DEVICE CONFIGURATION FOR I<sup>2</sup>C BUS

| 1) |

|----|

| 1  |

| BAUD<br>RATE<br>(K)                                        | Fosc = 2<br>KBAUD                                     | 0 MHz<br>%<br>ERROR                                 | SPBRG<br>value<br>(decimal)                            | 16 MHz<br>KBAUD                                        | %<br>ERROF                       | SPBRG<br>value<br>decimal                               |                                                                    | %                                                       | b Va                                          | PBRG<br>alue<br>cimal)                           | 7.16 MHz<br>KBAUD E                                                                       | %                                             | SPBRG<br>value<br>decimal)                  |                                               |                                                  |

|------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|----------------------------------|---------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------|-----------------------------------------------|--------------------------------------------------|

| 9.6                                                        | 9.615                                                 | +0.16                                               | 129                                                    | 9.615                                                  | +0.16                            | 103                                                     | 9.615                                                              | 5 +0.                                                   | 16                                            | 64                                               | 9.520                                                                                     | -0.83                                         | 46                                          |                                               |                                                  |

| 19.2                                                       | 19.230                                                | +0.16                                               | 64                                                     | 19.230                                                 | +0.16                            | 51                                                      | 18.93                                                              | 9 -1.3                                                  | 36                                            | 32                                               | 19.454                                                                                    | +1.32                                         | 22                                          |                                               |                                                  |

| 38.4                                                       | 37.878                                                | -1.36                                               | 32                                                     | 38.461                                                 | +0.16                            | 25                                                      | 39.06                                                              | 2 +1                                                    | .7                                            | 15                                               | 37.286                                                                                    | -2.90                                         | 11                                          |                                               |                                                  |

| 57.6                                                       | 56.818                                                | -1.36                                               | 21                                                     | 58.823                                                 | +2.12                            | 16                                                      | 56.81                                                              | 8 -1.3                                                  | 36                                            | 10                                               | 55.930                                                                                    | -2.90                                         | 7                                           |                                               |                                                  |

| 115.2                                                      | 113.636                                               | -1.36                                               | 10                                                     | 111.111                                                | -3.55                            | 8                                                       | 125                                                                | +8.                                                     | 51                                            | 4                                                | 111.860                                                                                   | -2.90                                         | 3                                           |                                               |                                                  |

| 250                                                        | 250                                                   | 0                                                   | 4                                                      | 250                                                    | 0                                | 3                                                       | NA                                                                 | -                                                       |                                               | -                                                | NA                                                                                        | -                                             | -                                           |                                               |                                                  |

| 625                                                        | 625                                                   | 0                                                   | 1                                                      | NA                                                     | -                                | -                                                       | 625                                                                | 0                                                       |                                               | 0                                                | NA                                                                                        | -                                             | -                                           |                                               |                                                  |

| 1250                                                       | 1250                                                  | 0                                                   | 0                                                      | NA                                                     | -                                | -                                                       | NA                                                                 | -                                                       |                                               | -                                                | NA                                                                                        | -                                             | -                                           |                                               |                                                  |

| DALID                                                      | Fosc = 5                                              | 000 1411-                                           |                                                        |                                                        |                                  |                                                         |                                                                    |                                                         |                                               |                                                  |                                                                                           |                                               |                                             |                                               |                                                  |

| BAUD<br>RATE                                               |                                                       | %                                                   | SPBRG<br>value                                         | 4 MHz                                                  | %                                | SPBRG<br>value                                          | 8.579 MH                                                           | %                                                       | SPBRG<br>value                                |                                                  | %                                                                                         | SPBRG<br>value                                |                                             | %                                             | SPBRG<br>value                                   |

|                                                            | KBAUD                                                 | %                                                   | SPBRG<br>value                                         |                                                        |                                  | SPBRG                                                   |                                                                    | %                                                       | value                                         |                                                  | %                                                                                         |                                               |                                             |                                               | value                                            |

| RATE                                                       |                                                       | %                                                   | SPBRG<br>value                                         |                                                        |                                  | SPBRG<br>value<br>(decimal) ł                           |                                                                    | %                                                       | value                                         |                                                  | %<br>UD ERROF                                                                             | value                                         |                                             | %                                             | value                                            |

| RATE<br>(K)                                                | KBAUD                                                 | %<br>ERROR                                          | SPBRG<br>value<br>(decimal)                            | KBAUD                                                  |                                  | SPBRG<br>value<br>(decimal) ł                           | KBAUD                                                              | %<br>ERROR                                              | value<br>(decimal                             | ) KBA                                            | %<br>UD ERROF<br>28 -6.99                                                                 | value<br>(decimal)                            | ) KBAUD                                     | %                                             | value                                            |

| RATE<br>(K)<br>9.6                                         | KBAUD<br>9.6                                          | %<br>ERROR<br>0                                     | SPBRG<br>value<br>(decimal)<br>32                      | KBAUD<br>NA                                            | ERROR<br>-                       | SPBRG<br>value<br>(decimal) H                           | KBAUD<br>9.727                                                     | %<br>ERROR<br>+1.32                                     | value<br>(decimal<br>22                       | ) KBA                                            | %<br>UD ERROF<br>28 -6.99<br>33 +8.51                                                     | value<br>(decimal)<br>6                       | ) KBAUD                                     | %                                             | value                                            |

| RATE<br>(K)<br>9.6<br>19.2                                 | KBAUD<br>9.6<br>18.645                                | %<br>ERROR<br>0<br>-2.94                            | SPBRG<br>value<br>(decimal)<br>32<br>16                | KBAUD<br>NA<br>1.202                                   | ERROR<br>-<br>+0.17              | SPBRG<br>value<br>(decimal) F<br>-<br>207<br>103        | KBAUD<br>9.727<br>18.643                                           | %<br>ERROR<br>+1.32<br>-2.90                            | value<br>(decimal<br>22<br>11                 | ) KBA<br>8.92<br>20.8                            | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61                                        | value<br>(decimal)<br>6<br>2                  | ) KBAUD<br>NA<br>NA                         | ERROR<br>-<br>-                               | value<br>(decimal)<br>-<br>-                     |

| RATE<br>(K)<br>9.6<br>19.2<br>38.4<br>57.6<br>115.2        | KBAUD<br>9.6<br>18.645<br>39.6<br>52.8<br>105.6       | %<br>ERROR<br>0<br>-2.94<br>+3.12                   | SPBRG<br>value<br>(decimal)<br>32<br>16<br>7           | KBAUD<br>NA<br>1.202<br>2.403<br>9.615<br>19.231       | -<br>+0.17<br>+0.13              | SPBRG<br>value<br>(decimal) H<br>207<br>103<br>25<br>12 | KBAUD<br>9.727<br>18.643<br>37.286<br>55.930<br>111.860            | %<br>ERROR<br>+1.32<br>-2.90<br>-2.90<br>-2.90<br>-2.90 | value<br>(decimal<br>22<br>11<br>5            | ) KBA<br>8.92<br>20.8<br>31.2<br>62.<br>NA       | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61<br>5 +8.51<br>A -                      | value<br>(decimal)<br>6<br>2<br>1             | ) KBAUD<br>NA<br>NA<br>NA<br>NA<br>NA       | * ERROR<br>-<br>-<br>-                        | value<br>(decimal)<br>-<br>-                     |

| RATE<br>(K)<br>9.6<br>19.2<br>38.4<br>57.6<br>115.2<br>250 | KBAUD<br>9.6<br>18.645<br>39.6<br>52.8<br>105.6<br>NA | %<br>ERROR<br>0<br>-2.94<br>+3.12<br>-8.33          | SPBRG<br>value<br>(decimal)<br>32<br>16<br>7<br>5      | KBAUD<br>NA<br>1.202<br>2.403<br>9.615<br>19.231<br>NA | +0.17<br>+0.13<br>+0.16          | SPBRG<br>value<br>(decimal) H<br>207<br>103<br>25<br>12 | KBAUD<br>9.727<br>18.643<br>37.286<br>55.930<br>111.860<br>223.721 | %<br>ERROR<br>+1.32<br>-2.90<br>-2.90<br>-2.90          | value<br>(decimal<br>22<br>11<br>5<br>3       | ) KBA<br>8.92<br>20.8<br>31.2<br>62.<br>NA<br>NA | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61<br>5 +8.51<br>A -<br>A -               | value<br>(decimal)<br>6<br>2<br>1<br>0        | ) KBAUD<br>NA<br>NA<br>NA<br>NA<br>NA<br>NA | * ERROR<br>-<br>-<br>-<br>-                   | value<br>(decimal)<br>-<br>-<br>-<br>-           |

| RATE<br>(K)<br>9.6<br>19.2<br>38.4<br>57.6<br>115.2        | KBAUD<br>9.6<br>18.645<br>39.6<br>52.8<br>105.6       | %<br>ERROR<br>0<br>-2.94<br>+3.12<br>-8.33<br>-8.33 | SPBRG<br>value<br>(decimal)<br>32<br>16<br>7<br>5<br>2 | KBAUD<br>NA<br>1.202<br>2.403<br>9.615<br>19.231       | +0.17<br>+0.13<br>+0.16<br>+0.16 | SPBRG<br>value<br>(decimal) H<br>207<br>103<br>25<br>12 | KBAUD<br>9.727<br>18.643<br>37.286<br>55.930<br>111.860            | %<br>ERROR<br>+1.32<br>-2.90<br>-2.90<br>-2.90<br>-2.90 | value<br>(decimal)<br>22<br>11<br>5<br>3<br>1 | ) KBA<br>8.92<br>20.8<br>31.2<br>62.<br>NA       | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61<br>5 +8.51<br>A -<br>A -<br>A -<br>A - | value<br>R (decimal)<br>6<br>2<br>1<br>0<br>- | ) KBAUD<br>NA<br>NA<br>NA<br>NA<br>NA       | %<br>ERROR<br>-<br>-<br>-<br>-<br>-<br>-<br>- | value<br>(decimal)<br>-<br>-<br>-<br>-<br>-<br>- |

#### TABLE 9-7 REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address | Name  | Bit 7                | Bit 6    | Bit 5     | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|----------------------|----------|-----------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF     | RCIF      | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h     | RCSTA | SPEN                 | RX9      | SREN      | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 1Ah     | RCREG | USART Re             | eceive F | legister  |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE     | RCIE      | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h     | TXSTA | CSRC                 | TX9      | TXEN      | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h     | SPBRG | Baud Rate            | Genera   | ator Regi | ster  |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Reception.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

#### 9.4 USART Synchronous Slave Mode

Synchronous slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 9.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the synchronous master and slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

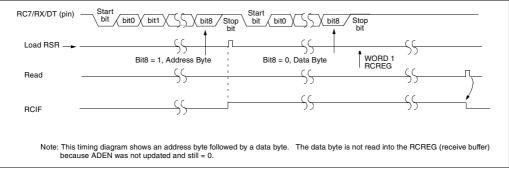

# 9.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the synchronous master and slave modes is identical except in the case of the SLEEP mode. Also, bit SREN is a don't care in slave mode.

If receive is enabled, by setting bit CREN, prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, then set enable bit  $\ensuremath{\mathsf{RCIE}}$  .

- 3. If 9-bit reception is desired, then set bit RX9.

- 4. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- 6. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

# FIGURE 11-2: ADCON1 REGISTER (ADDRESS 9Fh)

| ADFM    | VCFG                                                                   | 2 V                                                                                                | CFG1                                                                                                                                    | VCF                                                                                                     | GO P                                                                                               | CFG3                                                                                                       | PCFC                                                                                     | G2 P                                                                    | CFG1                                                                                                                                                                                                                                                                                                                                  | PCF                                                                | G0                                                                      | R =                 | Readable bit                                                         |

|---------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------|

| bit7    |                                                                        |                                                                                                    |                                                                                                                                         |                                                                                                         |                                                                                                    |                                                                                                            |                                                                                          |                                                                         |                                                                                                                                                                                                                                                                                                                                       | bit 0                                                              |                                                                         | W =<br>U =<br>- n = | Writable bit<br>Unimplemented bit, read as '0'<br>Value at POR reset |

| bit 7:  | <b>ADFM:</b><br>1 = Rig<br>0 = Leff                                    | ht justi                                                                                           | fied                                                                                                                                    | ormat S                                                                                                 | Select b                                                                                           | it                                                                                                         |                                                                                          |                                                                         |                                                                                                                                                                                                                                                                                                                                       |                                                                    |                                                                         |                     |                                                                      |

| bit 6:4 | VCFG2                                                                  | :VCFG                                                                                              | i0: Volt                                                                                                                                | age ref                                                                                                 | erence                                                                                             | configu                                                                                                    | ration                                                                                   | bits                                                                    |                                                                                                                                                                                                                                                                                                                                       |                                                                    |                                                                         |                     |                                                                      |

|         |                                                                        | Α/                                                                                                 | D VREF                                                                                                                                  | H                                                                                                       | Α                                                                                                  | /D VRE                                                                                                     | FL                                                                                       |                                                                         |                                                                                                                                                                                                                                                                                                                                       |                                                                    |                                                                         |                     |                                                                      |

|         | 000                                                                    |                                                                                                    | Avdd                                                                                                                                    |                                                                                                         |                                                                                                    | Avss                                                                                                       |                                                                                          |                                                                         |                                                                                                                                                                                                                                                                                                                                       |                                                                    |                                                                         |                     |                                                                      |

|         | 001                                                                    | Exte                                                                                               | ernal VF                                                                                                                                | REF+                                                                                                    | Exte                                                                                               | ernal V                                                                                                    | REF-                                                                                     |                                                                         |                                                                                                                                                                                                                                                                                                                                       |                                                                    |                                                                         |                     |                                                                      |

|         | 010                                                                    |                                                                                                    | ernal V                                                                                                                                 |                                                                                                         | Int                                                                                                | ernal V                                                                                                    | RL                                                                                       |                                                                         |                                                                                                                                                                                                                                                                                                                                       |                                                                    |                                                                         |                     |                                                                      |

|         | 011                                                                    |                                                                                                    | ernal VF                                                                                                                                |                                                                                                         |                                                                                                    | Avss                                                                                                       |                                                                                          |                                                                         |                                                                                                                                                                                                                                                                                                                                       |                                                                    |                                                                         |                     |                                                                      |

|         | 100                                                                    | Inte                                                                                               | ernal V                                                                                                                                 | RH                                                                                                      |                                                                                                    | Avss                                                                                                       |                                                                                          |                                                                         |                                                                                                                                                                                                                                                                                                                                       |                                                                    |                                                                         |                     |                                                                      |

|         | 101                                                                    |                                                                                                    | Avdd                                                                                                                                    |                                                                                                         |                                                                                                    | ernal V                                                                                                    |                                                                                          |                                                                         |                                                                                                                                                                                                                                                                                                                                       |                                                                    |                                                                         |                     |                                                                      |

|         | 110                                                                    |                                                                                                    | Avdd                                                                                                                                    |                                                                                                         | Int                                                                                                | ernal V                                                                                                    | RL                                                                                       |                                                                         |                                                                                                                                                                                                                                                                                                                                       |                                                                    |                                                                         |                     |                                                                      |

|         | 111                                                                    | Inte                                                                                               | ernal V                                                                                                                                 | RL                                                                                                      |                                                                                                    | Avss                                                                                                       |                                                                                          |                                                                         |                                                                                                                                                                                                                                                                                                                                       |                                                                    |                                                                         |                     |                                                                      |

| bit 3:0 | PCFG3                                                                  |                                                                                                    |                                                                                                                                         |                                                                                                         | onfigur<br>AN6                                                                                     |                                                                                                            | ts <sup>(1)</sup><br>AN4                                                                 | AN3                                                                     | AN2                                                                                                                                                                                                                                                                                                                                   | AN1                                                                | ANC                                                                     |                     |                                                                      |

| bit 3:0 |                                                                        | PCFG                                                                                               | i <b>0:</b> A/D                                                                                                                         | Port C                                                                                                  | -                                                                                                  | ation bi                                                                                                   |                                                                                          | AN3<br>A                                                                | AN2<br>A                                                                                                                                                                                                                                                                                                                              | AN1<br>A                                                           | ANC                                                                     |                     |                                                                      |

| bit 3:0 | PCFG3                                                                  | AN9<br>A                                                                                           | <b>i0:</b> A/D<br>AN8<br>A<br>A                                                                                                         | Port C<br>AN7<br>A<br>A                                                                                 | AN6<br>A<br>A                                                                                      | ation bi<br>AN5<br>A<br>A                                                                                  | AN4<br>A<br>A                                                                            | A<br>A                                                                  | A                                                                                                                                                                                                                                                                                                                                     | A<br>A                                                             | A<br>A                                                                  |                     |                                                                      |

| bit 3:0 | PCFG3 0000 0001 0010                                                   | AN9<br>A<br>A<br>A<br>A                                                                            | a <b>0:</b> A/D<br>AN8<br>A<br>A<br>A<br>A                                                                                              | Port C<br>AN7<br>A<br>A<br>A                                                                            | AN6<br>A<br>A<br>A                                                                                 | ation bi<br>AN5<br>A<br>A<br>A<br>A                                                                        | AN4<br>A<br>A<br>A                                                                       | A<br>A<br>A                                                             | A<br>A<br>A                                                                                                                                                                                                                                                                                                                           | A<br>A<br>A                                                        | A<br>A<br>A                                                             |                     |                                                                      |

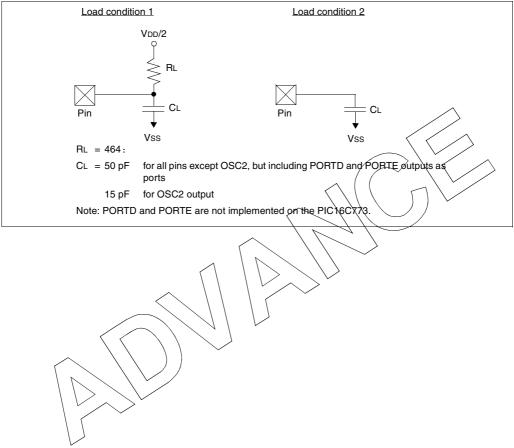

| bit 3:0 | PCFG3 0000 0001 0010 0011                                              | AN9<br>A<br>A<br>A<br>A<br>A<br>A                                                                  | ao: A/D<br>AN8<br>A<br>A<br>A<br>A<br>A                                                                                                 | Port C<br>AN7<br>A<br>A<br>A<br>A                                                                       | AN6<br>A<br>A<br>A<br>A                                                                            | AN5<br>A<br>A<br>A<br>A<br>A<br>A                                                                          | AN4<br>A<br>A<br>A<br>A                                                                  | A<br>A<br>A<br>A                                                        | A<br>A<br>A<br>A                                                                                                                                                                                                                                                                                                                      | A<br>A<br>A<br>A                                                   | A<br>A<br>A<br>A                                                        |                     |                                                                      |