Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 10x12b                                                                 |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-QFP                                                                     |

| Supplier Device Package    | 44-MQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc774t-i-pq |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

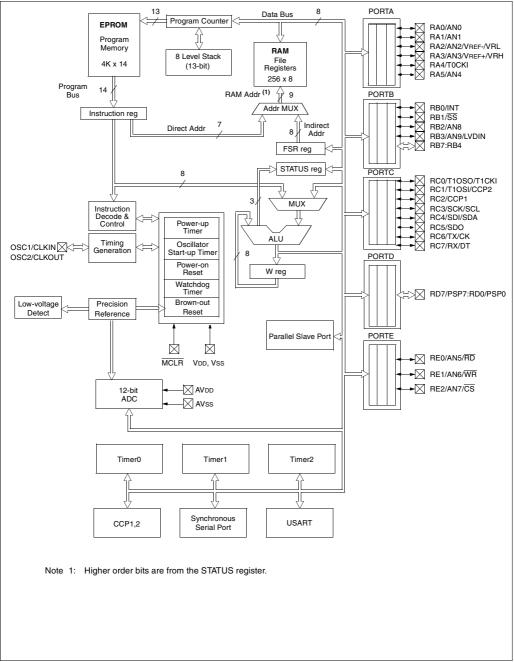

# 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (=1) will make the corresponding PORTC pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISC bit (=0) will make the corresponding PORTC pin an output, i.e., put the contents of the output latch on the selected pin.

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

### EXAMPLE 3-1: INITIALIZING PORTC

| BCF<br>CLRF | STATUS,<br>PORTC | RPO | ;; | Select Bank 0<br>Initialize PORTC by<br>clearing output |

|-------------|------------------|-----|----|---------------------------------------------------------|

|             |                  |     | ;  | data latches                                            |

| BSF         | STATUS,          | RP0 | ;  | Select Bank 1                                           |

| MOVLW       | 0xCF             |     | ;  | Value used to                                           |

|             |                  |     | ;  | initialize data                                         |

|             |                  |     | ;  | direction                                               |

| MOVWF       | TRISC            |     | ;  | Set RC<3:0> as inputs                                   |

|             |                  |     | ;  | RC<5:4> as outputs                                      |

|             |                  |     | ;  | RC<7:6> as inputs                                       |

## FIGURE 3-9: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

- Port/Peripheral select signal selects between port data and peripheral output.

- 3: Peripheral OE (output enable) is only activated if peripheral select is active.

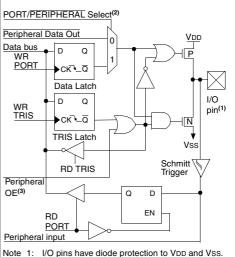

# 3.4 PORTD and TRISD Registers

This section is applicable to the 40/44-pin devices only.

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

PORTD can be configured as an 8-bit wide microprocessor port (parallel slave port) by setting control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

# FIGURE 3-10: PORTD BLOCK DIAGRAM (IN I/O PORT MODE)

# TABLE 3-7 PORTD FUNCTIONS

| Name     | Bit# | Buffer Type           | Function                                          |

|----------|------|-----------------------|---------------------------------------------------|

| RD0/PSP0 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit0 |

| RD1/PSP1 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit1 |

| RD2/PSP2 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit2 |

| RD3/PSP3 | bit3 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit3 |

| RD4/PSP4 | bit4 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit4 |

| RD5/PSP5 | bit5 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit5 |

| RD6/PSP6 | bit6 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit6 |

| RD7/PSP7 | bit7 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit7 |

|          | bit7 | ST/TTL <sup>(1)</sup> |                                                   |

Legend: ST = Schmitt Trigger input TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffer when in Parallel Slave Port Mode.

# TABLE 3-8 SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Address | Name  | Bit 7 | Bit 6  | Bit 5    | Bit 4       | Bit 3 | Bit 2     | Bit 1     | Bit 0     | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------|--------|----------|-------------|-------|-----------|-----------|-----------|--------------------------|---------------------------|

| 08h     | PORTD | RD7   | RD6    | RD5      | RD4         | RD3   | RD2       | RD1       | RD0       | xxxx xxxx                | uuuu uuuu                 |

| 88h     | TRISD | PORT  | D Data | Directio | on Register |       |           |           |           | 1111 1111                | 1111 1111                 |

| 89h     | TRISE | IBF   | OBF    | IBOV     | PSPMODE     | _     | PORTE Dat | 0000 -111 | 0000 -111 |                          |                           |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTD.

# PIC16C77X

# TABLE 3-9 PORTE FUNCTIONS

| Name       | Bit# | Buffer Type           | Function                                                                                                                                                                                         |

|------------|------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or read control input in parallel slave port mode or<br>analog input:<br>RD<br>1 = Not a read operation<br>0 = Read operation. Reads PORTD register (if chip selected)     |

| RE1/WR/AN6 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or write control input in parallel slave port mode or<br>analog input:<br>WR<br>1 = Not a write operation<br>0 = Write operation. Writes PORTD register (if chip selected) |

| RE2/CS/AN7 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or chip select control input in parallel slave port<br>mode or analog input:<br>CS<br>1 = Device is not selected<br>0 = Device is selected                                 |

Legend: ST = Schmitt Trigger input TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port Mode.

| Addr | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1       | Bit 0    | Value on:<br>POR,<br>BOR | Value on all other resets |

|------|--------|-------|-------|-------|---------|-------|---------|-------------|----------|--------------------------|---------------------------|

| 09h  | PORTE  | —     |       | _     | —       | —     | RE2     | RE1         | RE0      | xxx                      | uuu                       |

| 89h  | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | —     | PORTE D | Data Direct | ion Bits | 0000 -111                | 0000 -111                 |

| 9Fh  | ADCON1 | ADFM  | VCFG2 | VCFG1 | VCFG0   | PCFG3 | PCFG2   | PCFG1       | PCFG0    | 0000 0000                | 0000 0000                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTE.

#### 5.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (Two 8-bit registers; TMR1H and TMR1L)

- Readable and writable (Both registers)

- · Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- · Reset from CCP module trigger

Timer1 has a control register, shown in Figure 5-1. Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Figure 5-3 is a simplified block diagram of the Timer1 module.

Additional information on timer modules is available in the PICmicro™ Mid-Range Reference Manual, (DS33023).

#### 5.1 **Timer1 Operation**

Timer1 can operate in one of these modes:

- · As a timer

- · As a synchronous counter

- As an asynchronous counter

The operating mode is determined by the clock select bit. TMR1CS (T1CON<1>).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored.

Timer1 also has an internal "reset input". This reset can be generated by the CCP module (Section 7.0).

#### T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h) U-0 U-0 R/W-0 R/W-0 B/W-0 R/W-0 **B/W-0** R/W-0 T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON R = Readable bit W = Writable bit bit7 bit0 = Unimplemented bit, U read as '0' n = Value at POR reset bit 7-6: Unimplemented: Read as '0' bit 5-4: T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits 11 = 1:8 Prescale value 10 = 1:4 Prescale value 01 = 1:2 Prescale value 00 = 1:1 Prescale value T1OSCEN: Timer1 Oscillator Enable Control bit hit 3 1 = Oscillator is enabled 0 = Oscillator is shut off Note: The oscillator inverter and feedback resistor are turned off to eliminate power drain T1SYNC: Timer1 External Clock Input Synchronization Control bit bit 2: TMR1CS = 11 = Do not synchronize external clock input 0 = Synchronize external clock input TMR1CS = 0This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0. TMR1CS: Timer1 Clock Source Select bit bit 1: 1 = External clock from pin RC0/T1OSO/T1CKI (on the rising edge) 0 = Internal clock (Fosc/4)

# FIGURE 5-1:

- 1 = Enables Timer1

- 0 = Stops Timer1

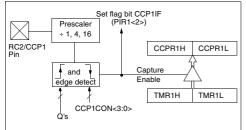

# 7.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as:

- · every falling edge

- · every rising edge

- · every 4th rising edge

- every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 7.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 is configured as an out-     |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

# FIGURE 7-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 7.1.2 TIMER1 MODE SELECTION

Timer1 must be running in timer mode or synchronized counter mode for the CCP module to use the capture feature. In asynchronous counter mode, the capture operation may not work.

#### 7.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in operating mode.

### 7.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in capture mode, the prescaler counter is cleared. This means that any reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 7-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

# EXAMPLE 7-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ; value                 |

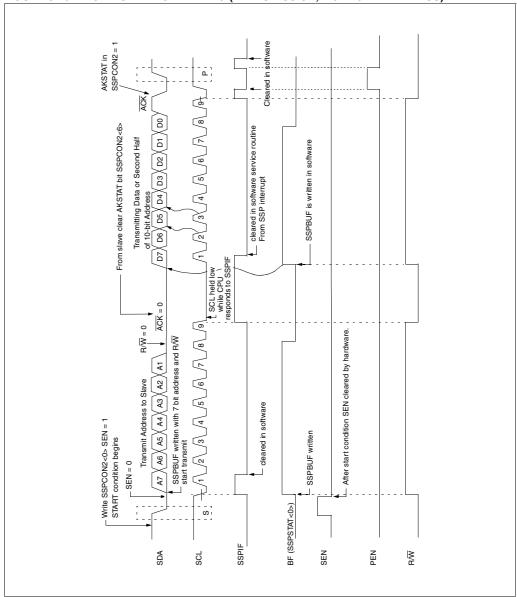

- The MSSP Module shifts in the ACK bit from the slave device, and writes its value into the SSPCON2 register (SSPCON2<6>).

- j) The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- k) The user generates a STOP condition by setting the STOP enable bit PEN in SSPCON2.

- I) Interrupt is generated once the STOP condition is complete.

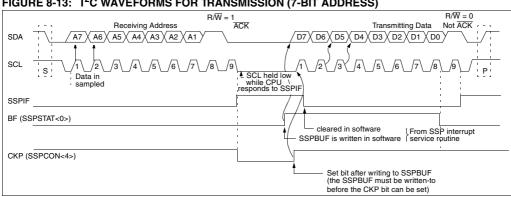

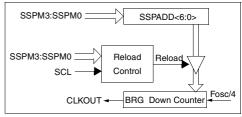

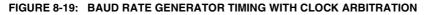

#### 8.2.8 BAUD RATE GENERATOR

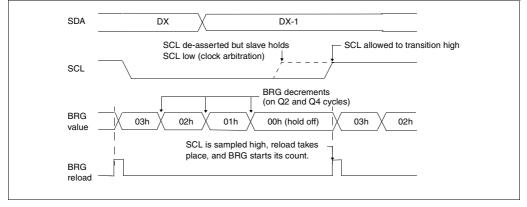

In  $l^2$ C master mode, the reload value for the BRG is located in the lower 7 bits of the SSPADD register (Figure 8-18). When the BRG is loaded with this value, the BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (TCY) on the Q2 and Q4 clock.

In I<sup>2</sup>C master mode, the BRG is reloaded automatically. If Clock Arbitration is taking place for instance, the BRG will be reloaded when the SCL pin is sampled high (Figure 8-19).

#### FIGURE 8-18: BAUD RATE GENERATOR BLOCK DIAGRAM

FIGURE 8-26: I<sup>2</sup>C MASTER MODE TIMING (TRANSMISSION, 7 OR 10-BIT ADDRESS)

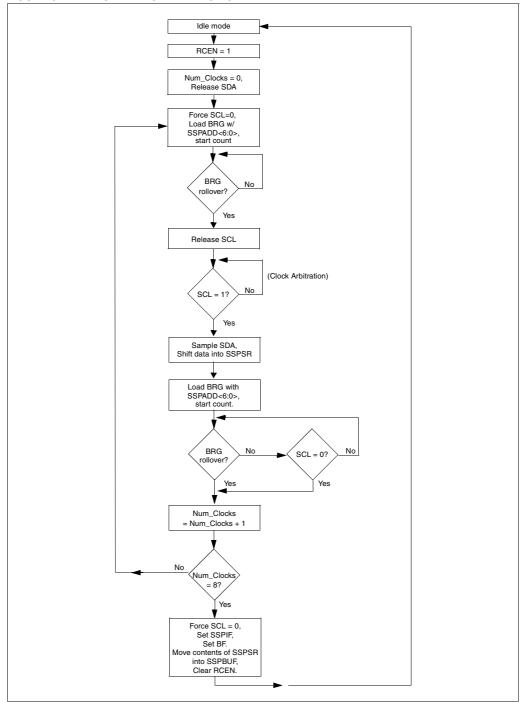

FIGURE 8-27: MASTER RECEIVER FLOWCHART

# FIGURE 9-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS 18h)

| R/W-0<br>SPEN | R/W-0<br>RX9                                                         | SREN                        | R/W-0<br>CREN            | R/W-0<br>ADDEN             | R-0<br>FERR | OERR         | R-x<br>RX9D                | R = Readable bit                                                                     |

|---------------|----------------------------------------------------------------------|-----------------------------|--------------------------|----------------------------|-------------|--------------|----------------------------|--------------------------------------------------------------------------------------|

| bit7          |                                                                      |                             |                          |                            |             |              | bit0                       | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset |

| bit 7:        | <b>SPEN</b> : Ser<br>1 = Serial p<br>0 = Serial p                    | ort enable                  | d (Configu               | res RC7/R                  | X/DT and I  | RC6/TX/Cł    | <pre>&lt; pins as se</pre> | rial port pins)                                                                      |

| bit 6:        | <b>RX9</b> : 9-bit I<br>1 = Selects<br>0 = Selects                   | 9-bit rece                  | otion                    |                            |             |              |                            |                                                                                      |

| bit 5:        | SREN: Sing                                                           | gle Receive                 | e Enable b               | it                         |             |              |                            |                                                                                      |

|               | <u>Asynchrone</u><br>Don't care                                      | ous mode                    |                          |                            |             |              |                            |                                                                                      |

|               | Synchronom1 = Enables0 = DisableThis bit is c                        | s single reo<br>s single re | ceive<br>ceive           | n is comple                | te.         |              |                            |                                                                                      |

|               | Synchrono<br>Unused in t                                             |                             | <u>slave</u>             |                            |             |              |                            |                                                                                      |

| bit 4:        | CREN: Cor                                                            | ntinuous Re                 | eceive Ena               | able bit                   |             |              |                            |                                                                                      |

|               | $\frac{\text{Asynchrono}}{1 = \text{Enables}}$ $0 = \text{Disable}$  | s continuou                 |                          |                            |             |              |                            |                                                                                      |

|               | $\frac{\text{Synchronom}}{1 = \text{Enables}}$ $0 = \text{Disables}$ | s continuou                 |                          |                            | e bit CREN  | l is cleared | (CREN ove                  | errides SREN)                                                                        |

| bit 3:        |                                                                      | ous mode s<br>address o     | 9-bit (RX9<br>detection, | <u>= 1)</u><br>enable inte |             |              |                            | er when RSR<8> is set<br>used as parity bit                                          |

| bit 2:        | FERR: Fran<br>1 = Framing<br>0 = No fran                             | g error (Ca                 |                          | ted by read                | ing RCRE    | G register a | and receive                | next valid byte)                                                                     |

| bit 1:        | <b>OERR</b> : Ove<br>1 = Overrun<br>0 = No ove                       | n error (Ca                 |                          | ed by clear                | ing bit CRI | EN)          |                            |                                                                                      |

| bit 0:        | <b>RX9D</b> : 9th                                                    | hit of rocoi                | und data (i              | Con ho nor                 | ity bit)    |              |                            |                                                                                      |

# 12.0 SPECIAL FEATURES OF THE CPU

These PICmicro devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Low-voltage detection

- SLEEP

- Code protection

- · ID locations

- · In-circuit serial programming

These devices have a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up type resets only (POR, BOR), designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

Additional information on special features is available in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

## 12.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

Some of the core features provided may not be necessary to each application that a device may be used for. The configuration word bits allow these features to be configured/enabled/disabled as necessary. These features include code protection, brown-out reset and its trippoint, the power-up timer, the watchdog timer and the devices oscillator mode. As can be seen in Figure 12-1, some additional configuration word bits have been provided for brown-out reset trippoint selection.

# FIGURE 12-1: CONFIGURATION WORD

| CP1     | CP0    | BORV1                | BORV0    | CP1    | CP0      | -                   | BODEN            | CP1              | CP0 | PWRTE | WDTE | FOSC1 | FOSC0       | Register:<br>Address | CONFIG<br>2007h |

|---------|--------|----------------------|----------|--------|----------|---------------------|------------------|------------------|-----|-------|------|-------|-------------|----------------------|-----------------|

| bit13   | 12     | 11                   | 10       | 9      | 8        | 7                   | 6                | 5                | 4   | 3     | 2    | 1     | bit0        | Address              | 2007h           |

| oit 13  | -12: ( | CP1:CP               | 0: Code  | Prote  | ction b  | oits <sup>(2)</sup> |                  |                  |     |       |      |       |             | 1                    |                 |

| bit 9-8 | B: ·   | 11 = Pro             | gram m   | emory  | code p   | rotecti             | on off           |                  |     |       |      |       |             |                      |                 |

| oit 5-4 |        | 10 = 080             |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        | 01 = 040             |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        | 00 = 000             |          |        | •        |                     |                  | (3)              |     |       |      |       |             |                      |                 |

| bit 11  |        |                      |          |        | n-out F  | eset V              | oltage bit       | s <sup>(3)</sup> |     |       |      |       |             |                      |                 |

|         |        | 11 = Vвс<br>10 = Vвс |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        | 0 = VBC              |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         | (      | 00 = Vвс             | R set to | 4.5V   |          |                     |                  |                  |     |       |      |       |             |                      |                 |

| bit 7:  | I      | Unimple              | mented   | I, Rea | d as '1' |                     |                  |                  |     |       |      |       |             |                      |                 |

| bit 6:  |        | BODEN:               | Brown-   | out Re | eset En  | able bi             | <sub>†</sub> (1) |                  |     |       |      |       |             |                      |                 |

|         |        | 1 = Brow             |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         | (      | ) = Brow             | n-out R  | eset d | isabled  |                     |                  |                  |     |       |      |       |             |                      |                 |

| bit 3:  | ī      | WRTE:                | Power-   | up Tin | ner Ena  | ble bit             | (1)              |                  |     |       |      |       |             |                      |                 |

|         |        | 1 = PWF              |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         | (      | D = PWF              | RT enabl | ed     |          |                     |                  |                  |     |       |      |       |             |                      |                 |

| bit 2:  |        | WDTE: \              |          | 0      | er Enał  | ole bit             |                  |                  |     |       |      |       |             |                      |                 |

|         |        | 1 = WDT              |          | -      |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        | O = WDT              |          | -      |          |                     |                  |                  |     |       |      |       |             |                      |                 |

| bit 1-0 |        | FOSC1:               |          |        | ator Se  | lectior             | bits             |                  |     |       |      |       |             |                      |                 |

|         |        | 11 = RC<br>10 = HS   |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        | 0 = HS<br>01 = XT (  |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        | 00 = LP              |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        |                      |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

| Note    |        |                      |          |        |          |                     |                  |                  |     |       |      |       | dless of th | ne value of b        | it PWRTE.       |

|         |        |                      |          |        |          |                     | ed anytim        |                  |     |       |      |       | tion scher  | na listad            |                 |

|         |        |                      |          |        |          |                     |                  |                  |     |       |      |       |             | election of a        | n unused        |

|         |        |                      |          |        |          |                     | nterrupt.        | , 000            |     |       |      |       |             |                      |                 |

# 12.2 Oscillator Configurations

#### 12.2.1 OSCILLATOR TYPES

The PIC16C77X can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

# 12.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 12-2). The PIC16C77X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications.

A difference from the other mid-range devices may be noted in that the device can be driven from an external clock only when configured in HS mode (Figure 12-3).

#### 12.2.3 RC OSCILLATOR

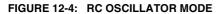

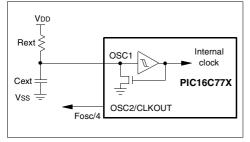

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. These factors and the variation due to tolerances of external R and C components used need to be taken into account for each application. Figure 12-4 shows how the R/C combination is connected to the PIC16C77X.

### FIGURE 12-14: WAKE-UP FROM SLEEP THROUGH INTERRUPT

|                                               |                                                   | Q1 Q2 Q3 Q4  | Q1 Q2 Q3 Q4       | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4 |

|-----------------------------------------------|---------------------------------------------------|--------------|-------------------|-------------------|-------------------|

|                                               |                                                   |              |                   |                   |                   |

| CLKOUT(4)                                     | Tost(2)                                           |              | \;                | \                 |                   |

| INT pin                                       |                                                   |              | 1 i               | 1                 |                   |

| INTF flag                                     | <u>لې او </u> |              | Interrupt Latency |                   |                   |

| (INTCOŇ<1>)                                   |                                                   |              | (Note 2)          | 1                 | 1                 |

| GIE bit<br>(INTCON<7>)                        | Processor in                                      |              | ·                 | 1                 |                   |

| (                                             | SLEEP                                             |              | · ·               | I<br>I            | 1                 |

| INSTRUCTION FLOW                              |                                                   |              | 1 I<br>1 I        | I<br>I            | I<br>I            |

| PC X PC X PC+1                                | PC+2                                              | PC+2         | χ PC + 2          | (0004h            | (0005h            |

| Instruction { Inst(PC) = SLEEP Inst(PC + 1)   |                                                   | Inst(PC + 2) | 1 1<br>1 1<br>1 1 | Inst(0004h)       | Inst(0005h)       |

| Instruction<br>executed Inst(PC - 1) SLEEP    |                                                   | Inst(PC + 1) | Dummy cycle       | Dummy cycle       | Inst(0004h)       |

| Note 1: XT, HS or LP oscillator mode assumed. | -                                                 |              |                   |                   |                   |

2: TOST = 1024TOSC (drawing not to scale) This delay will not be there for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

#### 12.14 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

Note: Microchip does not recommend code protecting windowed devices.

## 12.15 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

For ROM devices, these values are submitted along with the ROM code.

### 12.16 In-Circuit Serial Programming

PIC16CXXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

For complete details of serial programming, please refer to the In-Circuit Serial Programming (ICSP™) Guide, (DS30277).

# 13.0 INSTRUCTION SET SUMMARY

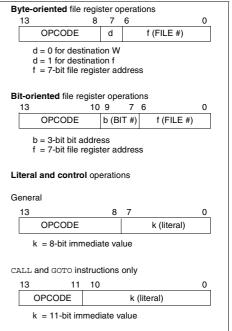

Each PIC16CXXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXX instruction set summary in Table 13-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 13-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

## TABLE 13-1 OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                 |  |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                        |  |  |  |  |  |  |

| W     | Working register (accumulator)                                                                                                                                              |  |  |  |  |  |  |

| b     | Bit address within an 8-bit file register                                                                                                                                   |  |  |  |  |  |  |

| k     | Literal field, constant data or label                                                                                                                                       |  |  |  |  |  |  |

| x     | Don't care location (= 0 or 1)<br>The assembler will generate code with x = 0. It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |  |  |  |  |  |  |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                |  |  |  |  |  |  |

| PC    | Program Counter                                                                                                                                                             |  |  |  |  |  |  |

| TO    | Time-out bit                                                                                                                                                                |  |  |  |  |  |  |

| PD    | Power-down bit                                                                                                                                                              |  |  |  |  |  |  |

The instruction set is highly orthogonal and is grouped into three basic categories:

- · Byte-oriented operations

- Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Table 13-2 lists the instructions recognized by the MPASM assembler.

Figure 13-1 shows the general formats that the instructions can have.

| Note: | To maintain upward compatibility with |

|-------|---------------------------------------|

|       | future PIC16CXXX products, do not use |

|       | the OPTION and TRIS instructions.     |

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

### FIGURE 13-1: GENERAL FORMAT FOR INSTRUCTIONS

A description of each instruction is available in the PICmicro™ Mid-Range Reference Manual, (DS33023).

# FIGURE 15-8: BANDGAP START-UP TIME

| TABLE 15-8     | BANDGAP START-UP TIME | $\sum$           |

|----------------|-----------------------|------------------|

|                |                       | 2                |

| Bandgap stable | ← TBGAP —►            |                  |

| Enable Bandgap |                       |                  |

| Vbgap          |                       | <br>'BGAP = 1.2V |

#### **TABLE 15-8 BANDGAP START-UP TIME**

| Parameter<br>No. | Sym       | Characteristic                        | Min | Тур | t   | Max | ί | Inits | $\searrow$          | Con                      | ditions                                                    | $\mathcal{D}$ |

|------------------|-----------|---------------------------------------|-----|-----|-----|-----|---|-------|---------------------|--------------------------|------------------------------------------------------------|---------------|

| 36*              | TBGAP     | Bandgap start-up time                 |     | 30  | //  | TBD |   | μs    | the inst<br>is enab | ant tha<br>ed an<br>band | e time be<br>at the bar<br>d the moi<br>gap refere<br>ble. | dgap<br>nent  |

| * The            | oo noroma | tore are characterized but not tested |     | · \ | . \ | · \ |   | >     |                     |                          |                                                            |               |

These parameters are characterized but not tested. Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

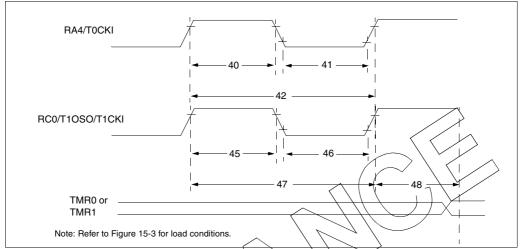

# FIGURE 15-11: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

|             |                   | 1        |   | \<br>\  | $\sim$    |

|-------------|-------------------|----------|---|---------|-----------|

| TADIE 16 10 | TIMER0 AND TIMER1 | EVTEDN/  |   | OV DENI | INDEMENTO |

| IADLE 13-12 |                   | EXICHINA |   |         |           |

|             |                   |          | r |         |           |

| Param | C         | Characteristic        |                       | $\rightarrow$       | Min                   | Treat | Max   | Unite    | Conditions                     |

|-------|-----------|-----------------------|-----------------------|---------------------|-----------------------|-------|-------|----------|--------------------------------|

| No.   | Sym       | Characteristic        | \ \                   |                     |                       | Тур†  | wax   | Units    | Conditions                     |

| 40*   | TIOLI     | TOOKI Link Dulas K    |                       |                     |                       |       |       |          | March allo a second            |

| 40."  | Tt0H      | T0CKI High Pulse 🕅    |                       | No Prescaler        | 0.5TCY + 20           | _     | _     | ns       | Must also meet<br>parameter 42 |

|       |           |                       |                       | With Prescaler      | 10                    | —     | —     | ns       |                                |

| 41*   | TtOL      | TOCKI Low Pulse W     | /iðth 1               | No Prescaler        | 0.5TCY + 20           | —     | —     | ns       | Must also meet                 |

|       |           |                       |                       | With Prescaler      | 10                    | —     |       | ns       | parameter 42                   |

| 42*   | Tt0P      | TOCK Period           |                       | No Prescaler        | TCY + 40              | —     |       | ns       |                                |

|       |           |                       |                       | With Prescaler      |                       | —     | —     | ns       | N = prescale value             |

|       |           | $\land \land \lor$    |                       |                     | 20 or <u>TCY + 40</u> |       |       |          | (2, 4,, 256)                   |

|       |           |                       |                       |                     | N                     |       |       |          |                                |

| 45*   | Tt1H      | TICKI High Time       | Synchronous, P        |                     | 0.5TCY + 20           | -     |       | ns       | Must also meet                 |

|       |           |                       | Synchronous,          | PIC16 <b>C</b> 77X  | 15                    | —     | —     | ns       | parameter 47                   |

|       |           | 1                     | Prescaler =<br>2,4,8  | PIC16 <b>LC</b> 77X | 25                    | -     |       | ns       |                                |

|       |           |                       | 2,4,8<br>Asynchronous | PIC16 <b>C</b> 77X  | 30                    | _     |       | ns       | -                              |

|       |           |                       | Asynchronous          | PIC16 <b>C</b> 77X  | 50                    |       |       |          | -                              |

| 46*   | Tt1L      | T1CKI Low Time        | Synchronous, P        |                     | 0.5TCY + 20           |       |       | ns       | Must also meet                 |

| 40    | ILL       | I TOKI LOW TIME       | Synchronous, P        | PIC16C77X           | 15                    | _     |       | ns<br>ns | parameter 47                   |

|       |           |                       | Prescaler =           | PIC16 <b>LC</b> 77X | 25                    | _     | _     |          |                                |

|       |           |                       | 2.4.8                 | PIC 16LC//X         | 25                    | _     | _     | ns       |                                |

|       |           |                       | Asynchronous          | PIC16 <b>C</b> 77X  | 30                    | _     |       | ns       |                                |

|       |           |                       | , lognon on ouo       | PIC16 <b>LC</b> 77X | 50                    | _     |       | ns       |                                |

| 47*   | Tt1P      | T1CKI input period    | Synchronous           | PIC16 <b>C</b> 77X  | Greater of:           | _     |       | ns       | N = prescale value             |

|       |           |                       | -,                    |                     | 30 OR TCY + 40        |       |       |          | (1, 2, 4, 8)                   |

|       |           |                       |                       |                     | N                     |       |       |          |                                |

|       |           |                       |                       | PIC16 <b>LC</b> 77X | Greater of:           | —     |       | ns       | N = prescale value             |

|       |           |                       |                       |                     | 50 OR <u>TCY + 40</u> |       |       |          | (1, 2, 4, 8)                   |

|       |           |                       |                       |                     | N                     |       |       |          |                                |

|       |           |                       | Asynchronous          | PIC16 <b>C</b> 77X  | 60                    | —     | -     | ns       |                                |

|       |           |                       |                       | PIC16 <b>LC</b> 77X | 100                   | —     | —     | ns       |                                |

|       | Ft1       | Timer1 oscillator inp |                       |                     | DC                    | —     | 50    | kHz      |                                |

|       |           | (oscillator enabled b |                       |                     |                       |       |       |          |                                |

| 48    | TCKEZtmr1 | Delay from external   | clock edge to tin     | ner increment       | 2Tosc                 | -     | 7Tosc |          |                                |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16C77X

NOTES:

# PIC16C77X PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.<br>Device F | -XX X /XX XXX<br>requency Temperature Package Pattern<br>Range Range                                                                                                                                                                    | Examples:<br>g) PIC16C774 -04/P 301 = Commercial temp.,<br>PDIP package, 4 MHz, normal VDD limits, QTP<br>pattern #301.                                                                              |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device               | PIC16C77X <sup>(1)</sup> , PIC16C77XT <sup>(2)</sup> ;VDD range 4.0V to 5.5V<br>PIC16LC77X <sup>(1)</sup> , PIC16LC77XT <sup>(2)</sup> ;VDD range 2.5V to 5.5V                                                                          | <ul> <li>h) PIC16LC773 - 04I/SO = Industrial temp., SOIC package, 200 kHz, Extended VDD limits.</li> <li>i) PIC16C774 - 20I/P = Industrial temp., PDIP package, 20MHz, normal VDD limits.</li> </ul> |

| Frequency Range      | 04 = 4 MHz<br>20 = 20 MHz                                                                                                                                                                                                               | Note 1: C = CMOS                                                                                                                                                                                     |

| Temperature Range    | $b^{(3)} = 0^{\circ}C$ to 70°C (Commercial)<br>I = -40°C to +85°C (Industrial)                                                                                                                                                          | LC = Low Power CMOS<br>T = in tape and reel - SOIC, SSOP,<br>PLCC,<br>MQFP, TQFP packages only.<br>2: b = blank                                                                                      |

| Package              | $\begin{array}{rcl} JW & = & Windowed CERDIP/Ceramic \\ PQ & = & MQFP (Metric PQFP) \\ PT & = & TQFP (Thin Quad Flatpack) \\ SO & = & SOIC \\ SP & = & Skinny plastic dip \\ P & = & PDIP \\ L & = & PLCC \\ SS & = & SSOP \end{array}$ |                                                                                                                                                                                                      |

| Pattern              | QTP, SQTP, Code or Special Requirements<br>(blank otherwise)                                                                                                                                                                            |                                                                                                                                                                                                      |

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type (including LC devices).

#### Sales and Support

#### **Data Sheets**

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.