Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XFI

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 10x12b                                                                 |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc774t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.2 OPTION\_REG REGISTER

The OPTION\_REG register is a readable and writable register which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0, and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

## FIGURE 2-4: OPTION\_REG REGISTER (ADDRESS 81h, 181h)

| RBPU     | INTEDG                   | TOCS                                          | TOSE      | PSA        | PS2           | PS1        | PS0  | R = Readable bit                           |  |  |  |  |  |  |  |  |

|----------|--------------------------|-----------------------------------------------|-----------|------------|---------------|------------|------|--------------------------------------------|--|--|--|--|--|--|--|--|

| t7       |                          |                                               |           | 1.0/1      | . 02          |            | bit0 | W = Writable bit                           |  |  |  |  |  |  |  |  |

|          |                          |                                               |           |            |               |            | 5.10 | U = Unimplemented bit,                     |  |  |  |  |  |  |  |  |

|          |                          |                                               |           |            |               |            |      | read as '0'                                |  |  |  |  |  |  |  |  |

|          |                          |                                               |           |            |               |            |      | <ul> <li>n = Value at POR reset</li> </ul> |  |  |  |  |  |  |  |  |

| oit 7:   | RBPU: PC                 | RTB Pull-                                     | up Enabl  | e bit      |               |            |      |                                            |  |  |  |  |  |  |  |  |

|          | 1 = PORTI                | B pull-ups                                    | are disal | oled       |               |            |      |                                            |  |  |  |  |  |  |  |  |

|          | 0 = PORTI                | B pull-ups                                    | are enab  | led by inc | lividual port | latch valu | es   |                                            |  |  |  |  |  |  |  |  |

| oit 6:   |                          | · ·                                           |           |            | ·             |            |      |                                            |  |  |  |  |  |  |  |  |

| л о.     | INTEDG: I<br>1 = Interru |                                               |           |            | nin           |            |      |                                            |  |  |  |  |  |  |  |  |

|          |                          |                                               |           |            |               |            |      |                                            |  |  |  |  |  |  |  |  |

|          | 0 = Interru              | pt on tailing                                 | g eage o  | TRB0/IN    | pin           |            |      |                                            |  |  |  |  |  |  |  |  |

| oit 5:   | TOCS: TM                 | R0 Clock S                                    | Source S  | elect bit  |               |            |      |                                            |  |  |  |  |  |  |  |  |

|          | 1 = Transit              | ion on RA4                                    | 4/T0CKI   | pin        |               |            |      |                                            |  |  |  |  |  |  |  |  |

|          | 0 = Interna              | ) = Internal instruction cycle clock (CLKOUT) |           |            |               |            |      |                                            |  |  |  |  |  |  |  |  |

| oit 4:   | TOSE: TM                 | R0 Source                                     | Edge Se   | elect bit  |               |            |      |                                            |  |  |  |  |  |  |  |  |

|          |                          |                                               |           |            | on RA4/T0     | CKI pin    |      |                                            |  |  |  |  |  |  |  |  |

|          |                          |                                               |           |            | on RA4/T0     |            |      |                                            |  |  |  |  |  |  |  |  |

| bit 3:   | PSA: Pres                |                                               | 0         |            |               |            |      |                                            |  |  |  |  |  |  |  |  |

| 011 3.   | 1 = Presca               |                                               |           |            |               |            |      |                                            |  |  |  |  |  |  |  |  |

|          | 0 = Presca               |                                               | ,         |            | modulo        |            |      |                                            |  |  |  |  |  |  |  |  |

|          |                          |                                               |           |            | module        |            |      |                                            |  |  |  |  |  |  |  |  |

| oit 2-0: | PS2:PS0:                 | Prescaler                                     | Rate Sel  | ect bits   |               |            |      |                                            |  |  |  |  |  |  |  |  |

|          | Bit Value                | TMR0 Ra                                       | te WD     | r Rate     |               |            |      |                                            |  |  |  |  |  |  |  |  |

|          | 000                      | 1:2                                           | 1 :       | 1          |               |            |      |                                            |  |  |  |  |  |  |  |  |

|          | 001                      | 1:4                                           | 1 :       |            |               |            |      |                                            |  |  |  |  |  |  |  |  |

|          | 010                      | 1:8                                           | 1:        |            |               |            |      |                                            |  |  |  |  |  |  |  |  |

|          | 011                      | 1:16                                          | 1:        |            |               |            |      |                                            |  |  |  |  |  |  |  |  |

|          | 100                      | 1:32                                          |           | 16         |               |            |      |                                            |  |  |  |  |  |  |  |  |

|          | 101<br>110               | 1:64                                          |           | 32<br>64   |               |            |      |                                            |  |  |  |  |  |  |  |  |

|          | TTO                      | 1:128                                         | · .       | 64<br>128  |               |            |      |                                            |  |  |  |  |  |  |  |  |

|          | 111                      |                                               |           |            |               |            |      |                                            |  |  |  |  |  |  |  |  |

# PIC16C77X

## 2.2.2.3 INTCON REGISTER

The INTCON Register is a readable and writable register which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## FIGURE 2-5: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

| R/W-0  | R/W-0                                          | R/W-0       | R/W-0       | R/W-0        | R/W-0                           | R/W-0       | R/W-x        |                                                                                                                        |

|--------|------------------------------------------------|-------------|-------------|--------------|---------------------------------|-------------|--------------|------------------------------------------------------------------------------------------------------------------------|

| GIE    | PEIE                                           | TOIE        | INTE        | RBIE         | T0IF                            | INTF        | RBIF         | R = Readable bit                                                                                                       |

| bit7   |                                                |             |             |              |                                 |             | bitO         | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>- n = Value at POR reset</li> </ul> |

| bit 7: | <b>GIE:</b> Glob<br>1 = Enable<br>0 = Disable  | es all un-r | nasked in   |              |                                 |             |              |                                                                                                                        |

| bit 6: | <b>PEIE</b> : Per<br>1 = Enable<br>0 = Disable | es all un-r | nasked pe   | eripheral in | iterrupts                       |             |              |                                                                                                                        |

| bit 5: | <b>TOIE</b> : TMF<br>1 = Enable<br>0 = Disable | es the TM   | R0 interru  | ıpt          | oit                             |             |              |                                                                                                                        |

| bit 4: | IINTE: RE<br>1 = Enable<br>0 = Disable         | es the RB   | 0/INT exte  | ernal interr | upt                             |             |              |                                                                                                                        |

| bit 3: | <b>RBIE</b> : RB<br>1 = Enable<br>0 = Disable  | es the RB   | port char   | ige interru  | pt                              |             |              |                                                                                                                        |

| bit 2: | <b>TOIF</b> : TMF<br>1 = TMR0<br>0 = TMR0      | register h  | nas overflo | wed (mus     | t be cleare                     | d in softwa | re)          |                                                                                                                        |

| bit 1: | INTF: RB(<br>1 = The R<br>0 = The R            | B0/INT ex   | ternal inte | errupt occi  | urred (must                     | be cleared  | d in softwa  | re)                                                                                                                    |

| bit 0: |                                                | st one of t | he RB7:R    | B4 pins ch   | t<br>nanged stat<br>anged state |             | e cleared in | software)                                                                                                              |

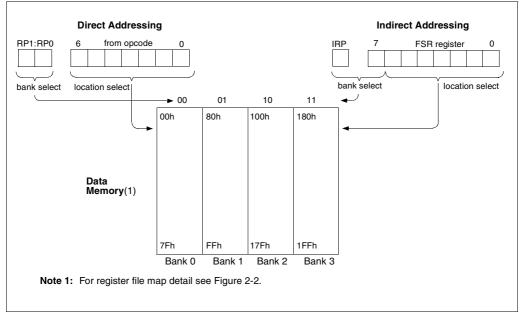

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-1.

#### EXAMPLE 2-1: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT     | incf<br>btfss | FSR<br>INDF<br>FSR<br>FSR,4 | ; to RAM<br>;clear INDF register<br>;inc pointer<br>;all done? |

|----------|---------------|-----------------------------|----------------------------------------------------------------|

|          | goto          | NEX.L.                      | ;NO, clear next                                                |

| CONTINUE |               |                             |                                                                |

|          | :             |                             | ;YES, continue                                                 |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-11.

## FIGURE 2-11: DIRECT/INDIRECT ADDRESSING

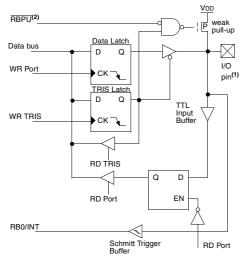

## 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISB bit (=0) will make the corresponding PORTB pin an output, i.e., put the contents of the output latch on the selected pin.

#### EXAMPLE 3-1: INITIALIZING PORTB

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| CLRF  | PORTB   |     | ; | Initialize PORTB by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISB   |     | ; | Set RB<3:0> as inputs |

|       |         |     | ; | RB<5:4> as outputs    |

|       |         |     | ; | RB<7:6> as inputs     |

|       |         |     |   |                       |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overrightarrow{\text{RBPU}}$  (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

The RB0 pin is multiplexed with the external interrupt (RB0/INT).

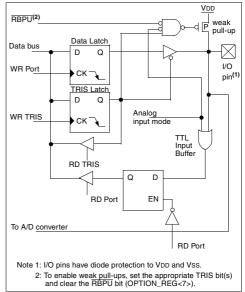

## FIGURE 3-4: BLOCK DIAGRAM OF RB0 PIN

Note 1: I/O pins have diode protection to VDD and VSS. 2: To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (OPTION\_REG<7>).

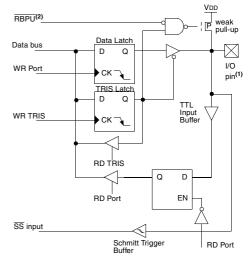

The RB1 pin is multiplexed with the SSP module slave select (RB1/SS).

#### FIGURE 3-5: BLOCK DIAGRAM OF RB1/SS PIN

Note 1: I/O pins have diode protection to VDD and Vss. 2: To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (OPTION\_REG<7>).

The RB2 pin is multiplexed with analog channel 8 (RB2/AN8).

#### FIGURE 3-6: BLOCK DIAGRAM OF RB2/AN8 PIN

## 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (=1) will make the corresponding PORTC pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISC bit (=0) will make the corresponding PORTC pin an output, i.e., put the contents of the output latch on the selected pin.

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

## EXAMPLE 3-1: INITIALIZING PORTC

| BCF<br>CLRF | STATUS,<br>PORTC | RPO | ;; | Select Bank 0<br>Initialize PORTC by<br>clearing output |

|-------------|------------------|-----|----|---------------------------------------------------------|

|             |                  |     | ;  | data latches                                            |

| BSF         | STATUS,          | RP0 | ;  | Select Bank 1                                           |

| MOVLW       | 0xCF             |     | ;  | Value used to                                           |

|             |                  |     | ;  | initialize data                                         |

|             |                  |     | ;  | direction                                               |

| MOVWF       | TRISC            |     | ;  | Set RC<3:0> as inputs                                   |

|             |                  |     | ;  | RC<5:4> as outputs                                      |

|             |                  |     | ;  | RC<7:6> as inputs                                       |

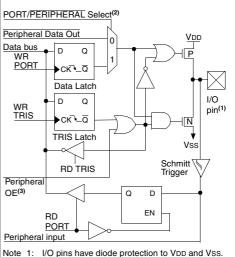

## FIGURE 3-9: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

- Port/Peripheral select signal selects between port data and peripheral output.

- 3: Peripheral OE (output enable) is only activated if peripheral select is active.

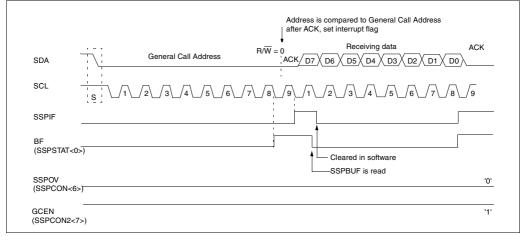

#### 8.2.2 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the START condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all 0's with R/W = 0

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> is set). Following a start-bit detect, 8-bits are shifted into SSPSR and the address is compared against SSPADD, and is also compared to the general call address, fixed in hardware. If the general call address matches, the SSPSR is transfered to the SSPBUF, the BF flag is set (eighth bit), and on the falling edge of the ninth bit ( $\overline{ACK}$  bit) the SSPIF flag is set.

When the interrupt is serviced. The source for the interrupt can be checked by reading the contents of the SSPBUF to determine if the address was device specific or a general call address.

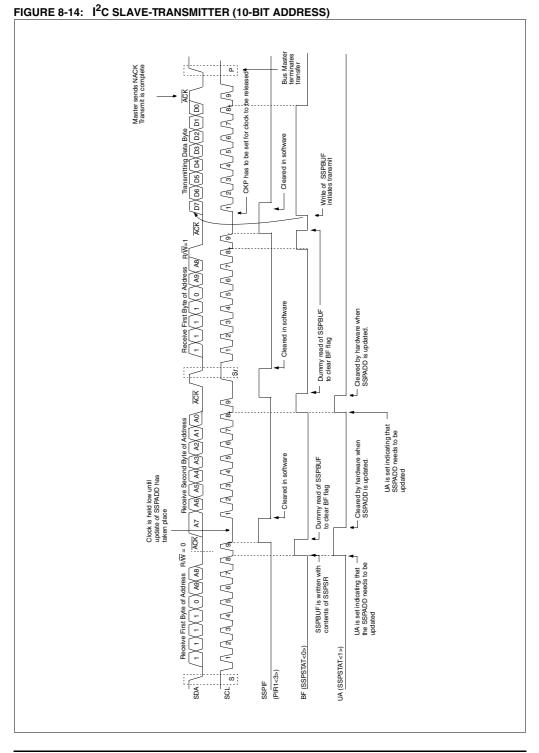

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match, and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when GCEN is set while the slave is configured in 10-bit address mode, then the second half of the address is not necessary, the UA bit will not be set, and the slave will begin receiving data after the acknowledge (Figure 8-16).

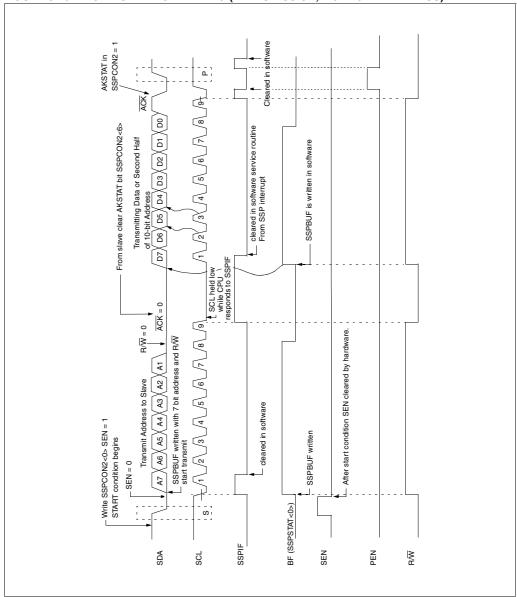

FIGURE 8-16: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE (7 OR 10-BIT MODE)

FIGURE 8-26: I<sup>2</sup>C MASTER MODE TIMING (TRANSMISSION, 7 OR 10-BIT ADDRESS)

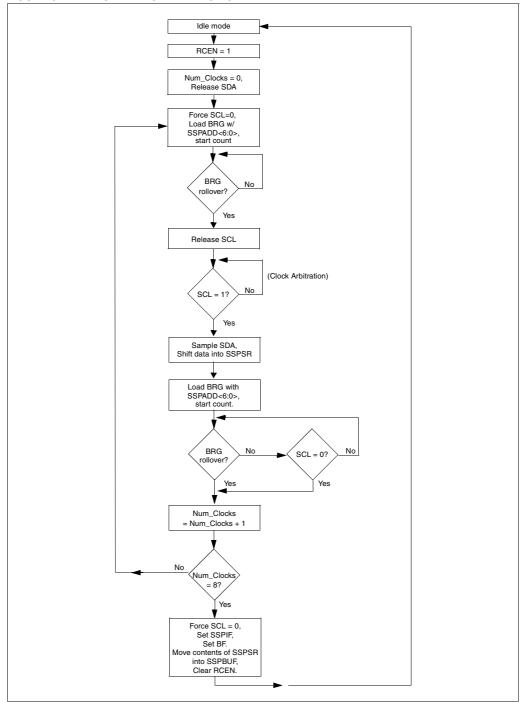

FIGURE 8-27: MASTER RECEIVER FLOWCHART

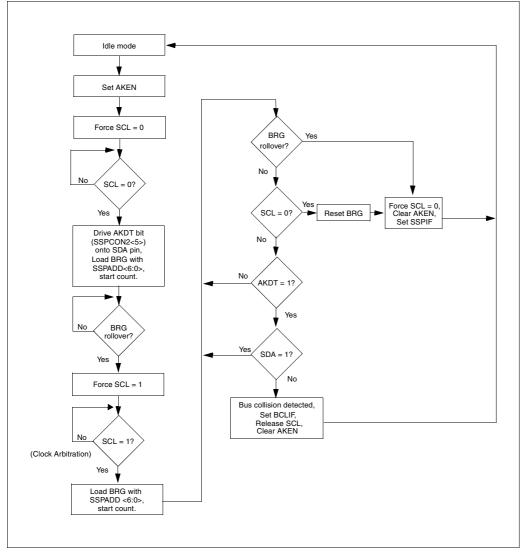

## FIGURE 8-30: ACKNOWLEDGE FLOWCHART

## 8.3 <u>Connection Considerations for I<sup>2</sup>C</u> Bus

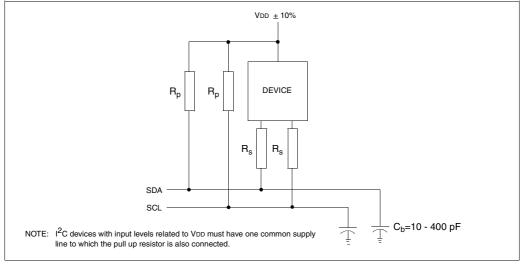

For standard-mode  $I^2C$  bus devices, the values of resistors  $\mathbf{R_p} \mathbf{R_s}$  in Figure 8-42 depends on the following parameters

- Supply voltage

- Bus capacitance

- Number of connected devices (input current + leakage current).

The supply voltage limits the minimum value of resistor  $R_p$  due to the specified minimum sink current of 3 mA at VoL max = 0.4V for the specified output stages. For

example, with a supply voltage of VDD =  $5V\pm10\%$  and VoL max = 0.4V at 3 mA, R<sub>p min</sub> = (5.5-0.4)/0.003 = 1.7 k\Omega. VDD as a function of **R**<sub>p</sub> is shown in Figure 8-42. The desired noise margin of 0.1VDD for the low level limits the maximum value of **R**<sub>s</sub>. Series resistors are optional and used to improve ESD susceptibility.

The bus capacitance is the total capacitance of wire, connections, and pins. This capacitance limits the maximum value of  $R_p$  due to the specified rise time (Figure 8-42).

The SMP bit is the slew rate control enabled bit. This bit is in the SSPSTAT register, and controls the slew rate of the I/O pins when in  $I^2C$  mode (master or slave).

## FIGURE 8-42: SAMPLE DEVICE CONFIGURATION FOR I<sup>2</sup>C BUS

# 9.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI). The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, Serial EEPROMs etc. The USART can be configured in the following modes:

- · Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>), and bits TRISC<7:6>, have to be set in order to configure pins RC6/TX/CK and RC7/ RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

The USART module also has a multi-processor communication capability using 9-bit address detection.

## FIGURE 9-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

| R/W-0<br>CSRC | R/W-0<br>TX9                                                | R/W-0<br>TXEN             | R/W-0<br>SYNC | U-0      | R/W-0<br>BRGH | R-1<br>TRMT | R/W-0<br>TX9D | R = Readable bit                                                                      |

|---------------|-------------------------------------------------------------|---------------------------|---------------|----------|---------------|-------------|---------------|---------------------------------------------------------------------------------------|

| bit7          | 173                                                         | TALN                      | 31110         |          | DROIT         |             | bitO          | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| oit 7:        | CSRC: Clo                                                   | ck Source                 | Select bit    |          |               |             |               |                                                                                       |

|               | Asynchrone<br>Don't care                                    | ous mode                  |               |          |               |             |               |                                                                                       |

|               | Synchrono<br>1 = Master<br>0 = Slave n                      | mode (Clo                 | •             |          |               | IG)         |               |                                                                                       |

| oit 6:        | <b>TX9</b> : 9-bit 1<br>1 = Selects<br>0 = Selects          | 9-bit trans               | smission      |          |               |             |               |                                                                                       |

| oit 5:        | <b>TXEN</b> : Tran<br>1 = Transm<br>0 = Transm<br>Note: SRE | it enabled<br>it disabled |               | EN in SY | NC mode.      |             |               |                                                                                       |

| oit 4:        | SYNC: USA<br>1 = Synchro<br>0 = Asynchro                    | onous mod                 | le            |          |               |             |               |                                                                                       |

| oit 3:        | Unimplem                                                    | ented: Rea                | ad as '0'     |          |               |             |               |                                                                                       |

| oit 2:        | BRGH: Hig                                                   | h Baud Ra                 | ate Select b  | it       |               |             |               |                                                                                       |

|               | Asynchrono<br>1 = High sp                                   | beed                      |               |          |               |             |               |                                                                                       |

|               | 0 = Low sp                                                  |                           |               |          |               |             |               |                                                                                       |

|               | Synchrono<br>Unused in t                                    |                           |               |          |               |             |               |                                                                                       |

| oit 1:        | <b>TRMT</b> : Tran<br>1 = TSR er<br>0 = TSR fu              | npty                      | Register St   | atus bit |               |             |               |                                                                                       |

| oit 0:        | <b>TX9D</b> : 9th                                           |                           |               |          |               |             |               |                                                                                       |

#### 9.1 **USART Baud Rate Generator (BRG)**

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In asynchronous mode bit BRGH (TXSTA<2>) also controls the baud rate. In synchronous mode bit BRGH is ignored. Table 9-1 shows the formula for computation of the baud rate for different USART modes which only apply in master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 9-1. From this, the error in baud rate can be determined.

Example 9-1 shows the calculation of the baud rate error for the following conditions:

> Fosc = 16 MHz Desired Baud Rate = 9600 BRGH = 0SYNC = 0

#### EXAMPLE 9-1: CALCULATING BAUD RATE ERROR

## Desired Baud rate = Fosc / (64 (X + 1))

| 9600           | =     | 16000000 /(64 (X + 1))       |

|----------------|-------|------------------------------|

| Х              | =     | L25.042」= 25                 |

| Calculated Bau | ıd Ra | ate=16000000 / (64 (25 + 1)) |

9615 =

(Calculated Baud Rate - Desired Baud Rate) Error = Desired Baud Rate

> (9615 - 9600) / 9600 -

0.16% -

It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. This is because the FOSC/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

9.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

#### TABLE 9-1 **BAUD RATE FORMULA**

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)     |

|------|-------------------------------------------|---------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate= Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = FOSC/(4(X+1))   | NA                        |

X = value in SPBRG (0 to 255)

#### **TABLE 9-2 REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR**

| Address | Name  | Bit 7  | Bit 6   | Bit 5     | Bit 4     | Bit 3 | Bit 2 | Bit 1 Bit 0 Value on<br>BOR |      |           | Value on all other resets |  |

|---------|-------|--------|---------|-----------|-----------|-------|-------|-----------------------------|------|-----------|---------------------------|--|

| 98h     | TXSTA | CSRC   | TX9     | TXEN      | SYNC      | _     | BRGH  | TRMT                        | TX9D | 0000 -010 | 0000 -010                 |  |

| 18h     | RCSTA | SPEN   | RX9     | SREN      | CREN      | ADDEN | FERR  | OERR                        | RX9D | 0000 000x | 0000 000x                 |  |

| 99h     | SPBRG | Baud R | ate Gei | 0000 0000 | 0000 0000 |       |       |                             |      |           |                           |  |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used by the BRG.

| BAUD<br>RATE | Fosc = 2 | 20 MHz<br>% | SPBRG<br>value |         | 0/    | SPBF<br>valu |      | 10 MHz  |       | %      | SPB<br>vali | SRG   | 7.15909 1 | ИНz<br>%  | SPBRG<br>value |       |           |

|--------------|----------|-------------|----------------|---------|-------|--------------|------|---------|-------|--------|-------------|-------|-----------|-----------|----------------|-------|-----------|

| (K)          | KBAUD    | ERROR       |                | ) KBAUD | ERRO  |              |      | KBAUD   |       |        | (deci       |       | KBAUD     | ERROR     | (decimal)      |       |           |

| 0.3          | NA       |             | -              | NA      | -     | -            |      | NA      |       | -      | -           |       | NA        |           | -              |       |           |

| 1.2          | NA       | -           | -              | NA      | -     | -            |      | NA      |       | -      | -           |       | NA        | -         | -              |       |           |

| 2.4          | NA       | -           | -              | NA      | -     | -            |      | NA      |       | -      | -           |       | NA        | -         | -              |       |           |

| 9.6          | NA       | -           | -              | NA      | -     | -            |      | 9.766   | +1    | .73    | 25          | 55    | 9.622     | +0.23     | 185            |       |           |

| 19.2         | 19.53    | +1.73       | 255            | 19.23   | +0.16 |              |      | 19.23   |       | .16    | 12          |       | 19.24     | +0.23     | 92             |       |           |

| 76.8         | 76.92    | +0.16       | 64             | 76.92   |       |              |      | 75.76   |       | .36    | 3           |       | 77.82     | +1.32     | 22             |       |           |

| 96           | 96.15    | +0.16       | 51             | 95.24   |       |              |      | 96.15   |       | .16    | 25          | -     | 94.20     | -1.88     | 18             |       |           |

| 300          | 294.1    | -1.96       | 16             | 307.69  |       |              |      | 312.5   |       | .17    | 7           |       | 298.3     | -0.57     | 5              |       |           |

| 500          | 500      | 0           | 9              | 500     | 0     | 7            |      | 500     |       | 0      | 4           |       | NA        | -         | -              |       |           |

| HIGH         | 5000     | -           | 0              | 4000    | -     | 0            |      | 2500    |       | -      | 0           |       | 1789.8    | -         | 0              |       |           |

| LOW          | 19.53    | -           | 255            | 15.625  | -     | 255          | 5    | 9.766   |       | -      | 25          | 55    | 6.991     | -         | 255            |       |           |

|              | Fosc =   | 5.0688 MH   | ۱z ،           | 4 MHz   |       |              | 3.57 | '9545 M | Hz    |        | 1           | MHz   |           |           | 32.768 k       | Hz    |           |

| BAUD         |          |             | SPBRG          |         |       | SPBRG        |      |         |       | SPBF   | RG          |       |           | SPBR      | à              |       | SPBRG     |

| RATE         | KBAUD    | %           |                | KBAUD   | %     | value        |      | AUD     | %     | valu   |             | KBAU  |           | value     | KBAUD          | %     | value     |

| (K)          |          | ERROR       | (decimal)      |         | ERROR | decimal)     |      | E       | RROR  | (decin | nal)        |       | ERRC      | R (decima | u)             | ERROR | (decimal) |

| 0.3          | NA       | -           | -              | NA      | -     | -            | Ν    | JA      | -     | -      |             | NA    | -         | -         | 0.303          | +1.14 | 26        |

| 1.2          | NA       | -           | -              | NA      | -     | -            | Ν    | A       | -     | -      |             | 1.20  | 2 +0.1    | 5 207     | 1.170          | -2.48 | 6         |

| 2.4          | NA       | -           | -              | NA      | -     | -            | Ν    | A       | -     | -      |             | 2.40  | 4 +0.1    | 5 103     | NA             | -     | -         |

| 9.6          | 9.6      | 0           | 131            | 9.615   | +0.16 | 103          | 9.   | 622 -   | +0.23 | 92     |             | 9.61  | 5 +0.1    | 6 25      | NA             | -     | -         |

| 19.2         | 19.2     | 0           | 65             | 19.231  | +0.16 | 51           |      |         | 0.83  | 46     |             | 19.24 |           |           | NA             | -     | -         |

| 76.8         | 79.2     | +3.13       | 15             | 76.923  | +0.16 | 12           |      |         | 2.90  | 11     |             | 83.3  | 4 +8.5    | 12        | NA             | -     | -         |

| 96           | 97.48    | +1.54       | 12             | 1000    | +4.17 | 9            |      |         | +3.57 | 8      | 1           | NA    | -         | -         | NA             | -     | -         |

| 300          | 316.8    | +5.60       | 3              | NA      | -     | -            |      |         | 0.57  | 2      |             | NA    | -         | -         | NA             | -     | -         |

| 500          | NA       | -           | -              | NA      | -     | -            |      | JA      | -     | -      |             | NA    | -         | -         | NA             | -     | -         |

| HIGH         | 1267     | -           | 0              | 100     | -     | 0            |      | 4.9     | -     | 0      | 1           | 250   |           | 0         | 8.192          | -     | 0         |

| LOW          | 4.950    | -           | 255            | 3.906   | -     | 255          | 3.   | 496     | -     | 255    | 5           | 0.976 | 6 -       | 255       | 0.032          | -     | 255       |

# TABLE 9-4 BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD        | Fosc = 2 |            | SPBRG             | 16 MHz |                | SPBF             | RG    | 0 MHz   |           |       | PBRG    | 7.15909 M |            | SPBRG              |        |       |

|-------------|----------|------------|-------------------|--------|----------------|------------------|-------|---------|-----------|-------|---------|-----------|------------|--------------------|--------|-------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal | KBAUE  | %<br>ERRO      | valu<br>R (decim |       | KBAUD   | %<br>ERRC |       | alue    | KBAUD     | %<br>ERROR | value<br>(decimal) |        |       |

|             | -        | Ennon      | (uconnui)         |        |                | i (ucom          |       |         |           |       | connun) |           | Ennon      | (aconnai)          |        |       |

| 0.3         | NA       | -          | -                 | NA     | -              | -                |       | NA      | -         |       | -       | NA        | -          | -                  |        |       |

| 1.2         | 1.221    | +1.73      | 255               | 1.202  |                |                  |       | 1.202   | +0.1      |       | 129     | 1.203     | +0.23      | 92                 |        |       |

| 2.4         | 2.404    | +0.16      | 129               | 2.404  |                |                  | ;     | 2.404   | +0.1      |       | 64      | 2.380     | -0.83      | 46                 |        |       |

| 9.6         | 9.469    | -1.36      | 32                | 9.615  | +0.16          |                  |       | 9.766   | +1.7      |       | 15      | 9.322     | -2.90      | 11                 |        |       |

| 19.2        | 19.53    | +1.73      | 15                | 19.23  | +0.16          |                  |       | 19.53   | +1.7      |       | 7       | 18.64     | -2.90      | 5                  |        |       |

| 76.8        | 78.13    | +1.73      | 3                 | 83.33  | +8.51          | 2                |       | 78.13   | +1.7      | 3     | 1       | NA        | -          | -                  |        |       |

| 96          | 104.2    | +8.51      | 2                 | NA     | -              | -                |       | NA      | -         |       | -       | NA        | -          | -                  |        |       |

| 300         | 312.5    | +4.17      | 0                 | NA     | -              | -                |       | NA      | -         |       | -       | NA        | -          | -                  |        |       |

| 500         | NA       | -          | -                 | NA     | -              | -                |       | NA      | -         |       | -       | NA        | -          | -                  |        |       |

| HIGH        | 312.5    | -          | 0                 | 250    | -              | 0                |       | 156.3   | -         |       | 0       | 111.9     | -          | 0                  |        |       |

| LOW         | 1.221    | -          | 255               | 0.977  | -              | 255              | ;     | 0.6104  | -         | :     | 255     | 0.437     | -          | 255                |        |       |

|             | Fosc = ! | 5.0688 MH  | lz 4              | 1 MHz  |                |                  | 3.579 | 9545 MH | z         |       | 1 MHz   |           |            | 32.768 k           | Hz     |       |

| BAUD        |          |            | SPBRG             |        |                | SPBRG            |       |         |           | SPBRG |         |           | SPBRG      |                    |        | SPBRG |

| BAUD        |          | %          | value             |        | %              | value            |       | 0       |           | value |         | %         | value      |                    | %      | value |

| (K)         | KBAUD    |            | (decimal)         | KBAUD  |                |                  | ква   |         |           |       | KBAU    |           |            | ) KBAUD            |        |       |

|             | 0.31     | +3.13      | , ,               | 0.3005 | -0.17          | 207              | 0.30  |         |           | 185   | 0.300   |           | 51         | 0.256              |        |       |

| 0.3<br>1.2  | 1.2      | +3.13      | 255<br>65         | 1.202  | -0.17<br>+1.67 | 207<br>51        | 1.19  |         | .23<br>83 | 46    | 1.202   |           | 12         | 0.256<br>NA        | -14.67 | 1     |

|             |          |            |                   |        |                | -                |       |         |           |       |         |           |            |                    | -      | -     |

| 2.4         | 2.4      | 0          | 32                | 2.404  | +1.67          | 25               | 2.43  |         |           | 22    | 2.232   |           | 6          | NA                 | -      | -     |

| 9.6         | 9.9      | +3.13      | 7                 | NA     | -              | -                | 9.32  |         | 90        | 5     | NA      | -         | -          | NA                 | -      | -     |

| 19.2        | 19.8     | +3.13      | 3                 | NA     | -              | -                | 18.6  |         | 90        | 2     | NA      | -         | -          | NA                 | -      | -     |

| 76.8        | 79.2     | +3.13      | 0                 | NA     | -              | -                | NA    |         | -         | -     | NA      | -         | -          | NA                 | -      | -     |

| 96          | NA       | -          | -                 | NA     | -              | -                | NA    |         | -         | -     | NA      | -         | -          | NA                 | -      | -     |

| 300         | NA       | -          | -                 | NA     | -              | -                | NA    |         | -         | -     | NA      | -         | -          | NA                 | -      | -     |

| 500         | NA       | -          | -                 | NA     | -              | -                | NA    |         | -         | -     | NA      | -         | -          | NA                 | -      | -     |

| HIGH        | 79.2     | -          |                   | 62.500 | -              | 0                | 55.9  |         | -         | 0     | 15.63   |           | 0          | 0.512              | -      | 0     |

| LOW         | 0.3094   | -          | 255               | 3.906  | -              | 255              | 0.21  | 85      | -         | 255   | 0.061   | 0 -       | 255        | 0.0020             | -      | 255   |

## 11.10 A/D Operation During Sleep

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be configured for RC (ADCS1:ADCS0 = 11b). With the RC clock source selected, when the GO/DONE bit is set the A/D module waits one instruction cycle before starting the conversion cycle. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise during the sample and conversion. When the conversion cycle is completed the GO/DONE bit is cleared, and the result loaded into the ADRESH and ADRESL registers. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction causes the present conversion to be aborted and the A/D module is turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

| Note: | For the A/D module to operate in SLEEP,    |

|-------|--------------------------------------------|

|       | the A/D clock source must be configured to |

|       | RC (ADCS1:ADCS0 = $11b$ ).                 |

## 11.11 Connection Considerations

Since the analog inputs employ ESD protection, they have diodes to VDD and Vss. This requires that the analog input must be between VDD and Vss. If the input voltage exceeds this range by greater than 0.3V (either direction), one of the diodes becomes forward biased and it may damage the device if the input current specification is exceeded.

An external RC filter is sometimes added for anti-aliasing of the input signal. The R component should be selected to ensure that the total source impedance is kept under the 2.5 k $\Omega$  recommended specification. Any external components connected (via hi-impedance) to an analog input pin (capacitor, zener diode, etc.) should have very little leakage current at the pin.

| Address               | Name   | Bit 7                | Bit 6       | Bit 5                 | Bit 4                         | Bit 3     | Bit 2          | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on all other Resets |

|-----------------------|--------|----------------------|-------------|-----------------------|-------------------------------|-----------|----------------|---------------|-----------|--------------------------|---------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE        | TOIE                  | INTE                          | RBIE      | TOIF           | INTF          | RBIF      | 0000 000x                | 0000 000u                 |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF        | RCIF                  | TXIF                          | SSPIF     | CCP1IF         | TMR2IF        | TMR1IF    | 0000 0000                | 0000 0000                 |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE        | RCIE                  | TXIE                          | SSPIE     | CCP1IE         | TMR2IE        | TMR1IE    | 0000 0000                | 0000 0000                 |

| 1Eh                   | ADRESH | A/D High B           | yte Result  | Register              |                               |           |                |               |           | xxxx xxxx                | uuuu uuuu                 |

| 9Eh                   | ADRESL | A/D Low By           | /te Result  | Register              |                               |           |                |               |           | xxxx xxxx                | uuuu uuuu                 |

| 9Bh                   | REFCON | VRHEN                | VRLEN       | VRHOEN                | VRLOEN                        | _         | _              | _             | _         | 0000                     | 0000                      |

| 1Fh                   | ADCON0 | ADCS1                | ADCS0       | CHS2                  | CHS1                          | CHS0      | GO/DONE        | CHS3          | ADON      | 0000 0000                | 0000 0000                 |

| 9Fh                   | ADCON1 | ADFM                 | VCFG2       | VCFG1                 | VCFG0                         | PCFG3     | PCFG2          | PCFG1         | PCFG0     | 0000 0000                | 0000 0000                 |

| 05h                   | PORTA  | _                    | -           | PORTA5 <sup>(2)</sup> | PORTA Data                    | Latch whe | n written: POR | TA<4:0> pins  | when read | 0x 0000                  | 0u 0000                   |

| 06h                   | PORTB  | PORTB Da             | ta Latch w  | hen written: I        | PORTB pins when read          |           |                |               | xxxx 11xx | uuuu 11uu                |                           |

| 09h <sup>(2)</sup>    | PORTE  | —                    |             | -                     | -                             | —         | RE2            | RE1           | RE0       | 000                      | 000                       |

| 85h                   | TRISA  | _                    | -           | bit5 <sup>(2)</sup>   | PORTA Data Direction Register |           |                |               | 11 1111   | 11 1111                  |                           |

| 86h                   | TRISB  | PORTB Da             | ta Directio | n Register            | L                             |           |                |               | 1111 1111 | 1111 1111                |                           |

| 89h <sup>(2)</sup>    | TRISE  | IBF                  | OBF         | IBOV                  | PSPMODE                       | _         | PORTE Data     | Direction Bit | 0000 -111 | 0000 -111                |                           |

## TABLE 11-3 SUMMARY OF A/D REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

2: These bits/registers are not implemented on the 28-pin devices, read as '0'.

#### 12.10 Interrupts

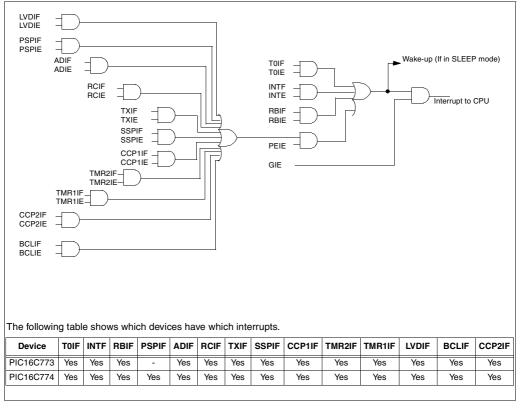

The PIC16C77X family has up to 14 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit

## FIGURE 12-11: INTERRUPT LOGIC

## 12.13 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  ${\tt SLEEP}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{\text{PD}}$  bit (STATUS<3>) is cleared, the  $\overline{\text{TO}}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD, or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D, disable external clocks. Pull all I/O pins, that are hi-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 12.13.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some Peripheral Interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. PSP read or write.

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. CCP capture mode interrupt.

- 4. Special event trigger (Timer1 in asynchronous mode using an external clock).

- 5. SSP (Start/Stop) bit detect interrupt.

- 6. SSP transmit or receive in slave mode (SPI/I<sup>2</sup>C).

- 7. USART RX or TX (synchronous slave mode).

- 8. A/D conversion (when A/D clock source is RC).

- 9. Low-voltage detect.

Other peripherals cannot generate interrupts since during SLEEP, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the substruction after the substruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 12.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

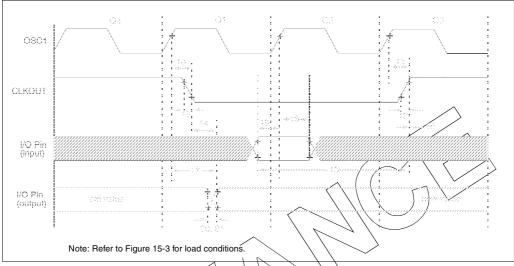

## FIGURE 15-5: CLKOUT AND I/O TIMING

| Parameter<br>No. | Sym       | Characteristic                          |                     | Min          | Тур† | Max         | Units  | Conditions |

|------------------|-----------|-----------------------------------------|---------------------|--------------|------|-------------|--------|------------|

| 10*              | TosH2ckL  | OSCIT to CLKQUT                         |                     |              | 75   | 200         | ns     | Note 1     |

| 11*              | TosH2ckH  | OSCIT to CLKOUT                         |                     | -            | 75   | 200         | ns     | Note 1     |

| 12*              | TckR      | QLKOUT rise time                        | $\checkmark$        | _            | 35   | 100         | ns     | Note 1     |

| 13*              | TCKF      | CLKOUT fall time                        |                     | _            | 35   | 100         | ns     | Note 1     |

| 14*              | Tck42ioV  | CLKOUT Ato Port out valio               | 1                   |              | _    | 0.5TCY + 20 | ns     | Note 1     |

| 15*              | TioV2ckH> | Port in valid before CLKOU              | Т↑                  | 0.25Tcy + 25 |      |             | ns     | Note 1     |

| 16*              | TekH2iol  | Port in hold after CLKOUT               | 0                   | _            |      | ns          | Note 1 |            |

| 17*              | To\$H2ioV | OSC1↑ (Q1 cycle) to<br>Port out valid   | _                   | 50           | 150  | ns          |        |            |

| 18*              | TosH2iol  | OSC1↑ (Q2 cycle) to                     | PIC16 <b>C</b> 77X  | 100          | _    | -           | ns     |            |

|                  |           | Port input invalid (I/O in hold time)   | PIC16 <b>LC</b> 77X | 200          |      | _           | ns     |            |

| 19*              | TioV2osH  | Port input valid to OSC1 <sup>↑</sup> ( | I/O in setup time)  | 0            |      | -           | ns     |            |

| 20*              | TioR      | Port output rise time                   | PIC16 <b>C</b> 77X  | _            | 10   | 25          | ns     |            |

|                  |           |                                         | PIC16 <b>LC</b> 77X | _            |      | 60          | ns     |            |

| 21*              | TioF      | Port output fall time                   | PIC16 <b>C</b> 77X  | _            | 10   | 25          | ns     |            |

|                  |           |                                         | PIC16 <b>LC</b> 77X | _            | _    | 60          | ns     |            |

| 22††*            | Tinp      | INT pin high or low time                |                     | Тсү          | —    | _           | ns     |            |

| 23††*            | Trbp      | RB7:RB4 change INT high                 | or low time         | Тсү          |      | _           | ns     |            |

#### **TABLE 15-6 CLKOUT AND I/O TIMING REQUIREMENTS**

These parameters are characterized but not tested.

t Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

these parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

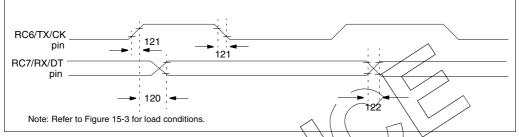

## FIGURE 15-14: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

## TABLE 15-15 USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                   |                         | Min_ | Typt | Max | Units | Conditions |

|--------------|----------|----------------------------------|-------------------------|------|------|-----|-------|------------|

| 120*         | TckH2dtV | SYNC XMIT (MASTER & SLAVE)       | PIC16C7Z4/773           | _    | _    | 80  | ns    |            |

|              |          | Clock high to data out valid     | PIC16LC774/773          | —    | —    | 100 | ns    |            |

| 121*         | Tckrf    |                                  | PIC16C774/773           | _    | —    | 45  | ns    |            |

|              |          | (Master Mode)                    | PIC16LC774/773          | —    | —    | 50  | ns    |            |

| 122*         | Tdtrf    | Data out rise time and fall time | PIC16 <b>C</b> 774/773  | —    | —    | 45  | ns    |            |

|              |          |                                  | PIC16 <b>LC</b> 774/773 |      | —    | 50  | ns    |            |

\* These parameters are characterized but not tested.

+: Data in "Typ" column is at \$V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

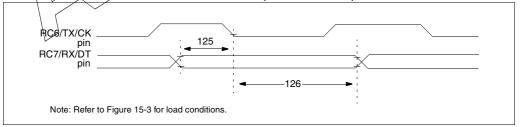

## FIGURE 15-15: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

## TABLE 15-16 USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                 | Min | Тур† | Max | Units    | Conditions |

|------------------|----------|--------------------------------------------------------------------------------|-----|------|-----|----------|------------|

| 125*             | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data setup before $CK \downarrow$ (DT setup time) | 15  |      |     |          |            |

| 126*             | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                 | 15  | _    |     | ns<br>ns |            |

\* These parameters are characterized but not tested.

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# w

| W Register                                    |

|-----------------------------------------------|

| Wake-up from SLEEP 127, 140                   |

| Interrupts 133, 134                           |

| MCLR Reset134                                 |

| Timing Diagram141                             |

| WDT Reset134                                  |

| Watchdog Timer (WDT) 127, 139                 |

| Block Diagram139                              |

| Enable (WDTE Bit)139                          |

| Programming Considerations139                 |

| RC Oscillator139                              |

| Time-out Period139                            |

| WDT Reset, Normal Operation 131, 133, 134     |

| WDT Reset, SLEEP 133, 134                     |

| Waveform for General Call Address Sequence 69 |

| WCOL                                          |

| WCOL Status Flag74                            |

| Write Collision Detect bit, WCOL55            |

| WWW, On-Line Support4                         |