Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | ·                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                             |

| Data Converters            | A/D 10x12b                                                              |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc774t-l |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16C77X

NOTES:

#### 2.2.2.2 OPTION\_REG REGISTER

The OPTION\_REG register is a readable and writable register which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0, and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

## FIGURE 2-4: OPTION\_REG REGISTER (ADDRESS 81h, 181h)

| RBPU     | INTEDG                   | TOCS          | TOSE       | PSA        | PS2           | PS1        | PS0  | R = Readable bit                           |

|----------|--------------------------|---------------|------------|------------|---------------|------------|------|--------------------------------------------|

| t7       |                          |               |            | 1.0/1      | . 02          |            | bit0 | W = Writable bit                           |

|          |                          |               |            |            |               |            | 5.10 | U = Unimplemented bit,                     |

|          |                          |               |            |            |               |            |      | read as '0'                                |

|          |                          |               |            |            |               |            |      | <ul> <li>n = Value at POR reset</li> </ul> |

| oit 7:   | RBPU: PC                 | RTB Pull-     | up Enabl   | e bit      |               |            |      |                                            |

|          | 1 = PORTI                | B pull-ups    | are disal  | oled       |               |            |      |                                            |

|          | 0 = PORTI                | B pull-ups    | are enab   | led by inc | lividual port | latch valu | es   |                                            |

| oit 6:   |                          | · ·           |            |            | ·             |            |      |                                            |

| л о.     | INTEDG: I<br>1 = Interru |               |            |            | nin           |            |      |                                            |

|          |                          |               |            |            |               |            |      |                                            |

|          | 0 = Interru              | pt on tailing | g eage o   | TRB0/IN    | pin           |            |      |                                            |

| oit 5:   | TOCS: TM                 | R0 Clock S    | Source S   | elect bit  |               |            |      |                                            |

|          | 1 = Transit              | ion on RA4    | 4/T0CKI    | pin        |               |            |      |                                            |

|          | 0 = Interna              | al instructio | on cycle o | clock (CLł | (OUT)         |            |      |                                            |

| oit 4:   | TOSE: TM                 | R0 Source     | Edge Se    | elect bit  |               |            |      |                                            |

|          |                          |               |            |            | on RA4/T0     | CKI pin    |      |                                            |

|          |                          |               |            |            | on RA4/T0     |            |      |                                            |

| bit 3:   | PSA: Pres                |               | 0          |            |               |            |      |                                            |

| JIL 3.   | 1 = Presca               |               |            |            |               |            |      |                                            |

|          | 0 = Presca               |               | ,          |            | modulo        |            |      |                                            |

|          |                          |               |            |            | module        |            |      |                                            |

| oit 2-0: | PS2:PS0:                 | Prescaler     | Rate Sel   | ect bits   |               |            |      |                                            |

|          | Bit Value                | TMR0 Ra       | te WD      | r Rate     |               |            |      |                                            |

|          | 000                      | 1:2           | 1 :        | 1          |               |            |      |                                            |

|          | 001                      | 1:4           | 1 :        |            |               |            |      |                                            |

|          | 010                      | 1:8           | 1:         |            |               |            |      |                                            |

|          | 011                      | 1:16          | 1:         |            |               |            |      |                                            |

|          | 100                      | 1:32          |            | 16         |               |            |      |                                            |

|          | 101<br>110               | 1:64          |            | 32<br>64   |               |            |      |                                            |

|          | TTO                      | 1:128         | · .        | 64<br>128  |               |            |      |                                            |

|          | 111                      |               |            |            |               |            |      |                                            |

## 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISB bit (=0) will make the corresponding PORTB pin an output, i.e., put the contents of the output latch on the selected pin.

#### EXAMPLE 3-1: INITIALIZING PORTB

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| CLRF  | PORTB   |     | ; | Initialize PORTB by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISB   |     | ; | Set RB<3:0> as inputs |

|       |         |     | ; | RB<5:4> as outputs    |

|       |         |     | ; | RB<7:6> as inputs     |

|       |         |     |   |                       |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overrightarrow{\text{RBPU}}$  (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

The RB0 pin is multiplexed with the external interrupt (RB0/INT).

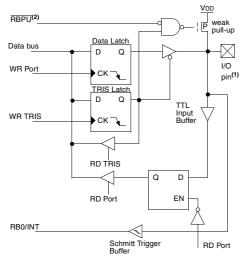

## FIGURE 3-4: BLOCK DIAGRAM OF RB0 PIN

Note 1: I/O pins have diode protection to VDD and VSS. 2: To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (OPTION\_REG<7>).

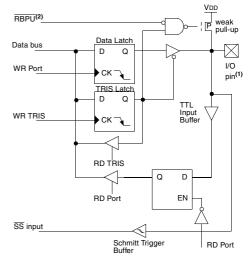

The RB1 pin is multiplexed with the SSP module slave select (RB1/SS).

#### FIGURE 3-5: BLOCK DIAGRAM OF RB1/SS PIN

Note 1: I/O pins have diode protection to VDD and Vss. 2: To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (OPTION\_REG<7>).

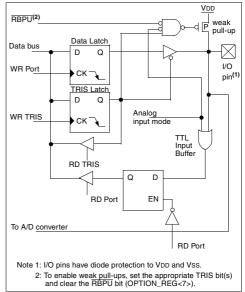

The RB2 pin is multiplexed with analog channel 8 (RB2/AN8).

#### FIGURE 3-6: BLOCK DIAGRAM OF RB2/AN8 PIN

## 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (=1) will make the corresponding PORTC pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISC bit (=0) will make the corresponding PORTC pin an output, i.e., put the contents of the output latch on the selected pin.

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

## EXAMPLE 3-1: INITIALIZING PORTC

| BCF<br>CLRF | STATUS,<br>PORTC | RPO | ;; | Select Bank 0<br>Initialize PORTC by<br>clearing output |

|-------------|------------------|-----|----|---------------------------------------------------------|

|             |                  |     | ;  | data latches                                            |

| BSF         | STATUS,          | RP0 | ;  | Select Bank 1                                           |

| MOVLW       | 0xCF             |     | ;  | Value used to                                           |

|             |                  |     | ;  | initialize data                                         |

|             |                  |     | ;  | direction                                               |

| MOVWF       | TRISC            |     | ;  | Set RC<3:0> as inputs                                   |

|             |                  |     | ;  | RC<5:4> as outputs                                      |

|             |                  |     | ;  | RC<7:6> as inputs                                       |

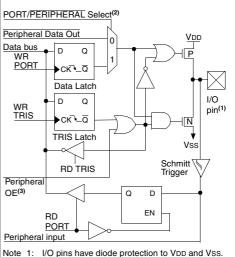

## FIGURE 3-9: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

- Port/Peripheral select signal selects between port data and peripheral output.

- 3: Peripheral OE (output enable) is only activated if peripheral select is active.

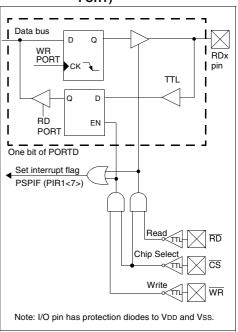

## 3.6 Parallel Slave Port

The Parallel Slave Port is implemented on the 40/44-pin devices only.

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port when control bit PSPMODE (TRISE<4>) is set. In slave mode it is asynchronously readable and writable by the external world through  $\overline{\text{RD}}$  control input pin RE0/ $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  control input pin RE1/ $\overline{\text{WR}}$ .

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD to be the RD input, RE1/WR to be the WR input and RE2/CS to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The configuration bits, PCFG3:PCFG0 (ADCON1<3:0>) must be configured to make pins RE2:RE0 as digital I/O.

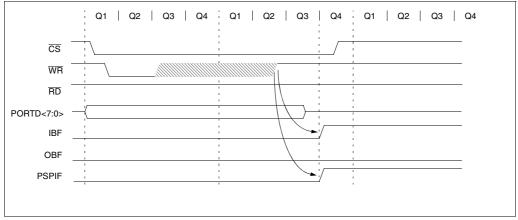

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low. A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low.

#### FIGURE 3-13: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

## FIGURE 3-14: PARALLEL SLAVE PORT WRITE WAVEFORMS

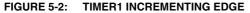

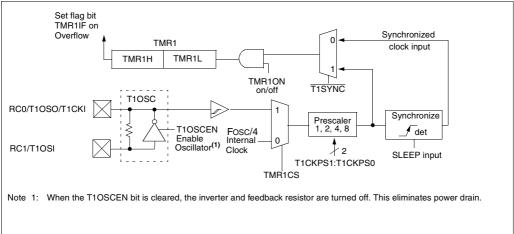

#### 5.1.1 TIMER1 COUNTER OPERATION

In this mode, Timer1 is being incremented via an external source. Increments occur on a rising edge. After Timer1 is enabled in counter mode, the module must first have a falling edge before the counter begins to increment.

## 7.0 CAPTURE/COMPARE/PWM (CCP) MODULE(S)

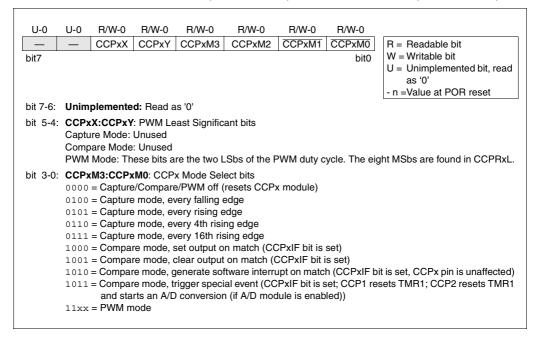

Each CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave Duty Cycle register. Table 7-1 shows the timer resources of the CCP module modes.

The operation of CCP1 is identical to that of CCP2, with the exception of the special trigger. Therefore, operation of a CCP module in the following sections is described with respect to CCP1.

Table 7-2 shows the interaction of the CCP modules.

## CCP1 Module

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

## CCP2 Module

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. All are readable and writable.

Additional information on the CCP module is available in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

## TABLE 7-1 CCP MODE - TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

| CCPx Mode | CCPy Mode | Interaction                                                                           |

|-----------|-----------|---------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base.                                                                  |

| Capture   | Compare   | The compare should be configured for the special event trigger, which clears TMR1.    |

| Compare   | Compare   | The compare(s) should be configured for the special event trigger, which clears TMR1. |

| PWM       | PWM       | The PWMs will have the same frequency, and update rate (TMR2 interrupt).              |

| PWM       | Capture   | None                                                                                  |

| PWM       | Compare   | None                                                                                  |

## TABLE 7-2 INTERACTION OF TWO CCP MODULES

## FIGURE 7-1: CCP1CON REGISTER (ADDRESS 17h) / CCP2CON REGISTER (ADDRESS 1Dh)

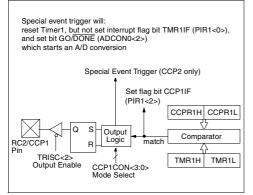

## 7.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- driven High

- driven Low

- remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

## FIGURE 7-3: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 7.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force       |

|-------|------------------------------------------------|

|       | the RC2/CCP1 compare output latch to the       |

|       | default low level. This is not the data latch. |

#### 7.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 7.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 7.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special trigger output of CCP2 resets the TMR1 register pair, and starts an A/D conversion (if the A/D module is enabled).

Note: The special event trigger from the CCP2 module will not set interrupt flag bit TMR1IF (PIR1<0>).

## TABLE 7-3 REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address               | Name    | Bit 7                | Bit 6     | Bit 5        | Bit 4       | Bit 3         | Bit 2      | Bit 1      | Bit 0  | PC   | e on:<br>)R,<br>)R | allo | e on<br>other<br>sets |

|-----------------------|---------|----------------------|-----------|--------------|-------------|---------------|------------|------------|--------|------|--------------------|------|-----------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE      | TOIE         | INTE        | RBIE          | TOIF       | INTF       | RBIF   | 0000 | 000x               | 0000 | 000u                  |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup> | ADIF      | RCIF         | TXIF        | SSPIF         | CCP1IF     | TMR2IF     | TMR1IF | 0000 | 0000               | 0000 | 0000                  |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup> | ADIE      | RCIE         | TXIE        | SSPIE         | CCP1IE     | TMR2IE     | TMR1IE | 0000 | 0000               | 0000 | 0000                  |

| 87h                   | TRISC   | PORTC Da             | ata Dire  | ction Regis  | ster        |               |            |            |        | 1111 | 1111               | 1111 | 1111                  |

| 0Eh                   | TMR1L   | Holding reg          | gister fo | or the Least | Significant | Byte of the   | 16-bit TMF | 1 register |        | xxxx | xxxx               | uuuu | uuuu                  |

| 0Fh                   | TMR1H   | Holding reg          | gister fo | or the Most  | Significant | Byte of the 1 | 6-bit TMR  | 1register  |        | xxxx | xxxx               | uuuu | uuuu                  |

| 10h                   | T1CON   | —                    | _         | T1CKPS1      | T1CKPS0     | T1OSCEN       | T1SYNC     | TMR1CS     | TMR1ON | 00   | 0000               | uu   | uuuu                  |

| 15h                   | CCPR1L  | Capture/Co           | ompare    | PWM regi     | ster1 (LSB) |               |            |            |        | xxxx | xxxx               | uuuu | uuuu                  |

| 16h                   | CCPR1H  | Capture/Co           | ompare    | PWM regi     | ster1 (MSB) | )             |            |            |        | xxxx | xxxx               | uuuu | uuuu                  |

| 17h                   | CCP1CON | —                    |           | CCP1X        | CCP1Y       | CCP1M3        | CCP1M2     | CCP1M1     | CCP1M0 | 00   | 0000               | 00   | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin, always maintain these bits clear.

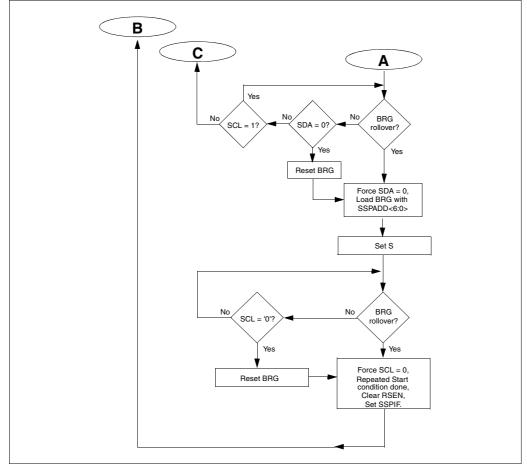

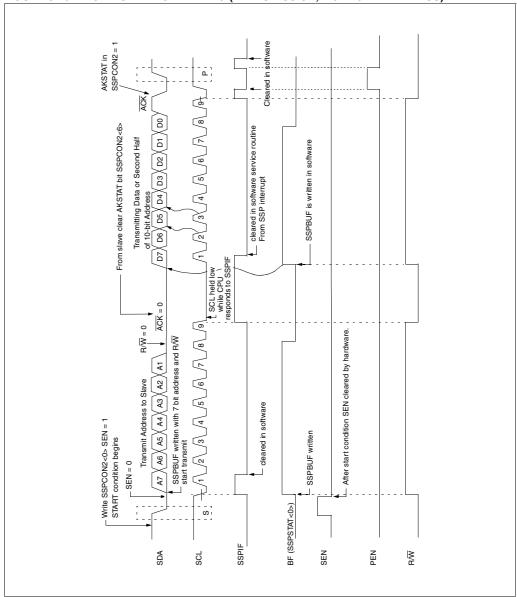

FIGURE 8-26: I<sup>2</sup>C MASTER MODE TIMING (TRANSMISSION, 7 OR 10-BIT ADDRESS)

## 8.2.12 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the receive enable bit, RCEN (SSPCON2<3>).

| Note: | The SSP Module must be in an IDLE        |

|-------|------------------------------------------|

|       | STATE before the RCEN bit is set, or the |

|       | RCEN bit will be disregarded.            |

The baud rate generator begins counting, and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag is set, the SSPIF is set, and the baud rate generator is suspended from counting, holding SCL low. The SSP is now in IDLE state, awaiting the next command. When the buffer is read by the CPU, the BF flag is automatically cleared. The user can then send an acknowledge bit at the end of reception, by setting the acknowledge sequence enable bit, AKEN (SSPCON2<4>).

#### 8.2.12.10 BF STATUS FLAG

In receive operation, BF is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when SSPBUF is read.

#### 8.2.12.11 SSPOV STATUS FLAG

In receive operation, SSPOV is set when 8 bits are received into the SSPSR, and the BF flag is already set from a previous reception.

#### 8.2.12.12 WCOL STATUS FLAG

If the user writes the SSPBUF when a receive is already in progress (i.e. SSPSR is still shifting in a data byte), then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

| 1) |

|----|

| 1  |

| BAUD<br>RATE<br>(K)                                        | Fosc = 2<br>KBAUD                                     | 0 MHz<br>%<br>ERROR                                 | SPBRG<br>value<br>(decimal)                            | 16 MHz<br>KBAUD                                        | %<br>ERROF                       | SPBRG<br>value<br>decimal                               |                                                                    | %                                                       | b Va                                          | PBRG<br>alue<br>cimal)                           | 7.16 MHz<br>KBAUD E                                                                       | %                                             | SPBRG<br>value<br>decimal)                  |                                               |                                                  |

|------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|----------------------------------|---------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------|-----------------------------------------------|--------------------------------------------------|

| 9.6                                                        | 9.615                                                 | +0.16                                               | 129                                                    | 9.615                                                  | +0.16                            | 103                                                     | 9.615                                                              | 5 +0.                                                   | 16                                            | 64                                               | 9.520                                                                                     | -0.83                                         | 46                                          |                                               |                                                  |

| 19.2                                                       | 19.230                                                | +0.16                                               | 64                                                     | 19.230                                                 | +0.16                            | 51                                                      | 18.93                                                              | 9 -1.3                                                  | 36                                            | 32                                               | 19.454                                                                                    | +1.32                                         | 22                                          |                                               |                                                  |

| 38.4                                                       | 37.878                                                | -1.36                                               | 32                                                     | 38.461                                                 | +0.16                            | 25                                                      | 39.06                                                              | 2 +1                                                    | .7                                            | 15                                               | 37.286                                                                                    | -2.90                                         | 11                                          |                                               |                                                  |

| 57.6                                                       | 56.818                                                | -1.36                                               | 21                                                     | 58.823                                                 | +2.12                            | 16                                                      | 56.81                                                              | 8 -1.3                                                  | 36                                            | 10                                               | 55.930                                                                                    | -2.90                                         | 7                                           |                                               |                                                  |

| 115.2                                                      | 113.636                                               | -1.36                                               | 10                                                     | 111.111                                                | -3.55                            | 8                                                       | 125                                                                | +8.                                                     | 51                                            | 4                                                | 111.860                                                                                   | -2.90                                         | 3                                           |                                               |                                                  |

| 250                                                        | 250                                                   | 0                                                   | 4                                                      | 250                                                    | 0                                | 3                                                       | NA                                                                 | -                                                       |                                               | -                                                | NA                                                                                        | -                                             | -                                           |                                               |                                                  |

| 625                                                        | 625                                                   | 0                                                   | 1                                                      | NA                                                     | -                                | -                                                       | 625                                                                | 0                                                       |                                               | 0                                                | NA                                                                                        | -                                             | -                                           |                                               |                                                  |

| 1250                                                       | 1250                                                  | 0                                                   | 0                                                      | NA                                                     | -                                | -                                                       | NA                                                                 | -                                                       |                                               | -                                                | NA                                                                                        | -                                             | -                                           |                                               |                                                  |

| DALID                                                      | Fosc = 5                                              | 000 1411-                                           |                                                        |                                                        |                                  |                                                         |                                                                    |                                                         |                                               |                                                  |                                                                                           |                                               |                                             |                                               |                                                  |

| BAUD<br>RATE                                               |                                                       | %                                                   | SPBRG<br>value                                         | 4 MHz                                                  | %                                | SPBRG<br>value                                          | 8.579 MH                                                           | %                                                       | SPBRG<br>value                                |                                                  | %                                                                                         | SPBRG<br>value                                |                                             | %                                             | SPBRG<br>value                                   |

|                                                            | KBAUD                                                 | %                                                   | SPBRG<br>value                                         |                                                        |                                  | SPBRG                                                   |                                                                    | %                                                       | value                                         |                                                  | %                                                                                         |                                               |                                             |                                               | value                                            |

| RATE                                                       |                                                       | %                                                   | SPBRG<br>value                                         |                                                        |                                  | SPBRG<br>value<br>(decimal) ł                           |                                                                    | %                                                       | value                                         |                                                  | %<br>UD ERROF                                                                             | value                                         |                                             | %                                             | value                                            |

| RATE<br>(K)                                                | KBAUD                                                 | %<br>ERROR                                          | SPBRG<br>value<br>(decimal)                            | KBAUD                                                  |                                  | SPBRG<br>value<br>(decimal) ł                           | KBAUD                                                              | %<br>ERROR                                              | value<br>(decimal                             | ) KBA                                            | %<br>UD ERROF<br>28 -6.99                                                                 | value<br>(decimal)                            | ) KBAUD                                     | %                                             | value                                            |

| RATE<br>(K)<br>9.6                                         | KBAUD<br>9.6                                          | %<br>ERROR<br>0                                     | SPBRG<br>value<br>(decimal)<br>32                      | KBAUD<br>NA                                            | ERROR<br>-                       | SPBRG<br>value<br>(decimal) H                           | KBAUD<br>9.727                                                     | %<br>ERROR<br>+1.32                                     | value<br>(decimal<br>22                       | ) KBA                                            | %<br>UD ERROF<br>28 -6.99<br>33 +8.51                                                     | value<br>(decimal)<br>6                       | ) KBAUD                                     | %                                             | value                                            |

| RATE<br>(K)<br>9.6<br>19.2                                 | KBAUD<br>9.6<br>18.645                                | %<br>ERROR<br>0<br>-2.94                            | SPBRG<br>value<br>(decimal)<br>32<br>16                | KBAUD<br>NA<br>1.202                                   | ERROR<br>-<br>+0.17              | SPBRG<br>value<br>(decimal) F<br>-<br>207<br>103        | KBAUD<br>9.727<br>18.643                                           | %<br>ERROR<br>+1.32<br>-2.90                            | value<br>(decimal<br>22<br>11                 | ) KBA<br>8.92<br>20.8                            | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61                                        | value<br>(decimal)<br>6<br>2                  | ) KBAUD<br>NA<br>NA                         | ERROR<br>-<br>-                               | value<br>(decimal)<br>-<br>-                     |

| RATE<br>(K)<br>9.6<br>19.2<br>38.4<br>57.6<br>115.2        | KBAUD<br>9.6<br>18.645<br>39.6<br>52.8<br>105.6       | %<br>ERROR<br>0<br>-2.94<br>+3.12                   | SPBRG<br>value<br>(decimal)<br>32<br>16<br>7           | KBAUD<br>NA<br>1.202<br>2.403<br>9.615<br>19.231       | -<br>+0.17<br>+0.13              | SPBRG<br>value<br>(decimal) H<br>207<br>103<br>25<br>12 | KBAUD<br>9.727<br>18.643<br>37.286<br>55.930<br>111.860            | %<br>ERROR<br>+1.32<br>-2.90<br>-2.90<br>-2.90<br>-2.90 | value<br>(decimal<br>22<br>11<br>5            | ) KBA<br>8.92<br>20.8<br>31.2<br>62.<br>NA       | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61<br>5 +8.51<br>A -                      | value<br>(decimal)<br>6<br>2<br>1             | ) KBAUD<br>NA<br>NA<br>NA<br>NA<br>NA       | * ERROR<br>-<br>-<br>-                        | value<br>(decimal)<br>-<br>-                     |

| RATE<br>(K)<br>9.6<br>19.2<br>38.4<br>57.6<br>115.2<br>250 | KBAUD<br>9.6<br>18.645<br>39.6<br>52.8<br>105.6<br>NA | %<br>ERROR<br>0<br>-2.94<br>+3.12<br>-8.33          | SPBRG<br>value<br>(decimal)<br>32<br>16<br>7<br>5      | KBAUD<br>NA<br>1.202<br>2.403<br>9.615<br>19.231<br>NA | +0.17<br>+0.13<br>+0.16          | SPBRG<br>value<br>(decimal) H<br>207<br>103<br>25<br>12 | KBAUD<br>9.727<br>18.643<br>37.286<br>55.930<br>111.860<br>223.721 | %<br>ERROR<br>+1.32<br>-2.90<br>-2.90<br>-2.90          | value<br>(decimal<br>22<br>11<br>5<br>3       | ) KBA<br>8.92<br>20.8<br>31.2<br>62.<br>NA<br>NA | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61<br>5 +8.51<br>A -<br>A -               | value<br>(decimal)<br>6<br>2<br>1<br>0        | ) KBAUD<br>NA<br>NA<br>NA<br>NA<br>NA<br>NA | * ERROR<br>-<br>-<br>-<br>-                   | value<br>(decimal)<br>-<br>-<br>-<br>-           |

| RATE<br>(K)<br>9.6<br>19.2<br>38.4<br>57.6<br>115.2        | KBAUD<br>9.6<br>18.645<br>39.6<br>52.8<br>105.6       | %<br>ERROR<br>0<br>-2.94<br>+3.12<br>-8.33<br>-8.33 | SPBRG<br>value<br>(decimal)<br>32<br>16<br>7<br>5<br>2 | KBAUD<br>NA<br>1.202<br>2.403<br>9.615<br>19.231       | +0.17<br>+0.13<br>+0.16<br>+0.16 | SPBRG<br>value<br>(decimal) H<br>207<br>103<br>25<br>12 | KBAUD<br>9.727<br>18.643<br>37.286<br>55.930<br>111.860            | %<br>ERROR<br>+1.32<br>-2.90<br>-2.90<br>-2.90<br>-2.90 | value<br>(decimal)<br>22<br>11<br>5<br>3<br>1 | ) KBA<br>8.92<br>20.8<br>31.2<br>62.<br>NA       | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61<br>5 +8.51<br>A -<br>A -<br>A -<br>A - | value<br>R (decimal)<br>6<br>2<br>1<br>0<br>- | ) KBAUD<br>NA<br>NA<br>NA<br>NA<br>NA       | %<br>ERROR<br>-<br>-<br>-<br>-<br>-<br>-<br>- | value<br>(decimal)<br>-<br>-<br>-<br>-<br>-<br>- |

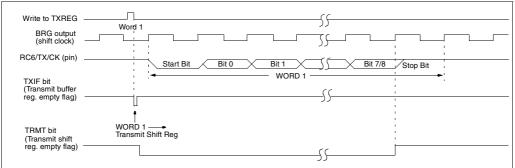

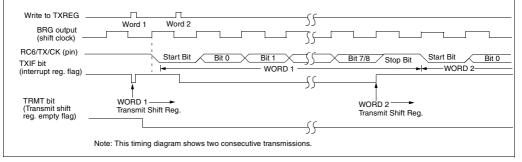

## FIGURE 9-5: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

## TABLE 9-6 REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address | Name  | Bit 7                | Bit 6    | Bit 5     | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|----------------------|----------|-----------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF     | RCIF      | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h     | RCSTA | SPEN                 | RX9      | SREN      | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 19h     | TXREG | USART Tra            | ansmit F | Register  |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE     | RCIE      | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h     | TXSTA | CSRC                 | TX9      | TXEN      | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h     | SPBRG | Baud Rate            | Genera   | ator Regi | ster  |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

The value that is in the ADRESH and ADRESL registers are not modified for a Power-on Reset. The ADRESH and ADRESL registers will contain unknown data after a Power-on Reset.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 11.6. After this acquisition time has elapsed the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

## 11.2 Configuring the A/D Module

## 11.3 Configuring Analog Port Pins

The ADCON1 and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS3:CHS0 bits and the TRIS bits.

- Note 1: When reading the PORTA or PORTE register, all pins configured as analog input channels will read as cleared (a low level). When reading the PORTB register, all pins configured as analog input channels will read as set (a high level). Pins configured as digital inputs, will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- Note 2: Analog levels on any pin that is defined as a digital input (including the ANx pins), may cause the input buffer to consume current that is out of the devices specification.

## 11.3.1 CONFIGURING THE REFERENCE VOLTAGES

The VCFG bits in the ADCON1 register configure the A/D module reference inputs. The reference high input can come from an internal reference (VRH) or (VRL), an external reference (VREF+), or AVDD. The low reference input can come from an internal reference (VRL), an external reference (VREF-), or AVSS. If an external reference is chosen for the reference high or reference low inputs, the port pin that multiplexes the incoming external references is configured as an analog input, regardless of the values contained in the A/D port configuration bits (PCFG3:PCFG0).

After the A/D module has been configured as desired. and the analog input channels have their corresponding TRIS bits selected for port inputs, the selected channel must be acquired before conversion is started. The A/D conversion cycle can be initiated by setting the GO/DONE bit. The A/D conversion begins, and lasts for 13TAD. The following steps should be followed for performing an A/D conversion:

- 1. Configure the A/D module

- Configure analog pins / voltage reference / and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if required)

- Clear ADIF bit

- Set ADIE bit

- Set PEIE bit

- · Set GIE bit

- 3. Wait the required acquisition time (3TAD)

- 4. Start conversion

- Set GO/DONE bit (ADCON0)

- 5. Wait 13TAD until A/D conversion is complete, by either:

- Polling for the GO/DONE bit to be cleared OR

- Waiting for the A/D interrupt

- 6. Read A/D Result registers (ADRESH and ADRESL), clear ADIF if required.

- 7. For next conversion, go to step 1, step 2 or step 3 as required.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRESH and ADRESL registers **WILL** be updated with the partially completed A/D conversion value. That is, the ADRESH and ADRESL registers **WILL** contain the value of the current incomplete conversion.

Note: Do not set the ADON bit and the GO/DONE bit in the same instruction. Doing so will cause the GO/DONE bit to be automatically cleared.

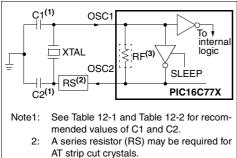

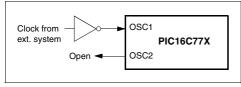

## FIGURE 12-2: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

3: RF varies with the crystal chosen.

## FIGURE 12-3: EXTERNAL CLOCK INPUT OPERATION (HS OSC CONFIGURATION)

## TABLE 12-1 CERAMIC RESONATORS

| Ranges Tested:                                                                                 |                                  |                                         |  |  |  |  |

|------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------|--|--|--|--|

| Mode                                                                                           | Freq                             | OSC2                                    |  |  |  |  |

| XT                                                                                             | 455 kHz<br>2.0 MHz<br>4.0 MHz    | 68 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |  |  |  |

| HS 8.0 MHz 10 - 68 pF 10 - 68 pF<br>16.0 MHz 10 - 22 pF 10 - 22 pF                             |                                  |                                         |  |  |  |  |

| These values are for design guidance only. See<br>notes at bottom of page.<br>Resonators Used: |                                  |                                         |  |  |  |  |

| 455 kHz Panasonic EFO-A455K04B ± 0.3%                                                          |                                  |                                         |  |  |  |  |

| 2.0 MHz                                                                                        | Murata Erie CSA2.00MG ± 0.5%     |                                         |  |  |  |  |

| 4.0 MHz                                                                                        | Murata Erie CSA4.00MG ± 0.5%     |                                         |  |  |  |  |

| 8.0 MHz                                                                                        | Murata Erie CSA8.00MT ± 0.5%     |                                         |  |  |  |  |

| 16.0 MHz                                                                                       | Hz Murata Erie CSA16.00MX ± 0.5% |                                         |  |  |  |  |

| All resonators used did not have built-in capacitors.                                          |                                  |                                         |  |  |  |  |

## TABLE 12-2 CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Osc Type                                                                | Crystal<br>Freq                | Cap. Range<br>C1 | Cap. Range<br>C2 |  |  |  |  |

|-------------------------------------------------------------------------|--------------------------------|------------------|------------------|--|--|--|--|

| LP                                                                      | 32 kHz                         | 33 pF            | 33 pF            |  |  |  |  |

|                                                                         | 200 kHz                        | 15 pF            | 15 pF            |  |  |  |  |

| XT                                                                      | 200 kHz                        | 47-68 pF         | 47-68 pF         |  |  |  |  |

|                                                                         | 1 MHz                          | 15 pF            | 15 pF            |  |  |  |  |

|                                                                         | 4 MHz                          | 15 pF            | 15 pF            |  |  |  |  |

| HS                                                                      | 4 MHz                          | 15 pF            | 15 pF            |  |  |  |  |

|                                                                         | 8 MHz                          | 15-33 pF         | 15-33 pF         |  |  |  |  |

|                                                                         | 20 MHz                         | 20 MHz 15-33 pF  |                  |  |  |  |  |

| These values are for design guidance only. See notes at bottom of page. |                                |                  |                  |  |  |  |  |

| Crystals Used                                                           |                                |                  |                  |  |  |  |  |

| 32 kHz                                                                  | Epson C-00                     | ± 20 PPM         |                  |  |  |  |  |

| 200 kHz                                                                 | STD XTL 2                      | ± 20 PPM         |                  |  |  |  |  |

| 1 MHz                                                                   | ECS ECS-                       | ± 50 PPM         |                  |  |  |  |  |

| 4 MHz                                                                   | ECS ECS-4                      | ± 50 PPM         |                  |  |  |  |  |

| 8 MHz                                                                   | EPSON CA                       | ± 30 PPM         |                  |  |  |  |  |

| 20 MHz                                                                  | EPSON CA-301 20.000M-C ± 30 PP |                  |                  |  |  |  |  |

Note 1: Recommended values of C1 and C2 are identical to the ranges tested (Table 12-1).

- Higher capacitance increases the stability of oscillator but also increases the start-up time.

- Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification.

| TABLE 12-6 INITIALIZATION CONDITIONS FOR ALL REGISTERS |     |      |                                    |                          |                                 |  |  |  |

|--------------------------------------------------------|-----|------|------------------------------------|--------------------------|---------------------------------|--|--|--|

| Register                                               | Dev | ices | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |  |  |  |

| W                                                      | 773 | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| INDF                                                   | 773 | 774  | N/A                                | N/A                      | N/A                             |  |  |  |

| TMR0                                                   | 773 | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| PCL                                                    | 773 | 774  | 0000h                              | 0000h                    | PC + 1 <b>(2)</b>               |  |  |  |

| STATUS                                                 | 773 | 774  | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>            |  |  |  |

| FSR                                                    | 773 | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| PORTA                                                  | 773 | 774  | 0x 0000                            | 0u 0000                  | uu uuuu                         |  |  |  |

| PORTB                                                  | 773 | 774  | xxxx 11xx                          | uuuu 11uu                | uuuu uuuu                       |  |  |  |

| PORTC                                                  | 773 | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| PORTD                                                  | 773 | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| PORTE                                                  | 773 | 774  | 000                                | 000                      | uuu                             |  |  |  |

| PCLATH                                                 | 773 | 774  | 0 0000                             | 0 0000                   | u uuuu                          |  |  |  |

| INTCON                                                 | 773 | 774  | 0000 000x                          | 0000 000u                | uuuu uuuu <b>(1)</b>            |  |  |  |

| PIR1                                                   | 773 | 774  | r000 0000                          | r000 0000                | ruuu uuuu <b>(1)</b>            |  |  |  |

|                                                        | 773 | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu <b>(1)</b>            |  |  |  |

| PIR2                                                   | 773 | 774  | 00                                 | 00                       | u uu <b>(1)</b>                 |  |  |  |

| TMR1L                                                  | 773 | 774  | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| TMR1H                                                  | 773 | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| T1CON                                                  | 773 | 774  | 00 0000                            | uu uuuu                  | uu uuuu                         |  |  |  |

| TMR2                                                   | 773 | 774  | 0000 0000                          | 00 0000 0000 0000        |                                 |  |  |  |

| T2CON                                                  | 773 | 774  | -000 0000                          | -000 0000                | -uuu uuuu                       |  |  |  |

| SSPBUF                                                 | 773 | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| SSPCON                                                 | 773 | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |

| CCPR1L                                                 | 773 | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| CCPR1H                                                 | 773 | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| CCP1CON                                                | 773 | 774  | 00 0000                            | 00 0000                  | uu uuuu                         |  |  |  |

| RCSTA                                                  | 773 | 774  | 0000 000x                          | 0000 000x                | uuuu uuuu                       |  |  |  |

| TXREG                                                  | 773 | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |

| RCREG                                                  | 773 | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |

| CCPR2L                                                 | 773 | 774  | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| CCPR2H                                                 | 773 | 774  | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| CCP2CON                                                | 773 | 774  | 00 0000                            | 00 0000                  | uu uuuu                         |  |  |  |

| ADRESH                                                 | 773 | 774  | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| ADCON0                                                 | 773 | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |

| OPTION_REG                                             | 773 | 774  | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |  |  |

| TABLE 12-6 | INITIALIZATION CONDITIONS FOR ALL REGISTERS |

|------------|---------------------------------------------|

|            |                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 12-5 for reset value for specific condition.

## 12.13 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  ${\tt SLEEP}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{\text{PD}}$  bit (STATUS<3>) is cleared, the  $\overline{\text{TO}}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD, or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D, disable external clocks. Pull all I/O pins, that are hi-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 12.13.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some Peripheral Interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. PSP read or write.

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. CCP capture mode interrupt.

- 4. Special event trigger (Timer1 in asynchronous mode using an external clock).

- 5. SSP (Start/Stop) bit detect interrupt.

- 6. SSP transmit or receive in slave mode (SPI/I<sup>2</sup>C).

- 7. USART RX or TX (synchronous slave mode).

- 8. A/D conversion (when A/D clock source is RC).

- 9. Low-voltage detect.

Other peripherals cannot generate interrupts since during SLEEP, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the substruction after the substruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 12.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

# PIC16C77X

NOTES:

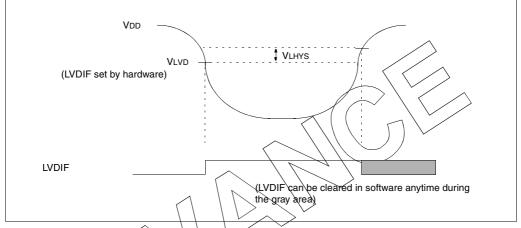

## FIGURE 15-1: LOW-VOLTAGE DETECT CHARACTERISTICS

| TABLE 1      | 5-3 ELECTRIC                                 | CAL CHARACT                            | ERISTICS:       | LVD          |                                      |                |                          |            |

|--------------|----------------------------------------------|----------------------------------------|-----------------|--------------|--------------------------------------|----------------|--------------------------|------------|

| DC CHAI      | RACTERISTICS                                 | Standard Operating temporating voltage | erature -4<br>0 | 40°C `<br>°C | $\leq$ TA $\leq$ TA $\leq$ TA $\leq$ | +85°C<br>+70°C | for industi<br>for comme | rial and   |

| Param<br>No. | Charact                                      | eristic                                | Symbol          | Min          | Тур†                                 | Max            | Units                    | Conditions |

| D420         | LVD Voltage                                  | LVV = 0100                             |                 | 2.5          | 2.58                                 | 2.66           | V                        |            |

|              |                                              | LVV = 0101                             |                 | 2.7          | 2.78                                 | 2.86           | V                        |            |

|              |                                              | LVV = 0110                             |                 | 2.8          | 2.89                                 | 2.98           | V                        |            |

| L L          |                                              | LVV = 0111                             |                 | 3.0          | 3.1                                  | 3.2            | V                        |            |

|              |                                              | LVV = 1000                             |                 | 3.3          | 3.41                                 | 3.52           | V                        |            |

|              |                                              | LVV = 1001                             |                 | 3.5          | 3.61                                 | 3.72           | V                        |            |

|              |                                              | LVV = 1010                             |                 | 3.6          | 3.72                                 | 3.84           | V                        |            |

|              |                                              | LVV = 1011                             |                 | 3.8          | 3.92                                 | 4.04           | V                        |            |

|              |                                              | LVV = 1100                             |                 | 4.0          | 4.13                                 | 4.26           | V                        |            |

|              |                                              | LVV = 1101                             |                 | 4.2          | 4.33                                 | 4.46           | V                        |            |

|              |                                              | LVV = 1110                             |                 | 4.5          | 4.64                                 | 4.78           | V                        |            |

| D421         | Supply Current                               |                                        | $\Delta$ ILVD   | —            | 10                                   | 20             | μΑ                       |            |

| D422*        | LVD Voltage Drift Temperature<br>coefficient |                                        | TCVout          | _            | 15                                   | 50             | ppm/°C                   |            |

| D423*        | 423* LVD Voltage Drift with respect to       |                                        | $\Delta VLVD/$  | —            | —                                    | 50             | μV/V                     |            |

|              | VDD Regulation                               |                                        |                 |              |                                      |                |                          |            |

| D424*        | Low-voltage Detec                            | t Hysteresis                           | VLHYS           | TBD          | —                                    | 100            | mV                       |            |

\* These parameters are characterized but not tested.

Note 1: Production tested at Tamb = 25°C. Specifications over temp limits ensured by characterization.

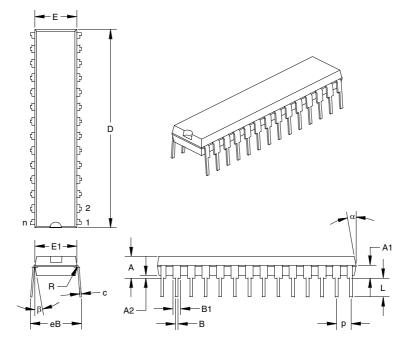

## 17.2 K04-070 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                        |                 | INCHES* |       |       | MILLIMETERS |       |       |  |

|------------------------------|-----------------|---------|-------|-------|-------------|-------|-------|--|

| Dimension Limits             |                 | MIN     | NOM   | MAX   | MIN         | NOM   | MAX   |  |

| PCB Row Spacing              |                 |         | 0.300 |       |             | 7.62  |       |  |

| Number of Pins               | n               |         | 28    |       |             | 28    |       |  |

| Pitch                        | р               |         | 0.100 |       |             | 2.54  |       |  |

| Lower Lead Width             | В               | 0.016   | 0.019 | 0.022 | 0.41        | 0.48  | 0.56  |  |

| Upper Lead Width             | B1 <sup>†</sup> | 0.040   | 0.053 | 0.065 | 1.02        | 1.33  | 1.65  |  |

| Shoulder Radius              | R               | 0.000   | 0.005 | 0.010 | 0.00        | 0.13  | 0.25  |  |

| Lead Thickness               | с               | 0.008   | 0.010 | 0.012 | 0.20        | 0.25  | 0.30  |  |

| Top to Seating Plane         | A               | 0.140   | 0.150 | 0.160 | 3.56        | 3.81  | 4.06  |  |

| Top of Lead to Seating Plane | A1              | 0.070   | 0.090 | 0.110 | 1.78        | 2.29  | 2.79  |  |

| Base to Seating Plane        | A2              | 0.015   | 0.020 | 0.025 | 0.38        | 0.51  | 0.64  |  |

| Tip to Seating Plane         | L               | 0.125   | 0.130 | 0.135 | 3.18        | 3.30  | 3.43  |  |

| Package Length               | D‡              | 1.345   | 1.365 | 1.385 | 34.16       | 34.67 | 35.18 |  |

| Molded Package Width         | E‡              | 0.280   | 0.288 | 0.295 | 7.11        | 7.30  | 7.49  |  |

| Radius to Radius Width       | E1              | 0.270   | 0.283 | 0.295 | 6.86        | 7.18  | 7.49  |  |

| Overall Row Spacing          | eB              | 0.320   | 0.350 | 0.380 | 8.13        | 8.89  | 9.65  |  |

| Mold Draft Angle Top         | α               | 5       | 10    | 15    | 5           | 10    | 15    |  |

| Mold Draft Angle Bottom      | β               | 5       | 10    | 15    | 5           | 10    | 15    |  |

\* Controlling Parameter.

<sup>†</sup> Dimension "B1" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B1."

<sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E."