Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                |                                                                          |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                              |

| Data Converters            | A/D 10x12b                                                               |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-QFP                                                                   |

| Supplier Device Package    | 44-MQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc774t-pq |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Key Features<br>PICmicro™ Mid-Range Reference Manual<br>(DS33023) | PIC16C773                          | PIC16C774                          |

|-------------------------------------------------------------------|------------------------------------|------------------------------------|

| Operating Frequency                                               | DC - 20 MHz                        | DC - 20 MHz                        |

| Resets (and Delays)                                               | POR, BOR, MCLR, WDT<br>(PWRT, OST) | POR, BOR, MCLR, WDT<br>(PWRT, OST) |

| Program Memory (14-bit words)                                     | 4K                                 | 4K                                 |

| Data Memory (bytes)                                               | 256                                | 256                                |

| Interrupts                                                        | 13                                 | 14                                 |

| I/O Ports                                                         | Ports A,B,C                        | Ports A,B,C,D,E                    |

| Timers                                                            | 3                                  | 3                                  |

| Capture/Compare/PWM modules                                       | 2                                  | 2                                  |

| Serial Communications                                             | MSSP, USART                        | MSSP, USART                        |

| Parallel Communications                                           | —                                  | PSP                                |

| 12-bit Analog-to-Digital Module                                   | 6 input channels                   | 10 input channels                  |

| Instruction Set                                                   | 35 Instructions                    | 35 Instructions                    |

# PIC16C77X

NOTES:

# PIC16C77X

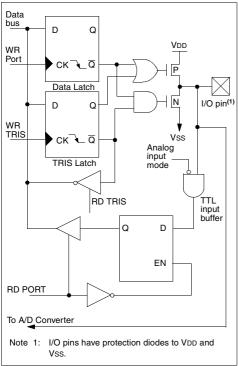

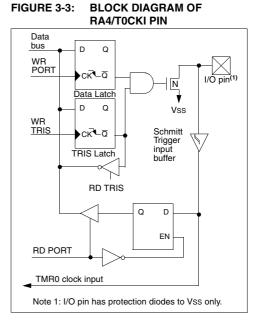

#### FIGURE 3-2: BLOCK DIAGRAM OF RA1:RA0 AND RA5 PINS

### TABLE 3-1 PORTA FUNCTIONS

| Name                   | Bit# | Buffer | Function                                                                                    |

|------------------------|------|--------|---------------------------------------------------------------------------------------------|

| RA0/AN0                | bit0 | TTL    | Input/output or analog input0                                                               |

| RA1/AN1                | bit1 | TTL    | Input/output or analog input1                                                               |

| RA2/AN2/VREF-/VRL      | bit2 | TTL    | Input/output or analog input2 or VREF- input or internal reference voltage low              |

| RA3/AN3/VREF+/VRH      | bit3 | TTL    | Input/output or analog input or VREF+ input or output of internal<br>reference voltage high |

| RA4/T0CKI              | bit4 | ST     | Input/output or external clock input for Timer0<br>Output is open drain type                |

| RA5/AN4 <sup>(1)</sup> | bit5 | TTL    | Input/output or analog input                                                                |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: RA5 is reserved on the 28-pin devices, maintain this bit clear.

### TABLE 3-2 SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name                 | Bit 7 | Bit 6 | Bit 5   | Bit 4      | Bit 3      | Bit 2 | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|----------------------|-------|-------|---------|------------|------------|-------|---------|---------|--------------------------|---------------------------|

| 05h     | PORTA <sup>(1)</sup> | —     | _     | RA5     | RA4        | RA3        | RA2   | RA1     | RA0     | 0x 0000                  | 0u 0000                   |

| 85h     | TRISA <sup>(1)</sup> | —     | —     | PORTA [ | Data Direc | tion Regis |       | 11 1111 | 11 1111 |                          |                           |

| 9Fh     | ADCON1               | ADFM  | VCFG2 | VCFG1   | VCFG0      | PCFG3      | PCFG2 | PCFG1   | PCFG0   | 0000 0000                | 0000 0000                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: PORTA<5>, TRISA<5> are reserved on the 28-pin devices, maintain these bits clear.

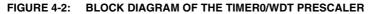

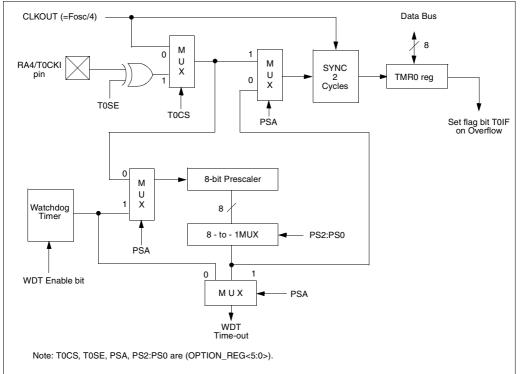

#### 4.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

Note: To avoid an unintended device RESET, a specific instruction sequence (shown in the PICmicro™ Mid-Range Reference Manual, DS33023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

#### 4.3 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP since the timer is shut off during SLEEP.

#### TABLE 4-1 REGISTERS ASSOCIATED WITH TIMER0

| Address               | Name       | Bit 7  | Bit 6                   | Bit 5                         | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------------------|------------|--------|-------------------------|-------------------------------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 01h,101h              | TMR0       | Timer0 | ïmer0 module's register |                               |       |       |       |       |       | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE    | PEIE                    | TOIE                          | INTE  | RBIE  | TOIF  | INTF  | RBIF  | 0000 000x                | 0000 000u                 |

| 81h,181h              | OPTION_REG | RBPU   | INTEDG                  | TOCS                          | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                 |

| 85h                   | TRISA      | _      | _                       | PORTA Data Direction Register |       |       |       |       |       | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

#### 5.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (Two 8-bit registers; TMR1H and TMR1L)

- Readable and writable (Both registers)

- · Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- · Reset from CCP module trigger

Timer1 has a control register, shown in Figure 5-1. Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Figure 5-3 is a simplified block diagram of the Timer1 module.

Additional information on timer modules is available in the PICmicro™ Mid-Range Reference Manual, (DS33023).

#### 5.1 **Timer1 Operation**

Timer1 can operate in one of these modes:

- · As a timer

- · As a synchronous counter

- As an asynchronous counter

The operating mode is determined by the clock select bit. TMR1CS (T1CON<1>).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored.

Timer1 also has an internal "reset input". This reset can be generated by the CCP module (Section 7.0).

#### T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h) U-0 U-0 R/W-0 R/W-0 B/W-0 R/W-0 **B/W-0** R/W-0 T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON R = Readable bit W = Writable bit bit7 bit0 = Unimplemented bit, U read as '0' n = Value at POR reset bit 7-6: Unimplemented: Read as '0' bit 5-4: T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits 11 = 1:8 Prescale value 10 = 1:4 Prescale value 01 = 1:2 Prescale value 00 = 1:1 Prescale value T1OSCEN: Timer1 Oscillator Enable Control bit hit 3 1 = Oscillator is enabled 0 = Oscillator is shut off Note: The oscillator inverter and feedback resistor are turned off to eliminate power drain T1SYNC: Timer1 External Clock Input Synchronization Control bit bit 2: TMR1CS = 11 = Do not synchronize external clock input 0 = Synchronize external clock input TMR1CS = 0This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0. TMR1CS: Timer1 Clock Source Select bit bit 1: 1 = External clock from pin RC0/T1OSO/T1CKI (on the rising edge) 0 = Internal clock (Fosc/4)

#### FIGURE 5-1:

- 1 = Enables Timer1

- 0 = Stops Timer1

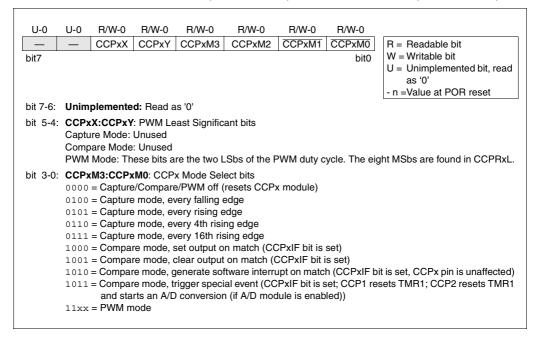

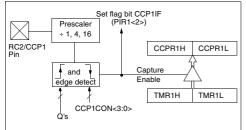

## 7.0 CAPTURE/COMPARE/PWM (CCP) MODULE(S)

Each CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave Duty Cycle register. Table 7-1 shows the timer resources of the CCP module modes.

The operation of CCP1 is identical to that of CCP2, with the exception of the special trigger. Therefore, operation of a CCP module in the following sections is described with respect to CCP1.

Table 7-2 shows the interaction of the CCP modules.

#### CCP1 Module

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

#### CCP2 Module

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. All are readable and writable.

Additional information on the CCP module is available in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

#### TABLE 7-1 CCP MODE - TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

| CCPx Mode | CCPy Mode | Interaction                                                                           |

|-----------|-----------|---------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base.                                                                  |

| Capture   | Compare   | The compare should be configured for the special event trigger, which clears TMR1.    |

| Compare   | Compare   | The compare(s) should be configured for the special event trigger, which clears TMR1. |

| PWM       | PWM       | The PWMs will have the same frequency, and update rate (TMR2 interrupt).              |

| PWM       | Capture   | None                                                                                  |

| PWM       | Compare   | None                                                                                  |

#### TABLE 7-2 INTERACTION OF TWO CCP MODULES

#### FIGURE 7-1: CCP1CON REGISTER (ADDRESS 17h) / CCP2CON REGISTER (ADDRESS 1Dh)

#### 7.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as:

- · every falling edge

- · every rising edge

- · every 4th rising edge

- every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 7.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 is configured as an out-     |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

## FIGURE 7-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 7.1.2 TIMER1 MODE SELECTION

Timer1 must be running in timer mode or synchronized counter mode for the CCP module to use the capture feature. In asynchronous counter mode, the capture operation may not work.

#### 7.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in operating mode.

#### 7.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in capture mode, the prescaler counter is cleared. This means that any reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 7-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 7-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ; value                 |

## FIGURE 8-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS: 94h)

| R/W-0  | R/W-0                                                         | R-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R-0                                                                        | R-0                                       | R-0                                          | R-0          | R-0                                            |                                                                                    |

|--------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------|--------------|------------------------------------------------|------------------------------------------------------------------------------------|

| SMP    | CKE                                                           | D/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Р                                                                          | S                                         | R/W                                          | UA           | BF                                             | R =Readable bit                                                                    |

| bit7   |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |                                           |                                              |              | bit0                                           | W =Writable bit<br>U =Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset |

| oit 7: | <u>SPI Ma</u>                                                 | ample bi<br>ster Mod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <u>e</u>                                                                   | end of data                               | a output time                                |              |                                                |                                                                                    |

|        | 0 = Inpi<br><u>SPI Sla</u>                                    | ut data sa<br><u>ve Mode</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | impled at i                                                                | middle of c                               | lata output ti<br>ed in slave r              | me           |                                                |                                                                                    |

|        | 1= Slev                                                       | rate cor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            | ed for star                               | dard speed                                   | •            | <hz 1="" and="" i<="" td=""><td>MHz)</td></hz> | MHz)                                                                               |

| oit 6: | CKP =                                                         | <u>0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                                                                          | ect (Figure                               | 8-6, Figure 8                                | 3-8, and Fig | ure 8-9)                                       |                                                                                    |

|        | 0 = Dat<br><u>CKP =</u><br>1 = Dat                            | a transmi<br><u>1</u><br>a transmi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | tted on fal<br>tted on fal                                                 | ling edge o<br>ling edge o<br>ling edge o | of SCK<br>of SCK                             |              |                                                |                                                                                    |

| oit 5: | 1 = Indi                                                      | cates tha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t the last b                                                               |                                           | /)<br>ed or transm<br>ed or transm           |              |                                                |                                                                                    |

| oit 4: | 1 = Indi                                                      | de only.<br>cates tha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                            | t has been                                | en the MSS<br>detected las                   |              |                                                | SSPEN is cleared)<br>ET)                                                           |

| oit 3: | 1 = Indi                                                      | de only.<br>cates tha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                            | it has beer                               | en the MSS                                   |              |                                                | SSPEN is cleared)<br>EET)                                                          |

| oit 2: | This bit<br>address                                           | holds the match te holds the holds t | e R/W bit<br>the next                                                      | informatio                                | mode only)<br>on following<br>top bit, or no |              | lress matc                                     | h. This bit is only valid from th                                                  |

|        | 0 = Wri<br><u>In I<sup>2</sup>C n</u><br>1 = Trai<br>0 = Trai | te<br><u>naster mo</u><br>nsmit is ir<br>nsmit is n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | n progress<br>ot in progr                                                  | ess.                                      |                                              | KEN will in  | diagta if th                                   | e MSSP is in IDLE mode                                                             |

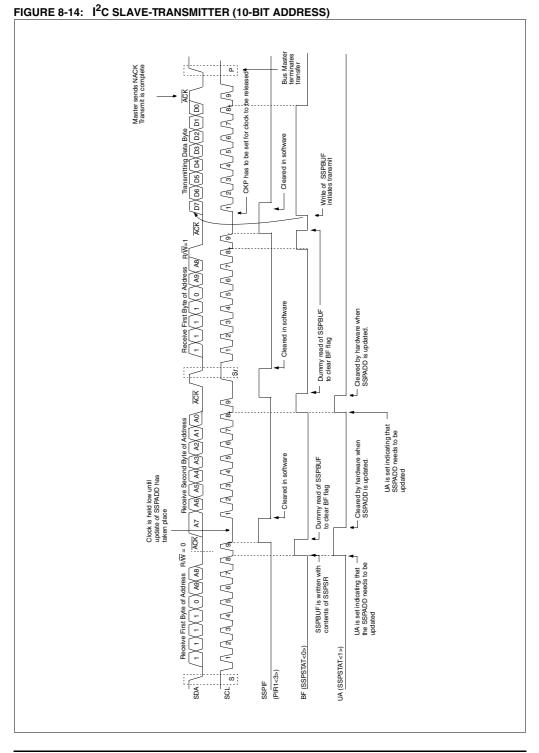

| oit 1: | <b>UA</b> : Up<br>1 = Indi                                    | date Add<br>cates tha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ress (10-b<br>t the user                                                   | it I <sup>2</sup> C mod                   | e only)<br>Ipdate the ac                     |              |                                                |                                                                                    |

| oit O: | <u>Receive</u><br>1 = Rec<br>0 = Rec<br><u>Transm</u>         | eive com<br>eive not<br>it (l <sup>2</sup> C mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>d I<sup>2</sup>C mod</u><br>plete, SSI<br>complete,<br><u>ode only)</u> | PBUF is fu<br>SSPBUF i                    |                                              |              |                                                |                                                                                    |

- The MSSP Module shifts in the ACK bit from the slave device, and writes its value into the SSPCON2 register (SSPCON2<6>).

- j) The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- k) The user generates a STOP condition by setting the STOP enable bit PEN in SSPCON2.

- I) Interrupt is generated once the STOP condition is complete.

#### 8.2.8 BAUD RATE GENERATOR

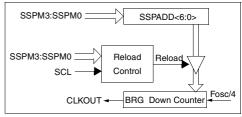

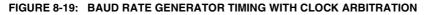

In  $l^2$ C master mode, the reload value for the BRG is located in the lower 7 bits of the SSPADD register (Figure 8-18). When the BRG is loaded with this value, the BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (TCY) on the Q2 and Q4 clock.

In I<sup>2</sup>C master mode, the BRG is reloaded automatically. If Clock Arbitration is taking place for instance, the BRG will be reloaded when the SCL pin is sampled high (Figure 8-19).

#### FIGURE 8-18: BAUD RATE GENERATOR BLOCK DIAGRAM

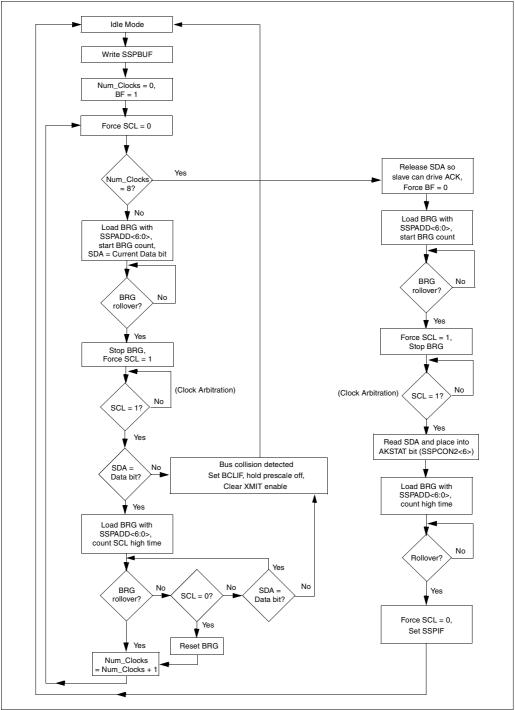

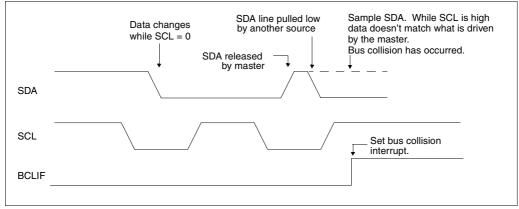

## 8.2.18 MULTI -MASTER COMMUNICATION, BUS COLLISION, AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the I<sup>2</sup>C port to its IDLE state. (Figure 8-34).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are de-asserted, and the SSPBUF can be written to. When the user services the bus collision interrupt service routine, and if the  $l^2C$  bus is free, the user can resume communication by asserting a START condition.

If a START, Repeated Start, STOP, or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are de-asserted, and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision interrupt service routine, and if the  $l^2$ C bus is free, the user can resume communication by asserting a START condition.

The Master will continue to monitor the SDA and SCL pins, and if a STOP condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when bus collision occurred.

In multi-master mode, the interrupt generation on the detection of start and stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is idle and the S and P bits are cleared.

FIGURE 8-34: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

### TABLE 13-2 PIC16CXXX INSTRUCTION SET

| Mnemonic,<br>Operands                  |        | Description                  | Cycles |     | 14-Bit | Opcode | e    | Status   | Notes |

|----------------------------------------|--------|------------------------------|--------|-----|--------|--------|------|----------|-------|

|                                        |        |                              |        | MSb |        | LSb    |      | Affected |       |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |        |                              |        |     |        |        |      |          |       |

| ADDWF                                  | f, d   | Add W and f                  | 1      | 00  | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF                                  | f, d   | AND W with f                 | 1      | 00  | 0101   | dfff   | ffff | Z        | 1,2   |

| CLRF                                   | f      | Clear f                      | 1      | 00  | 0001   | lfff   | ffff | Z        | 2     |

| CLRW                                   | -      | Clear W                      | 1      | 00  | 0001   | 0xxx   | xxxx | Z        |       |

| COMF                                   | f, d   | Complement f                 | 1      | 00  | 1001   | dfff   | ffff | Z        | 1,2   |

| DECF                                   | f, d   | Decrement f                  | 1      | 00  | 0011   | dfff   | ffff | Z        | 1,2   |

| DECFSZ                                 | f, d   | Decrement f, Skip if 0       | 1(2)   | 00  | 1011   | dfff   | ffff |          | 1,2,3 |

| INCF                                   | f, d   | Increment f                  | 1      | 00  | 1010   | dfff   | ffff | Z        | 1,2   |

| INCFSZ                                 | f, d   | Increment f, Skip if 0       | 1(2)   | 00  | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF                                  | f, d   | Inclusive OR W with f        | 1      | 00  | 0100   | dfff   | ffff | Z        | 1,2   |

| MOVF                                   | f, d   | Move f                       | 1      | 00  | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVWF                                  | f      | Move W to f                  | 1      | 00  | 0000   | lfff   | ffff |          |       |

| NOP                                    | -      | No Operation                 | 1      | 00  | 0000   | 0xx0   | 0000 |          |       |

| RLF                                    | f, d   | Rotate Left f through Carry  | 1      | 00  | 1101   | dfff   | ffff | С        | 1,2   |

| RRF                                    | f, d   | Rotate Right f through Carry | 1      | 00  | 1100   | dfff   | ffff | С        | 1,2   |

| SUBWF                                  | f, d   | Subtract W from f            | 1      | 00  | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF                                  | f, d   | Swap nibbles in f            | 1      | 00  | 1110   | dfff   | ffff |          | 1,2   |

| XORWF                                  | f, d   | Exclusive OR W with f        | 1      | 00  | 0110   | dfff   | ffff | Z        | 1,2   |

| BIT-ORIENT                             | ED FIL | E REGISTER OPERATIONS        |        |     |        |        |      |          |       |

| BCF                                    | f, b   | Bit Clear f                  | 1      | 01  | 00bb   | bfff   | ffff |          | 1,2   |

| BSF                                    | f, b   | Bit Set f                    | 1      | 01  | 01bb   | bfff   | ffff |          | 1,2   |

| BTFSC                                  | f, b   | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb   | bfff   | ffff |          | 3     |

| BTFSS                                  | f, b   | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb   | bfff   | ffff |          | 3     |

| LITERAL A                              | ND CO  | NTROL OPERATIONS             |        |     |        |        |      |          |       |

| ADDLW                                  | k      | Add literal and W            | 1      | 11  | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW                                  | k      | AND literal with W           | 1      | 11  | 1001   | kkkk   | kkkk | Z        |       |

| CALL                                   | k      | Call subroutine              | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CLRWDT                                 | -      | Clear Watchdog Timer         | 1      | 00  | 0000   | 0110   | 0100 | TO,PD    |       |

| GOTO                                   | k      | Go to address                | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| IORLW                                  | k      | Inclusive OR literal with W  | 1      | 11  | 1000   | kkkk   | kkkk | Z        |       |

| MOVLW                                  | k      | Move literal to W            | 1      | 11  | 00xx   | kkkk   | kkkk |          |       |

| RETFIE                                 | -      | Return from interrupt        | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW                                  | k      | Return with literal in W     | 2      | 11  | 01xx   | kkkk   | kkkk |          |       |

| RETURN                                 | -      | Return from Subroutine       | 2      | 0.0 | 0000   | 0000   | 1000 |          |       |

| SLEEP                                  | -      | Go into standby mode         | 1      | 00  | 0000   | 0110   | 0011 | TO,PD    |       |

| SUBLW                                  | k      | Subtract W from literal      | 1      | 11  | 110x   | kkkk   | kkkk | C,DC,Z   |       |

| XORLW                                  | k      | Exclusive OR literal with W  | 1      | 11  |        | kkkk   |      | Z        |       |

|                                        |        |                              | 1      | 1   |        |        |      |          | l     |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

### 15.4 DC Characteristics: VREF

#### TABLE 15-2 ELECTRICAL CHARACTERISTICS: VREF

| DC CHAR      | ACTERISTICS       | Standard Op<br>Operating ter | mperature      | -40°C<br>0°C | C` ≤ TA:<br>≤ TA: | ≤ +85°C<br>≤ +70°C  | for industr<br>for comme | ial and                   |

|--------------|-------------------|------------------------------|----------------|--------------|-------------------|---------------------|--------------------------|---------------------------|

| Param<br>No. | Charact           |                              | Symbol         | Min          | Typ†              | Max                 | Units                    | Conditions                |

| D400         | Output Voltage    |                              | VRL            | 2.0          | 2.048             | 2.1                 | V                        | VDD ≥ 2.5V                |

|              |                   |                              | VRH            | 4.0          | 4.096             | 4.2                 | V                        | VDØ ≥ 4.5V                |

| D401A        | VRL Quiescent S   | upply Current                | $\Delta IVRL$  | —            | 70                | TBD                 | μΑ                       | No load on VRL.           |

| D401B        | VRH Quiescent S   | Supply Current               | $\Delta IVRH$  | _            | 70                | TBD                 | µtA                      | No load on VRH.           |

| D402         | Ouput Voltage Dr  | ift                          | TCVOUT         | —            | 15*               | 50*                 | ppm/°C/                  | Note 1                    |

| D404         | External Load So  | urce                         | IVREFSO        | —            | _                 | ,5* (               | (mA                      |                           |

| D405         | External Load Sir | ık                           | IVREFSI        | —            | _                 | <- <del>5</del> * \ | ∖mA                      |                           |

| D406         | Load Regulation   |                              | AVOUT/         | —            | 1                 | TBD                 |                          | Isource = 0 mA to<br>5 mA |

|              |                   |                              |                | ~            | 71                | TBD*                | Am/V/mA                  | Isink = 0 mA to<br>5 mA   |

| D407         | Line Regulation   |                              | AVOUT/<br>AVDD | A            | _/                | 50*                 | μV/V                     |                           |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Production tested at TAMB  $= 25^{\circ}$ C. Specifications over temp limits guaranteed by characterization.

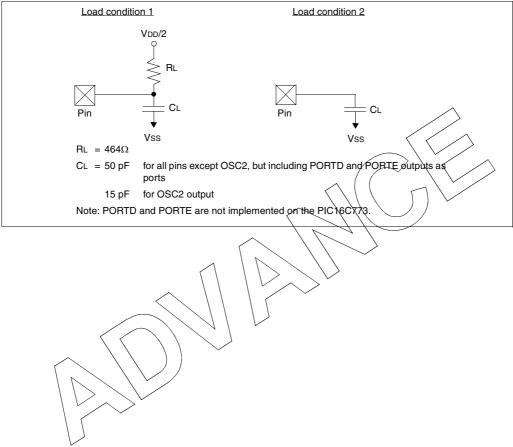

#### FIGURE 15-3: LOAD CONDITIONS

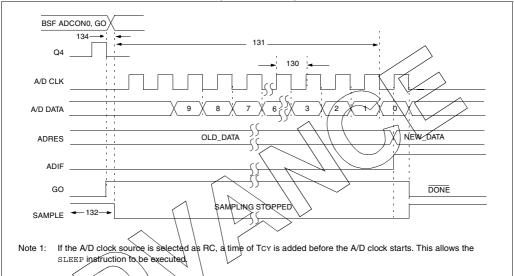

#### FIGURE 15-10: A/D CONVERSION TIMING (SLEEP MODE)

## TABLE 15-11 A/D CONVERSION REQUIREMENTS

| Parameter | Sym        | Characteristic                      | Min    | Typ†         | Max | Units | Conditions                                                                                                                                                                                                           |

|-----------|------------|-------------------------------------|--------|--------------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.       | $\searrow$ |                                     |        |              |     |       |                                                                                                                                                                                                                      |

| 130       | TAD        | A/D clock period                    | 1.6    | —            |     | μS    | $V_{REF} \ge 2.5V$                                                                                                                                                                                                   |

|           |            | ~                                   | TBD    | —            | _   | μs    | VREF full range                                                                                                                                                                                                      |

| 130*      | TAD        | A/D Internal RC                     |        |              |     |       | ADCS1:ADCS0 = 11 (RC mode)                                                                                                                                                                                           |

| V         |            | oscillator period                   | 3.0    | 6.0          | 9.0 | μs    | At VDD = 3.0V                                                                                                                                                                                                        |

|           |            |                                     | 2.0    | 4.0          | 6.0 | μS    | At VDD = 5.0V                                                                                                                                                                                                        |

| 131*      | TCNV       | Conversion time (not                | _      | 13Tad        |     | —     |                                                                                                                                                                                                                      |

|           |            | including acquisition time)(Note 1) |        |              |     |       |                                                                                                                                                                                                                      |

| 132*      | TACQ       | Acquisition Time                    | Note 2 | 11.5         | _   | μs    |                                                                                                                                                                                                                      |

|           |            |                                     | 5*     | _            | _   | μs    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1LSb (i.e<br>1mV @ 4.096V) from the last sam<br>pled voltage (as stated on CHOLD) |

| 134*      | TGO        | Q4 to A/D clock start               | _      | Tosc/2 + Tcy | —   | _     | If the A/D clock source is selected<br>as RC, a time of Tcy is added<br>before the A/D clock starts. This<br>allows the SLEEP instruction to be<br>executed.                                                         |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 11.6 for minimum conditions.

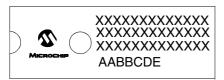

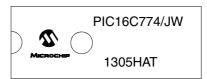

#### Package Marking Information (Cont'd)

####

#### 40-Lead CERDIP Windowed

#### Example

#### Example

#### 44-Lead TQFP

### Example

#### 44-Lead MQFP

#### 44-Lead PLCC

## Example

#### Example

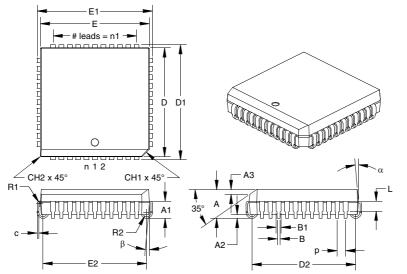

#### 17.10 K04-048 44-Lead Plastic Leaded Chip Carrier (L) – Square

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                   |                 | INCHES* |       |       | MILLIMETERS |       |       |

|-------------------------|-----------------|---------|-------|-------|-------------|-------|-------|

| Dimension Limits        |                 | MIN     | NOM   | MAX   | MIN         | NOM   | MAX   |

| Number of Pins          | n               |         | 44    |       |             | 44    |       |

| Pitch                   | р               |         | 0.050 |       |             | 1.27  |       |

| Overall Pack. Height    | А               | 0.165   | 0.173 | 0.180 | 4.19        | 4.38  | 4.57  |

| Shoulder Height         | A1              | 0.095   | 0.103 | 0.110 | 2.41        | 2.60  | 2.79  |

| Standoff                | A2              | 0.015   | 0.023 | 0.030 | 0.38        | 0.57  | 0.76  |

| Side 1 Chamfer Dim.     | A3              | 0.024   | 0.029 | 0.034 | 0.61        | 0.74  | 0.86  |

| Corner Chamfer (1)      | CH1             | 0.040   | 0.045 | 0.050 | 1.02        | 1.14  | 1.27  |

| Corner Chamfer (other)  | CH2             | 0.000   | 0.005 | 0.010 | 0.00        | 0.13  | 0.25  |

| Overall Pack. Width     | E1              | 0.685   | 0.690 | 0.695 | 17.40       | 17.53 | 17.65 |

| Overall Pack. Length    | D1              | 0.685   | 0.690 | 0.695 | 17.40       | 17.53 | 17.65 |

| Molded Pack. Width      | E‡              | 0.650   | 0.653 | 0.656 | 16.51       | 16.59 | 16.66 |

| Molded Pack. Length     | D‡              | 0.650   | 0.653 | 0.656 | 16.51       | 16.59 | 16.66 |

| Footprint Width         | E2              | 0.610   | 0.620 | 0.630 | 15.49       | 15.75 | 16.00 |

| Footprint Length        | D2              | 0.610   | 0.620 | 0.630 | 15.49       | 15.75 | 16.00 |

| Pins along Width        | n1              |         | 11    |       |             | 11    |       |

| Lead Thickness          | с               | 0.008   | 0.010 | 0.012 | 0.20        | 0.25  | 0.30  |

| Upper Lead Width        | B1 <sup>†</sup> | 0.026   | 0.029 | 0.032 | 0.66        | 0.74  | 0.81  |

| Lower Lead Width        | В               | 0.015   | 0.018 | 0.021 | 0.38        | 0.46  | 0.53  |

| Upper Lead Length       | L               | 0.050   | 0.058 | 0.065 | 1.27        | 1.46  | 1.65  |

| Shoulder Inside Radius  | R1              | 0.003   | 0.005 | 0.010 | 0.08        | 0.13  | 0.25  |

| J-Bend Inside Radius    | R2              | 0.015   | 0.025 | 0.035 | 0.38        | 0.64  | 0.89  |

| Mold Draft Angle Top    | α               | 0       | 5     | 10    | 0           | 5     | 10    |

| Mold Draft Angle Bottom | β               | 0       | 5     | 10    | 0           | 5     | 10    |

Controlling Parameter.

<sup>†</sup> Dimension "B1" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B1."

<sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E." JEDEC equivalent:MO-047 AC

# **PIC16C77X**

| Interrupts, Flag Bits               |             |

|-------------------------------------|-------------|

| A/D Converter Flag (ADIF Bit)       |             |

| CCP1 Flag (CCP1IF Bit)              | 20, 48, 49  |

| CCP2 Flag (CCP2IF Bit)              |             |

| Interrupt on Change (RB7:RB4) Flag  |             |

| (RBIF Bit)                          | 18, 30, 138 |

| PSP Read/Write Flag (PSPIF Bit)     |             |

| RB0/INT Flag (INTF Bit)             |             |

| SSP Flag (SSPIF Bit)                |             |

| TMR0 Overflow Flag (T0IF Bit)       | 18, 138     |

| TMR1 Overflow Flag (TMR1IF Bit)     |             |

| TMR2 to PR2 Match Flag (TMR2IF Bit) |             |

| USART Receive Flag (RCIF Bit)       |             |

| USART Transmit Flag (TXIE Bit)      |             |

|                                     |             |

## Κ

KeeLoq® Evaluation and Programming Tools ......148

#### Μ

| Master Clear (MCLR)                                     |

|---------------------------------------------------------|

| MCLR Reset, Normal Operation                            |

| MCLR Reset, SLEEP 131, 133, 134                         |

| Memory Organization                                     |

| Data Memory11                                           |

| Program Memory11                                        |

| MPLAB Integrated Development Environment Software . 147 |

| Multi-Master Communication90                            |

| Multi-Master Mode72                                     |

## 0

| OPCODE Field Descriptions |        |

|---------------------------|--------|

| OPTION_REG Register       |        |

| INTEDG Bit                |        |

| PS2:PS0 Bits              | 17, 39 |

| PSA Bit                   | 17, 39 |

| RBPU Bit                  |        |

| T0CS Bit                  |        |

| T0SE Bit                  |        |

| OSC1/CLKIN Pin            |        |

| OSC2/CLKOUT Pin           |        |

| Oscillator Configuration  |        |

| HS                        |        |

| LP                        |        |

| RC                        |        |

| ХТ                        |        |

| Oscillator, Timer1        |        |

| Oscillator, WDT           |        |

## Ρ

| Ρ                             | 54         |

|-------------------------------|------------|

| Packaging                     | 175        |

| Paging, Program Memory        |            |

| Parallel Slave Port (PSP)     | 9, 34, 37  |

| Block Diagram                 |            |

| RE0/RD/AN5 Pin                | 9, 36, 37  |

| RE1/WR/AN6 Pin                |            |

| RE2/CS/AN7 Pin                |            |

| Read Waveforms                | , ,        |

| Read/Write Enable (PSPIE Bit) |            |

| Read/Write Flag (PSPIF Bit)   |            |

| Select (PSPMODE Bit)          |            |

| Write Waveforms               |            |

| PCL Register                  |            |

| PCLATH Register               |            |

|                               | 10, 14, 10 |