Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Discontinued at Digi-Key                                                           |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                            |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 20MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | PWM, WDT                                                                           |

| Number of I/O              | 103                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 12K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 2.7V                                                                       |

| Data Converters            | A/D 16x8/10b                                                                       |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 144-LQFP                                                                           |

| Supplier Device Package    | PG-TQFP-144-7                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc167ci-32f20f-bb-a |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **General Device Information**

# 2 General Device Information

# 2.1 Introduction

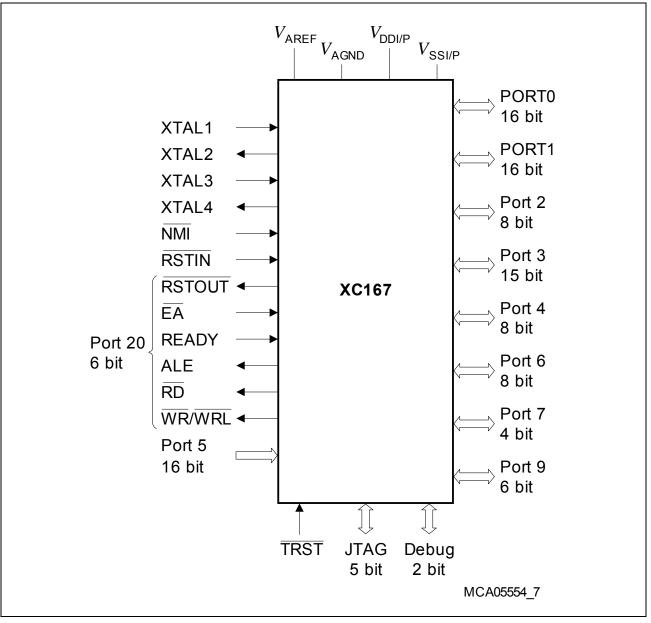

The XC167 derivatives are high-performance members of the Infineon XC166 Family of full featured single-chip CMOS microcontrollers. These devices extend the functionality and performance of the C166 Family in terms of instructions (MAC unit), peripherals, and speed. They combine high CPU performance (up to 40 million instructions per second) with high peripheral functionality and enhanced IO-capabilities. They also provide clock generation via PLL and various on-chip memory modules such as program Flash, program RAM, and data RAM.

Figure 1 Logic Symbol

# **General Device Information**

| Table 2     | Pi          | n Definit      | tions and F                                                                      | unctions                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|-------------|-------------|----------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Sym-<br>bol | Pin<br>Num. | Input<br>Outp. | Function                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| P20.12      | 3           | 10             | For details, please refer to the description of <b>P20</b> .                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| NMI         | 4           | 1              | pin causes<br>the PWRD<br>pin must <u>be</u><br>mode. If NI<br>continue to       | Non-Maskable Interrupt Input. A high to low transition at this<br>bin causes the CPU to vector to the NMI trap routine. When<br>he PWRDN (power down) instruction is executed, the NMI<br>bin must be low in order to force the XC167 into power down<br>node. If NMI is high, when PWRDN is executed, the part will<br>continue to run in normal mode.<br>If not used, pin NMI should be pulled high externally.<br>Port 6 is an 8-bit bidirectional I/O port. Each pin can be |  |  |  |  |

| P6          |             | IO             | programme<br>state) or ou<br>driver). The<br>or special).                        | ed for input (output driver in high-impedance<br>utput (configurable as push/pull or open drain<br>e input threshold of Port 6 is selectable (standard                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| P6.0        | 7           | 0              | The Port 6 pins also serve for alternate functions:<br>CS0 Chip Select 0 Output, |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| P6.1        | 8           | 10<br>0        | CC0IO<br>CS1                                                                     | CAPCOM1: CC0 Capture Inp./Compare Output<br>Chip Select 1 Output,                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| P6.2        | 9           | 10<br>0        | CC1IO<br>CS2                                                                     | CAPCOM1: CC1 Capture Inp./Compare Output<br>Chip Select 2 Output,                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 1 0.2       | 0           | 10             | CC2IO                                                                            | CAPCOM1: CC2 Capture Inp./Compare Output                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| P6.3        | 10          | 0              | CS3                                                                              | Chip Select 3 Output,                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| P6.4        | 11          | 10<br>0<br>10  | CC3IO<br>CS4<br>CC4IO                                                            | CAPCOM1: CC3 Capture Inp./Compare Output<br>Chip Select 4 Output,<br>CAPCOM1: CC4 Capture Inp./Compare Output                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| P6.5        | 12          |                | HOLD                                                                             | External Master Hold Request Input,                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|             |             | IO             | CC5IO                                                                            | CAPCOM1: CC5 Capture Inp./Compare Output                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| P6.6        | 13          | I/O            | HLDA                                                                             | Hold Acknowledge Output (master mode) or Input (slave mode),                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| P6.7        | 14          | 10<br>0<br>10  | CC6IO<br>BREQ<br>CC7IO                                                           | CAPCOM1: CC6 Capture Inp./Compare Output<br>Bus Request Output,<br>CAPCOM1: CC7 Capture Inp./Compare Output                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

# **General Device Information**

| Table 2          | Table 2Pin Definitions and Functions (cont'd) |                |                                                                                                                                                      |  |  |  |  |  |

|------------------|-----------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Sym-<br>bol      | Pin<br>Num.                                   | Input<br>Outp. | Function                                                                                                                                             |  |  |  |  |  |

| $V_{AREF}$       | 41                                            | —              | Reference voltage for the A/D converter.                                                                                                             |  |  |  |  |  |

| $V_{AGND}$       | 42                                            | _              | Reference ground for the A/D converter.                                                                                                              |  |  |  |  |  |

| $V_{DDI}$        | 48, 78,<br>135                                | -              | Digital Core Supply Voltage (On-Chip Modules):<br>+2.5 V during normal operation and idle mode.<br>Please refer to the <b>Operating Conditions</b> . |  |  |  |  |  |

| V <sub>DDP</sub> | 6, 20,<br>28, 58,<br>88,<br>103,<br>125       | -              | Digital Pad Supply Voltage (Pin Output Drivers):<br>+5 V during normal operation and idle mode.<br>Please refer to the <b>Operating Conditions</b> . |  |  |  |  |  |

| V <sub>SSI</sub> | 47, 79,<br>136,<br>139                        | _              | <b>Digital Ground</b><br>Connect decoupling capacitors to adjacent $V_{\text{DD}}/V_{\text{SS}}$ pin pairs as close as possible to the pins.         |  |  |  |  |  |

| V <sub>SSP</sub> | 5, 19,<br>27, 89,<br>104,<br>126              | -              | All $V_{\rm SS}$ pins must be connected to the ground-line or ground-<br>plane.                                                                      |  |  |  |  |  |

1) The CAN interface lines are assigned to ports P4, P7, and P9 under software control.

# 3 Functional Description

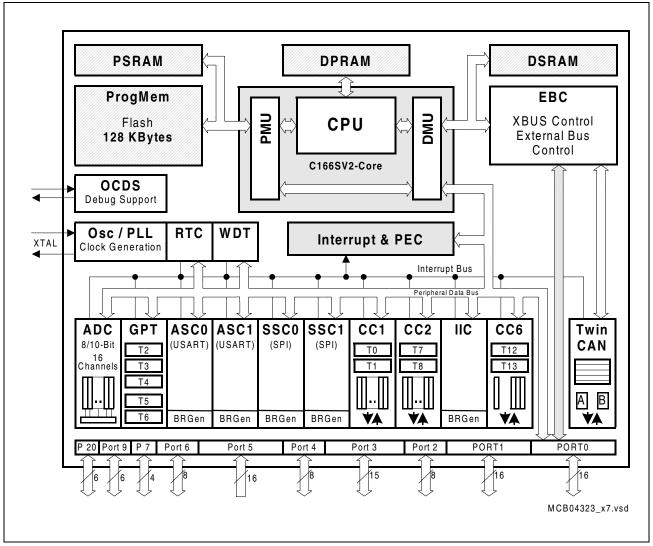

The architecture of the XC167 combines advantages of RISC, CISC, and DSP processors with an advanced peripheral subsystem in a very well-balanced way. In addition, the on-chip memory blocks allow the design of compact systems-on-silicon with maximum performance (computing, control, communication).

The on-chip memory blocks (program code-memory and SRAM, dual-port RAM, data SRAM) and the set of generic peripherals are connected to the CPU via separate buses. Another bus, the LXBus, connects additional on-chip resources as well as external resources (see **Figure 3**).

This bus structure enhances the overall system performance by enabling the concurrent operation of several subsystems of the XC167.

The following block diagram gives an overview of the different on-chip components and of the advanced, high bandwidth internal bus structure of the XC167.

Figure 3 Block Diagram

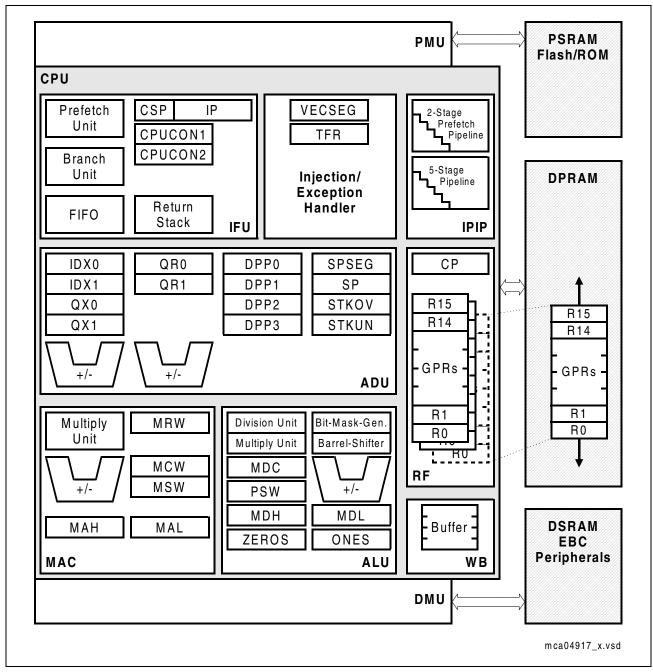

# 3.3 Central Processing Unit (CPU)

The main core of the CPU consists of a 5-stage execution pipeline with a 2-stage instruction-fetch pipeline, a 16-bit arithmetic and logic unit (ALU), a 32-bit/40-bit multiply and accumulate unit (MAC), a register-file providing three register banks, and dedicated SFRs. The ALU features a multiply and divide unit, a bit-mask generator, and a barrel shifter.

# Figure 4 CPU Block Diagram

Based on these hardware provisions, most of the XC167's instructions can be executed in just one machine cycle which requires 25 ns at 40 MHz CPU clock. For example, shift

The XC167 also provides an excellent mechanism to identify and to process exceptions or error conditions that arise during run-time, so-called 'Hardware Traps'. Hardware traps cause immediate non-maskable system reaction which is similar to a standard interrupt service (branching to a dedicated vector table location). The occurrence of a hardware trap is additionally signified by an individual bit in the trap flag register (TFR). Except when another higher prioritized trap service is in progress, a hardware trap will interrupt any actual program execution. In turn, hardware trap services can normally not be interrupted by standard or PEC interrupts.

**Table 5** shows all of the possible exceptions or error conditions that can arise during runtime:

| Exception Condition                                                                                                                                                               | Trap<br>Flag                        | Trap<br>Vector                            | Vector<br>Location <sup>1)</sup>                                                                                     | Trap<br>Number                                                           | Trap<br>Priority           |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------|--|

| <ul> <li>Reset Functions:</li> <li>Hardware Reset</li> <li>Software Reset</li> <li>Watchdog Timer<br/>Overflow</li> </ul>                                                         | _                                   | RESET<br>RESET<br>RESET                   | xx'0000 <sup>H</sup><br>xx'0000 <sup>H</sup>                                                                         | 00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub>                    | <br>   <br>                |  |

| <ul> <li>Class A Hardware Traps:</li> <li>Non-Maskable Interrupt</li> <li>Stack Overflow</li> <li>Stack Underflow</li> <li>Software Break</li> </ul>                              | NMI<br>STKOF<br>STKUF<br>SOFTBRK    | NMITRAP<br>STOTRAP<br>STUTRAP<br>SBRKTRAP | xx'0008 <sub>H</sub><br>xx'0010 <sub>H</sub><br>xx'0018 <sub>H</sub><br>xx'0020 <sub>H</sub>                         | 02 <sub>H</sub><br>04 <sub>H</sub><br>06 <sub>H</sub><br>08 <sub>H</sub> | <br>  <br>                 |  |

| <ul> <li>Class B Hardware Traps:</li> <li>Undefined Opcode</li> <li>PMI Access Error</li> <li>Protected Instruction<br/>Fault</li> <li>Illegal Word Operand<br/>Access</li> </ul> | UNDOPC<br>PACER<br>PRTFLT<br>ILLOPA | BTRAP<br>BTRAP<br>BTRAP<br>BTRAP          | xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub> | 0A <sub>H</sub><br>0A <sub>H</sub><br>0A <sub>H</sub><br>0A <sub>H</sub> | <br> <br>                  |  |

| Reserved                                                                                                                                                                          | _                                   | -                                         | [2C <sub>H</sub> - 3C <sub>H</sub> ]                                                                                 | [0B <sub>H</sub> -<br>0F <sub>H</sub> ]                                  | -                          |  |

| Software Traps <ul> <li>TRAP Instruction</li> </ul>                                                                                                                               | _                                   | _                                         | Any<br>[xx'0000 <sub>H</sub> -<br>xx'01FC <sub>H</sub> ]<br>in steps of<br>4 <sub>H</sub>                            | Any<br>[00 <sub>H</sub> -<br>7F <sub>H</sub> ]                           | Current<br>CPU<br>Priority |  |

# Table 5Hardware Trap Summary

1) Register VECSEG defines the segment where the vector table is located to.

# 3.5 On-Chip Debug Support (OCDS)

The On-Chip Debug Support system provides a broad range of debug and emulation features built into the XC167. The user software running on the XC167 can thus be debugged within the target system environment.

The OCDS is controlled by an external debugging device via the debug interface, consisting of the IEEE-1149-conforming JTAG port and a break interface. The debugger controls the OCDS via a set of dedicated registers accessible via the JTAG interface. Additionally, the OCDS system can be controlled by the CPU, e.g. by a monitor program. An injection interface allows the execution of OCDS-generated instructions by the CPU.

Multiple breakpoints can be triggered by on-chip hardware, by software, or by an external trigger input. Single stepping is supported as well as the injection of arbitrary instructions and read/write access to the complete internal address space. A breakpoint trigger can be answered with a CPU-halt, a monitor call, a data transfer, or/and the activation of an external signal.

Tracing data can be obtained via the JTAG interface or via the external bus interface for increased performance.

The debug interface uses a set of 6 interface signals (4 JTAG lines, 2 break lines) to communicate with external circuitry. These interface signals use dedicated pins.

Complete system emulation is supported by the New Emulation Technology (NET) interface.

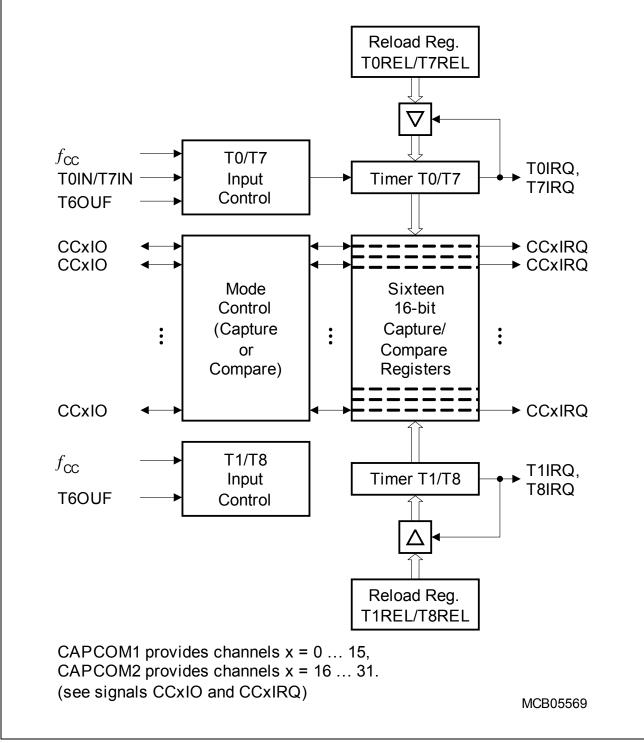

Figure 5 CAPCOM1/2 Unit Block Diagram

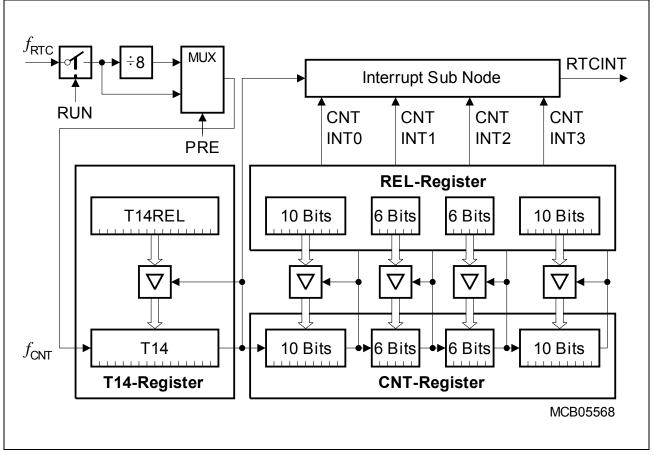

# 3.9 Real Time Clock

The Real Time Clock (RTC) module of the XC167 is directly clocked via a separate clock driver either with the on-chip auxiliary oscillator frequency ( $f_{\text{RTC}} = f_{\text{OSCa}}$ ) or with the prescaled on-chip main oscillator frequency ( $f_{\text{RTC}} = f_{\text{OSCm}}/32$ ). It is therefore independent from the selected clock generation mode of the XC167.

The RTC basically consists of a chain of divider blocks:

- a selectable 8:1 divider (on off)

- the reloadable 16-bit timer T14

- the 32-bit RTC timer block (accessible via registers RTCH and RTCL), made of:

- a reloadable 10-bit timer

- a reloadable 6-bit timer

- a reloadable 6-bit timer

- a reloadable 10-bit timer

All timers count up. Each timer can generate an interrupt request. All requests are combined to a common node request.

# Figure 9 RTC Block Diagram

Note: The registers associated with the RTC are not affected by a reset in order to maintain the correct system time even when intermediate resets are executed.

The RTC module can be used for different purposes:

- System clock to determine the current time and date, optionally during idle mode, sleep mode, and power down mode

- Cyclic time based interrupt, to provide a system time tick independent of CPU frequency and other resources, e.g. to wake up regularly from idle mode

- 48-bit timer for long term measurements (maximum timespan is > 100 years)

- Alarm interrupt for wake-up on a defined time

# 3.10 A/D Converter

For analog signal measurement, a 10-bit A/D converter with 16 multiplexed input channels and a sample and hold circuit has been integrated on-chip. It uses the method of successive approximation. The sample time (for loading the capacitors) and the conversion time is programmable (in two modes) and can thus be adjusted to the external circuitry. The A/D converter can also operate in 8-bit conversion mode, where the conversion time is further reduced.

Overrun error detection/protection is provided for the conversion result register (ADDAT): either an interrupt request will be generated when the result of a previous conversion has not been read from the result register at the time the next conversion is complete, or the next conversion is suspended in such a case until the previous result has been read.

For applications which require less analog input channels, the remaining channel inputs can be used as digital input port pins.

The A/D converter of the XC167 supports four different conversion modes. In the standard Single Channel conversion mode, the analog level on a specified channel is sampled once and converted to a digital result. In the Single Channel Continuous mode, the analog level on a specified channel is repeatedly sampled and converted without software intervention. In the Auto Scan mode, the analog levels on a prespecified number of channels are sequentially sampled and converted. In the Auto Scan Continuous mode, the prespecified channels are repeatedly sampled and converted. In addition, the conversion of a specific channel can be inserted (injected) into a running sequence without disturbing this sequence. This is called Channel Injection Mode.

The Peripheral Event Controller (PEC) may be used to automatically store the conversion results into a table in memory for later evaluation, without requiring the overhead of entering and exiting interrupt routines for each data transfer.

After each reset and also during normal operation the ADC automatically performs calibration cycles. This automatic self-calibration constantly adjusts the converter to changing operating conditions (e.g. temperature) and compensates process variations.

These calibration cycles are part of the conversion cycle, so they do not affect the normal operation of the A/D converter.

In order to decouple analog inputs from digital noise and to avoid input trigger noise those pins used for analog input can be disconnected from the digital IO or input stages under software control. This can be selected for each pin separately via register P5DIDIS (Port 5 Digital Input Disable).

The Auto-Power-Down feature of the A/D converter minimizes the power consumption when no conversion is in progress.

# 3.11 Asynchronous/Synchronous Serial Interfaces (ASC0/ASC1)

The Asynchronous/Synchronous Serial Interfaces ASC0/ASC1 (USARTs) provide serial communication with other microcontrollers, processors, terminals or external peripheral components. They are upward compatible with the serial ports of the Infineon 8-bit microcontroller families and support full-duplex asynchronous communication and half-duplex synchronous communication. A dedicated baud rate generator with a fractional divider precisely generates all standard baud rates without oscillator tuning. For transmission, reception, error handling, and baudrate detection 5 separate interrupt vectors are provided.

In asynchronous mode, 8- or 9-bit data frames (with optional parity bit) are transmitted or received, preceded by a start bit and terminated by one or two stop bits. For multiprocessor communication, a mechanism to distinguish address from data bytes has been included (8-bit data plus wake-up bit mode). IrDA data transmissions up to 115.2 kbit/s with fixed or programmable IrDA pulse width are supported.

In synchronous mode, bytes (8 bits) are transmitted or received synchronously to a shift clock which is generated by the ASC0/1. The LSB is always shifted first.

In both modes, transmission and reception of data is FIFO-buffered. An autobaud detection unit allows to detect asynchronous data frames with its baudrate and mode with automatic initialization of the baudrate generator and the mode control bits.

A number of optional hardware error detection capabilities has been included to increase the reliability of data transfers. A parity bit can automatically be generated on transmission or be checked on reception. Framing error detection allows to recognize data frames with missing stop bits. An overrun error will be generated, if the last character received has not been read out of the receive buffer register at the time the reception of a new character is complete.

# Summary of Features

- Full-duplex asynchronous operating modes

- 8- or 9-bit data frames, LSB first, one or two stop bits, parity generation/checking

- Baudrate from 2.5 Mbit/s to 0.6 bit/s (@ 40 MHz)

- Multiprocessor mode for automatic address/data byte detection

- Support for IrDA data transmission/reception up to max. 115.2 kbit/s (@ 40 MHz)

- Loop-back capability

- Auto baudrate detection

- Half-duplex 8-bit synchronous operating mode at 5 Mbit/s to 406.9 bit/s (@ 40 MHz)

- Buffered transmitter/receiver with FIFO support (8 entries per direction)

- Loop-back option available for testing purposes

- Interrupt generation on transmitter buffer empty condition, last bit transmitted condition, receive buffer full condition, error condition (frame, parity, overrun error), start and end of an autobaud detection

# Summary of Features

- CAN functionality according to CAN specification V2.0 B active

- Data transfer rate up to 1 Mbit/s

- Flexible and powerful message transfer control and error handling capabilities

- Full-CAN functionality and Basic CAN functionality for each message object

- 32 flexible message objects

- Assignment to one of the two CAN nodes

- Configuration as transmit object or receive object

- Concatenation to a 2-, 4-, 8-, 16-, or 32-message buffer with FIFO algorithm

- Handling of frames with 11-bit or 29-bit identifiers

- Individual programmable acceptance mask register for filtering for each object

- Monitoring via a frame counter

- Configuration for Remote Monitoring Mode

- Up to eight individually programmable interrupt nodes can be used

- CAN Analyzer Mode for bus monitoring is implemented

Note: When a CAN node has the interface lines assigned to Port 4, the segment address output on Port 4 must be limited. CS lines can be used to increase the total amount of addressable external memory.

# 3.14 IIC Bus Module

The integrated IIC Bus Module handles the transmission and reception of frames over the two-line IIC bus in accordance with the IIC Bus specification. The IIC Module can operate in slave mode, in master mode or in multi-master mode. It can receive and transmit data using 7-bit or 10-bit addressing. Up to 4 send/receive data bytes can be stored in the extended buffers.

Several physical interfaces (port pins) can be established under software control. Data can be transferred at speeds up to 400 kbit/s.

Two interrupt nodes dedicated to the IIC module allow efficient interrupt service and also support operation via PEC transfers.

Note: The port pins associated with the IIC interfaces must be switched to open drain mode, as required by the IIC specification.

| Parameter                                                  | Symbol                           |    | Limit Values |      | Unit | <b>Test Condition</b>             |  |

|------------------------------------------------------------|----------------------------------|----|--------------|------|------|-----------------------------------|--|

|                                                            |                                  |    | Min.         | Max. |      |                                   |  |

| Configuration pull-                                        | $I_{\text{CPDL}}^{11)}$          |    | _            | 10   | μA   | $V_{\rm IN} = V_{\rm ILmax}$      |  |

| down current <sup>13)</sup>                                | I <sub>CPDH</sub> <sup>12)</sup> |    | 120          | -    | μA   | $V_{\rm IN} = V_{\rm IHmin}$      |  |

| Level inactive hold current <sup>14)</sup>                 | $I_{\rm LHI}^{11)}$              |    | -            | -10  | μA   | $V_{ m OUT}$ = 0.5 × $V_{ m DDP}$ |  |

| Level active hold current <sup>14)</sup>                   | $I_{LHA}^{(12)}$                 |    | -100         | -    | μA   | V <sub>OUT</sub> = 0.45 V         |  |

| XTAL1, XTAL3 input current                                 | I <sub>IL</sub>                  | CC | -            | ±20  | μA   | $0 V < V_{IN} < V_{DDI}$          |  |

| Pin capacitance <sup>15)</sup><br>(digital inputs/outputs) | C <sub>IO</sub>                  | CC | -            | 10   | pF   | -                                 |  |

# Table 11 DC Characteristics (Operating Conditions apply)<sup>1)</sup> (cont'd)

1) Keeping signal levels within the limits specified in this table, ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{OV}$ .

2) If XTAL1 is driven by a crystal, reaching an amplitude (peak to peak) of  $0.4 \times V_{DDI}$  is sufficient.

3) If XTAL3 is driven by a crystal, reaching an amplitude (peak to peak) of  $0.25 \times V_{DDI}$  is sufficient.

4) This parameter is tested for P2, P3, P4, P6, P7, P9.

The maximum deliverable output current of a port driver depends on the selected output driver mode, see Table 12, Current Limits for Port Output Drivers. The limit for pin groups must be respected.

- 6) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL} \rightarrow V_{SS}$ ,  $V_{OH} \rightarrow V_{DDP}$ ). However, only the levels for nominal output currents are guaranteed.

- 7) This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage results from the external circuitry.

- 8) An additional error current ( $I_{INJ}$ ) will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{OV}$ .

- 9) The driver of P3.15 is designed for faster switching, because this pin can deliver the reference clock for the bus interface (CLKOUT). The maximum leakage current for P3.15 is, therefore, increased to 1 μA.

- 10) This specification is valid during Reset for configuration on RD, WR, EA, PORT0. The pull-ups on RD and WR (WRL/WRH) are also active during bus hold.

- 11) The maximum current may be drawn while the respective signal line remains inactive.

- 12) The minimum current must be drawn to drive the respective signal line active.

- 13) This specification is valid during Reset for configuration on ALE. The pull-down on ALE is also active during bus hold.

- 14) This specification is valid during Reset for pins P6.4-0, which can act as  $\overline{CS}$  outputs. The pull-ups on  $\overline{CS}$  outputs are also active during bus hold.

The pull-up on pin HLDA is active when arbitration is enabled and the EBC operates in slave mode.

15) Not subject to production test - verified by design/characterization.

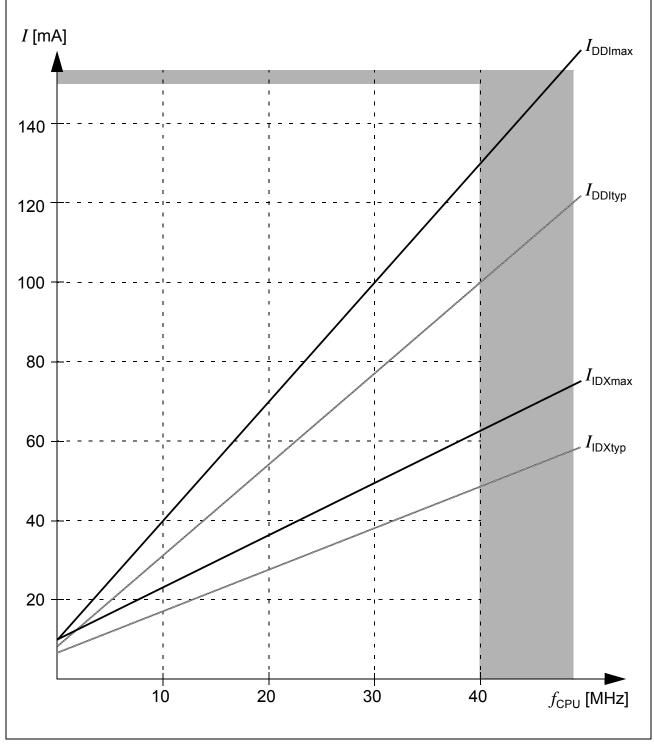

Figure 11 Supply/Idle Current as a Function of Operating Frequency

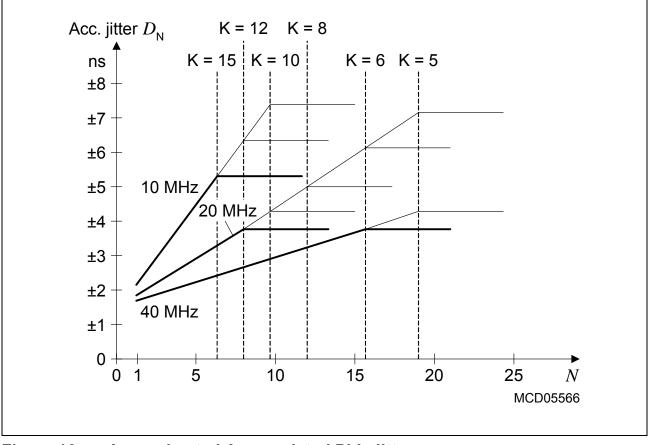

generation or measurement, lower baudrates, etc.) the deviation caused by the PLL jitter is negligible.

The value of the accumulated PLL jitter depends on the number of consecutive VCO output cycles within the respective timeframe. The VCO output clock is divided by the output prescaler (K = PLLODIV+1) to generate the master clock signal  $f_{MC}$ . Therefore, the number of VCO cycles can be represented as K × N, where N is the number of consecutive  $f_{MC}$  cycles (TCM).

For a period of **N**  $\times$  TCM the accumulated PLL jitter is defined by the deviation D<sub>N</sub>:

$D_N$  [ns] = ±(1.5 + 6.32 × N /  $f_{MC}$ );  $f_{MC}$  in [MHz], N = number of consecutive TCMs.

So, for a period of 3 TCMs @ 20 MHz and K = 12:  $D_3 = \pm(1.5 + 6.32 \times 3 / 20) = 2.448$  ns.

This formula is applicable for K × N < 95. For longer periods the K × N = 95 value can be used. This steady value can be approximated by:  $D_{Nmax}$  [ns] = ±(1.5 + 600 / (K ×  $f_{MC}$ )).

# Figure 16 Approximated Accumulated PLL Jitter

Note: The bold lines indicate the minimum accumulated jitter which can be achieved by selecting the maximum possible output prescaler factor K.

Different frequency bands can be selected for the VCO, so the operation of the PLL can be adjusted to a wide range of input and output frequencies:

| PLLCON.PLLVB | VCO Frequency Range | Base Frequency Range |  |  |

|--------------|---------------------|----------------------|--|--|

| 00           | 100 150 MHz         | 20 80 MHz            |  |  |

| 01           | 150 200 MHz         | 40 130 MHz           |  |  |

| 10           | 200 250 MHz         | 60 180 MHz           |  |  |

| 11           | Reserved            |                      |  |  |

#### .1) 4: . . 40 £

1) Not subject to production test - verified by design/characterization.

# 4.4.2 On-chip Flash Operation

The XC167's Flash module delivers data within a fixed access time (see Table 17).

Accesses to the Flash module are controlled by the PMI and take 1+WS clock cycles, where WS is the number of Flash access waitstates selected via bitfield WSFLASH in register IMBCTRL. The resulting duration of the access phase must cover the access time  $t_{ACC}$  of the Flash array. Therefore, the required Flash waitstates depend on the available speed grade as well as on the actual system frequency.

Note: The Flash access waitstates only affect non-sequential accesses. Due to prefetching mechanisms, the performance for sequential accesses (depending on the software structure) is only partially influenced by waitstates.

In typical applications, eliminating one waitstate increases the average performance by 5% ... 15%.

| Symb             | Symbol                       |                                       | Limit Values                                            |                                                                             |                                                                                                                                                                                                    |

|------------------|------------------------------|---------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                              | Min.                                  | Тур.                                                    | Max.                                                                        |                                                                                                                                                                                                    |

| t <sub>ACC</sub> | CC                           | -                                     | _                                                       | 70 <sup>1)</sup>                                                            | ns                                                                                                                                                                                                 |

| t <sub>ACC</sub> | CC                           | -                                     | _                                                       | 50 <sup>1)</sup>                                                            | ns                                                                                                                                                                                                 |

| t <sub>PR</sub>  | CC                           | -                                     | 2 <sup>2)</sup>                                         | 5                                                                           | ms                                                                                                                                                                                                 |

| t <sub>ER</sub>  | CC                           | -                                     | 200 <sup>2)</sup>                                       | 500                                                                         | ms                                                                                                                                                                                                 |

|                  | $t_{ACC}$ $t_{ACC}$ $t_{PR}$ | $t_{ACC} CC$ $t_{ACC} CC$ $t_{PR} CC$ | Min. $t_{ACC}$ CC $t_{ACC}$ CC $t_{ACC}$ CC $t_{PR}$ CC | Min.Typ. $t_{ACC}$ CC- $t_{ACC}$ CC- $t_{PR}$ CC- $t_{PR}$ CC- $t_{PR}$ CC- | Min.         Typ.         Max. $t_{ACC}$ CC         -         -         70 <sup>1)</sup> $t_{ACC}$ CC         -         -         50 <sup>1)</sup> $t_{PR}$ CC         -         2 <sup>2)</sup> 5 |

# Table 17 Flash Characteristics (Operating Conditions apply)

The actual access time is also influenced by the system frequency, so the frequency ranges are not fully linear. See Table 18.

2) Programming and erase time depends on the system frequency. Typical values are valid for 40 MHz.

Example: For an operating frequency of 40 MHz (clock cycle = 25 ns), Standard devices must be operated with 2 waitstates:  $((2+1) \times 25 \text{ ns}) \ge 70 \text{ ns}.$

Grade A devices can be operated with 1 waitstate:  $((1+1) \times 25 \text{ ns}) \ge 50 \text{ ns}$ .

Table 18 indicates the interrelation of waitstates, system frequency, and speed grade.

| Required Waitstates               | Frequency Range for<br>Standard Flash Speed | Frequency Range for<br>Flash Speed Grade A |

|-----------------------------------|---------------------------------------------|--------------------------------------------|

| $0$ WS (WSFLASH = $00_B$ )        | $f_{\rm CPU} \le$ 16 MHz                    | $f_{\sf CPU} \le$ 20 MHz                   |

| 1 WS (WSFLASH = $01_B$ )          | $f_{\rm CPU} \le$ 28 MHz                    | $f_{\rm CPU} \le$ 40 MHz                   |

| 2 WS (WSFLASH = 10 <sub>B</sub> ) | $f_{\rm CPU} \le$ 40 MHz                    | $f_{\rm CPU} \le$ 40 MHz                   |

Note: The maximum achievable system frequency is limited by the properties of the respective derivative, i.e. 40 MHz (or 20 MHz for xxx-32F20F devices).

# **External Bus Arbitration**

# Table 23Bus Arbitration Timing (Operating Conditions apply)

| Parameter                                   | Symbol                  |    |      | Limits |    |  |

|---------------------------------------------|-------------------------|----|------|--------|----|--|

|                                             |                         |    | Min. | Max.   |    |  |

| Input setup time for:<br>HOLD input         | <i>tc</i> <sub>40</sub> | SR | 29   | -      | ns |  |

| Output delay rising edge for:<br>HLDA, BREQ | <i>tc</i> <sub>41</sub> | CC | -1   | 6      | ns |  |

| Output delay falling edge for:<br>HLDA      | <i>tc</i> <sub>42</sub> | CC | 1    | 15     | ns |  |

Note: The shaded parameters have been verified by characterization. They are not subject to production test.

www.infineon.com