Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

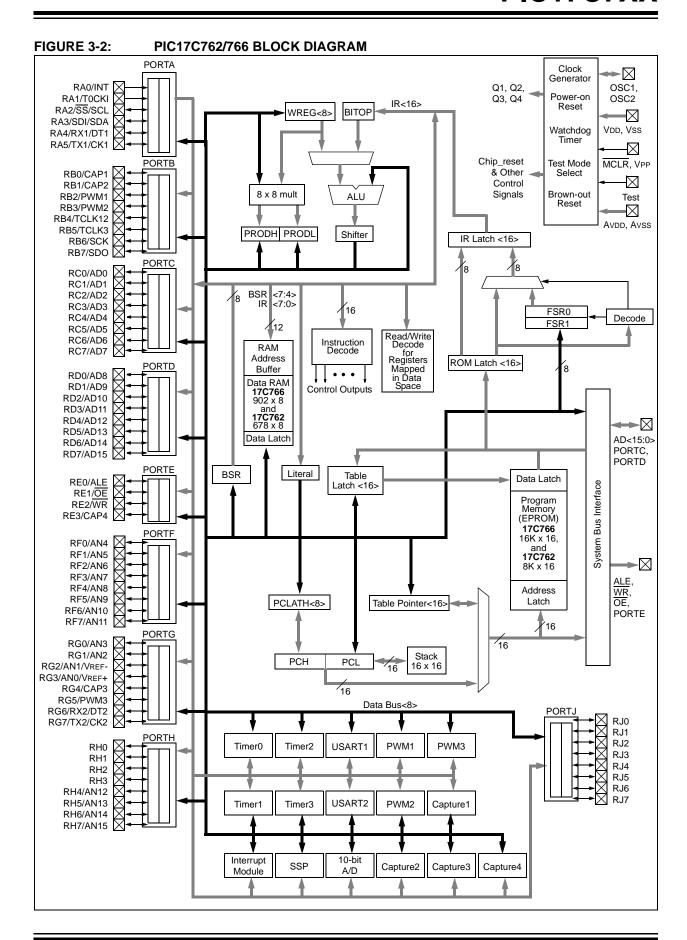

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| _                          |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Details                    |                                                                           |

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 16MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 50                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 454 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 68-LCC (J-Lead)                                                           |

| Supplier Device Package    | 68-PLCC (24.23x24.23)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c752-16e-l |

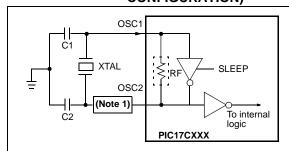

# FIGURE 4-2: CRYSTAL OR CERAMIC RESONATOR OPERATION (XT OR LF OSC CONFIGURATION)

See Table 4-1 and Table 4-2 for recommended values of C1 and C2.

Note 1: A series resistor (Rs) may be required for AT strip cut crystals.

### TABLE 4-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS

| Oscillator<br>Type | Resonator<br>Frequency         | Capacitor Range<br>C1 = C2 <sup>(1)</sup> |

|--------------------|--------------------------------|-------------------------------------------|

| LF                 | 455 kHz<br>2.0 MHz             | 15 - 68 pF<br>10 - 33 pF                  |

| XT                 | 4.0 MHz<br>8.0 MHz<br>16.0 MHz | 22 - 68 pF<br>33 - 100 pF<br>33 - 100 pF  |

Higher capacitance increases the stability of the oscillator, but also increases the start-up time. These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

Note 1: These values include all board capacitances on this pin. Actual capacitor value depends on board capacitance.

| Resonators | Resonators Used:       |        |  |  |  |  |  |

|------------|------------------------|--------|--|--|--|--|--|

| 455 kHz    | Panasonic EFO-A455K04B | ± 0.3% |  |  |  |  |  |

| 2.0 MHz    | Murata Erie CSA2.00MG  | ± 0.5% |  |  |  |  |  |

| 4.0 MHz    | Murata Erie CSA4.00MG  | ± 0.5% |  |  |  |  |  |

| 8.0 MHz    | Murata Erie CSA8.00MT  | ± 0.5% |  |  |  |  |  |

| 16.0 MHz   | Murata Erie CSA16.00MX | ± 0.5% |  |  |  |  |  |

Resonators used did not have built-in capacitors.

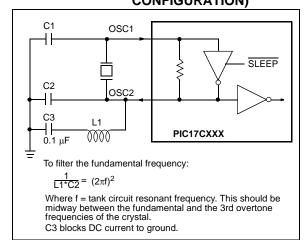

FIGURE 4-3: CRYSTAL OPERATION,

OVERTONE CRYSTALS

(XT OSC

CONFIGURATION)

TABLE 4-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Osc<br>Type | Freq                  | C1 <sup>(2)</sup> | C2 <sup>(2)</sup> |

|-------------|-----------------------|-------------------|-------------------|

| LF          | 32 kHz                | 100-150 pF        | 100-150 pF        |

|             | 1 MHz                 | 10-68 pF          | 10-68 pF          |

|             | 2 MHz                 | 10-68 pF          | 10-68 pF          |

| XT          | 2 MHz                 | 47-100 pF         | 47-100 pF         |

|             | 4 MHz                 | 15-68 pF          | 15-68 pF          |

|             | 8 MHz                 | 15-47 pF          | 15-47 pF          |

|             | 16 MHz                | 15-47 pF          | 15-47 pF          |

|             | 24 MHz <sup>(1)</sup> | 15-47 pF          | 15-47 pF          |

|             | 32 MHz <sup>(1)</sup> | 10-47 pF          | 10-47 pF          |

Higher capacitance increases the stability of the oscillator, but also increases the start-up time and the oscillator current. These values are for design guidance only. Rs may be required in XT mode to avoid overdriving the crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values for external components.

- Note 1: Overtone crystals are used at 24 MHz and higher. The circuit in Figure 4-3 should be used to select the desired harmonic frequency.

- 2: These values include all board capacitances on this pin. Actual capacitor value depends on board capacitance.

| Crystals | S Used: |

|----------|---------|

|----------|---------|

| 32.768 kHz | Epson C-001R32.768K-A | ± 20 PPM |

|------------|-----------------------|----------|

| 1.0 MHz    | ECS-10-13-1           | ± 50 PPM |

| 2.0 MHz    | ECS-20-20-1           | ± 50 PPM |

| 4.0 MHz    | ECS-40-20-1           | ± 50 PPM |

| 8.0 MHz    | ECS ECS-80-S-4        | ± 50 PPM |

|            | ECS-80-18-1           |          |

| 16.0 MHz   | ECS-160-20-1          | ± 50 PPM |

| 25 MHz     | CTS CTS25M            | ± 50 PPM |

| 32 MHz     | CRYSTEK HF-2          | ± 50 PPM |

Peripheral In

Data Bus

RD\_PORTE

WR\_PORTE

WR\_DDRE

WR\_DDRE

WR\_DDRE

WR\_DDRE

WR\_DDRE

WR\_DDRE

WR\_DDRE

WR\_DDRE

FIGURE 10-12: BLOCK DIAGRAM OF RE3/CAP4 PORT PIN

**TABLE 10-9: PORTE FUNCTIONS**

| Name     | Bit  | Buffer Type | Function                                                           |

|----------|------|-------------|--------------------------------------------------------------------|

| RE0/ALE  | bit0 | TTL         | Input/output or system bus Address Latch Enable (ALE) control pin. |

| RE1/OE   | bit1 | TTL         | Input/output or system bus Output Enable (OE) control pin.         |

| RE2/WR   | bit2 | TTL         | Input/output or system bus Write (WR) control pin.                 |

| RE3/CAP4 | bit3 | ST          | Input/output or Capture4 input pin.                                |

Legend: TTL = TTL input, ST = Schmitt Trigger input

TABLE 10-10: REGISTERS/BITS ASSOCIATED WITH PORTE

| Address     | Name  | Bit 7                             | Bit 6             | Bit 5  | Bit 4  | Bit 3    | Bit 2  | Bit 1     | Bit 0     | Value on<br>POR,<br>BOR | MCLR, WDT |

|-------------|-------|-----------------------------------|-------------------|--------|--------|----------|--------|-----------|-----------|-------------------------|-----------|

| 15h, Bank 1 | PORTE | _                                 | _                 | _      | _      | RE3/CAP4 | RE2/WR | RE1/OE    | RE0/ALE   | xxxx                    | uuuu      |

| 14h, Bank 1 | DDRE  | Data Direction Register for PORTE |                   |        |        |          |        |           | 1111      | 1111                    |           |

| 14h, Bank 7 | CA4L  | Capture4                          | Capture4 Low Byte |        |        |          |        |           | xxxx xxxx | uuuu uuuu               |           |

| 15h, Bank 7 | CA4H  | Capture4 High Byte                |                   |        |        |          |        | xxxx xxxx | uuuu uuuu |                         |           |

| 16h, Bank 7 | TCON3 | _                                 | CA40VF            | CA3OVF | CA4ED1 | CA4ED0   | CA3ED1 | CA3ED0    | PWM3ON    | -000 0000               | -000 0000 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

# 11.0 OVERVIEW OF TIMER RESOURCES

The PIC17C7XX has four timer modules. Each module can generate an interrupt to indicate that an event has occurred. These timers are called:

- Timer0 16-bit timer with programmable 8-bit prescaler

- Timer1 8-bit timer

- Timer2 8-bit timer

- Timer3 16-bit timer

For enhanced time base functionality, four input Captures and three Pulse Width Modulation (PWM) outputs are possible. The PWMs use the Timer1 and Timer2 resources and the input Captures use the Timer3 resource.

#### 11.1 Timer0 Overview

The Timer0 module is a simple 16-bit overflow counter. The clock source can be either the internal system clock (Fosc/4) or an external clock.

When Timer0 uses an external clock source, it has the flexibility to allow user selection of the incrementing edge, rising or falling.

The Timer0 module also has a programmable prescaler. The T0PS3:T0PS0 bits (T0STA<4:1>) determine the prescale value. TMR0 can increment at the following rates: 1:1, 1:2, 1:4, 1:8, 1:16, 1:32, 1:64, 1:128, 1:256.

Synchronization of the external clock occurs after the prescaler. When the prescaler is used, the external clock frequency may be higher than the device's frequency. The maximum external frequency on the TOCKI pin is 50 MHz, given the high and low time requirements of the clock.

#### 11.2 Timer1 Overview

The Timer1 module is an 8-bit timer/counter with an 8-bit period register (PR1). When the TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set and an interrupt will be generated if enabled. In Counter mode, the clock comes from the RB4/TCLK12 pin, which can also be selected to be the clock for the Timer2 module.

TMR1 can be concatenated with TMR2 to form a 16-bit timer. The TMR1 register is the LSB and TMR2 is the MSB. When in the 16-bit timer mode, there is a corresponding 16-bit period register (PR2:PR1). When the TMR2:TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set and an interrupt will be generated, if enabled.

#### 11.3 Timer2 Overview

The Timer2 module is an 8-bit timer/counter with an 8-bit period register (PR2). When the TMR2 value rolls over from the period match value to 0h, the TMR2IF flag is set and an interrupt will be generated, if enabled. In Counter mode, the clock comes from the RB4/TCLK12 pin, which can also provide the clock for the Timer1 module.

TMR2 can be concatenated with TMR1 to form a 16-bit timer. The TMR2 register is the MSB and TMR1 is the LSB. When in the 16-bit timer mode, there is a corresponding 16-bit period register (PR2:PR1). When the TMR2:TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set and an interrupt will be generated, if enabled.

#### 11.4 Timer3 Overview

The Timer3 module is a 16-bit timer/counter with a 16-bit period register. When the TMR3H:TMR3L value rolls over to 0h, the TMR3IF bit is set and an interrupt will be generated, if enabled. In Counter mode, the clock comes from the RB5/TCLK3 pin.

When operating in the four Capture modes, the period registers become the second (of four) 16-bit capture registers.

#### 11.5 Role of the Timer/Counters

The timer modules are general purpose, but have dedicated resources associated with them. Tlmer1 and Timer2 are the time bases for the three Pulse Width Modulation (PWM) outputs, while Timer3 is the time base for the four input captures.

#### 14.2 USART Asynchronous Mode

In this mode, the USART uses standard nonreturn-to-zero (NRZ) format (one START bit, eight or nine data bits, and one STOP bit). The most common data format is 8-bits. An on-chip dedicated 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART's transmitter and receiver are functionally independent but use the same data format and baud rate. The baud rate generator produces a clock x64 of the bit shift rate. Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

The Asynchronous mode is selected by clearing the SYNC bit (TXSTA<4>).

The USART Asynchronous module consists of the following components:

- · Baud Rate Generator

- · Sampling Circuit

- · Asynchronous Transmitter

- · Asynchronous Receiver

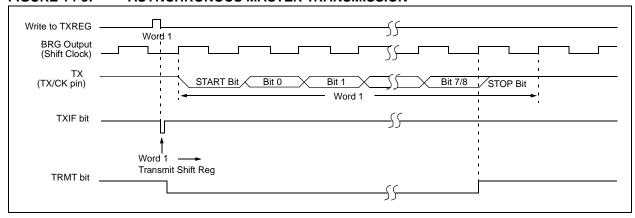

## 14.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 14-1. The heart of the transmitter is the transmit shift register (TSR). The shift register obtains its data from the read/write transmit buffer (TXREG). TXREG is loaded with data in software. The TSR is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once TXREG transfers the data to the TSR (occurs in one Tcy at the end of the current BRG cycle), the TXREG is empty and an interrupt bit, TXIF, is set. This interrupt can be enabled/disabled by setting/clearing the TXIE bit. TXIF will be set, regardless of TXIE and cannot be reset in software. It will reset only when new data is loaded into TXREG. While TXIF indicates the status of the TXREG, the TRMT (TXSTA<1>) bit shows the status of the TSR.

TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR is empty.

**Note:** The TSR is not mapped in data memory, so it is not available to the user.

Transmission enabled bv settina TXEN (TXSTA<5>) bit. The actual transmission will not occur until TXREG has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 14-3). The transmission can also be started by first loading TXREG and then setting TXEN. Normally, when transmission is first started, the TSR is empty, so a transfer to TXREG will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 14-4). Clearing TXEN during a transmission will cause the transmission to be aborted. This will reset the transmitter and the TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit value should be written to TX9D (TXSTA<0>). The ninth bit value must be written before writing the 8-bit data to the TXREG. This is because a data write to TXREG can result in an immediate transfer of the data to the TSR (if the TSR is empty).

Steps to follow when setting up an Asynchronous Transmission:

- Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the TXIE bit.

- 4. If 9-bit transmission is desired, then set the TX9 bit.

- 5. If 9-bit transmission is selected, the ninth bit should be loaded in TX9D.

- 6. Load data to the TXREG register.

- 7. Enable the transmission by setting TXEN (starts transmission).

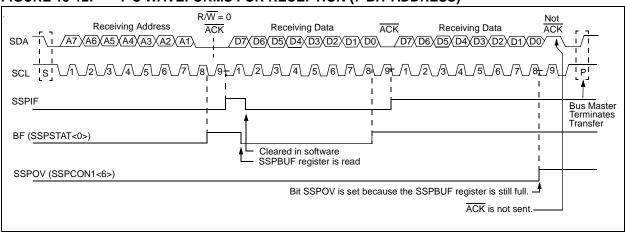

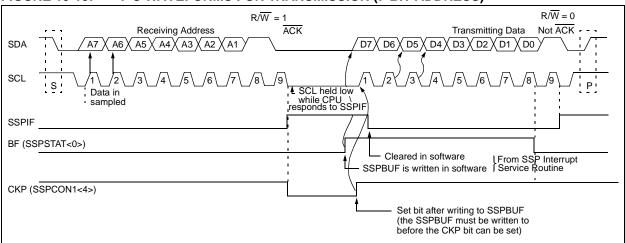

#### 15.2.1.3 Slave Transmission

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The  $\overline{ACK}$  pulse will be sent on the ninth bit, and the SCL pin is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then SCL pin should be enabled by setting bit CKP (SSPCON1<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 15-13).

An SSP interrupt is generated for each data transfer byte. The SSPIF flag bit must be cleared in software, and the SSPSTAT register is used to determine the status of the byte transfer. The SSPIF flag bit is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the not  $\overline{ACK}$  is latched by the slave, the slave logic is reset and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, the SCL pin should be enabled by setting the CKP bit.

FIGURE 15-12: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

#### FIGURE 15-13: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

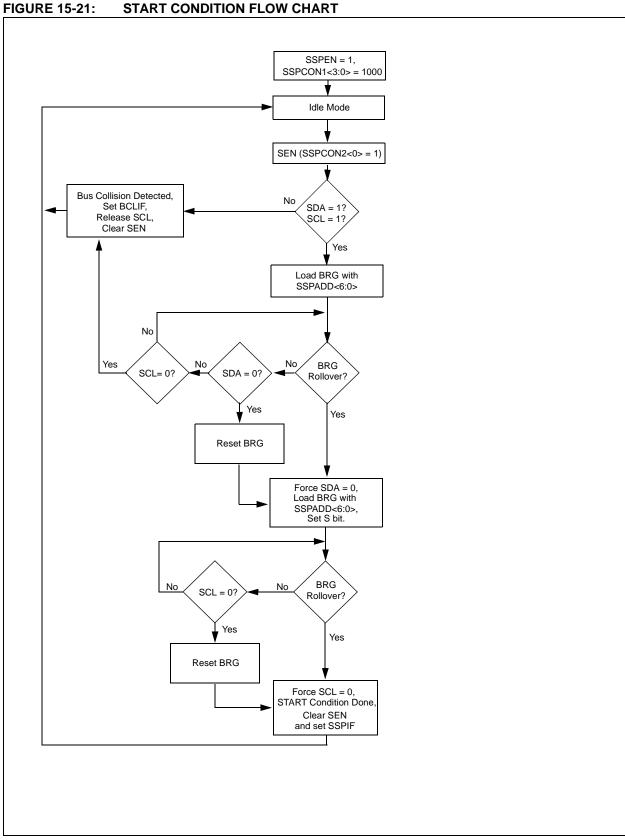

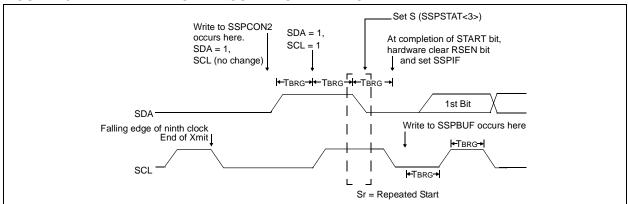

### 15.2.10 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C module is in the idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the baud rate generator is loaded with the contents of SSPADD<6:0> and begins counting. The SDA pin is released (brought high) for one baud rate generator count (TBRG). When the baud rate generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA is low) for one TBRG while SCL is high. Following this, the RSEN bit in the SSPCON2 register will be automatically cleared and the baud rate generator is not reloaded, leaving the SDA pin held low. As soon as a START condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the baud rate generator has timed out.

**Note 1:** If the RSEN is programmed while any other event is in progress, it will not take effect.

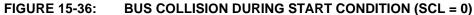

- 2: A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low to high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode), or eight bits of data (7-bit mode).

#### 15.2.10.1 WCOL status flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

**Note:** Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

FIGURE 15-22: REPEAT START CONDITION WAVEFORM

## 15.2.11 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address, or either half of a 10-bit address, is accomplished by simply writing a value to SSPBUF register. This action will set the buffer full flag (BF) and allow the baud rate generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time spec). SCL is held low for one baud rate generator roll over count (TBRG). Data should be valid before SCL is released high (see Data setup time spec). When the SCL pin is released high, it is held that way for TBRG, the data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA, allowing the slave device being addressed to respond with an ACK bit during the ninth bit time, if an address match occurs or if data was received properly. The status of ACK is read into the ACKDT on the falling edge of the ninth clock. If the master receives an acknowledge, the acknowledge status bit (AKSTAT) is cleared. If not, the bit is set. After the ninth clock, the SSPIF is set and the master clock (baud rate generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 15-26).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL until all seven address bits and the  $R/\overline{W}$  bit are completed. On the falling edge of the eighth clock, the master will de-assert the SDA pin, allowing the slave to respond with an acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the baud rate generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 15.2.11.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

#### 15.2.11.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

#### 15.2.11.3 AKSTAT Status Flag

In Transmit mode, the AKSTAT bit (SSPCON2<6 $\geq$ ) is cleared when the slave has sent an acknowledge (ACK = 0) and is set when the slave does not acknowledge (ACK = 1). A slave sends an acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

#### 15.2.12 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the receive enable bit, RCEN (SSPCON2<3>).

Note: The SSP Module must be in an IDLE STATE before the RCEN bit is set, or the RCEN bit will be disregarded.

The baud rate generator begins counting and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag is set, the SSPIF is set and the baud rate generator is suspended from counting, holding SCL low. The SSP is now in IDLE state, awaiting the next command. When the buffer is read by the CPU, the BF flag is automatically cleared. The user can then send an acknowledge bit at the end of reception, by setting the acknowledge sequence enable bit, ACKEN (SSPCON2<4>).

#### 15.2.12.1 BF Status Flag

In receive operation, BF is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when SSPBUF is read.

#### 15.2.12.2 SSPOV Status Flag

In receive operation, SSPOV is set when 8 bits are received into the SSPSR, and the BF flag is already set from a previous reception.

#### 15.2.12.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

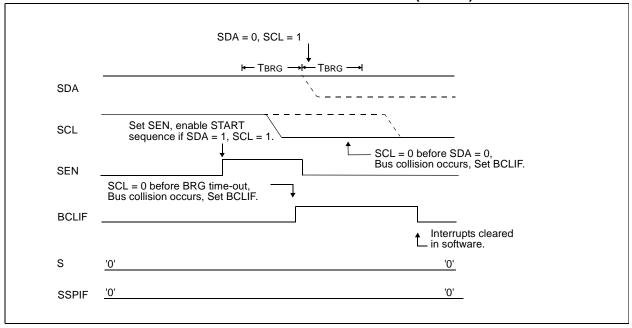

#### FIGURE 15-37: BRG RESET DUE TO SDA COLLISION DURING START CONDITION

#### 15.4 Example Program

Example 15-2 shows MPLAB® C17 'C' code for using the I<sup>2</sup>C module in Master mode to communicate with a 24LC01B serial EEPROM. This example uses the PIC® MCU 'C' libraries included with MPLAB C17.

#### EXAMPLE 15-2: INTERFACING TO A 24LC01B SERIAL EEPROM (USING MPLAB C17)

```

// Include necessary header files

#include <p17c756.h>

// Processor header file

// Delay routines header file

// Standard Library header file

#include <delays.h>

#include <stdlib.h>

// Stanuaru Bleen.

// I2C routines header file

#include <i2c16.h>

#define CONTROL 0xa0

// Control byte definition for 24LC01B

// Function declarations

void main(void);

void WritePORTD(static unsigned char data);

void ByteWrite(static unsigned char address, static unsigned char data);

unsigned char ByteRead(static unsigned char address);

void ACKPoll(void);

// Main program

void main(void)

static unsigned char address; // I2C address of 24LC01B

static unsigned char datao; \hspace{0.2in} // Data written to 24LC01B

static unsigned char datai;

// Data read from 24LC01B

// Preset address to 0

address = 0;

OpenI2C(MASTER,SLEW_ON);

\ensuremath{//} Configure I2C Module Master mode, Slew rate control on

SSPADD = 39;

// Configure clock for 100KHz

while(address<128)

// Loop 128 times, 24LC01B is 128x8

datao = PORTB:

do

ByteWrite(address, datao); // Write data to EEPROM

ACKPoll();

// Poll the 24LC01B for state

datai = ByteRead(address); // Read data from EEPROM into SSPBUF

} while(datai != datao);

// Loop as long as data not correctly

written to 24LC01B

address++:

// Increment address

}

while(1)

// Done writing 128 bytes to 24LC01B, Loop forever

{

Nop();

}

```

#### **EXAMPLE 15-2: INTERFACING TO A 24LC01B SERIAL EEPROM (USING MPLAB C17)**

```

// Writes the byte data to 24LC01B at the specified address

void ByteWrite(static unsigned char address, static unsigned char data)

StartI2C();

// Send start bit

// Wait for idle condition

IdleI2C();

WriteI2C(CONTROL);

// Send control byte

IdleI2C();

// Wait for idle condition

if (!SSPCON2bits.ACKSTAT)

// If 24LC01B ACKs

WriteI2C(address);

// Send control byte

IdleI2C();

// Wait for idle condition

// If 24LC01B ACKs

if (!SSPCON2bits.ACKSTAT)

WriteI2C(data);

// Send data

IdleI2C();

// Wait for idle condition

StopI2C();

// Send stop bit

// Wait for idle condition

IdleI2C();

return;

// Reads a byte of data from 24LC01B at the specified address

unsigned char ByteRead(static unsigned char address)

// Send start bit

StartI2C();

IdleI2C();

// Wait for idle condition

WriteI2C(CONTROL);

// Send control byte

IdleI2C();

// Wait for idle condition

if (!SSPCON2bits.ACKSTAT)

// If the 24LC01B ACKs

// Send address

WriteI2C(address);

// Wait for idle condition

IdleI2C();

if (!SSPCON2bits.ACKSTAT) // If the 24LC01B ACKs

RestartI2C();

// Send restart

IdleI2C();

// Wait for idle condition

// Send control byte with R/W set

WriteI2C(CONTROL+1);

IdleI2C();

// Wait for idle condition

// If the 24LC01B ACKs

if (!SSPCON2bits.ACKSTAT)

// Read a byte of data from 24LC01B

getcI2C();

// Wait for idle condition

IdleI2C();

NotAckI2C();

// Send a NACK to 24LC01B

IdleI2C();

// Wait for idle condition

// Send stop bit

StopI2C();

IdleI2C();

// Wait for idle condition

}

return(SSPBUF);

```

| TABLRD       | Table Re        | ad      |            | TAE  | LWT          | Table                 |

|--------------|-----------------|---------|------------|------|--------------|-----------------------|

| Example1:    | TABLRD          | 1, 1    | , REG ;    | Syn  | tax:         | [ label               |

| Before Inst  | ruction         |         |            | Ope  | rands:       | 0 ≤ f ≤               |

| REG          |                 | =       | 0x53       | •    |              | i ∈ [0,1              |

| TBLAT        | Н               | =       | 0xAA       |      |              | t ∈ [0,               |

| TBLAT        | L               | =       | 0x55       | 0    |              |                       |

| TBLPT        | R               | =       | 0xA356     | Ope  | ration:      | If $t = 0$            |

| MEMO         | RY(TBLPTR)      | =       | 0x1234     |      |              | $f \rightarrow TE$    |

| After Instru | ıction (table w | rite co | ompletion) |      |              | If t = 1              |

| REG          | •               | =       | 0xAA       |      |              | $f \rightarrow TE$    |

| TBLAT        | H               | =       | 0x12       |      |              | TBLAT                 |

| TBLAT        | L               | =       | 0x34       |      |              | If i = 1              |

| TBLPT        | R               | =       | 0xA357     |      |              | TBLP                  |

| MEMO         | RY(TBLPTR)      | =       | 0x5678     |      |              | If $i = 0$            |

| Example2:    | TABLRD          | 0, 0    | , REG ;    |      |              | TBLP                  |

| Before Inst  | ruction         |         |            | Stat | us Affected: | None                  |

| REG          |                 | =       | 0x53       | Enc  | oding:       | 1010                  |

| TBLAT        | Н               | =       | 0xAA       |      | ·            | 4 1-                  |

| TBLAT        | L               | =       | 0x55       | Des  | cription:    | 1. Lo                 |

| TBLPT        | R               | =       | 0xA356     |      |              | la <sup>.</sup><br>If |

| MEMO         | RY(TBLPTR)      | =       | 0x1234     |      |              | If                    |

| After Instru | ction (table w  | rite co | ompletion) |      |              | 2. Th                 |

| REG          | •               | =       | 0x55       |      |              | te                    |

| TBLAT        | H               | =       | 0x12       |      |              | lo                    |

| TBLAT        | L               | =       | 0x34       |      |              | If                    |

| TBLPT        | R               | =       | 0xA356     |      |              | pr                    |

| MEMO         | RY(TBLPTR)      | =       | 0x1234     |      |              | th                    |

|              |                 |         |            |      |              | If                    |

|              |                 |         |            |      |              | El                    |

|              |                 |         |            |      |              | in                    |

|              |                 |         |            |      |              | ar                    |

|              |                 |         |            | N    |              | CLR/VPP               |

|              |                 |         |            |      | ~            | e for succ            |

|              |                 |         |            |      | memo         |                       |

|              |                 |         |            |      |              | .R/VPP = \            |

|              |                 |         |            |      | the pro      | ogrammin              |

| TABLWT                                                                                                                        | Table Writ                                                                                                                                                                                                                | e                                                          |                                                                                                                |                                                                          |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|--|

| Syntax:                                                                                                                       | [ label ] TABLWT t,i,f                                                                                                                                                                                                    |                                                            |                                                                                                                |                                                                          |  |  |

| Operands:                                                                                                                     | $0 \le f \le 255$<br>$i \in [0,1]$<br>$t \in [0,1]$                                                                                                                                                                       |                                                            |                                                                                                                |                                                                          |  |  |

| Operation:                                                                                                                    | If $t = 0$ ,<br>$f \rightarrow TBLATL$ ;<br>If $t = 1$ ,<br>$f \rightarrow TBLATH$ ;<br>$TBLAT \rightarrow Prog Mem (TBLPTR)$ ;<br>If $i = 1$ ,<br>$TBLPTR + 1 \rightarrow TBLPTR$<br>If $i = 0$ ,<br>TBLPTR is unchanged |                                                            |                                                                                                                |                                                                          |  |  |

| Status Affected: None                                                                                                         |                                                                                                                                                                                                                           |                                                            |                                                                                                                |                                                                          |  |  |

| Encoding:                                                                                                                     | 1010                                                                                                                                                                                                                      | 11ti                                                       | ffff                                                                                                           | ffff                                                                     |  |  |

| Description:  1. Load value in 'f' into 16-bit ta latch (TBLAT)  If t = 1: load into high byte;  If t = 0: load into low byte |                                                                                                                                                                                                                           |                                                            |                                                                                                                | e;                                                                       |  |  |

|                                                                                                                               | ten to location If TBL program the inst If TBLF EPRON instruct                                                                                                                                                            | the pointe PTR point memoral ruction PTR point Mocalion is | of TBLAT as program in d to by TB points to early location takes two-nts to an ation, the terminated received. | memory<br>SLPTR.<br>external<br>on, then<br>cycle.<br>internal<br>en the |  |  |

|                                                                                                                               | The MCLR/VPP pin must be at the programming voltage for successful programming of internal                                                                                                                                |                                                            |                                                                                                                |                                                                          |  |  |

/DD

ng sequence of internal memory will be interrupted. A short write will occur (2 TCY). The internal memory location will not be affected.

> The TBLPTR can be automatically incremented

If i = 1; TBLPTR is not incremented

If i = 0; TBLPTR is incremented

Words:

Cycles: 2 (many if write is to on-chip

EPROM program memory)

Q Cycle Activity:

| Q1              | Q2                                                      | Q3              | Q4                                                                 |

|-----------------|---------------------------------------------------------|-----------------|--------------------------------------------------------------------|

| Decode          | Read<br>register 'f'                                    | Process<br>Data | Write<br>register<br>TBLATH or<br>TBLATL                           |

| No<br>operation | No<br>operation<br>(Table Pointer<br>on Address<br>bus) | No<br>operation | No<br>operation<br>(Table Latch on<br>Address bus,<br>WR goes low) |

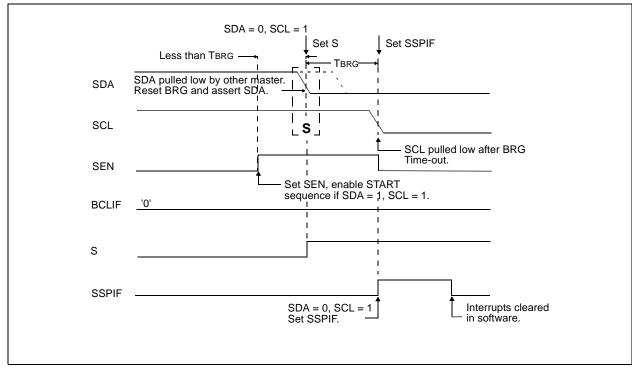

FIGURE 20-9: TIMERO EXTERNAL CLOCK TIMINGS

TABLE 20-4: TIMERO EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym  | Character              | Min            | Тур†                                         | Max | Units | Conditions |                                          |

|--------------|------|------------------------|----------------|----------------------------------------------|-----|-------|------------|------------------------------------------|

| 40           | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5Tcy + 20                                  | _   | _     | ns         |                                          |

|              |      |                        | With Prescaler | 10                                           | _   | _     | ns         |                                          |

| 41           | TtOL | T0CKI Low Pulse Width  | No Prescaler   | 0.5Tcy + 20                                  | _   | _     | ns         |                                          |

|              |      |                        | With Prescaler | 10                                           | _   | _     | ns         |                                          |

| 42           | Tt0P | T0CKI Period           |                | Greater of:<br>20 ns or <u>Tcy + 40</u><br>N | _   |       | ns         | N = prescale<br>value (1, 2, 4,,<br>256) |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated.

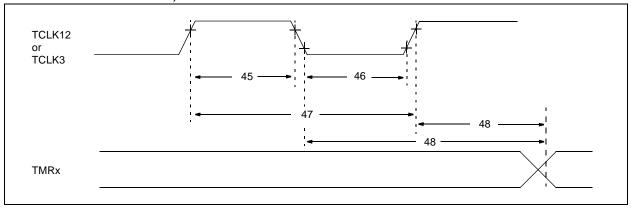

FIGURE 20-10: TIMER1, TIMER2 AND TIMER3 EXTERNAL CLOCK TIMINGS

TABLE 20-5: TIMER1, TIMER2 AND TIMER3 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       | Characteristic                                                | Min           | Тур† | Max   | Units | Conditions                         |

|--------------|-----------|---------------------------------------------------------------|---------------|------|-------|-------|------------------------------------|

| 45           | Tt123H    | TCLK12 and TCLK3 high time                                    | 0.5Tcy + 20   | _    | _     | ns    |                                    |

| 46           | Tt123L    | TCLK12 and TCLK3 low time                                     | 0.5Tcy + 20   | _    | _     | ns    |                                    |

| 47           | Tt123P    | TCLK12 and TCLK3 input period                                 | Tcy + 40<br>N | _    | _     | ns    | N = prescale<br>value (1, 2, 4, 8) |

| 48           | TckE2tmrl | Delay from selected External Clock Edge to<br>Timer increment | 2Tosc         | _    | 6Tosc |       |                                    |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated.

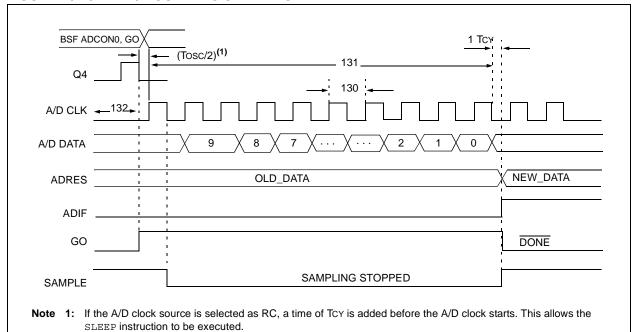

**TABLE 20-18: A/D CONVERTER CHARACTERISTICS**

| Param.<br>No. | Sym                                       | Charac                                         | teristic                          | Min            | Тур†                      | Max            | Units    | Conditions                                                              |

|---------------|-------------------------------------------|------------------------------------------------|-----------------------------------|----------------|---------------------------|----------------|----------|-------------------------------------------------------------------------|

| A01           | NR                                        | Resolution                                     |                                   | _              | _                         | 10             | bit      | VREF+ = VDD = 5.12V,<br>$VSS \le VAIN \le VREF+$                        |

|               |                                           |                                                |                                   |                | _                         | 10             | bit      | $(VREF+ - VREF-) \ge 3.0V$ ,<br>$VREF- \le VAIN \le VREF+$              |

| A02           | EABS                                      | Absolute error                                 |                                   | _              | _                         | < ±1           | LSb      | VREF+ = VDD = 5.12V,<br>$VSS \le VAIN \le VREF+$                        |

|               |                                           |                                                |                                   | _              | _                         | < ±1           | LSb      | $(VREF+ - VREF-) \ge 3.0V$ ,<br>$VREF- \le VAIN \le VREF+$              |

| A03           | EIL                                       | Integral linearity error                       |                                   | _              | _                         | < ±1           | LSb      | VREF+ = VDD = 5.12V,<br>$VSS \le VAIN \le VREF+$                        |

|               |                                           |                                                |                                   | _              | _                         | < ±1           | LSb      | $(VREF+ - VREF-) \ge 3.0V$ ,<br>$VREF- \le VAIN \le VREF+$              |

| A04           | EDL                                       | Differential linear                            | ity error                         | _              | _                         | < ±1           | LSb      | VREF+ = VDD = 5.12V,<br>$VSS \le VAIN \le VREF+$                        |

|               |                                           |                                                |                                   | _              | _                         | < ±1           | LSb      | $(VREF+ - VREF-) \ge 3.0V$ ,<br>$VREF- \le VAIN \le VREF+$              |

| A05           | EFS                                       | S Full scale error                             |                                   | _              | _                         | < ±1           | LSb      | VREF+ = VDD = 5.12V,<br>$VSS \le VAIN \le VREF+$                        |

|               |                                           |                                                |                                   |                | _                         | < ±1           | LSb      | $(VREF+ \longrightarrow VREF-) \ge 3.0V,$<br>$VREF- \le VAIN \le VREF+$ |

| A06           | EOFF                                      | Offset error                                   |                                   | _              | _                         | < ±1           | LSb      | VREF+ = VDD = 5.12V,<br>$VSS \le VAIN \le VREF+$                        |

|               |                                           |                                                |                                   |                | _                         | < ±1           | LSb      | $(VREF+ \longrightarrow VREF-) \ge 3.0V,$<br>$VREF- \le VAIN \le VREF+$ |

| A10           | _                                         | Monotonicity                                   |                                   | _              | guaranteed <sup>(3)</sup> |                |          | $Vss \le Vain \le Vref$                                                 |

| A20           | VREF                                      | Reference voltage<br>(VREF+ — VREF-)           |                                   | VO             | _                         |                | <b>V</b> | VREF delta when changing voltage levels on VREF inputs                  |

| A20A          |                                           |                                                |                                   | 3V             | _                         | _              | V        | Absolute minimum electrical spec. to ensure 10-bit accuracy             |

| A21           | VREF+                                     | Reference voltage high                         |                                   | Avss<br>+ 3.0V | _                         | AVDD +<br>0.3V | V        |                                                                         |

| A22           | VREF-                                     | Reference voltage low                          |                                   | Avss -<br>0.3V | _                         | AVDD -<br>3.0V | V        |                                                                         |

| A25           | Vain                                      | Analog input voltage                           |                                   | Avss -<br>0.3V | _                         | Vref +<br>0.3V | V        |                                                                         |

| A30           | ZAIN                                      | Recommended impedance of analog voltage source |                                   | _              | _                         | 10.0           | kΩ       |                                                                         |

| A40           | IAD                                       |                                                | A/D conversion PIC17 <b>C</b> XXX |                | 180                       |                | μΑ       | Average current consumption when                                        |

|               |                                           | current (VDD) PIC17LCXXX                       |                                   | _              | 90                        | _              | μΑ       | A/D is on (Note 1)                                                      |

| A50           | IREF                                      | VREF input current (Note 2)                    |                                   | 10             | _                         | 1000           | μА       | During VAIN acquisition.  Based on differential of VHOLD to VAIN        |

|               | Date in "Tim" column is at EV 25°C unless |                                                |                                   | _              | _                         | 10             | μΑ       | During A/D conversion cycle                                             |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated.

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

- 2: VREF current is from RG0 and RG1 pins or AVDD and AVSs pins, whichever is selected as reference input.

- 3: The A/D conversion result never decreases with an increase in the Input Voltage and has no missing codes.

FIGURE 20-23: A/D CONVERSION TIMING

**TABLE 20-19: A/D CONVERSION REQUIREMENTS**

| Param.<br>No.            | Sym  | Characteristic                                            |                     | Min      | Тур†   | Max | Units                   | Conditions                                                                                                                                                                                              |

|--------------------------|------|-----------------------------------------------------------|---------------------|----------|--------|-----|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130 TAD A/D clock period |      | PIC17 <b>C</b> XXX                                        | 1.6                 | _        | _      | μS  | Tosc based, VREF ≥ 3.0V |                                                                                                                                                                                                         |

|                          |      |                                                           | PIC17 <b>LC</b> XXX | 3.0      | _      | _   | μS                      | Tosc based, VREF full range                                                                                                                                                                             |

|                          |      |                                                           | PIC17 <b>C</b> XXX  | 2.0      | 4.0    | 6.0 | μS                      | A/D RC mode                                                                                                                                                                                             |

|                          |      |                                                           | PIC17 <b>LC</b> XXX | 3.0      | 6.0    | 9.0 | μS                      | A/D RC mode                                                                                                                                                                                             |

| 131                      | TCNV | Conversion time (not including acquisition time) (Note 1) |                     | 11       | _      | 12  | Tad                     |                                                                                                                                                                                                         |

| 132                      | TACQ | Acquisition time                                          |                     | (Note 2) | 20     | _   | μS                      |                                                                                                                                                                                                         |

|                          |      |                                                           |                     | 10       | _      |     | μs                      | The minimum time is the amplifier settling time. This may be used if the "new" input voltage has not changed by more than 1LSb (i.e., 5 mV @ 5.12V) from the last sampled voltage (as stated on CHOLD). |

| 134                      | Tgo  | Q4 to ADCLK start                                         |                     | _        | Tosc/2 | _   |                         | If the A/D clock source is selected as RC, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                        |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated.

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 16.1 for minimum conditions when input voltage has changed more than 1 LSb.

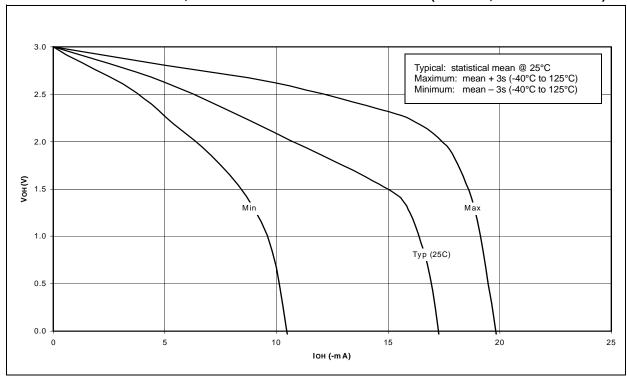

FIGURE 21-19: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 3V, -40°C TO +125°C)

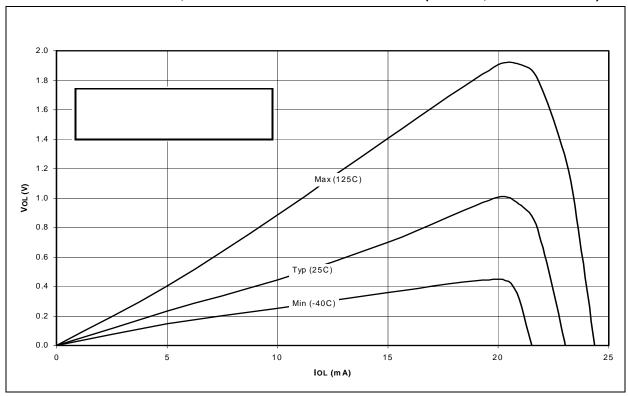

FIGURE 21-20: TYPICAL, MINIMUM AND MAXIMUM Vol vs. Iol (VDD = 3V, -40°C TO +125°C)

# PIC17C7XX

| Bus Collision During a RESTART Condition | 173    | Configuration                              |                                         |

|------------------------------------------|--------|--------------------------------------------|-----------------------------------------|

| Bus Collision During a START Condition   | 171    | Bits                                       | 192                                     |

| Bus Collision During a STOP Condition    | 174    | Locations                                  | 192                                     |

| Bus Collision Interrupt Enable, BCLIE    | 36     | Oscillator                                 | 17, 192                                 |

| Bus Collision Interrupt Flag bit, BCLIF  | 38     | Word                                       | 191                                     |

| C                                        |        | CPFSEQ                                     | 209                                     |

| C                                        | 11, 51 | CPFSGT                                     | 209                                     |

| CA1/PR3                                  | 102    | CPFSLT                                     | 210                                     |

| CA1ED0                                   | 101    | CPUSTA                                     | 52, 194                                 |

| CA1ED1                                   | 101    | Crystal Operation, Overtone Crystals       | 18                                      |

| CA1IE                                    | 35     | Crystal or Ceramic Resonator Operation     | 18                                      |

| CA1IF                                    | 37     | Crystal Oscillator                         | 17                                      |

| CA1OVF                                   | 102    | D                                          |                                         |

| CA2ED0                                   | 101    | D/Ā                                        | 134                                     |

| CA2ED1                                   | 101    | Data Memory                                |                                         |

| CA2H                                     |        | GPR                                        | 43, 46                                  |

| CA2IE                                    | *      | Indirect Addressing                        | ,                                       |

| CA2IF                                    | ,      | Organization                               |                                         |

| CA2L                                     | ,      | SFR                                        |                                         |

| CA2OVF                                   | ,      | Data Memory Banking                        |                                         |

| CA3H                                     |        | Data/Address bit, D/A                      |                                         |

| CA3IE                                    |        | DAW                                        |                                         |

| CA3IF                                    |        | DC                                         |                                         |

| CA3L                                     |        | DDRB                                       | ,                                       |

| CA4H                                     |        | DDRC                                       | , -,                                    |

| CA4IE                                    |        | DDRD                                       |                                         |

| CA4IF                                    |        | DDRE                                       | -, -, -                                 |

| Calculating Baud Rate Error              |        | DDRF                                       | , ,                                     |

| CALL                                     |        | DDRG                                       |                                         |

| Capacitor Selection                      |        | DECF                                       | • • • • • • • • • • • • • • • • • • • • |

| Ceramic Resonators                       | 18     | DECFSNZ                                    |                                         |

| Crystal Oscillator                       |        | DECFSZ                                     |                                         |

| Capture                                  |        | Delay From External Clock Edge             |                                         |

| Capture Sequence to Read Example         |        | Digit Borrow                               |                                         |

| Capture1                                 | 110    | Digit Carry (DC)                           |                                         |

| Mode                                     | 101    | Duty Cycle                                 |                                         |

| Overflow                                 |        | F                                          | 107                                     |

| Capture1 Interrupt                       | ,      | Electrical Characteristics                 |                                         |

| Capture2                                 |        | PIC17C752/756                              |                                         |

| Mode                                     | 101    | Absolute Maximum Ratings                   | 230                                     |

| Overflow                                 |        | Capture Timing                             |                                         |

| Capture2 Interrupt                       | - ,    | CLKOUT and I/O Timing                      |                                         |

| Capture3 Interrupt Enable, CA3IE         |        | DC Characteristics                         |                                         |

| Capture3 Interrupt Flag bit, CA3IF       |        | External Clock Timing                      |                                         |

| Capture4 Interrupt Enable, CA4IE         |        | Memory Interface Read Timing               |                                         |

| Capture4 Interrupt Flag bit, CA4IF       |        | Memory Interface Write Timing              |                                         |

| Carry (C)                                |        | Parameter Measurement Information          |                                         |

| Ceramic Resonators                       |        | Reset, Watchdog Timer, Oscillator Start-up |                                         |

| Circular Buffer                          |        | Timer and Power-up Timer Timing            |                                         |

| CKE                                      |        | Timer Clock Timing                         |                                         |

| CKP                                      | _      | Timer1, Timer2 and Timer3 Clock Timing     |                                         |

| Clearing the Prescaler                   |        | Timing Parameter Symbology                 |                                         |

| Clock Polarity Select bit, CKP           |        | USART Module Synchronous Receive Tim       |                                         |

| Clock/Instruction Cycle (Figure)         |        | USART Module Synchronous Transmission      | •                                       |

| Clocking Scheme/Instruction Cycle        |        | Timing                                     |                                         |

| CLRF                                     |        | EPROM Memory Access Time Order Suffix      |                                         |

| CLRWDT                                   |        | Errata                                     |                                         |

| Code Examples                            | 200    | Extended Microcontroller                   |                                         |

| Indirect Addressing                      | 55     | Extended Microcontroller Mode              |                                         |

| Loading the SSPBUF register              |        | External Memory Interface                  |                                         |

| •                                        |        | External Program Memory Waveforms          |                                         |

| Saving Status and WREG in RAM Table Read |        | External Frogram Memory Wavelonis          | 40                                      |

| Table Write                              |        |                                            |                                         |

| Code Protection                          |        |                                            |                                         |

| COME                                     | 195    |                                            |                                         |

# PIC17C7XX

| SEEVAL Evaluation and Programming System | 236          | SSPIE                                        | 36            |

|------------------------------------------|--------------|----------------------------------------------|---------------|

| Serial Clock, SCK                        |              | SSPIF                                        | 38, 145       |

| Serial Clock, SCL                        | 144          | SSPM3:SSPM0                                  | 135           |

| Serial Data Address, SDA                 | 144          | SSPOV                                        | 135, 144, 162 |

| Serial Data In, SDI                      | 137          | SSPSTAT                                      | 50, 134, 144  |

| Serial Data Out, SDO                     | 137          | ST Input                                     | 278           |

| SETF                                     | 224          | Stack                                        |               |

| SFR                                      | 198          | Operation                                    | 54            |

| SFR (Special Function Registers)         | 43           | Pointer                                      | 54            |

| SFR As Source/Destination                |              | Stack                                        | 43            |

| Signed Math                              | 11           | START bit (S)                                | 134           |

| Slave Select Synchronization             | 140          | START Condition Enabled bit, SAE             | 136           |

| Slave Select, SS                         | 137          | STKAV                                        | 52, 54        |

| SLEEP                                    | 194, 225     | STOP bit (P)                                 | 134           |

| SLEEP Mode, All Peripherals Disabled     | 273          | STOP Condition Enable bit                    | 136           |

| SLEEP Mode, BOR Enabled                  | 273          | SUBLW                                        | 225           |

| SMP                                      |              | SUBWF                                        | 226           |

| Software Simulator (MPLAB SIM)           | 234          | SUBWFB                                       | 226           |

| SPBRG 1                                  | 26, 130, 132 | SWAPF                                        |               |

| SPBRG1                                   | 27, 48       | Synchronous Master Mode                      |               |

| SPBRG2                                   | ,            | Synchronous Master Reception                 |               |

| SPE                                      |              | Synchronous Master Transmission              |               |

| Special Features of the CPU              |              | Synchronous Serial Port                      |               |

| Special Function Registers               | 43, 198      | Synchronous Serial Port Enable bit, SSPEN    |               |

| Summary                                  |              | Synchronous Serial Port Interrupt            |               |

| Special Function Registers, File Map     | 47           | Synchronous Serial Port Interrupt Enable, SS | PIE 36        |

| SPI                                      |              | Synchronous Serial Port Mode Select bits,    |               |

| Master Mode                              |              | SSPM3:SSPM0                                  |               |

| Serial Clock                             |              | Synchronous Slave Mode                       | 131           |

| Serial Data In                           |              | Т                                            |               |

| Serial Data Out                          |              | T0CKI                                        |               |

| Serial Peripheral Interface (SPI)        |              | T0CKI Pin                                    |               |

| Slave Select                             |              | T0CKIE                                       |               |

| SPI clock                                |              | T0CKIF                                       |               |

| SPI Mode                                 |              | T0CS                                         |               |

| SPI Clock Edge Select, CKE               |              | T0IE                                         |               |

| SPI Data Input Sample Phase Select, SMP  |              | TOIF                                         | _             |

| SPI Master/Slave Connection              | 138          | T0SE                                         |               |

| SPI Module  Master/Slave Connection      | 100          | TOSTA                                        |               |

| Slave Mode                               |              | T16                                          |               |

| Slave Select Synchronization             |              | Table Latch                                  |               |

| Slave Synch Timing                       |              | Table Pointer                                | 55            |

| SS                                       |              | Table Read                                   | 0.4           |

| SSP                                      |              | Example                                      |               |

| Block Diagram (SPI Mode)                 |              | . 45.5                                       |               |

| SPI Mode                                 |              | TLRD<br>Table Write                          | 64            |

| SSPADD                                   |              | Code                                         | 60            |

| SSPBUF                                   |              |                                              |               |

| SSPCON1                                  | •            | Timing To External Memory                    |               |

| SSPCON2                                  |              | TABLRD                                       |               |

| SSPSR                                    |              | TABLWT                                       | ,             |

| SSPSTAT                                  | •            | TAD                                          |               |

| SSP I <sup>2</sup> C                     | ,            | TBLATH                                       |               |

| SSP I <sup>2</sup> C Operation           | 143          | TBLATL                                       |               |

| SSP Module                               |              | TBLPTRH                                      |               |

| SPI Master Mode                          | 139          | TBLPTRL                                      |               |

| SPI Master/Slave Connection              |              | TCLK12                                       |               |

| SPI Slave Mode                           | 140          | TCLK3                                        |               |

| SSPCON1 Register                         | 143          | TCON1                                        |               |

| SSP Overflow Detect bit, SSPOV           |              | TCON2                                        | ,             |

| SSPADD                                   | 50           | TCON2,TCON3                                  |               |

| SSPBUF                                   | 50, 144      | TCON3                                        |               |

| SSPCON1                                  |              | Time-Out Sequence                            | ,             |

| SSPCON2                                  |              | Timer Resources                              |               |

| SSPEN                                    | 135          |                                              |               |