Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 16MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 454 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c752-16i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

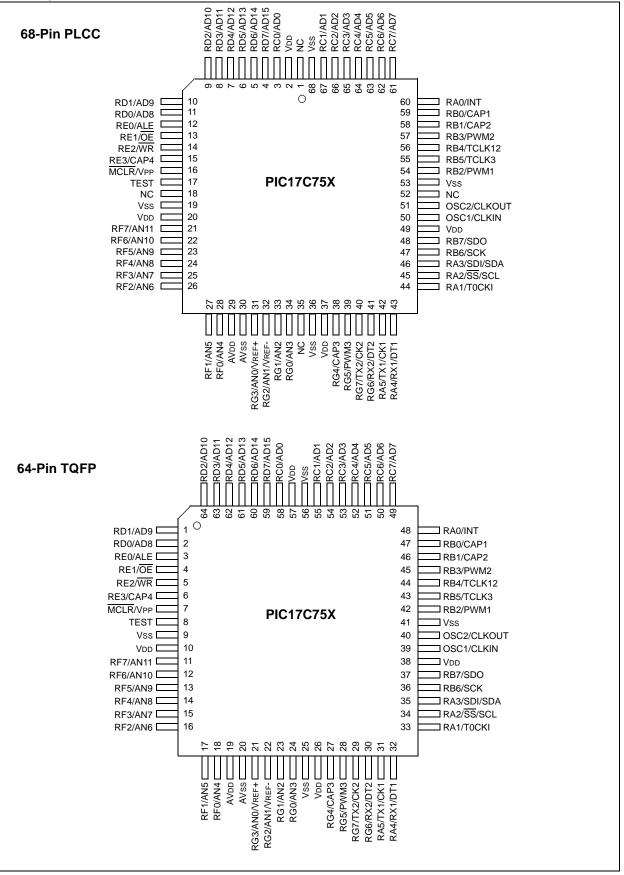

# Pin Diagrams cont.'d

| TABLE 3-1:  | PINOUT DESCRIPTIONS |             |             |             |            |                    |                |                                                                                                                                                                                                                                                           |

|-------------|---------------------|-------------|-------------|-------------|------------|--------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | PIC17C75X           |             |             | PIC17C76X   |            |                    |                |                                                                                                                                                                                                                                                           |

| Name        | DIP<br>No.          | PLCC<br>No. | TQFP<br>No. | PLCC<br>No. | QFP<br>No. | I/O/P<br>Type      | Buffer<br>Type | Description                                                                                                                                                                                                                                               |

| OSC1/CLKIN  | 47                  | 50          | 39          | 62          | 49         | Ι                  | ST             | Oscillator input in Crystal/Resonator or RC Oscillator<br>mode. External clock input in External Clock mode.                                                                                                                                              |

| OSC2/CLKOUT | 48                  | 51          | 40          | 63          | 50         | 0                  |                | Oscillator output. Connects to crystal or resonator in<br>Crystal Oscillator mode. In RC Oscillator or External<br>Clock modes, OSC2 pin outputs CLKOUT which has<br>one fourth the frequency (Fosc/4) of OSC1 and<br>denotes the instruction cycle rate. |

| MCLR/Vpp    | 15                  | 16          | 7           | 20          | 9          | I/P                | ST             | Master clear (RESET) input or Programming Voltage (VPP) input. This is the active low RESET input to the device.                                                                                                                                          |

|             |                     |             |             |             |            |                    |                | PORTA pins have individual differentiations that are listed in the following descriptions:                                                                                                                                                                |

| RA0/INT     | 56                  | 60          | 48          | 72          | 58         | I                  | ST             | RA0 can also be selected as an external inter-<br>rupt input. Interrupt can be configured to be on<br>positive or negative edge. Input only pin.                                                                                                          |

| RA1/T0CKI   | 41                  | 44          | 33          | 56          | 43         | I                  | ST             | RA1 can also be selected as an external inter-<br>rupt input and the interrupt can be configured to<br>be on positive or negative edge. RA1 can also<br>be selected to be the clock input to the Timer0<br>timer/counter. Input only pin.                 |

| RA2/SS/SCL  | 42                  | 45          | 34          | 57          | 44         | I/O <sup>(2)</sup> | ST             | RA2 can also be used as the slave select input<br>for the SPI or the clock input for the I <sup>2</sup> C bus.<br>High voltage, high current, open drain port pin.                                                                                        |

| RA3/SDI/SDA | 43                  | 46          | 35          | 58          | 45         | I/O <sup>(2)</sup> | ST             | RA3 can also be used as the data input for the SPI or the data for the I <sup>2</sup> C bus.<br>High voltage, high current, open drain port pin.                                                                                                          |

| RA4/RX1/DT1 | 40                  | 43          | 32          | 51          | 38         | I/O <sup>(1)</sup> | ST             | RA4 can also be selected as the USART1 (SCI)<br>Asynchronous Receive or USART1 (SCI)<br>Synchronous Data.<br>Output available from USART only.                                                                                                            |

| RA5/TX1/CK1 | 39                  | 42          | 31          | 50          | 37         | I/O <sup>(1)</sup> | ST             | RA5 can also be selected as the USART1 (SCI)<br>Asynchronous Transmit or USART1 (SCI)<br>Synchronous Clock.<br>Output available from USART only.                                                                                                          |

|             |                     |             |             |             |            |                    |                | PORTB is a bi-directional I/O Port with software<br>configurable weak pull-ups.                                                                                                                                                                           |

| RB0/CAP1    | 55                  | 59          | 47          | 71          | 57         | I/O                | ST             | RB0 can also be the Capture1 input pin.                                                                                                                                                                                                                   |

| RB1/CAP2    | 54                  | 58          | 46          | 70          | 56         | I/O                | ST             | RB1 can also be the Capture2 input pin.                                                                                                                                                                                                                   |

| RB2/PWM1    | 50                  | 54          | 42          | 66          | 52         | I/O                | ST             | RB2 can also be the PWM1 output pin.                                                                                                                                                                                                                      |

| RB3/PWM2    | 53                  | 57          | 45          | 69          | 55         | I/O                | ST             | RB3 can also be the PWM2 output pin.                                                                                                                                                                                                                      |

| RB4/TCLK12  | 52                  | 56          | 44          | 68          | 54         | I/O                | ST             | RB4 can also be the external clock input to Timer1 and Timer2.                                                                                                                                                                                            |

| RB5/TCLK3   | 51                  | 55          | 43          | 67          | 53         | I/O                | ST             | RB5 can also be the external clock input to Timer3.                                                                                                                                                                                                       |

| RB6/SCK     | 44                  | 47          | 36          | 59          | 46         | I/O                | ST             | RB6 can also be used as the master/slave clock for the SPI.                                                                                                                                                                                               |

| RB7/SDO     | 45                  | 48          | 37          | 60          | 47         | I/O                | ST             | RB7 can also be used as the data output for the SPI.                                                                                                                                                                                                      |

####

Legend: I = Input only; O = Output only; I/O = Input/Output; P = Power; — = Not Used; TTL = TTL input;

ST = Schmitt Trigger input

**Note 1:** The output is only available by the peripheral operation.

2: Open drain input/output pin. Pin forced to input upon any device RESET.

DS30289C-page 14

# PIC17C7XX

NOTES:

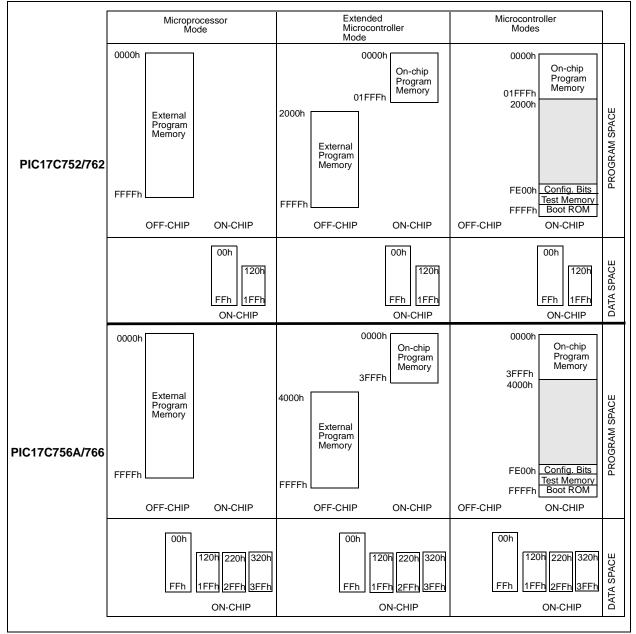

### TABLE 7-1: MODE MEMORY ACCESS

| Operating<br>Mode            | Internal<br>Program<br>Memory | Configuration Bits,<br>Test Memory,<br>Boot ROM |  |  |

|------------------------------|-------------------------------|-------------------------------------------------|--|--|

| Microprocessor               | No Access                     | No Access                                       |  |  |

| Microcontroller              | Access                        | Access                                          |  |  |

| Extended<br>Microcontroller  | Access                        | No Access                                       |  |  |

| Protected<br>Microcontroller | Access                        | Access                                          |  |  |

The PIC17C7XX can operate in modes where the program memory is off-chip. They are the Microprocessor and Extended Microcontroller modes. The Microprocessor mode is the default for an unprogrammed device.

Regardless of the processor mode, data memory is always on-chip.

#### FIGURE 7-2: MEMORY MAP IN DIFFERENT MODES

#### 7.2.2.1 ALU Status Register (ALUSTA)

The ALUSTA register contains the status bits of the Arithmetic and Logic Unit and the mode control bits for the indirect addressing register.

As with all the other registers, the ALUSTA register can be the destination for any instruction. If the ALUSTA register is the destination for an instruction that affects the Z, DC, C, or OV bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Therefore, the result of an instruction with the ALUSTA register as destination may be different than intended.

For example, the CLRF ALUSTA, F instruction will clear the upper four bits and set the Z bit. This leaves the ALUSTA register as 0000u1uu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions be used to alter the ALUSTA register, because these instructions do not affect any status bits. To see how other instructions affect the status bits, see the "Instruction Set Summary."

| Note 1: The C and DC bits operate as a borrow and |

|---------------------------------------------------|

| digit borrow bit, respectively, in subtraction.   |

| See the SUBLW and SUBWF instructions for          |

| examples.                                         |

2: The overflow bit will be set if the 2's complement result exceeds +127, or is less than -128.

The Arithmetic and Logic Unit (ALU) is capable of carrying out arithmetic or logical operations on two operands, or a single operand. All single operand instructions operate either on the WREG register, or the given file register. For two operand instructions, one of the operands is the WREG register and the other is either a file register, or an 8-bit immediate constant.

# REGISTER 7-1: ALUSTA REGISTER (ADDRESS: 04h, UNBANKED)

|         | R/W-1                                                   | R/W-1                                                          | R/W-1                                          | R/W-1                                 | R/W-x       | R/W-x                                      | R/W-x        | R/W-x |

|---------|---------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------|---------------------------------------|-------------|--------------------------------------------|--------------|-------|

|         | FS3                                                     | FS2                                                            | FS1                                            | FS0                                   | OV          | Z                                          | DC           | С     |

|         | bit 7                                                   |                                                                |                                                |                                       |             |                                            |              | bit 0 |

|         |                                                         |                                                                |                                                |                                       |             |                                            |              |       |

| bit 7-6 | 00 = Post a<br>01 = Post a                              | FSR1 Mode auto-decreme<br>auto-increme<br>value does           | ent FSR1 va<br>ent FSR1 val                    |                                       |             |                                            |              |       |

| bit 5-4 | 00 = Post a<br>01 = Post a                              | FSR0 Mode<br>auto-decreme<br>auto-increme<br>value does        | ent FSR0 va<br>ent FSR0 val                    |                                       |             |                                            |              |       |

| bit 3   | magnitude<br>1 = Overflo                                |                                                                | es the sign b<br>or signed ar                  | it (bit7) to ch                       | ange state. | licates an over                            | flow of the  | 7-bit |

| bit 2   |                                                         | sult of an arit<br>sult of an arit                             |                                                |                                       |             |                                            |              |       |

| bit 1   | For ADDWF<br>1 = A carry                                | arry/borrow b<br>and ADDLW<br>-out from the<br>ry-out from the | instructions.<br>e 4th Iow ord                 |                                       |             | ed                                         |              |       |

|         | Note:                                                   | For borrow,                                                    | the polarity i                                 | s reversed.                           |             |                                            |              |       |

| bit 0   | C: Carry/bo                                             | orrow bit                                                      |                                                |                                       |             |                                            |              |       |

|         | complement<br>For rotate (<br>source reg<br>1 = A carry | nt of the seco<br>(RRCF, RLCF)                                 | ond operand<br>) instructions<br>e Most Signif | s, this bit is lo<br>ficant bit of th | aded with e | s executed by<br>ither the high c<br>urred | U U          |       |

|         | Note:                                                   | For borrow,                                                    | the polarity i                                 | s reversed.                           |             |                                            |              |       |

|         |                                                         |                                                                |                                                |                                       |             |                                            |              |       |

|         | Legend:                                                 |                                                                |                                                |                                       |             |                                            |              |       |

|         | R = Reada                                               | ble bit                                                        | W = W                                          | ritable bit                           | U = Unim    | plemented bit                              | , read as '0 | ,     |

'1' = Bit is set

- n = Value at POR Reset

x = Bit is unknown

'0' = Bit is cleared

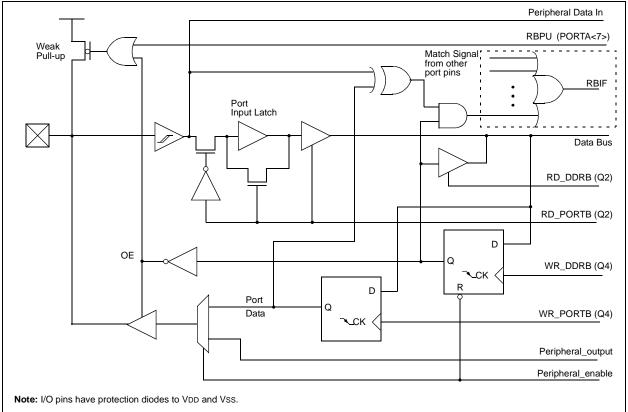

Example 10-2 shows an instruction sequence to initialize PORTB. The Bank Select Register (BSR) must be selected to Bank 0 for the port to be initialized. The following example uses the MOVLB instruction to load the BSR register for bank selection.

#### EXAMPLE 10-2: INITIALIZING PORTB

| MOVLB | 0      |   | ; Select Bank 0            |

|-------|--------|---|----------------------------|

| CLRF  | PORTB, | F | ; Init PORTB by clearing   |

|       |        |   | ; output data latches      |

| MOVLW | 0xCF   |   | ; Value used to initialize |

|       |        |   | ; data direction           |

| MOVWF | DDRB   |   | ; Set RB<3:0> as inputs    |

|       |        |   | ; RB<5:4> as outputs       |

|       |        |   | ; RB<7:6> as inputs        |

|       |        |   |                            |

### FIGURE 10-6: BLOCK DIAGRAM OF RB3:RB2 PORT PINS

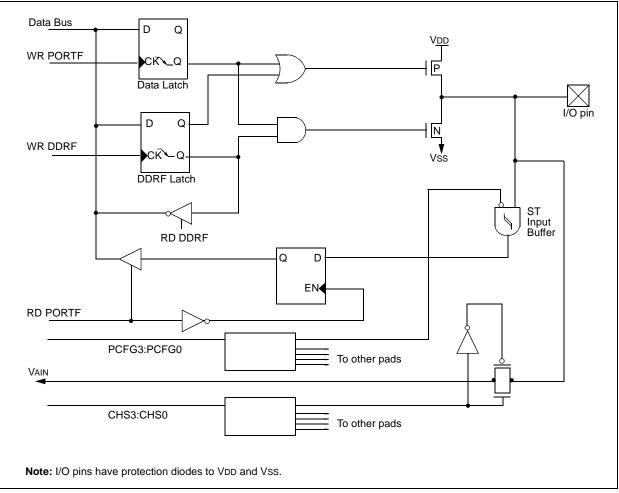

# 10.6 PORTF and DDRF Registers

PORTF is an 8-bit wide bi-directional port. The corresponding data direction register is DDRF. A '1' in DDRF configures the corresponding port pin as an input. A '0' in the DDRF register configures the corresponding port pin as an output. Reading PORTF reads the status of the pins, whereas writing to PORTF will write to the respective port latch.

All eight bits of PORTF are multiplexed with 8 channels of the 10-bit A/D converter.

Upon RESET, the entire Port is automatically configured as analog inputs and must be configured in software to be a digital I/O. Example 10-6 shows an instruction sequence to initialize PORTF. The Bank Select Register (BSR) must be selected to Bank 5 for the port to be initialized. The following example uses the MOVLB instruction to load the BSR register for bank selection.

#### EXAMPLE 10-6: INITIALIZING PORTF

| MOVLB | 5      |   | ; | Select Bank 5         |

|-------|--------|---|---|-----------------------|

| MOVWF | 0x0E   |   | ; | Configure PORTF as    |

| MOVWF | ADCON1 |   | ; | Digital               |

| CLRF  | PORTF, | F | ; | Initialize PORTF data |

|       |        |   | ; | latches before        |

|       |        |   | ; | the data direction    |

|       |        |   | ; | register              |

| MOVLW | 0x03   |   | ; | Value used to init    |

|       |        |   | ; | data direction        |

| MOVWF | DDRF   |   | ; | Set RF<1:0> as inputs |

|       |        |   | ; | RF<7:2> as outputs    |

|       |        |   |   |                       |

# FIGURE 10-13: BLOCK DIAGRAM OF RF7:RF0

# TABLE 10-11: PORTF FUNCTIONS

| Name     | Bit  | Buffer Type | Function                         |

|----------|------|-------------|----------------------------------|

| RF0/AN4  | bit0 | ST          | Input/output or analog input 4.  |

| RF1/AN5  | bit1 | ST          | Input/output or analog input 5.  |

| RF2/AN6  | bit2 | ST          | Input/output or analog input 6.  |

| RF3/AN7  | bit3 | ST          | Input/output or analog input 7.  |

| RF4/AN8  | bit4 | ST          | Input/output or analog input 8.  |

| RF5/AN9  | bit5 | ST          | Input/output or analog input 9.  |

| RF6/AN10 | bit6 | ST          | Input/output or analog input 10. |

| RF7/AN11 | bit7 | ST          | Input/output or analog input 11. |

Legend: ST = Schmitt Trigger input

# TABLE 10-12: REGISTERS/BITS ASSOCIATED WITH PORTF

| Address     | Name   | Bit 7        | Bit 6        | Bit 5        | Bit 4       | Bit 3       | Bit 2       | Bit 1       | Bit 0       | Value on<br>POR,<br>BOR | MCLR,<br>WDT |

|-------------|--------|--------------|--------------|--------------|-------------|-------------|-------------|-------------|-------------|-------------------------|--------------|

| 10h, Bank 5 | DDRF   | Data Dire    | ection Reg   | gister for P | ORTF        |             |             |             |             | 1111 1111               | 1111 1111    |

| 11h, Bank 5 | PORTF  | RF7/<br>AN11 | RF6/<br>AN10 | RF5/<br>AN9  | RF4/<br>AN8 | RF3/<br>AN7 | RF2/<br>AN6 | RF1/<br>AN5 | RF0/<br>AN4 | 0000 0000               | 0000 0000    |

| 15h, Bank 5 | ADCON1 | ADCS1        | ADCS0        | ADFM         | —           | PCFG3       | PCFG2       | PCFG1       | PCFG0       | 000- 0000               | 000- 0000    |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTF.

The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, Serial EEPROMs etc. The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

The SPEN (RCSTA<7>) bit has to be set in order to configure the I/O pins as the Serial Communication Interface (USART).

The USART module will control the direction of the RX/ DT and TX/CK pins, depending on the states of the USART configuration bits in the RCSTA and TXSTA registers. The bits that control I/O direction are:

- SPEN

- TXEN

- SREN

- CREN

- CSRC

### REGISTER 14-2: RCSTA1 REGISTER (ADDRESS: 13h, BANK 0) RCSTA2 REGISTER (ADDRESS: 13h, BANK 4)

|       | R/W-0                            | R/W-0                                              | R/W-0        | R/W-0         | U-0           | R-0            | R-0             | R-x        |

|-------|----------------------------------|----------------------------------------------------|--------------|---------------|---------------|----------------|-----------------|------------|

|       | SPEN                             | RX9                                                | SREN         | CREN          | _             | FERR           | OERR            | RX9D       |

|       | bit 7                            |                                                    |              |               |               |                |                 | bit 0      |

|       |                                  |                                                    |              |               |               |                |                 |            |

| bit 7 | 1 = Config                       | rial Port Enab<br>ures TX/CK a<br>port disabled    |              | pins as seria | l port pins   |                |                 |            |

| bit 6 | <b>RX9</b> : 9-bit<br>1 = Select | Receive Sele<br>s 9-bit recepti<br>s 8-bit recepti | ion          |               |               |                |                 |            |

| bit 5 |                                  | igle Receive<br>ables the rec                      |              | single byte.  | After receivi | ng the byte, t | this bit is aut | omatically |

|       |                                  | ous mode:<br>e reception<br>e reception            |              |               |               |                |                 |            |

|       | Note:                            | This bit is ig                                     | nored in syr | nchronous sla | ave receptio  | n.             |                 |            |

|       | <u>Asynchron</u><br>Don't care   | ious mode:                                         |              |               |               |                |                 |            |

| bit 4 |                                  | ntinuous Rec<br>ables the con                      |              |               | ial data.     |                |                 |            |

|       | 1 = Enable                       | ious mode:<br>e continuous i<br>es continuous      |              |               |               |                |                 |            |

|       |                                  | ous mode:<br>es continuous<br>es continuous        |              | until CREN is | cleared (Cl   | REN override   | s SREN)         |            |

| bit 3 | Unimplem                         | nented: Read                                       | as '0'       |               |               |                |                 |            |

| bit 2 |                                  | aming Error bi<br>ng error (upda<br>ming error     |              | ling RCREG    | )             |                |                 |            |

| bit 1 |                                  | Overrun Erro<br>In (cleared by<br>errun error      |              | REN)          |               |                |                 |            |

| bit 0 | <b>RX9D</b> : 9th                | bit of Receiv                                      | e Data (can  | be the softw  | are calculat  | ed parity bit) |                 |            |

|       |                                  |                                                    |              |               |               |                |                 |            |

|       | Legend:                          |                                                    |              |               |               |                |                 |            |

|       | R = Reada                        | able bit                                           | W = W        | /ritable bit  | U = Unin      | nplemented b   | oit, read as '0 | ,          |

|       | - n = Value                      | e at POR Res                                       | et '1' = B   | it is set     | '0' = Bit i   | s cleared      | x = Bit is ur   | nknown     |

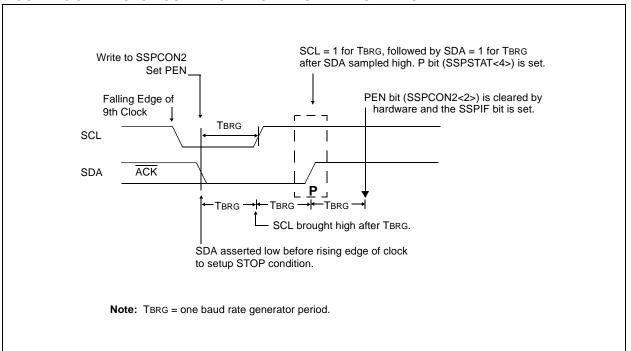

#### 15.2.14 STOP CONDITION TIMING

A STOP bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit PEN (SSPCON2<2>). At the end of a receive/ transmit the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the baud rate generator is reloaded and counts down to '0'. When the baud rate generator times out, the SCL pin will be brought high and one TBRG (baud rate generator rollover count) later, the SDA pin will be de-asserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 15-31).

Whenever the firmware decides to take control of the bus, it will first determine if the bus is busy by checking the S and P bits in the SSPSTAT register. If the bus is busy, then the CPU can be interrupted (notified) when a STOP bit is detected (i.e., bus is free).

#### 15.2.14.1 WCOL Status Flag

If the user writes the SSPBUF when a STOP sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 15-31: STOP CONDITION RECEIVE OR TRANSMIT MODE

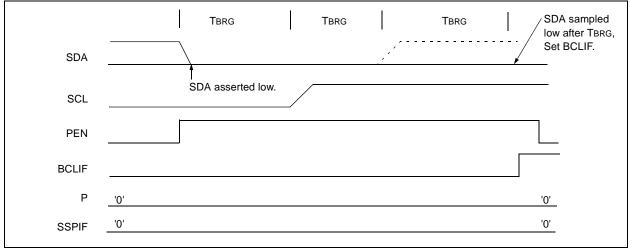

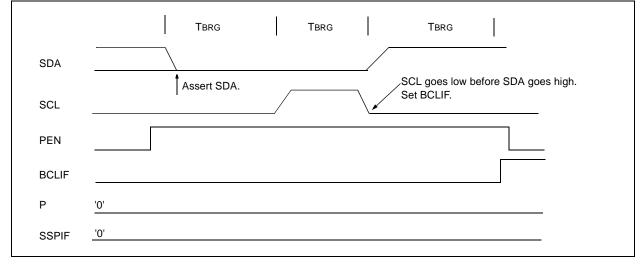

#### 15.2.18.3 Bus Collision During a STOP Condition

Bus collision occurs during a STOP condition if:

- a) After the SDA pin has been de-asserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is de-asserted, SCL is sampled low before SDA goes high.

The STOP condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the baud rate generator is loaded with SSPADD<6:0> and counts down to '0'. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0'. If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 15-40).

# FIGURE 15-40: BUS COLLISION DURING A STOP CONDITION (CASE 1)

# FIGURE 15-41: BUS COLLISION DURING A STOP CONDITION (CASE 2)

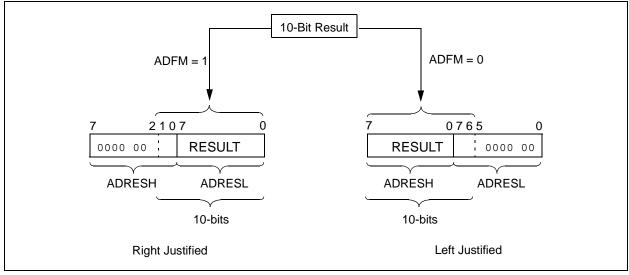

# 16.4.1 A/D RESULT REGISTERS

The ADRESH:ADRESL register pair is the location where the 10-bit A/D result is loaded at the completion of the A/D conversion. This register pair is 16-bits wide. The A/D module gives the flexibility to left or right justify the 10-bit result in the 16-bit result register. The A/D Format Select bit (ADFM) controls this justification. Figure 16-6 shows the operation of the A/D result justification. The extra bits are loaded with '0's'. When an A/ D result will not overwrite these locations (A/D disable), these registers may be used as two general purpose 8bit registers.

# 16.5 A/D Operation During SLEEP

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared, and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from

# FIGURE 16-6: A/D RESULT JUSTIFICATION

SLEEP. If the A/D interrupt is not enabled, the A/D module will then be turned off, although the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

Note: For the A/D module to operate in SLEEP, the A/D clock source must be set to RC (ADCS1:ADCS0 = 11). To allow the conversion to occur during SLEEP, ensure the SLEEP instruction immediately follows the instruction that sets the GO/DONE bit.

# 16.6 Effects of a RESET

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off, and any conversion is aborted.

The value that is in the ADRESH:ADRESL registers is not modified for a Power-on Reset. The ADRESH:ADRESL registers will contain unknown data after a Power-on Reset.

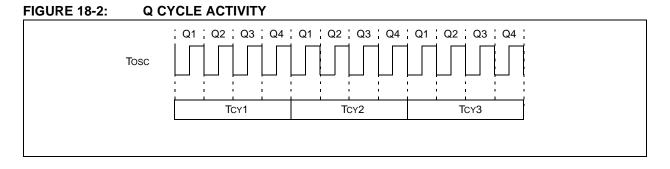

# 18.2 Q Cycle Activity

Each instruction cycle (TcY) is comprised of four Q cycles (Q1-Q4). The Q cycle is the same as the device oscillator cycle (Tosc). The Q cycles provide the timing/ designation for the Decode, Read, Process Data, Write, etc., of each instruction cycle. The following diagram shows the relationship of the Q cycles to the instruction cycle.

The four Q cycles that make up an instruction cycle (TCY) can be generalized as:

- Q1: Instruction Decode Cycle or forced No operation

- Q2: Instruction Read Cycle or No operation

- Q3: Process the Data

- Q4: Instruction Write Cycle or No operation

Each instruction will show the detailed Q cycle operation for the instruction.

| CPF                                                                                                                                                                                                                                                                                                                            | Compare f with WREG,<br>CPFSLT skip if f < WREG |                             |                                                                |                 |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------|----------------------------------------------------------------|-----------------|--|--|--|--|

| Synt                                                                                                                                                                                                                                                                                                                           | ax:                                             | [label] C                   | PFSLT f                                                        |                 |  |  |  |  |

| Ope                                                                                                                                                                                                                                                                                                                            | rands:                                          | $0 \le f \le 255$           | 5                                                              |                 |  |  |  |  |

| Ope                                                                                                                                                                                                                                                                                                                            | ration:                                         | skip if (f) <               | (f) – (WREG),<br>skip if (f) < (WREG)<br>(unsigned comparison) |                 |  |  |  |  |

| State                                                                                                                                                                                                                                                                                                                          | us Affected:                                    | None                        |                                                                |                 |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                                                                           | oding:                                          | 0011                        | 0000 fff                                                       | f ffff          |  |  |  |  |

| Description:<br>Compares the contents of data memory<br>location 'f' to the contents of WREG by<br>performing an unsigned subtraction.<br>If the contents of 'f' are less than the<br>contents of WREG, then the fetched<br>instruction is discarded and a NOP is<br>executed instead, making this a<br>two-cycle instruction. |                                                 |                             |                                                                |                 |  |  |  |  |

| Wor                                                                                                                                                                                                                                                                                                                            | ds:                                             | 1                           |                                                                |                 |  |  |  |  |

| Cycl                                                                                                                                                                                                                                                                                                                           | es:                                             | 1 (2)                       | 1 (2)                                                          |                 |  |  |  |  |

| QC                                                                                                                                                                                                                                                                                                                             | ycle Activity:                                  |                             |                                                                |                 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                | Q1                                              | Q2                          | Q3                                                             | Q4              |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                | Decode                                          | Read<br>register 'f'        | Process<br>Data                                                | No<br>operation |  |  |  |  |

| lf sk                                                                                                                                                                                                                                                                                                                          | ip:                                             |                             |                                                                |                 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                | Q1                                              | Q2                          | Q3                                                             | Q4              |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                | No<br>operation                                 | No<br>operation             | No<br>operation                                                | No<br>operation |  |  |  |  |

| <u>Exa</u>                                                                                                                                                                                                                                                                                                                     | <u>mple</u> :                                   | HERE (<br>NLESS :<br>LESS : |                                                                |                 |  |  |  |  |

| Before Instruction<br>PC = Address (HERE)<br>W = ?                                                                                                                                                                                                                                                                             |                                                 |                             |                                                                |                 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                | After Instruct<br>If REG<br>PC<br>If REG<br>PC  | < WF<br>= Ad<br>≥ WF        | REG;<br>dress (LESS)<br>REG;<br>dress (NLESS                   | )               |  |  |  |  |

| DAW               | Decimal A                                                                                                                                 | Adjust WF                                                                                                                                                                                                                                                | REG R    | egister                                     |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------|--|--|--|

| Syntax:           | [label] D                                                                                                                                 | AW f,s                                                                                                                                                                                                                                                   |          |                                             |  |  |  |

| Operands:         | 0 ≤ f ≤ 255<br>s ∈ [0,1]                                                                                                                  | 0 ≤ f ≤ 255<br>s ∈ [0,1]                                                                                                                                                                                                                                 |          |                                             |  |  |  |

| Operation:        | If [ [WREG-<br>[WREG<3:0<br>then<br>WREG<7:4                                                                                              | )> > 9]                                                                                                                                                                                                                                                  | -        |                                             |  |  |  |

|                   | If [WREG<<br>then<br>WREG<7:4<br>else<br>WREG<7:4                                                                                         | -<br>⊳ + 6→ f<7                                                                                                                                                                                                                                          | ':4>, s< | 7:4>;                                       |  |  |  |

|                   | If [WREG<3:0> > 9].OR.[DC = 1]<br>then<br>WREG<3:0> + $6 \rightarrow f$ <3:0>, s<3:0>;<br>else<br>WREG<3:0> $\rightarrow f$ <3:0>, s<3:0> |                                                                                                                                                                                                                                                          |          |                                             |  |  |  |

| Status Affected:  | С                                                                                                                                         |                                                                                                                                                                                                                                                          |          |                                             |  |  |  |

| Encoding:         | 0010 111s ffff fff                                                                                                                        |                                                                                                                                                                                                                                                          |          |                                             |  |  |  |

| Description:      | WREG, res<br>tion of two<br>BCD forma<br>packed BC<br>s = 0: Re<br>me                                                                     | DAW adjusts the eight-bit value in<br>WREG, resulting from the earlier addi-<br>tion of two variables (each in packed<br>BCD format) and produces a correct<br>packed BCD result.<br>s = 0: Result is placed in Data<br>memory location 'f' and<br>WREG. |          |                                             |  |  |  |

|                   |                                                                                                                                           | s = 1: Result is placed in Data<br>memory location 'f'.                                                                                                                                                                                                  |          |                                             |  |  |  |

| Words:            | 1                                                                                                                                         |                                                                                                                                                                                                                                                          |          |                                             |  |  |  |

| Cycles:           | 1                                                                                                                                         |                                                                                                                                                                                                                                                          |          |                                             |  |  |  |

| Q Cycle Activity: |                                                                                                                                           |                                                                                                                                                                                                                                                          |          |                                             |  |  |  |

| Q1                | Q2                                                                                                                                        | Q3                                                                                                                                                                                                                                                       |          | Q4                                          |  |  |  |

| Decode            | Read<br>register 'f'                                                                                                                      | Process<br>Data                                                                                                                                                                                                                                          | re<br>ar | Write<br>gister 'f'<br>nd other<br>becified |  |  |  |

Example: DAW REG1, 0

| Before Instr  | uctio | n    |  |

|---------------|-------|------|--|

| WREG          | =     | 0xA5 |  |

| REG1          | =     | ??   |  |

| С             | =     | 0    |  |

| DC            | =     | 0    |  |

| After Instruc | tion  |      |  |

| WREG          | =     | 0x05 |  |

| REG1          | =     | 0x05 |  |

| С             | =     | 1    |  |

| DC            | =     | 0    |  |

|               |       |      |  |

| INCF              | Incremen                                                        | tf                          |             |                       |

|-------------------|-----------------------------------------------------------------|-----------------------------|-------------|-----------------------|

| Syntax:           | [ label ]                                                       | INCF f                      | ,d          |                       |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \end{array}$ | 5                           |             |                       |

| Operation:        | (f) + 1 $\rightarrow$ (                                         | dest)                       |             |                       |

| Status Affected:  | OV, C, DC                                                       | ;, Z                        |             |                       |

| Encoding:         | 0001                                                            | 010d                        | ffff        | ffff                  |

| Description:      | The conten<br>mented. If '<br>WREG. If 'c<br>back in regi       | d' is 0, th<br>l' is 1, the | e result is | placed in             |

| Words:            | 1                                                               |                             |             |                       |

| Cycles:           | 1                                                               |                             |             |                       |

| Q Cycle Activity: |                                                                 |                             |             |                       |

| Q1                | Q2                                                              | Q3                          |             | Q4                    |

| Decode            | Read<br>register 'f'                                            | Proce<br>Dat                |             | Vrite to<br>stination |

| Example:          | INCF                                                            | CNT,                        | 1           |                       |

| Before Instr      |                                                                 |                             |             |                       |

| CNT<br>Z<br>C     | = 0xFF<br>= 0<br>= ?                                            |                             |             |                       |

| After Instruc     | tion                                                            |                             |             |                       |

| CNT<br>Z<br>C     | = 0x00<br>= 1<br>= 1                                            |                             |             |                       |

|                   |                                                                 |                             |             |                       |

| INC        | FSZ                                   | Incremen                                                                                    | t f, skip if O                                                  |                                                                                        |

|------------|---------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Synt       | ax:                                   | [ label ]                                                                                   | NCFSZ f,o                                                       | ł                                                                                      |

| Ope        | rands:                                | $0 \le f \le 255$<br>d $\in [0,1]$                                                          | 5                                                               |                                                                                        |

| Ope        | ration:                               | (f) + 1 $\rightarrow$ (skip if resu                                                         |                                                                 |                                                                                        |

| Stat       | us Affected:                          | None                                                                                        |                                                                 |                                                                                        |

| Enc        | oding:                                | 0001                                                                                        | 111d ff                                                         | ff ffff                                                                                |

| Des        | cription:                             | mented. If '<br>WREG. If 'd<br>back in regi<br>If the result<br>which is alr<br>and a NOP i | l' is 1, the res<br>ster 'f'.<br>is 0, the next<br>eady fetched | sult is placed ir<br>ult is placed<br>i instruction,<br>is discarded<br>istead, making |

| Wor        | ds:                                   | 1                                                                                           |                                                                 |                                                                                        |

| Cyc        | es:                                   | 1(2)                                                                                        |                                                                 |                                                                                        |

| QC         | ycle Activity:                        |                                                                                             |                                                                 |                                                                                        |

|            | Q1                                    | Q2                                                                                          | Q3                                                              | Q4                                                                                     |

|            | Decode                                | Read<br>register 'f'                                                                        | Process<br>Data                                                 | Write to destination                                                                   |

| lf sk      | ip:                                   |                                                                                             |                                                                 |                                                                                        |

|            | Q1                                    | Q2                                                                                          | Q3                                                              | Q4                                                                                     |

|            | No<br>operation                       | No<br>operation                                                                             | No<br>operation                                                 | No<br>operation                                                                        |

| <u>Exa</u> | <u>mple</u> :                         | NZERO                                                                                       | INCFSZ C<br>:                                                   | NT, 1                                                                                  |

|            | Before Instru<br>PC                   |                                                                                             | (HERE)                                                          |                                                                                        |

|            | After Instruct<br>CNT<br>If CNT<br>PC | = CNT +<br>= 0;                                                                             | l<br>S(ZERO)                                                    |                                                                                        |

- If CNT  $\neq$  0;

- PC = Address (NZERO)

| мо         | VLR                                    | Move Lite<br>BSR                                                                                           | eral to hi                                                      | igh nibb                                                               | le in                          |

|------------|----------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------|

| Synt       | ax:                                    | [ label ]                                                                                                  | MOVLR                                                           | k                                                                      |                                |

| Ope        | rands:                                 | $0 \le k \le 15$                                                                                           |                                                                 |                                                                        |                                |

| Ope        | ration:                                | $k \rightarrow (BSR)$                                                                                      | <7:4>)                                                          |                                                                        |                                |

| State      | us Affected:                           | None                                                                                                       |                                                                 |                                                                        |                                |

| Enc        | oding:                                 | 1011                                                                                                       | 101x                                                            | kkkk                                                                   | uuuu                           |

| Des        | cription:                              | The 4-bit lit<br>most signifi<br>Select Regi<br>4-bits of the<br>are affected<br>BSR is unc<br>will encode | cant 4-bit<br>ster (BSR<br>e Bank Se<br>d. The low<br>hanged. 1 | s of the B<br>R). Only the<br>elect Regist<br>ver half of<br>The asser | ank<br>le high<br>ster<br>the  |

| Wor        | ds:                                    | 1                                                                                                          |                                                                 |                                                                        |                                |

| Сус        | les:                                   | 1                                                                                                          |                                                                 |                                                                        |                                |

| QC         | ycle Activity:                         |                                                                                                            |                                                                 |                                                                        |                                |

|            | Q1                                     | Q2                                                                                                         | Q3                                                              |                                                                        | Q4                             |

|            | Decode                                 | Read literal<br>'k'                                                                                        | Proces<br>Data                                                  | lite                                                                   | Write<br>ral 'k' to<br>SR<7:4> |

| <u>Exa</u> | <u>mple</u> :<br>Before Instru         |                                                                                                            |                                                                 |                                                                        |                                |

|            | BSR regi<br>After Instruct<br>BSR regi | tion                                                                                                       |                                                                 |                                                                        |                                |

| MO\         | /LW Move Literal to WREG |                      |               |          |     |                  |

|-------------|--------------------------|----------------------|---------------|----------|-----|------------------|

| Synt        | ax:                      | [ label ]            | MOVLW         | / k      |     |                  |

| Ope         | rands:                   | $0 \le k \le 2$      | 55            |          |     |                  |

| Ope         | ration:                  | $k \rightarrow (WR)$ | EG)           |          |     |                  |

| Statu       | us Affected:             | None                 |               |          |     |                  |

| Enco        | oding:                   | 1011                 | 0000          | kkk      | k   | kkkk             |

| Desc        | cription:                | The eight-<br>WREG.  | bit literal ' | k' is lo | ade | d into           |

| Wor         | ds:                      | 1                    |               |          |     |                  |

| Cycl        | es:                      | 1                    |               |          |     |                  |

| QC          | cle Activity:            |                      |               |          |     |                  |

|             | Q1                       | Q2                   | Q             | 3        |     | Q4               |

|             | Decode                   | Read<br>literal 'k'  | Proce<br>Dat  |          | -   | Vrite to<br>VREG |

|             |                          |                      |               |          |     |                  |

| <u>Exar</u> | <u>mple</u> :            | MOVLW                | 0x5A          |          |     |                  |

After Instruction WREG = 0x5A

© 1998-2013 Microchip Technology Inc.

# PIC17C7XX

NOTES:

| Param<br>No. | Sym  | Characteristic         |                           | Min | Max | Units | Conditions                |

|--------------|------|------------------------|---------------------------|-----|-----|-------|---------------------------|

| 110          | Tbuf | Bus free time          | 100 kHz mode              | 4.7 | —   | ms    | Time the bus must be free |

|              |      |                        | 400 kHz mode              | 1.3 | _   | ms    | before a new transmission |

|              |      |                        | 1 MHz mode <sup>(1)</sup> | 0.5 | —   | ms    | can start                 |

| D102         | Cb   | Bus capacitive loading |                           | _   | 400 | pF    |                           |

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C$  pins.

2: A fast mode (400 KHz) I<sup>2</sup>C bus device can be used in a standard mode I<sup>2</sup>C bus system, but the parameter # 107 ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line. Parameter #102 + #107 = 1000 + 250 = 1250 ns (for 100 kHz mode) before the SCL line is released.

**3:**  $C_b$  is specified to be from 10-400pF. The minimum specifications are characterized with  $C_b$ =10pF. The rise time spec ( $t_r$ ) is characterized with  $R_p$ = $R_p$  min. The minimum fall time specification ( $t_f$ ) is characterized with  $C_b$ =10pF,and  $R_p$ = $R_p$  max. These are only valid for fast mode operation (VDD=4.5-5.5V) and where the SPM bit (SSPSTAT<7>) =1.)

4: Max specifications for these parameters are valid for falling edge only. Specs are characterized with R<sub>p</sub>=R<sub>p</sub> min and C<sub>b</sub>=400pF for standard mode, 200pF for fast mode, and 10pF for 1MHz mode.

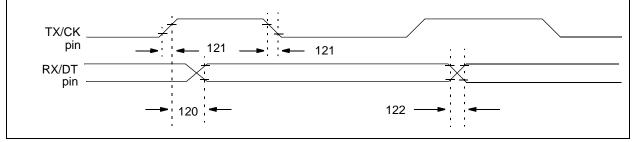

#### FIGURE 20-19: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 20-14: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                    |                     |   | Тур† | Max | Units | Conditions |

|--------------|----------|-----------------------------------|---------------------|---|------|-----|-------|------------|

| 120          | TckH2dtV | SYNC XMIT (MASTER & SLAVE)        |                     |   |      |     |       |            |

|              |          | Clock high to data out valid      | PIC17 <b>C</b> XXX  | — | —    | 50  | ns    |            |

|              |          |                                   | PIC17LCXXX          | - | —    | 75  | ns    |            |

| 121          | TckRF    | Clock out rise time and fall time | PIC17 <b>C</b> XXX  | — | —    | 25  | ns    |            |

|              |          | (Master mode)                     | PIC17 <b>LC</b> XXX | — | —    | 40  | ns    |            |

| 122          | TdtRF    | Data out rise time and fall time  | PIC17 <b>C</b> XXX  | — | —    | 25  | ns    |            |

|              |          |                                   | PIC17 <b>LC</b> XXX | _ | _    | 40  | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated.

# PIC17C7XX

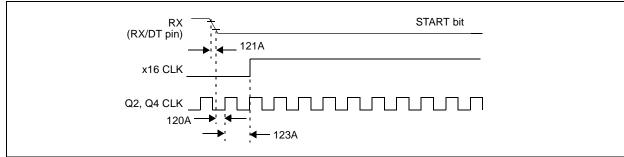

### FIGURE 20-21: USART ASYNCHRONOUS MODE START BIT DETECT

#### TABLE 20-16: USART ASYNCHRONOUS MODE START BIT DETECT REQUIREMENTS

| Param<br>No. | Sym       | Characteristic                                                 |          | Min | Тур | Max      | Unit<br>s | Conditions |

|--------------|-----------|----------------------------------------------------------------|----------|-----|-----|----------|-----------|------------|

| 120A         | TdtL2ckH  | Time to ensure that the RX pin is sampled low                  |          |     | _   | TCY      | ns        |            |

| 121A         | TdtRF     | Data rise time and fall time                                   | Receive  | _   | —   | (Note 1) | ns        |            |

|              |           |                                                                | Transmit | _   | _   | 40       | ns        |            |

| 123A         | TckH2bckL | Time from RX pin sampled low to first rising edge of x16 clock |          | _   | _   | Тсү      | ns        |            |

Note 1: Schmitt trigger will determine logic level.

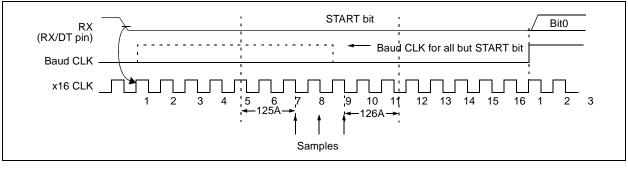

# FIGURE 20-22: USART ASYNCHRONOUS RECEIVE SAMPLING WAVEFORM

# TABLE 20-17: USART ASYNCHRONOUS RECEIVE SAMPLING REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                                  | Min | Тур | Max | Unit<br>s | Conditions |

|--------------|----------|-------------------------------------------------|-----|-----|-----|-----------|------------|

| 125A         | TdtL2ckH | Setup time of RX pin to first data sampled      | TCY | —   |     | ns        |            |

| 126A         | TdtL2ckH | Hold time of RX pin from last data sam-<br>pled | Тсү |     |     | ns        |            |

# APPENDIX A: MODIFICATIONS

The following is the list of modifications over the PIC16CXX microcontroller family:

- Instruction word length is increased to 16-bit. This allows larger page sizes, both in program memory (8 Kwords verses 2 Kwords) and register file (256 bytes versus 128 bytes).

- 2. Four modes of operation: Microcontroller, Protected Microcontroller, Extended Microcontroller, and Microprocessor.

- 22 new instructions. The MOVF, TRIS and OPTION instructions are no longer supported.

- Four new instructions (TLRD, TLWT, TABLRD, TABLWT) for transferring data between data memory and program memory. They can be used to "self program" the EPROM program memory.

- Single cycle data memory to data memory transfers possible (MOVPF and MOVFP instructions). These instructions do not affect the Working register (WREG).

- 6. W register (WREG) is now directly addressable.

- 7. A PC high latch register (PCLATH) is extended to 8-bits. The PCLATCH register is now both readable and writable.

- 8. Data memory paging is redefined slightly.

- 9. DDR registers replace function of TRIS registers.

- 10. Multiple Interrupt vectors added. This can decrease the latency for servicing interrupts.

- 11. Stack size is increased to 16 deep.

- 12. BSR register for data memory paging.

- 13. Wake-up from SLEEP operates slightly differently.

- 14. The Oscillator Start-Up Timer (OST) and Power-Up Timer (PWRT) operate in parallel and not in series.

- 15. PORTB interrupt-on-change feature works on all eight port pins.

- 16. TMR0 is 16-bit, plus 8-bit prescaler.

- 17. Second indirect addressing register added (FSR1 and FSR2). Control bits can select the FSR registers to auto-increment, auto-decrement, remain unchanged after an indirect address.

- 18. Hardware multiplier added (8 x 8  $\rightarrow$  16-bit).

- 19. Peripheral modules operate slightly differently.

- 20. A/D has both VREF+ and VREF- inputs.

- 21. USARTs do not implement BRGH feature.

- 22. Oscillator modes slightly redefined.

- 23. Control/Status bits and registers have been placed in different registers and the control bit for globally enabling interrupts has inverse polarity.

- 24. In-circuit serial programming is implemented differently.

# APPENDIX B: COMPATIBILITY

To convert code written for PIC16CXXX to PIC17CXXX, the user should take the following steps:

- 1. Remove any TRIS and OPTION instructions, and implement the equivalent code.

- 2. Separate the Interrupt Service Routine into its four vectors.

- Replace: MOVF REG1, W with:

- MOVFP REG1, WREG 4. Replace: MOVF REG1, W MOVWF REG2 with: MOVPF REG1, REG2 ; Addr(REG1)<20h or MOVFP REG1, REG2 ; Addr(REG2)<20h

| Note: | If REG1 a | If REG1 and REG2 are both at addresses |        |              |     |  |  |  |  |

|-------|-----------|----------------------------------------|--------|--------------|-----|--|--|--|--|

|       | greater t | hen 20h                                | n, two | instructions | are |  |  |  |  |

|       | required. |                                        |        |              |     |  |  |  |  |

|       | MOVFP     | REG1,                                  | WREG   | ;            |     |  |  |  |  |

|       | MOVPF     | WREG,                                  | REG2   | ;            |     |  |  |  |  |

- 5. Ensure that all bit names and register names are updated to new data memory map locations.

- 6. Verify data memory banking.

- 7. Verify mode of operation for indirect addressing.

- 8. Verify peripheral routines for compatibility.

- 9. Weak pull-ups are enabled on RESET.

- 10. WDT time-outs always reset the device (in run or SLEEP mode).

# B.1 Upgrading from PIC17C42 Devices

To convert code from the PIC17C42 to all the other PIC17CXXX devices, the user should take the following steps.

- 1. If the hardware multiply is to be used, ensure that any variables at address 18h and 19h are moved to another address.

- 2. Ensure that the upper nibble of the BSR was not written with a non-zero value. This may cause unexpected operation since the RAM bank is no longer 0.

- 3. The disabling of global interrupts has been enhanced, so there is no additional testing of the GLINTD bit after a BSF CPUSTA, GLINTD instruction.