Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 33MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 454 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c752-33i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 5-4:             | INITIALIZATION CONDITIONS FOR SPECIAL FUNCTION REGISTERS (CONTINUED) |                                   |                         |                                         |  |  |  |  |

|------------------------|----------------------------------------------------------------------|-----------------------------------|-------------------------|-----------------------------------------|--|--|--|--|

| Register               | Address                                                              | Power-on Reset<br>Brown-out Reset | MCLR Reset<br>WDT Reset | Wake-up from SLEEP<br>through Interrupt |  |  |  |  |

| Bank 1                 |                                                                      |                                   |                         |                                         |  |  |  |  |

| DDRC <sup>(5)</sup>    | 10h                                                                  | 1111 1111                         | 1111 1111               | սսսս սսսս                               |  |  |  |  |

| PORTC <sup>(4,5)</sup> | 11h                                                                  | xxxx xxxx                         | uuuu uuuu               | นนนน นนนน                               |  |  |  |  |

| DDRD <sup>(5)</sup>    | 12h                                                                  | 1111 1111                         | 1111 1111               | นนนน นนนน                               |  |  |  |  |

| PORTD <sup>(4,5)</sup> | 13h                                                                  | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| DDRE <sup>(5)</sup>    | 14h                                                                  | 1111                              | 1111                    | uuuu                                    |  |  |  |  |

| PORTE <sup>(4,5)</sup> | 15h                                                                  | xxxx                              | uuuu                    | uuuu                                    |  |  |  |  |

| PIR1                   | 16h                                                                  | x000 0010                         | u000 0010               | սսսս սսսս(1)                            |  |  |  |  |

| PIE1                   | 17h                                                                  | 0000 0000                         | 0000 0000               | uuuu uuuu                               |  |  |  |  |

| Bank 2                 |                                                                      |                                   |                         |                                         |  |  |  |  |

| TMR1                   | 10h                                                                  | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| TMR2                   | 11h                                                                  | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| TMR3L                  | 12h                                                                  | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| TMR3H                  | 13h                                                                  | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| PR1                    | 14h                                                                  | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| PR2                    | 15h                                                                  | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| PR3/CA1L               | 16h                                                                  | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| PR3/CA1H               | 17h                                                                  | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| Bank 3                 |                                                                      |                                   |                         |                                         |  |  |  |  |

| PW1DCL                 | 10h                                                                  | xx                                | uu                      | uu                                      |  |  |  |  |

| PW2DCL                 | 11h                                                                  | xx0                               | uu0                     | uuu                                     |  |  |  |  |

| PW1DCH                 | 12h                                                                  | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| PW2DCH                 | 13h                                                                  | xxxx xxxx                         | uuuu uuuu               | นนนน นนนน                               |  |  |  |  |

| CA2L                   | 14h                                                                  | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| CA2H                   | 15h                                                                  | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| TCON1                  | 16h                                                                  | 0000 0000                         | 0000 0000               | uuuu uuuu                               |  |  |  |  |

| TCON2                  | 17h                                                                  | 0000 0000                         | 0000 0000               | uuuu uuuu                               |  |  |  |  |

### TABLE 5-4: INITIALIZATION CONDITIONS FOR SPECIAL FUNCTION REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented, read as '0', q = value depends on condition

Note 1: One or more bits in INTSTA, PIR1, PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GLINTD bit is cleared, the PC is loaded with the interrupt vector.

3: See Table 5-3 for RESET value of specific condition.

4: This is the value that will be in the port output latch.

**5:** When the device is configured for Microprocessor or Extended Microcontroller mode, the operation of this port does not rely on these registers.

6: On any device RESET, these pins are configured as inputs.

### 5.1.5 BROWN-OUT RESET (BOR)

PIC17C7XX devices have on-chip Brown-out Reset circuitry. This circuitry places the device into a RESET when the device voltage falls below a trip point (BVDD). This ensures that the device does not continue program execution outside the valid operation range of the device. Brown-out Resets are typically used in AC line applications, or large battery applications, where large loads may be switched in (such as automotive).

| Note: | Before using the on-chip Brown-out for a |

|-------|------------------------------------------|

|       | voltage supervisory function, please     |

|       | review the electrical specifications to  |

|       | ensure that they meet your requirements. |

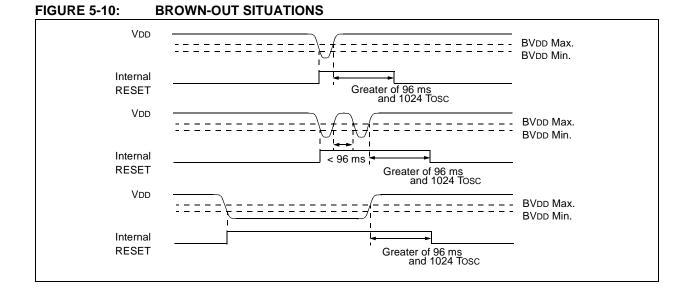

The BODEN configuration bit can disable (if clear/ programmed), or enable (if set) the Brown-out Reset circuitry. If VDD falls below BVDD (typically 4.0 V, paramter #D005 in electrical specification section), for greater than parameter #35, the Brown-out situation will reset the chip. A RESET is not guaranteed to occur if VDD falls below BVDD for less than paramter #35. The chip will remain in Brown-out Reset until VDD rises above BVDD. The Power-up Timer and Oscillator Startup Timer will then be invoked. This will keep the chip in RESET the greater of 96 ms and 1024 Tosc. If VDD drops below BVDD while the Power-up Timer/Oscillator Start-up Timer is running, the chip will go back into a Brown-out Reset. The Power-up Timer/Oscillator Startup Timer will be initialized. Once VDD rises above BVDD, the Power-up Timer/Oscillator Start-up Timer will start their time delays. Figure 5-10 shows typical Brown-out situations.

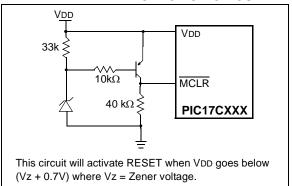

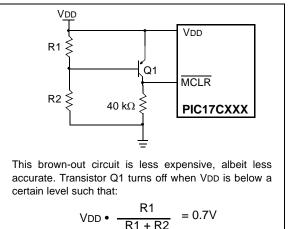

In some applications, the Brown-out Reset trip point of the device may not be at the desired level. Figure 5-8 and Figure 5-9 are two examples of external circuitry that may be implemented. Each needs to be evaluated to determine if they match the requirements of the application.

### EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

FIGURE 5-9:

### EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

© 1998-2013 Microchip Technology Inc.

### 6.2 Peripheral Interrupt Enable Register1 (PIE1) and Register2 (PIE2)

These registers contains the individual enable bits for the peripheral interrupts.

### REGISTER 6-2: PIE1 REGISTER (ADDRESS: 17h, BANK 1)

|       |                                | •                               |            | ,            | ,            |              |                 |       |

|-------|--------------------------------|---------------------------------|------------|--------------|--------------|--------------|-----------------|-------|

|       | R/W-0                          | R/W-0                           | R/W-0      | R/W-0        | R/W-0        | R/W-0        | R/W-0           | R/W-0 |

|       | RBIE                           | TMR3IE                          | TMR2IE     | TMR1IE       | CA2IE        | CA1IE        | TX1IE           | RC1IE |

|       | bit 7                          |                                 |            |              |              |              |                 | bit 0 |

|       |                                |                                 |            |              |              |              |                 |       |

| bit 7 |                                | RTB Interrupt                   | •          |              |              |              |                 |       |

|       |                                | e PORTB inte<br>e PORTB inte    |            |              |              |              |                 |       |

| bit 6 |                                | MR3 Interrup                    | •          | •            |              |              |                 |       |

| bit 0 |                                | • TMR3 interr                   |            |              |              |              |                 |       |

|       | 0 = Disable                    | e TMR3 inter                    | rupt       |              |              |              |                 |       |

| bit 5 |                                | MR2 Interrup                    |            |              |              |              |                 |       |

|       |                                | e TMR2 interr<br>e TMR2 inter   | •          |              |              |              |                 |       |

| bit 4 |                                | MR1 Interrup                    | •          |              |              |              |                 |       |

| DIL 4 |                                | • TMR1 interr                   |            |              |              |              |                 |       |

|       |                                | e TMR1 inter                    | •          |              |              |              |                 |       |

| bit 3 |                                | pture2 Interr                   |            | oit          |              |              |                 |       |

|       |                                | e Capture2 in<br>e Capture2 ir  |            |              |              |              |                 |       |

| bit 2 |                                | e Capture2 in<br>apture1 Interr | •          | vit          |              |              |                 |       |

|       |                                | e Capture1 in                   |            | ni -         |              |              |                 |       |

|       | 0 = Disable Capture1 interrupt |                                 |            |              |              |              |                 |       |

| bit 1 |                                | ART1 Transr                     |            |              |              |              |                 |       |

|       |                                | e USART1 Tra<br>e USART1 Tr     |            |              |              |              |                 |       |

| bit 0 |                                | SART1 Recei                     |            |              | ταρι         |              |                 |       |

| DILO  |                                | USART1 Re                       |            |              |              |              |                 |       |

|       |                                | e USART1 R                      |            |              |              |              |                 |       |

|       |                                |                                 |            |              |              |              |                 |       |

|       | Legend:                        |                                 |            |              |              |              |                 |       |

|       | R = Reada                      | ble bit                         | W = W      | /ritable bit | U = Unim     | plemented bi | it, read as '0' |       |

|       | - n = Value                    | at POR Res                      | et '1' = B | it is set    | '0' = Bit is | s cleared    | x = Bit is un   | known |

|       |                                |                                 |            |              |              |              |                 |       |

### EXAMPLE 6-1: SAVING STATUS AND WREG IN RAM (SIMPLE)

; The addresses that are used to store the CPUSTA and WREG values must be in the data memory ; address range of 1Ah - 1Fh. Up to 6 locations can be saved and restored using the MOVFP ; instruction. This instruction neither affects the status bits, nor corrupts the WREG register. UNBANK1 ; Address for 1st location to save EQU 0x01A UNBANK2 EQU 0x01B ; Address for 2nd location to save UNBANK3 EQU 0x01C ; Address for 3rd location to save UNBANK4 0x01D EOU ; Address for 4th location to save UNBANK5 EQU 0x01E ; Address for 5th location to save (Label Not used in program) ; UNBANK6 EQU 0x01F ; Address for 6th location to save (Label Not used in program) ; ; ; At Interrupt Vector Address • ALUSTA, UNBANK1 PUSH MOVFP ; Push ALUSTA value MOVFP BSR, UNBANK2 ; Push BSR value MOVFP WREG, UNBANK3 ; Push WREG value MOVFP PCLATH, UNBANK4 ; Push PCLATH value ; ; Interrupt Service Routine (ISR) code : ; UNBANK4, PCLATH ; Restore PCLATH value POP MOVFP UNBANK3, WREG ; Restore WREG value MOVFP MOVFP UNBANK2, BSR ; Restore BSR value MOVFP UNBANK1, ALUSTA ; Restore ALUSTA value ; RETFIE ; Return from interrupt (enable interrupts)

### 7.2.2.3 TMR0 Status/Control Register (T0STA)

This register contains various control bits. Bit7 (INTEDG) is used to control the edge upon which a signal on the RA0/INT pin will set the RA0/INT interrupt flag. The other bits configure Timer0, it's prescaler and clock source.

### REGISTER 7-3: T0STA REGISTER (ADDRESS: 05h, UNBANKED)

| R/W-0  | R/W-0                                         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0   |

|--------|-----------------------------------------------|-------|-------|-------|-------|-------|-------|

| INTEDG | T0SE                                          | T0CS  | T0PS3 | T0PS2 | T0PS1 | T0PS0 |       |

| bit 7  |                                               |       |       |       |       |       | bit 0 |

|        |                                               |       |       |       |       |       |       |

|        | INTEDG: RA0/INT Pin Interrupt Edge Select bit |       |       |       |       |       |       |

| bit 7<br>bit 6 | This bit selects<br>1 = Rising edge<br>0 = Falling edge<br><b>T0SE</b> : Timer0 E                                                                                                                   | <ul> <li>INTEDG: RA0/INT Pin Interrupt Edge Select bit</li> <li>This bit selects the edge upon which the interrupt is detected.</li> <li>1 = Rising edge of RA0/INT pin generates interrupt</li> <li>0 = Falling edge of RA0/INT pin generates interrupt</li> <li>TOSE: Timer0 External Clock Input Edge Select bit</li> <li>This bit selects the edge upon which TMR0 will increment.</li> </ul> |  |  |  |  |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                | <u>When TOCS = 0 (External Clock):</u><br>1 = Rising edge of RA1/T0CKI pin increments TMR0 and/or sets the T0CKIF bit<br>0 = Falling edge of RA1/T0CKI pin increments TMR0 and/or sets a T0CKIF bit |                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|                | <u>When T0CS = 1</u><br>Don't care                                                                                                                                                                  | I (Internal Clock):                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| bit 5          | This bit selects<br>1 = Internal inst                                                                                                                                                               | S: Timer0 Clock Source Select bit<br>bit selects the clock source for Timer0.<br>Internal instruction clock cycle (Tcy)<br>External clock input on the T0CKI pin                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| bit 4-1        |                                                                                                                                                                                                     | Timer0 Prescale Selection bits<br>ct the prescale value for Timer0.                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                | T0PS3:T0PS0                                                                                                                                                                                         | Prescale Value                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|                | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1xxx                                                                                                                                | 1:1<br>1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

bit 0

Unimplemented: Read as '0'

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR Reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# PIC17C7XX

NOTES:

## 10.0 I/O PORTS

PIC17C75X devices have seven I/O ports, PORTA through PORTG. PIC17C76X devices have nine I/O ports, PORTA through PORTJ. PORTB through PORTJ have a corresponding Data Direction Register (DDR), which is used to configure the port pins as inputs or outputs. Some of these ports pins are multiplexed with alternate functions.

PORTC, PORTD, and PORTE are multiplexed with the system bus. These pins are configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, these pins are general purpose I/O.

PORTA, PORTB, PORTE<3>, PORTF, PORTG and the upper four bits of PORTH are multiplexed with the peripheral features of the device. These peripheral features are:

- Timer Modules

- Capture Modules

- PWM Modules

- USART/SCI Modules

- SSP Module

- A/D Module

- External Interrupt pin

When some of these peripheral modules are turned on, the port pin will automatically configure to the alternate function. The modules that do this are:

- PWM Module

- SSP Module

- USART/SCI Module

When a pin is automatically configured as an output by a peripheral module, the pins data direction (DDR) bit is unknown. After disabling the peripheral module, the user should re-initialize the DDR bit to the desired configuration.

The other peripheral modules (which require an input) must have their data direction bits configured appropriately.

| Note: | A pin that is a peripheral input, can be con-   |

|-------|-------------------------------------------------|

|       | figured as an output (DDRx <y> is cleared).</y> |

|       | The peripheral events will be determined        |

|       | by the action output on the port pin.           |

When the device enters the "RESET state", the Data Direction registers (DDR) are forced set, which will make the I/O hi-impedance inputs. The RESET state of some peripheral modules may force the I/O to other operations, such as analog inputs or the system bus.

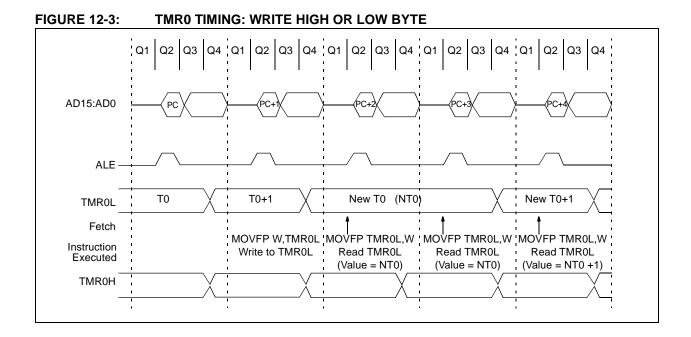

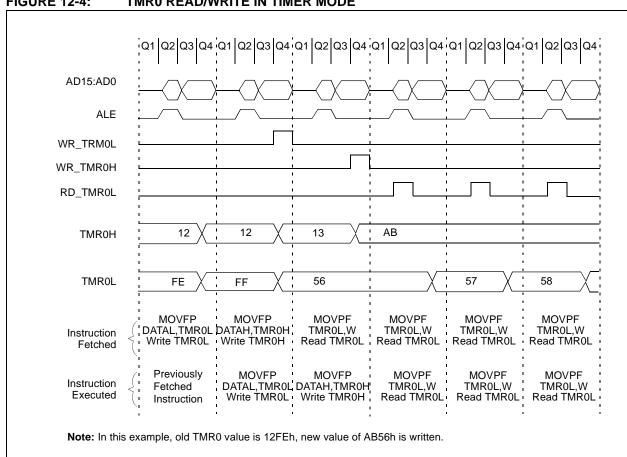

### 12.3 Read/Write Consideration for TMR0

Although TMR0 is a 16-bit timer/counter, only 8-bits at a time can be read or written during a single instruction cycle. Care must be taken during any read or write.

### 12.3.1 READING 16-BIT VALUE

The problem in reading the entire 16-bit value is that after reading the low (or high) byte, its value may change from FFh to 00h.

Example 12-1 shows a 16-bit read. To ensure a proper read, interrupts must be disabled during this routine.

EXAMPLE 12-1: 16-BIT READ

| MOVPF  | TMROL, | TMPLO | ;read low tmr0  |

|--------|--------|-------|-----------------|

| MOVPF  | TMROH, | TMPHI | ;read high tmr0 |

| MOVFP  | TMPLO, | WREG  | ;tmplo -> wreg  |

| CPFSLT | TMROL  |       | ;tmr0l < wreg?  |

| RETURN |        |       | ;no then return |

| MOVPF  | TMROL, | TMPLO | ;read low tmr0  |

| MOVPF  | TMROH, | TMPHI | ;read high tmr0 |

| RETURN |        |       | ;return         |

|        |        |       |                 |

### 12.3.2 WRITING A 16-BIT VALUE TO TMR0

Since writing to either TMR0L or TMR0H will effectively inhibit increment of that half of the TMR0 in the next cycle (following write), but not inhibit increment of the other half, the user must write to TMR0L first and TMR0H second, in two consecutive instructions, as shown in Example 12-2. The interrupt must be disabled. Any write to either TMR0L or TMR0H clears the prescaler.

### EXAMPLE 12-2: 16-BIT WRITE

| BSF   | CPUSTA, GLINTD ; Disable interrupts |

|-------|-------------------------------------|

| MOVFP | RAM_L, TMROL ;                      |

| MOVFP | RAM_H, TMROH ;                      |

| BCF   | CPUSTA, GLINTD ; Done, enable       |

|       | ; interrupts                        |

|       |                                     |

### 12.4 Prescaler Assignments

Timer0 has an 8-bit prescaler. The prescaler selection is fully under software control; i.e., it can be changed "on the fly" during program execution. Clearing the prescaler is recommended before changing its setting. The value of the prescaler is "unknown" and assigning a value that is less than the present value, makes it difficult to take this unknown time into account.

# PIC17C7XX

#### FIGURE 12-4: **TMR0 READ/WRITE IN TIMER MODE**

#### **TABLE 12-1: REGISTERS/BITS ASSOCIATED WITH TIMER0**

| Address       | Name   | Bit 7    | Bit 6                                       | Bit 5 | Bit 4  | Bit 3 | Bit 2  | Bit 1 | Bit 0     | Value on<br>POR,<br>BOR | MCLR, WDT |

|---------------|--------|----------|---------------------------------------------|-------|--------|-------|--------|-------|-----------|-------------------------|-----------|

| 05h, Unbanked | TOSTA  | INTEDG   | TOSE                                        | T0CS  | T0PS3  | T0PS2 | T0PS1  | T0PS0 | —         | 0000 000-               | 0000 000- |

| 06h, Unbanked | CPUSTA | —        | -                                           | STKAV | GLINTD | TO    | PD     | POR   | BOR       | 11 11qq                 | 11 qquu   |

| 07h, Unbanked | INTSTA | PEIF     | TOCKIF                                      | T0IF  | INTF   | PEIE  | TOCKIE | TOIE  | INTE      | 0000 0000               | 0000 0000 |

| 0Bh, Unbanked | TMR0L  | TMR0 Reg | MR0 Register; Low Byte                      |       |        |       |        |       |           | xxxx xxxx               | uuuu uuuu |

| 0Ch, Unbanked | TMR0H  | TMR0 Reg | MR0 Register; High Byte xxxx xxxx uuuu uuuu |       |        |       |        |       | uuuu uuuu |                         |           |

Legend: x = unknown, u = unchanged, - = unimplemented, read as a '0', q = value depends on condition. Shaded cells are not used by Timer0.

## 13.0 TIMER1, TIMER2, TIMER3, PWMS AND CAPTURES

The PIC17C7XX has a wealth of timers and time based functions to ease the implementation of control applications. These time base functions include three PWM outputs and four Capture inputs.

Timer1 and Timer2 are two 8-bit incrementing timers, each with an 8-bit period register (PR1 and PR2, respectively) and separate overflow interrupt flags. Timer1 and Timer2 can operate either as timers (increment on internal FOSC/4 clock), or as counters (increment on falling edge of external clock on pin RB4/TCLK12). They are also software configurable to operate as a single 16-bit timer/counter. These timers are also used as the time base for the PWM (Pulse Width Modulation) modules.

Timer3 is a 16-bit timer/counter which uses the TMR3H and TMR3L registers. Timer3 also has two additional registers (PR3H/CA1H:PR3L/CA1L) that are configurable as a 16-bit period register or a 16-bit capture register. TMR3 can be software configured to increment from the internal system clock (FOSC/4), or from an external signal on the RB5/TCLK3 pin. Timer3 is the time base for all of the 16-bit captures.

Six other registers comprise the Capture2, Capture3, and Capture4 registers (CA2H:CA2L, CA3H:CA3L, and CA4H:CA4L).

Figure 13-1, Figure 13-2 and Figure 13-3 are the control registers for the operation of Timer1, Timer2 and Timer3, as well as PWM1, PWM2, PWM3, Capture1, Capture2, Capture3 and Capture4.

Table 13-1 shows the Timer resource requirements for these time base functions. Each timer is an open resource so that multiple functions may operate with it.

### TABLE 13-1: TIME-BASE FUNCTION/ RESOURCE REQUIREMENTS

| Time Base Function | Timer Resource   |

|--------------------|------------------|

| PWM1               | Timer1           |

| PWM2               | Timer1 or Timer2 |

| PWM3               | Timer1 or Timer2 |

| Capture1           | Timer3           |

| Capture2           | Timer3           |

| Capture3           | Timer3           |

| Capture4           | Timer3           |

### REGISTER 13-1: TCON1 REGISTER (ADDRESS: 16h, BANK 3)

|         | R/W-0                                      | R/W-0                        | R/W-0       | R/W-0        | R/W-0       | R/W-0        | R/W-0           | R/W-0  |  |

|---------|--------------------------------------------|------------------------------|-------------|--------------|-------------|--------------|-----------------|--------|--|

|         | CA2ED1                                     | CA2ED0                       | CA1ED1      | CA1ED0       | T16         | TMR3CS       | TMR2CS          | TMR1CS |  |

|         | bit 7                                      |                              |             |              |             |              |                 | bit 0  |  |

|         |                                            |                              |             |              |             |              |                 |        |  |

| bit 7-6 |                                            | <b>CA2ED0</b> : Ca           |             |              |             |              |                 |        |  |

|         | •                                          | ure on every<br>ure on every | • •         |              |             |              |                 |        |  |

|         |                                            | ure on every                 |             | dge          |             |              |                 |        |  |

|         |                                            | ure on every                 |             |              |             |              |                 |        |  |

| bit 5-4 |                                            | <b>CA1ED0</b> : Ca           |             |              |             |              |                 |        |  |

|         |                                            | ure on every                 |             |              |             |              |                 |        |  |

|         | •                                          | ure on every<br>ure on every | • •         | dae          |             |              |                 |        |  |

|         | •                                          | ure on every                 | •           | •            |             |              |                 |        |  |

| bit 3   |                                            | r2:Timer1 Mo                 |             |              |             |              |                 |        |  |

|         |                                            | 2 and Timer1                 |             |              |             |              |                 |        |  |

| h 11 O  |                                            | 2 and Timer1                 |             |              |             |              |                 |        |  |

| bit 2   |                                            | Timer3 Clock                 |             | edge of the  | RB5/TCLK3   | 8 nin        |                 |        |  |

|         |                                            | increments of                |             |              |             | , p          |                 |        |  |

| bit 1   | TMR2CS:                                    | Timer2 Cloc                  | k Source Se | lect bit     |             |              |                 |        |  |

|         |                                            |                              |             | edge of the  | RB4/TCLK1   | 2 pin        |                 |        |  |

|         | 0 = TMR2 increments off the internal clock |                              |             |              |             |              |                 |        |  |

| bit 0   |                                            | Timer1 Cloc                  |             |              |             | 2 nin        |                 |        |  |

|         |                                            | increments of                |             | edge of the  | KD4/IGLK    | z pin        |                 |        |  |

|         |                                            |                              |             |              |             |              |                 |        |  |

|         | Legend:                                    |                              |             |              |             |              |                 |        |  |

|         | R = Reada                                  | ble bit                      | W = W       | /ritable bit | U = Unin    | nplemented b | oit, read as 'C | )'     |  |

|         | - n = Value                                | at POR Res                   | et '1' = B  | it is set    | '0' = Bit i | s cleared    | x = Bit is ur   | nknown |  |

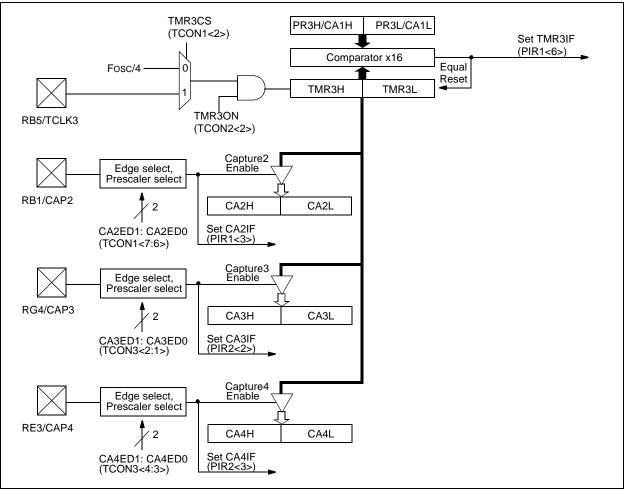

### 13.2 Timer3

Timer3 is a 16-bit timer consisting of the TMR3H and TMR3L registers. TMR3H is the high byte of the timer and TMR3L is the low byte. This timer has an associated 16-bit period register (PR3H/CA1H:PR3L/CA1L). This period register can be software configured to be a another 16-bit capture register.

When the TMR3CS bit (TCON1<2>) is clear, the timer increments every instruction cycle (Fosc/4). When TMR3CS is set, the counter increments on every falling edge of the RB5/TCLK3 pin. In either mode, the TMR3ON bit must be set for the timer/counter to increment. When TMR3ON is clear, the timer will not increment or set flag bit TMR3IF.

Timer3 has two modes of operation, depending on the CA1/PR3 bit (TCON2<3>). These modes are:

- Three capture and one period register mode

- · Four capture register mode

The PIC17C7XX has up to four 16-bit capture registers that capture the 16-bit value of TMR3 when events are detected on capture pins. There are four capture pins

(RB0/CAP1, RB1/CAP2, RG4/CAP3, and RE3/CAP4), one for each capture register pair. The capture pins are multiplexed with the I/O pins. An event can be:

- · A rising edge

- A falling edge

- · Every 4th rising edge

- · Every 16th rising edge

Each 16-bit capture register has an interrupt flag associated with it. The flag is set when a capture is made. The capture modules are truly part of the Timer3 block. Figure 13-5 and Figure 13-6 show the block diagrams for the two modes of operation.

### 13.2.1 THREE CAPTURE AND ONE PERIOD REGISTER MODE

In this mode, registers PR3H/CA1H and PR3L/CA1L constitute a 16-bit period register. A block diagram is shown in Figure 13-5. The timer increments until it equals the period register and then resets to 0000h on the next timer clock. TMR3 Interrupt Flag bit (TMR3IF) is set at this point. This interrupt can be disabled by clearing the TMR3 Interrupt Enable bit (TMR3IE). TMR3IF must be cleared in software.

### FIGURE 13-5: TIMER3 WITH THREE CAPTURE AND ONE PERIOD REGISTER BLOCK DIAGRAM

This mode (3 Capture, 1 Period) is selected if control bit CA1/PR3 is clear. In this mode, the Capture1 register, consisting of high byte (PR3H/CA1H) and low byte (PR3L/CA1L), is configured as the period control register for TMR3. Capture1 is disabled in this mode and the corresponding interrupt bit, CA1IF, is never set. TMR3 increments until it equals the value in the period register and then resets to 0000h on the next timer clock.

All other Captures are active in this mode.

### 13.2.1.1 Capture Operation

The CAxED1 and CAxED0 bits determine the event on which capture will occur. The possible events are:

- Capture on every falling edge

- Capture on every rising edge

- Capture every 4th rising edge

- Capture every 16th rising edge

When a capture takes place, an interrupt flag is latched into the CAxIF bit. This interrupt can be enabled by setting the corresponding mask bit CAxIE. The Peripheral Interrupt Enable bit (PEIE) must be set and the Global Interrupt Disable bit (GLINTD) must be cleared for the interrupt to be acknowledged. The CAxIF interrupt flag bit is cleared in software.

When the capture prescale select is changed, the prescaler is not reset and an event may be generated. Therefore, the first capture after such a change will be ambiguous. However, it sets the time-base for the next capture. The prescaler is reset upon chip RESET.

The capture pin, CAPx, is a multiplexed pin. When used as a port pin, the capture is not disabled. However, the user can simply disable the Capture interrupt by clearing CAxIE. If the CAPx pin is used as an output pin, the user can activate a capture by writing to the port pin. This may be useful during development phase to emulate a capture interrupt. The input on the capture pin CAPx is synchronized internally to internal phase clocks. This imposes certain restrictions on the input waveform (see the Electrical Specification section for timing).

The capture overflow status flag bit is double buffered. The master bit is set if one captured word is already residing in the Capture register (CAxH:CAxL) and another "event" has occurred on the CAPx pin. The new event will not transfer the TMR3 value to the capture register, protecting the previous unread capture value. When the user reads both the high and the low bytes (in any order) of the Capture register, the master overflow bit is transferred to the slave overflow bit (CAxOVF) and then the master bit is reset. The user can then read TCONx to determine the value of CAx-OVF.

The recommended sequence to read capture registers and capture overflow flag bits is shown in Example 13-1.

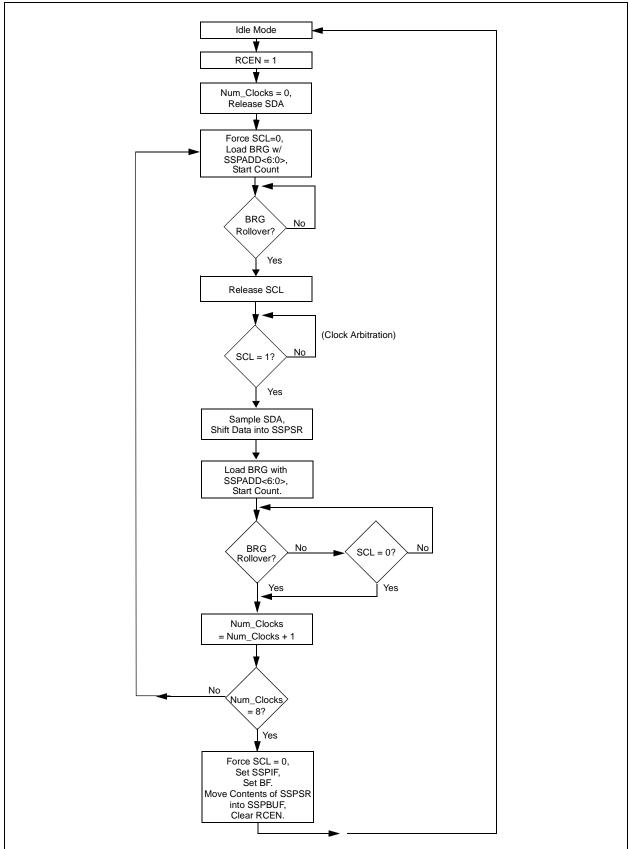

### 15.2.1.1 Addressing

Once the MSSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register on the falling edge of the 8th SCL pulse.

- b) The buffer full bit, BF, is set on the falling edge of the 8th SCL pulse.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR2<7>), is set (interrupt is generated if enabled) - on the falling edge of the 9th SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for a 10-bit address is as follows, with steps 7- 9 for slave-transmitter:

- 1. Receive first (high) byte of Address (bits SSPIF, BF and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of Address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of Address. This will clear bit UA and release the SCL line.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

Note: Following the Repeated Start condition (step 7) in 10-bit mode, the user only needs to match the first 7-bit address. The user does not update the SSPADD for the second half of the address.

### 15.2.1.2 Slave Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON1<6>) is set.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR2<7>) must be cleared in software. The SSPSTAT register is used to determine the status of the received byte.

Note: The SSPBUF will be loaded if the SSPOV bit is set and the BF flag is cleared. If a read of the SSPBUF was performed, but the user did not clear the state of the SSPOV bit before the next receive occurred, the ACK is not sent and the SSP-BUF is updated.

|    | ts as Data<br>s Received | SSPSR $ ightarrow$ SSPBUF | Generate ACK<br>Pulse | Set bit SSPIF<br>(SSP Interrupt occurs |  |

|----|--------------------------|---------------------------|-----------------------|----------------------------------------|--|

| BF | SSPOV                    |                           | Fuise                 | if enabled)                            |  |

| 0  | 0                        | Yes                       | Yes                   | Yes                                    |  |

| 1  | 0                        | No                        | No                    | Yes                                    |  |

| 1  | 1                        | No                        | No                    | Yes                                    |  |

| 0  | 1                        | Yes                       | No                    | Yes                                    |  |

### TABLE 15-2: DATA TRANSFER RECEIVED BYTE ACTIONS

Note 1: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

### 15.2.3 SLEEP OPERATION

While in SLEEP mode, the  $I^2C$  module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from SLEEP (if the SSP interrupt is enabled).

### 15.2.4 EFFECTS OF A RESET

A RESET disables the SSP module and terminates the current transfer.

| Address       | Name    | Bit 7    | Bit 6         | Bit 5                    | Bit 4      | Bit 3      | Bit 2  | Bit 1 | Bit 0 | POR, BOR  | MCLR, WDT |

|---------------|---------|----------|---------------|--------------------------|------------|------------|--------|-------|-------|-----------|-----------|

| 07h, Unbanked | INTSTA  | PEIF     | <b>T0CKIF</b> | T0IF                     | INTF       | PEIE       | T0CKIE | TOIE  | INTE  | 0000 0000 | 0000 0000 |

| 10h, Bank 4   | PIR2    | SSPIF    | BCLIF         | ADIF                     | —          | CA4IF      | CA3IF  | TX2IF | RC2IF | 000- 0000 | 000- 0000 |

| 11h, Bank 4   | PIE2    | SSPIE    | BCLIE         | ADIE                     | —          | CA4IE      | CA3IE  | TX2IE | RC2IE | 000- 0000 | 000- 0000 |

| 10h. Bank 6   | SSPADD  | Synchron | nous Serial P | ort (I <sup>2</sup> C mo | de) Addres | s Register |        |       |       | 0000 0000 | 0000 0000 |

| 14h, Bank 6   | SSPBUF  | Synchron | nous Serial P | ort Receive              | Buffer/Tra | nsmit Reg  | ister  |       |       | xxxx xxxx | uuuu uuuu |

| 11h, Bank 6   | SSPCON1 | WCOL     | SSPOV         | SSPEN                    | CKP        | SSPM3      | SSPM2  | SSPM1 | SSPM0 | 0000 0000 | 0000 0000 |

| 12h, Bank 6   | SSPCON2 | GCEN     | ACKSTAT       | ACKDT                    | ACKEN      | RCEN       | PEN    | RSEN  | SEN   | 0000 0000 | 0000 0000 |

| 13h, Bank 6   | SSPSTAT | SMP      | CKE           | D/A                      | Р          | S          | R/W    | UA    | BF    | 0000 0000 | 0000 0000 |

## TABLE 15-3: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in I<sup>2</sup>C mode.

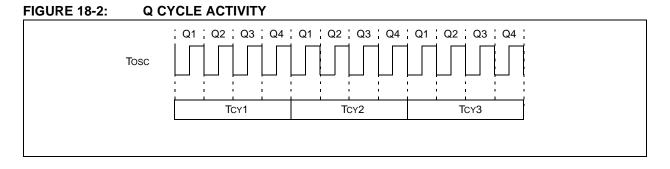

### 18.2 Q Cycle Activity

Each instruction cycle (TcY) is comprised of four Q cycles (Q1-Q4). The Q cycle is the same as the device oscillator cycle (Tosc). The Q cycles provide the timing/ designation for the Decode, Read, Process Data, Write, etc., of each instruction cycle. The following diagram shows the relationship of the Q cycles to the instruction cycle.

The four Q cycles that make up an instruction cycle (TCY) can be generalized as:

- Q1: Instruction Decode Cycle or forced No operation

- Q2: Instruction Read Cycle or No operation

- Q3: Process the Data

- Q4: Instruction Write Cycle or No operation

Each instruction will show the detailed Q cycle operation for the instruction.

# PIC17C7XX

| ANDWF                                       | AND WR                                                         | AND WREG with f                                                                                                                                     |                      |  |  |  |  |

|---------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|

| Syntax: [ label ] ANDWF f,d                 |                                                                |                                                                                                                                                     |                      |  |  |  |  |

| Operands:                                   | $\begin{array}{l} 0 \leq f \leq 25 \\ d \in [0,1] \end{array}$ | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \end{array}$                                                                                     |                      |  |  |  |  |

| Operation:                                  | (WREG) .                                                       | AND. (f) $\rightarrow$ (                                                                                                                            | dest)                |  |  |  |  |

| Status Affected:                            | Z                                                              |                                                                                                                                                     |                      |  |  |  |  |

| Encoding:                                   | 0000                                                           | 101d ff                                                                                                                                             | ff ffff              |  |  |  |  |

| Description:                                | register 'f'.<br>in WREG. I                                    | The contents of WREG are AND'ed with register 'f'. If 'd' is 0 the result is stored in WREG. If 'd' is 1 the result is stored back in register 'f'. |                      |  |  |  |  |

| Words:                                      | 1                                                              | 1                                                                                                                                                   |                      |  |  |  |  |

| Cycles:                                     | 1                                                              | 1                                                                                                                                                   |                      |  |  |  |  |

| Q Cycle Activity:                           |                                                                |                                                                                                                                                     |                      |  |  |  |  |

| Q1                                          | Q2                                                             | Q3                                                                                                                                                  | Q4                   |  |  |  |  |

| Decode                                      | Read<br>register 'f'                                           | Process<br>Data                                                                                                                                     | Write to destination |  |  |  |  |

| Example: ANDWF REG, 1<br>Before Instruction |                                                                |                                                                                                                                                     |                      |  |  |  |  |

| BCF Bit Clear f           |               |                                                                    |                                                                     |           |    |                     |  |  |

|---------------------------|---------------|--------------------------------------------------------------------|---------------------------------------------------------------------|-----------|----|---------------------|--|--|

| Syntax: [ label ] BCF f,b |               |                                                                    |                                                                     |           |    |                     |  |  |

| Ope                       | rands:        | $\begin{array}{l} 0 \leq f \leq 25 \\ 0 \leq b \leq 7 \end{array}$ | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \end{array}$ |           |    |                     |  |  |

| Ope                       | ration:       | $0 \rightarrow (f < b >$                                           | •)                                                                  |           |    |                     |  |  |

| Statu                     | us Affected:  | None                                                               |                                                                     |           |    |                     |  |  |

| Encoding:                 |               | 1000                                                               | 1bbb                                                                | 1bbb ffff |    | ffff                |  |  |

| Desc                      | cription:     | Bit 'b' in register 'f' is cleared.                                |                                                                     |           |    |                     |  |  |

| Words:                    |               | 1                                                                  |                                                                     |           |    |                     |  |  |

| Cycl                      | es:           | 1                                                                  | 1                                                                   |           |    |                     |  |  |

| QC                        | cle Activity: |                                                                    |                                                                     |           |    |                     |  |  |

| Q1<br>Decode              |               | Q2                                                                 | Q                                                                   | 3         | Q4 |                     |  |  |

|                           |               | Read<br>register 'f'                                               | Process<br>Data I                                                   |           |    | Write<br>gister 'f' |  |  |

|                           |               |                                                                    |                                                                     |           |    |                     |  |  |

| <u>Exar</u>               | <u>mple</u> : | BCF                                                                | FLAG_F                                                              | REG,      | 7  |                     |  |  |

Before Instruction FLAG\_REG = 0xC7

After Instruction FLAG\_REG = 0x47

$\begin{array}{rrrr} Before Instruction \\ WREG &= & 0x17 \\ REG &= & 0xC2 \\ \end{tabular} \\ After Instruction \\ WREG &= & 0x17 \end{array}$

REG = 0x02

| cted:<br>:                                                                                                                                                                                                                                                                                                                                                                                                                           | result is sto                                                                                   | 5<br>(dest)<br>2, Z                                            | 6. If 'd'                                                                                                                                                  | is 1, the                                                                                                                     | S<br>  S<br>  E                                                                                      |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|

| :                                                                                                                                                                                                                                                                                                                                                                                                                                    | $d \in [0,1]$ (f) - 1 -> (f) OV, C, DC OV, C, DC OO00 Decrement result is stor result is stor 1 | dest)<br>2, Z<br>011d fi<br>register 'f'. If<br>red in WREC    | 'd' is 0<br>6. If 'd'                                                                                                                                      | ), the<br>is 1, the                                                                                                           | ) S<br>E                                                                                             |  |  |

| :                                                                                                                                                                                                                                                                                                                                                                                                                                    | OV, C, DC<br>0000<br>Decrement<br>result is sto<br>result is sto<br>1                           | 011d fr<br>register 'f'. If<br>rred in WREG                    | 'd' is 0<br>6. If 'd'                                                                                                                                      | ), the<br>is 1, the                                                                                                           | ] S                                                                                                  |  |  |

| :                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0000<br>Decrement<br>result is sto<br>result is sto<br>1                                        | 011d fr<br>register 'f'. If<br>red in WREG                     | 'd' is 0<br>6. If 'd'                                                                                                                                      | ), the<br>is 1, the                                                                                                           | J                                                                                                    |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | Decrement<br>result is sto<br>result is sto<br>1                                                | register 'f'. If<br>red in WREC                                | 'd' is 0<br>6. If 'd'                                                                                                                                      | ), the<br>is 1, the                                                                                                           | J                                                                                                    |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | result is sto<br>result is sto<br>1                                                             | ored in WREC                                                   | 6. If 'd'                                                                                                                                                  | is 1, the                                                                                                                     |                                                                                                      |  |  |

| tivitv <i>e</i>                                                                                                                                                                                                                                                                                                                                                                                                                      | -                                                                                               |                                                                |                                                                                                                                                            |                                                                                                                               |                                                                                                      |  |  |

| tiv <i>iit</i> o <i>c</i>                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                               |                                                                |                                                                                                                                                            |                                                                                                                               |                                                                                                      |  |  |

| +i., <i>i</i> . +., <i>i</i> .                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                 |                                                                |                                                                                                                                                            |                                                                                                                               |                                                                                                      |  |  |

| tivity:                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                 |                                                                |                                                                                                                                                            |                                                                                                                               |                                                                                                      |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                    | Q2                                                                                              | Q3                                                             |                                                                                                                                                            | Q4                                                                                                                            |                                                                                                      |  |  |

| ode                                                                                                                                                                                                                                                                                                                                                                                                                                  | Read<br>register 'f'                                                                            | Process<br>Data                                                |                                                                                                                                                            |                                                                                                                               | ] v                                                                                                  |  |  |

| Example:DECFCNT, 1Before InstructionCNT $Z$ = $Z$ </td |                                                                                                 |                                                                |                                                                                                                                                            |                                                                                                                               |                                                                                                      |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | Instruct<br>IT =<br>structio<br>IT =                                                            | Decr<br>DECF<br>Instruction<br>IT = 0x01<br>= 0<br>Instruction | Decr     Read<br>register 'f'     Process<br>Data       DECF     CNT, 1       Instruction       IT     =       0       struction       IT     =       0x00 | Decr     CNT,     1       DECF     CNT,     1       Instruction     =     0       IT     =     0       Istruction     =     0 | DeceRead<br>register 'f'Process<br>DataWrite to<br>destinationDECFCNT, 1InstructionIT=0structionIT=0 |  |  |

| DEC               | FSZ                                    | Decreme                                                                                    | Decrement f, skip if 0                                                                                                                                                                                                                                                                                                    |                                            |                              |  |  |  |  |

|-------------------|----------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------|--|--|--|--|

| Synt              | ax:                                    | [label]                                                                                    | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                        |                                            |                              |  |  |  |  |

| Ope               | rands:                                 | $0 \le f \le 255$<br>$d \in [0,1]$                                                         | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                           |                                            |                              |  |  |  |  |

| Ope               | ration:                                |                                                                                            | (f) $-1 \rightarrow$ (dest);<br>skip if result = 0                                                                                                                                                                                                                                                                        |                                            |                              |  |  |  |  |

| Statu             | us Affected:                           | None                                                                                       |                                                                                                                                                                                                                                                                                                                           |                                            |                              |  |  |  |  |

| Enco              | oding:                                 | 0001                                                                                       | 0001 011d ffff ff                                                                                                                                                                                                                                                                                                         |                                            |                              |  |  |  |  |

| Desc              | cription:                              | mented. If v<br>WREG. If 'c<br>back in reg<br>If the result<br>which is alr<br>and a NOP i | The contents of register 'f' are decre-<br>mented. If 'd' is 0, the result is placed in<br>WREG. If 'd' is 1, the result is placed<br>back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched is discarded<br>and a NOP is executed instead, making<br>it a two-cycle instruction. |                                            |                              |  |  |  |  |

| Wor               | ds:                                    | 1                                                                                          |                                                                                                                                                                                                                                                                                                                           |                                            |                              |  |  |  |  |

| Cycl              | es:                                    | 1(2)                                                                                       |                                                                                                                                                                                                                                                                                                                           |                                            |                              |  |  |  |  |

| Q Cycle Activity: |                                        |                                                                                            |                                                                                                                                                                                                                                                                                                                           |                                            |                              |  |  |  |  |