Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 16MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 902 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 68-LCC (J-Lead)                                                            |

| Supplier Device Package    | 68-PLCC (24.23x24.23)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c756a-16e-l |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 3-1: | PINC       | DUT DE      | SCRIP       | TIONS       | (CON       | TINUE         | D)             |                                                                                                                                                                               |

|------------|------------|-------------|-------------|-------------|------------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | F          | PIC17C7     | 5X          | PIC17       | 7C76X      |               |                |                                                                                                                                                                               |

| Name       | DIP<br>No. | PLCC<br>No. | TQFP<br>No. | PLCC<br>No. | QFP<br>No. | I/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                   |

|            |            |             |             |             |            |               |                | PORTC is a bi-directional I/O Port.                                                                                                                                           |

| RC0/AD0    | 2          | 3           | 58          | 3           | 72         | I/O           | TTL            | This is also the least significant byte (LSB) of                                                                                                                              |

| RC1/AD1    | 63         | 67          | 55          | 83          | 69         | I/O           | TTL            | the 16-bit wide system bus in Microprocessor                                                                                                                                  |

| RC2/AD2    | 62         | 66          | 54          | 82          | 68         | I/O           | TTL            | mode or Extended Microcontroller mode. In                                                                                                                                     |

| RC3/AD3    | 61         | 65          | 53          | 81          | 67         | I/O           | TTL            | multiplexed system bus configuration, these<br>pins are address output as well as data input of                                                                               |

| RC4/AD4    | 60         | 64          | 52          | 80          | 66         | I/O           | TTL            | output.                                                                                                                                                                       |

| RC5/AD5    | 58         | 63          | 51          | 79          | 65         | I/O           | TTL            |                                                                                                                                                                               |

| RC6/AD6    | 58         | 62          | 50          | 78          | 64         | I/O           | TTL            |                                                                                                                                                                               |

| RC7/AD7    | 57         | 61          | 49          | 77          | 63         | I/O           | TTL            |                                                                                                                                                                               |

|            |            |             |             |             |            |               |                | PORTD is a bi-directional I/O Port.                                                                                                                                           |

| RD0/AD8    | 10         | 11          | 2           | 15          | 4          | I/O           | TTL            | This is also the most significant byte (MSB) of                                                                                                                               |

| RD1/AD9    | 9          | 10          | 1           | 14          | 3          | I/O           | TTL            | the 16-bit system bus in Microprocessor mode                                                                                                                                  |

| RD2/AD10   | 8          | 9           | 64          | 9           | 78         | I/O           | TTL            | or Extended Microcontroller mode. In multi-                                                                                                                                   |

| RD3/AD11   | 7          | 8           | 63          | 8           | 77         | I/O           | TTL            | plexed system bus configuration, these pins an<br>address output as well as data input or output.                                                                             |

| RD4/AD12   | 6          | 7           | 62          | 7           | 76         | I/O           | TTL            |                                                                                                                                                                               |

| RD5/AD13   | 5          | 6           | 61          | 6           | 75         | I/O           | TTL            |                                                                                                                                                                               |

| RD6/AD14   | 4          | 5           | 60          | 5           | 74         | I/O           | TTL            |                                                                                                                                                                               |

| RD7/AD15   | 3          | 4           | 59          | 4           | 73         | I/O           | TTL            |                                                                                                                                                                               |

|            |            |             |             |             |            |               |                | PORTE is a bi-directional I/O Port.                                                                                                                                           |

| RE0/ALE    | 11         | 12          | 3           | 16          | 5          | I/O           | TTL            | In Microprocessor mode or Extended Microcor<br>troller mode, RE0 is the Address Latch Enable<br>(ALE) output. Address should be latched on the<br>falling edge of ALE output. |

| RE1/OE     | 12         | 13          | 4           | 17          | 6          | I/O           | TTL            | In Microprocessor or Extended Microcontroller mode, RE1 is the Output Enable (OE) control output (active low).                                                                |

| RE2/WR     | 13         | 14          | 5           | 18          | 7          | I/O           | TTL            | In Microprocessor or Extended Microcontroller mode, RE2 is the Write Enable (WR) control output (active low).                                                                 |

| RE3/CAP4   | 14         | 15          | 6           | 19          | 8          | I/O           | ST             | RE3 can also be the Capture4 input pin.                                                                                                                                       |

|            |            |             |             |             |            |               |                | PORTF is a bi-directional I/O Port.                                                                                                                                           |

| RF0/AN4    | 26         | 28          | 18          | 36          | 24         | I/O           | ST             | RF0 can also be analog input 4.                                                                                                                                               |

| RF1/AN5    | 25         | 27          | 17          | 35          | 23         | I/O           | ST             | RF1 can also be analog input 5.                                                                                                                                               |

| RF2/AN6    | 24         | 26          | 16          | 30          | 18         | I/O           | ST             | RF2 can also be analog input 6.                                                                                                                                               |

| RF3/AN7    | 23         | 25          | 15          | 29          | 17         | I/O           | ST             | RF3 can also be analog input 7.                                                                                                                                               |

| RF4/AN8    | 22         | 24          | 14          | 28          | 16         | I/O           | ST             | RF4 can also be analog input 8.                                                                                                                                               |

| RF5/AN9    | 21         | 23          | 13          | 27          | 15         | I/O           | ST             | RF5 can also be analog input 9.                                                                                                                                               |

| RF6/AN10   | 20         | 22          | 12          | 26          | 14         | I/O           | ST             | RF6 can also be analog input 10.                                                                                                                                              |

| RF7/AN11   | 19         | 21          | 11          | 25          | 13         | I/O           | ST             | RF7 can also be analog input 11.                                                                                                                                              |

TABLE 3-1: PINOUT DESCRIPTIONS (CONTINUED)

Legend: I = Input only; O = Output only; I/O = Inp P = Power; — = Not Used; TTL = T

I/O = Input/Output; TTL = TTL input;

ST = Schmitt Trigger input

Note 1: The output is only available by the peripheral operation.2: Open drain input/output pin. Pin forced to input upon any device RESET.

### 13.0 TIMER1, TIMER2, TIMER3, PWMS AND CAPTURES

The PIC17C7XX has a wealth of timers and time based functions to ease the implementation of control applications. These time base functions include three PWM outputs and four Capture inputs.

Timer1 and Timer2 are two 8-bit incrementing timers, each with an 8-bit period register (PR1 and PR2, respectively) and separate overflow interrupt flags. Timer1 and Timer2 can operate either as timers (increment on internal FOSC/4 clock), or as counters (increment on falling edge of external clock on pin RB4/TCLK12). They are also software configurable to operate as a single 16-bit timer/counter. These timers are also used as the time base for the PWM (Pulse Width Modulation) modules.

Timer3 is a 16-bit timer/counter which uses the TMR3H and TMR3L registers. Timer3 also has two additional registers (PR3H/CA1H:PR3L/CA1L) that are configurable as a 16-bit period register or a 16-bit capture register. TMR3 can be software configured to increment from the internal system clock (FOSC/4), or from an external signal on the RB5/TCLK3 pin. Timer3 is the time base for all of the 16-bit captures.

Six other registers comprise the Capture2, Capture3, and Capture4 registers (CA2H:CA2L, CA3H:CA3L, and CA4H:CA4L).

Figure 13-1, Figure 13-2 and Figure 13-3 are the control registers for the operation of Timer1, Timer2 and Timer3, as well as PWM1, PWM2, PWM3, Capture1, Capture2, Capture3 and Capture4.

Table 13-1 shows the Timer resource requirements for these time base functions. Each timer is an open resource so that multiple functions may operate with it.

#### TABLE 13-1: TIME-BASE FUNCTION/ RESOURCE REQUIREMENTS

| Time Base Function | Timer Resource   |

|--------------------|------------------|

| PWM1               | Timer1           |

| PWM2               | Timer1 or Timer2 |

| PWM3               | Timer1 or Timer2 |

| Capture1           | Timer3           |

| Capture2           | Timer3           |

| Capture3           | Timer3           |

| Capture4           | Timer3           |

#### REGISTER 13-1: TCON1 REGISTER (ADDRESS: 16h, BANK 3)

|          | R/W-0                                                                                                        | R/W-0                        | R/W-0       | R/W-0        | R/W-0       | R/W-0        | R/W-0           | R/W-0  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------|------------------------------|-------------|--------------|-------------|--------------|-----------------|--------|--|--|--|

|          | CA2ED1                                                                                                       | CA2ED0                       | CA1ED1      | CA1ED0       | T16         | TMR3CS       | TMR2CS          | TMR1CS |  |  |  |

|          | bit 7                                                                                                        |                              |             |              |             |              |                 | bit 0  |  |  |  |

|          |                                                                                                              |                              |             |              |             |              |                 |        |  |  |  |

| bit 7-6  | CA2ED1:CA2ED0: Capture2 Mode Select bits                                                                     |                              |             |              |             |              |                 |        |  |  |  |

|          |                                                                                                              | ure on every<br>ure on every |             |              |             |              |                 |        |  |  |  |

|          |                                                                                                              | ure on every                 |             | dae          |             |              |                 |        |  |  |  |

|          | •                                                                                                            | ure on every                 | •           | •            |             |              |                 |        |  |  |  |

| bit 5-4  |                                                                                                              | CA1ED0: Ca                   | •           |              |             |              |                 |        |  |  |  |

|          |                                                                                                              | ure on every                 |             |              |             |              |                 |        |  |  |  |

|          | •                                                                                                            | ure on every<br>ure on every | • •         | dae          |             |              |                 |        |  |  |  |

|          |                                                                                                              | ure on every                 |             |              |             |              |                 |        |  |  |  |

| bit 3    |                                                                                                              | r2:Timer1 Mo                 |             |              |             |              |                 |        |  |  |  |

|          |                                                                                                              | 2 and Timer1<br>2 and Timer1 |             |              |             |              |                 |        |  |  |  |

| bit 2    |                                                                                                              | Timer3 Cloc                  |             |              |             |              |                 |        |  |  |  |

| DILZ     |                                                                                                              | increments of                |             |              | RB5/TCLK    | 3 pin        |                 |        |  |  |  |

|          |                                                                                                              | increments of                |             |              |             |              |                 |        |  |  |  |

| bit 1    | TMR2CS:                                                                                                      | Timer2 Cloc                  | k Source Se | lect bit     |             |              |                 |        |  |  |  |

|          |                                                                                                              | increments of                |             |              | RB4/TCLK    | l2 pin       |                 |        |  |  |  |

| <b>L</b> | • • • • • • • • •                                                                                            | increments of                |             |              |             |              |                 |        |  |  |  |

| bit 0    |                                                                                                              | Timer1 Cloc                  |             |              | RB4/TCLK    | l2 nin       |                 |        |  |  |  |

|          | 1 = TMR1 increments off the falling edge of the RB4/TCLK12 pin<br>0 = TMR1 increments off the internal clock |                              |             |              |             |              |                 |        |  |  |  |

|          |                                                                                                              |                              |             |              |             |              |                 |        |  |  |  |

|          | Legend:                                                                                                      |                              |             |              |             |              |                 |        |  |  |  |

|          | R = Reada                                                                                                    | ble bit                      | W = W       | /ritable bit | U = Unir    | nplemented b | oit, read as '0 | )'     |  |  |  |

|          | - n = Value                                                                                                  | at POR Res                   | et '1' = B  | it is set    | '0' = Bit i | s cleared    | x = Bit is u    | nknown |  |  |  |

## PIC17C7XX

NOTES:

#### REGISTER 15-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS: 13h, BANK 6) R/W-0 R/W-0 R-0 R-0 R-0 R-0 R-0 R-0 SMP CKE D/A Р S R/W UA BF bit 7 bit 0 bit 7 SMP: Sample bit SPI Master mode: 1 = Input data sampled at end of data output time 0 = Input data sampled at middle of data output time SPI Slave mode: SMP must be cleared when SPI is used in Slave mode In I<sup>2</sup>C Master or Slave mode: 1 = Slew rate control disabled for Standard Speed mode (100 kHz and 1 MHz) 0 = Slew rate control enabled for High Speed mode (400 kHz) bit 6 CKE: SPI Clock Edge Select (Figure 15-6, Figure 15-8 and Figure 15-9) CKP = 0: 1 = Data transmitted on rising edge of SCK 0 = Data transmitted on falling edge of SCK CKP = 1: 1 = Data transmitted on falling edge of SCK 0 = Data transmitted on rising edge of SCK bit 5 D/A: Data/Address bit (I<sup>2</sup>C mode only) 1 = Indicates that the last byte received or transmitted was data 0 = Indicates that the last byte received or transmitted was address P: STOP bit bit 4 $(l^2C \text{ mode only})$ . This bit is cleared when the MSSP module is disabled, SSPEN is cleared.) 1 = Indicates that a STOP bit has been detected last (this bit is '0' on RESET) 0 = STOP bit was not detected last bit 3 S: START bit (I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.) 1 = Indicates that a START bit has been detected last (this bit is '0' on RESET) 0 = START bit was not detected last **R/W**: Read/Write bit Information (I<sup>2</sup>C mode only) bit 2 This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to the next START bit, STOP bit, or not ACK bit. In I<sup>2</sup>C Slave mode: 1 = Read0 = WriteIn I<sup>2</sup>C Master mode: 1 = Transmit is in progress 0 = Transmit is not in progress Oring this bit with SEN, RSEN, PEN, RCEN, or ACKEN will indicate if the MSSP is in IDLE mode. bit 1 **UA**: Update Address (10-bit I<sup>2</sup>C mode only) 1 = Indicates that the user needs to update the address in the SSPADD register 0 = Address does not need to be updated bit 0 BF: Buffer Full Status bit Receive (SPI and I<sup>2</sup>C modes) 1 = Receive complete, SSPBUF is full 0 = Receive not complete, SSPBUF is empty Transmit (I<sup>2</sup>C mode only) 1 = Data transmit in progress (does not include the ACK and STOP bits), SSPBUF is full 0 = Data transmit complete (does not include the ACK and STOP bits), SSPBUF is emptyLegend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

#### 15.2.3 SLEEP OPERATION

While in SLEEP mode, the  $I^2C$  module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from SLEEP (if the SSP interrupt is enabled).

#### 15.2.4 EFFECTS OF A RESET

A RESET disables the SSP module and terminates the current transfer.

| Address       | Name    | Bit 7    | Bit 6         | Bit 5                    | Bit 4      | Bit 3      | Bit 2  | Bit 1 | Bit 0 | POR, BOR  | MCLR, WDT |

|---------------|---------|----------|---------------|--------------------------|------------|------------|--------|-------|-------|-----------|-----------|

| 07h, Unbanked | INTSTA  | PEIF     | T0CKIF        | TOIF                     | INTF       | PEIE       | T0CKIE | T0IE  | INTE  | 0000 0000 | 0000 0000 |

| 10h, Bank 4   | PIR2    | SSPIF    | BCLIF         | ADIF                     | _          | CA4IF      | CA3IF  | TX2IF | RC2IF | 000- 0000 | 000- 0000 |

| 11h, Bank 4   | PIE2    | SSPIE    | BCLIE         | ADIE                     | _          | CA4IE      | CA3IE  | TX2IE | RC2IE | 000- 0000 | 000- 0000 |

| 10h. Bank 6   | SSPADD  | Synchror | nous Serial P | ort (I <sup>2</sup> C mo | de) Addres | s Register |        |       |       | 0000 0000 | 0000 0000 |

| 14h, Bank 6   | SSPBUF  | Synchror | nous Serial P | ort Receive              | Buffer/Tra | nsmit Regi | ister  |       |       | XXXX XXXX | սսսս սսսս |

| 11h, Bank 6   | SSPCON1 | WCOL     | SSPOV         | SSPEN                    | CKP        | SSPM3      | SSPM2  | SSPM1 | SSPM0 | 0000 0000 | 0000 0000 |

| 12h, Bank 6   | SSPCON2 | GCEN     | ACKSTAT       | ACKDT                    | ACKEN      | RCEN       | PEN    | RSEN  | SEN   | 0000 0000 | 0000 0000 |

| 13h, Bank 6   | SSPSTAT | SMP      | CKE           | D/A                      | Р          | S          | R/W    | UA    | BF    | 0000 0000 | 0000 0000 |

### TABLE 15-3: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in I<sup>2</sup>C mode.

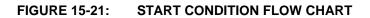

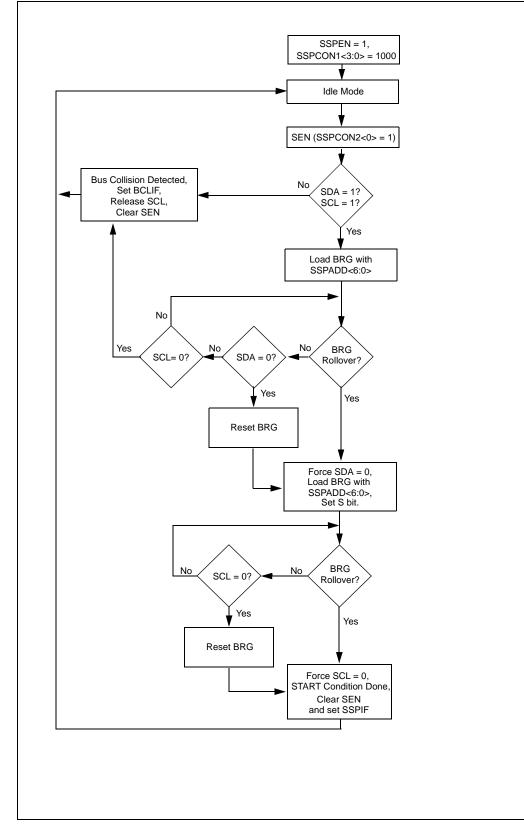

#### FIGURE 15-32: STOP CONDITION FLOW CHART

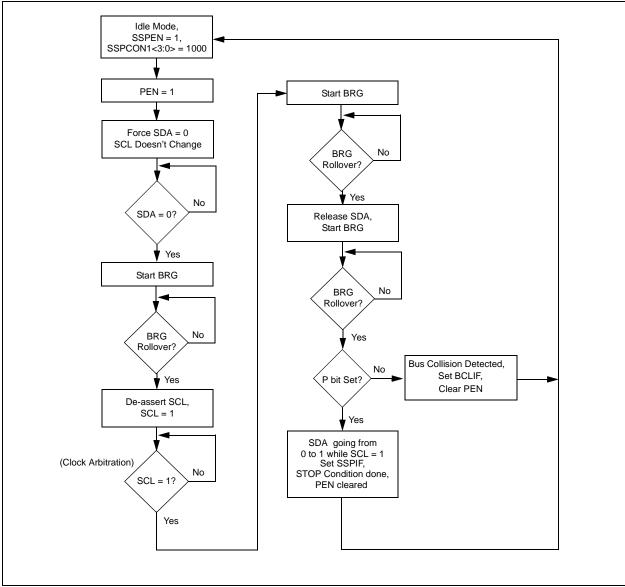

## 15.3 Connection Considerations for I<sup>2</sup>C Bus

For standard mode  $I^2C$  bus devices, the values of resistors  $R_p R_s$  in Figure 15-42 depends on the following parameters:

- Supply voltage

- Bus capacitance

- Number of connected devices (input current + leakage current)

The supply voltage limits the minimum value of resistor  $R_p$  due to the specified minimum sink current of 3 mA at VoL max = 0.4V for the specified output stages. For

example, with a supply voltage of VDD =  $5V \pm 10\%$  and VOL max = 0.4V at 3 mA,  $R_p \min$  = (5.5-0.4)/0.003 = 1.7 k $\Omega$ . VDD as a function of  $R_p$  is shown in Figure 15-42. The desired noise margin of 0.1 VDD for the low level, limits the maximum value of  $R_s$ . Series resistors are optional and used to improve ESD susceptibility.

The bus capacitance is the total capacitance of wire, connections and pins. This capacitance limits the maximum value of  $R_p$  due to the specified rise time (Figure 15-42).

The SMP bit is the slew rate control enabled bit. This bit is in the SSPSTAT register and controls the slew rate of the I/O pins when in  $I^2C$  mode (master or slave).

#### FIGURE 15-42: SAMPLE DEVICE CONFIGURATION FOR I<sup>2</sup>C BUS

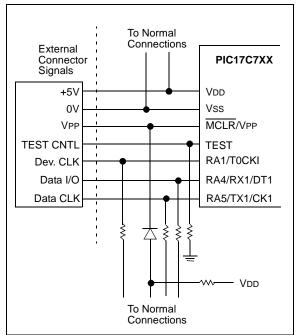

#### 17.6 In-Circuit Serial Programming

The PIC17C7XX group of the high-end family (PIC17CXXX) has an added feature that allows serial programming while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware to be programmed.

Devices may be serialized to make the product unique; "special" variants of the product may be offered and code updates are possible. This allows for increased design flexibility.

To place the device into the Serial Programming Test mode, two pins will need to be placed at VIHH. These are the TEST pin and the MCLR/VPP pin. Also, a sequence of events must occur as follows:

- 1. The TEST pin is placed at VIHH.

- 2. The MCLR/VPP pin is placed at VIHH.

There is a setup time between step 1 and step 2 that must be met.

After this sequence, the Program Counter is pointing to program memory address 0xFF60. This location is in the Boot ROM. The code initializes the USART/SCI so that it can receive commands. For this, the device must be clocked. The device clock source in this mode is the RA1/T0CKI pin. After delaying to allow the USART/SCI to initialize, commands can be received. The flow is shown in these 3 steps:

- 1. The device clock source starts.

- 2. Wait 80 device clocks for Boot ROM code to configure the USART/SCI.

- 3. Commands may now be sent.

|             | During Programming |      |                                                   |  |  |  |

|-------------|--------------------|------|---------------------------------------------------|--|--|--|

| Name        | Function           | Туре | Description                                       |  |  |  |

| RA4/RX1/DT1 | DT                 | I/O  | Serial Data                                       |  |  |  |

| RA5/TX1/CK1 | СК                 | I    | Serial Clock                                      |  |  |  |

| RA1/T0CKI   | OSCI               | I    | Device Clock Source                               |  |  |  |

| TEST        | TEST               | I    | Test mode selection control input, force to VIHH  |  |  |  |

| MCLR/VPP    | MCLR/VPP           | Р    | Master Clear Reset and Device Programming Voltage |  |  |  |

| Vdd         | Vdd                | Р    | Positive supply for logic and I/O pins            |  |  |  |

| Vss         | Vss                | Р    | Ground reference for logic and I/O pins           |  |  |  |

#### TABLE 17-3: ICSP INTERFACE PINS

For complete details of serial programming, please refer to the PIC17C7XX Programming Specification. (Contact your local Microchip Technology Sales Office for availability.)

FIGURE 17-3:

#### TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

# PIC17C7XX

| MO\   | /PF            | Move p te                                                                                                           | o f                                                                                              |      |                       |  |  |  |  |

|-------|----------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------|-----------------------|--|--|--|--|

| Synt  | ax:            | [label] N                                                                                                           | [label] MOVPF p,f                                                                                |      |                       |  |  |  |  |

| Ope   | rands:         |                                                                                                                     | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq p \leq 31 \end{array}$                             |      |                       |  |  |  |  |

| Ope   | ration:        | $(p) \to (f)$                                                                                                       |                                                                                                  |      |                       |  |  |  |  |

| Statu | us Affected:   | Z                                                                                                                   |                                                                                                  |      |                       |  |  |  |  |

| Enco  | oding:         | 010p                                                                                                                | рррр                                                                                             | ffff | ffff                  |  |  |  |  |

| Des   | cription:      | 'p' to data r<br>'f' can be a<br>space (00h<br>to 1Fh.<br>Either 'p' o<br>special situ<br>MOVPFis p<br>ring a perip | p' or 'f' can be WREG (a useful,                                                                 |      |                       |  |  |  |  |

|       |                | tion. Both '                                                                                                        | or an I/O port) to a data memory loca-<br>tion. Both 'f' and 'p' can be indirectly<br>addressed. |      |                       |  |  |  |  |

| Wor   | ds:            | 1                                                                                                                   |                                                                                                  |      |                       |  |  |  |  |

| Cycl  | es:            | 1                                                                                                                   |                                                                                                  |      |                       |  |  |  |  |

| QC    | ycle Activity: |                                                                                                                     |                                                                                                  |      |                       |  |  |  |  |

|       | Q1             | Q2                                                                                                                  | Q3                                                                                               | 3    | Q4                    |  |  |  |  |

|       | Decode         | Read<br>register 'p'                                                                                                | Proce<br>Dat                                                                                     |      | Write<br>register 'f' |  |  |  |  |

| Example: | MOVPF | REG1, REG2 |

|----------|-------|------------|

|          |       |            |

| Before | Instruction |

|--------|-------------|

| Delote | manucuon    |

| = | 0x11 |  |  |  |  |  |

|---|------|--|--|--|--|--|

| = | 0x33 |  |  |  |  |  |

|   |      |  |  |  |  |  |

| = | 0x11 |  |  |  |  |  |

|   | 0x11 |  |  |  |  |  |

|   | =    |  |  |  |  |  |

| MOVWF                        | Move WR                    | EG to f       |      |                                 |

|------------------------------|----------------------------|---------------|------|---------------------------------|

| Syntax:                      | [label]                    | MOVWF         | = f  |                                 |

| Operands:                    | $0 \le f \le 25$           | 5             |      |                                 |

| Operation:                   | (WREG) -                   | → (f)         |      |                                 |

| Status Affected:             | None                       |               |      |                                 |

| Encoding:                    | 0000                       | 0001          | ffff | ffff                            |

| Description:                 |                            | can be a      |      | register 'f'.<br>ere in the 256 |

| Words:                       | 1                          |               |      |                                 |

| Cycles:                      | 1                          |               |      |                                 |

| Q Cycle Activity:            |                            |               |      |                                 |

| Q1                           | Q2                         | Q3            |      | Q4                              |

| Decode                       | Read<br>register 'f'       | Proce<br>Data |      | Write<br>register 'f'           |

| Example:                     | MOVWF                      | REG           |      |                                 |

| Before Instru<br>WREG<br>REG | iction<br>= 0x4F<br>= 0xFF |               |      |                                 |

=

0x4F

0x4F

After Instruction WREG =

REG

| RET                                                                                                                                                                                 | FIE                                       | Return fro                                                              | Return from Interrupt |                      |       |                                          | LW             | Returi    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------|-----------------------|----------------------|-------|------------------------------------------|----------------|-----------|

| Synt                                                                                                                                                                                | ax:                                       | [label] I                                                               | RETFIE                |                      | -     | Synt                                     | [ label        |           |

| Ope                                                                                                                                                                                 | rands:                                    | None                                                                    |                       |                      |       | Ope                                      | rands:         | 0 ≤ k ≤   |

| Ope                                                                                                                                                                                 | ration:                                   | $\begin{array}{l} TOS \rightarrow (P \\ 0 \rightarrow GLIN \end{array}$ | TD;                   |                      |       | Operation:                               |                |           |

| PCLATH is unchanged.                                                                                                                                                                |                                           |                                                                         |                       |                      | State | us Affected:                             | None           |           |

| State                                                                                                                                                                               | us Affected:                              | GLINTD                                                                  |                       |                      | _     | Enco                                     | oding:         | 1011      |

| Enco                                                                                                                                                                                | oding:                                    | 0000                                                                    | 0000 000              | 0 0101               |       | Des                                      | cription:      | WREG      |

| Description:<br>Return from Interrupt. Stack is POP'ed<br>and Top-of-Stack (TOS) is loaded in the<br>PC. Interrupts are enabled by clearing<br>the GLINTD bit. GLINTD is the global |                                           |                                                                         | _                     |                      |       | 'k'. The<br>the top<br>The hig<br>remain |                |           |

|                                                                                                                                                                                     |                                           | interrupt dis                                                           | able bit (CPU         | STA<4>).             |       | Wor                                      | ds:            | 1         |

| Wor                                                                                                                                                                                 | ds:                                       | 1                                                                       |                       |                      |       | Cycl                                     | es:            | 2         |

| Cycl                                                                                                                                                                                | es:                                       | 2                                                                       |                       |                      |       | QC                                       | ycle Activity: |           |

| QC                                                                                                                                                                                  | ycle Activity:                            |                                                                         |                       |                      |       |                                          | Q1             | Q2        |

|                                                                                                                                                                                     | Q1                                        | Q2                                                                      | Q3                    | Q4                   |       |                                          | Decode         | Read      |

|                                                                                                                                                                                     | Decode                                    | No<br>operation                                                         | Clear<br>GLINTD       | POP PC<br>from stack |       |                                          |                | literal ' |

|                                                                                                                                                                                     | No                                        | No                                                                      | No                    | No                   |       |                                          | No             | No        |

|                                                                                                                                                                                     | operation                                 | operation                                                               | operation             | operation            | ]     |                                          | operation      | operatio  |

| <u>Exa</u>                                                                                                                                                                          | <u>mple</u> :                             | RETFIE                                                                  |                       |                      |       | <b>F</b>                                 |                | CALLT     |

|                                                                                                                                                                                     | After Interrupt<br>PC = TOS<br>GLINTD = 0 |                                                                         |                       |                      |       | <u>Exai</u>                              | <u>mple</u> :  | CALL T    |

| RET              | LW             | Return Li                                   | Return Literal to WREG                                                                                                                                                                      |               |                                          |  |  |  |

|------------------|----------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------------------------|--|--|--|

| Synt             | ax:            | [label]                                     | [label] RETLW k                                                                                                                                                                             |               |                                          |  |  |  |

| Ope              | rands:         | $0 \le k \le 25$                            | $0 \le k \le 255$                                                                                                                                                                           |               |                                          |  |  |  |

| Ope              | ration:        | · ·                                         | $k \rightarrow (WREG); TOS \rightarrow (PC);$<br>PCLATH is unchanged                                                                                                                        |               |                                          |  |  |  |

| State            | us Affected:   | None                                        |                                                                                                                                                                                             |               |                                          |  |  |  |

| Enco             | oding:         | 1011                                        | 0110                                                                                                                                                                                        | kkkk          | kkkk                                     |  |  |  |

| Description:     |                | 'k'. The pro<br>the top of th<br>The high a | WREG is loaded with the eight-bit literal<br>'k'. The program counter is loaded from<br>the top of the stack (the return address).<br>The high address latch (PCLATH)<br>remains unchanged. |               |                                          |  |  |  |

| Wor              | ds:            | 1                                           | 1                                                                                                                                                                                           |               |                                          |  |  |  |

| Cycl             | es:            | 2                                           | 2                                                                                                                                                                                           |               |                                          |  |  |  |

| QC               | vcle Activity: |                                             |                                                                                                                                                                                             |               |                                          |  |  |  |

|                  | Q1             | Q2                                          | Q3                                                                                                                                                                                          | 3             | Q4                                       |  |  |  |

|                  | Decode         | Read<br>literal 'k'                         | Proce<br>Dat                                                                                                                                                                                |               | POP PC<br>rom stack,<br>Write to<br>WREG |  |  |  |

|                  | No             | No                                          | No                                                                                                                                                                                          |               | No                                       |  |  |  |

|                  | operation      | operation                                   | opera                                                                                                                                                                                       | tion          | operation                                |  |  |  |

| <u>Example</u> : |                | ; WR                                        | et value<br>EG now has<br>e value<br>; ; WREG :                                                                                                                                             | s<br>= offset | ble                                      |  |  |  |

. RETLW kn ; End of table

0x07

WREG = value of k7

Before Instruction WREG =

After Instruction

© 1998-2013 Microchip Technology Inc.

| TABLRD                                                        | Table Read                                      |                                          | <u> </u> |

|---------------------------------------------------------------|-------------------------------------------------|------------------------------------------|----------|

| Example1:                                                     | TABLRD 1, 1, R                                  | EG ;                                     | S        |

| Before Instruc<br>REG<br>TBLATH<br>TBLATL<br>TBLPTR<br>MEMORY | ction =<br>=<br>=<br>=<br>(TBLPTR) =            | 0x53<br>0xAA<br>0x55<br>0xA356<br>0x1234 | 0        |

| REG<br>TBLATH<br>TBLATL<br>TBLPTR<br>MEMORY                   | on (table write co<br>=<br>=<br>(TBLPTR) =      | 0xAA<br>0x12<br>0x34<br>0xA357<br>0x5678 |          |

| Example2:                                                     | TABLRD 0, 0, R                                  | EG;                                      | S        |

| Before Instruc<br>REG<br>TBLATH<br>TBLATL<br>TBLPTR<br>MEMORY | ction =<br>=<br>=<br>=<br>(TBLPTR) =            | 0x53<br>0xAA<br>0x55<br>0xA356<br>0x1234 | E        |

| REG<br>TBLATH<br>TBLATL<br>TBLPTR                             | on (table write co<br>=<br>=<br>=<br>(TBLPTR) = | 0x55<br>0x12<br>0x34<br>0xA356<br>0x1234 |          |

|                                                               |                                                 |                                          |          |

|                                                               |                                                 |                                          | M<br>C   |

| TAB                                              | LWT               | Table Write                                                                                                                                                                                                |  |  |  |  |  |

|--------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Synt                                             | ax:               | [label] TABLWT t,i,f                                                                                                                                                                                       |  |  |  |  |  |

| Ope                                              | rands:            | $0 \le f \le 255$<br>i $\in [0,1]$<br>t $\in [0,1]$                                                                                                                                                        |  |  |  |  |  |

| Ope                                              | ration:           | If t = 0,<br>f $\rightarrow$ TBLATL;<br>If t = 1,<br>f $\rightarrow$ TBLATH;<br>TBLAT $\rightarrow$ Prog Mem (TBLPTR);<br>If i = 1,<br>TBLPTR + 1 $\rightarrow$ TBLPTR<br>If i = 0,<br>TBLPTR is unchanged |  |  |  |  |  |

| Statu                                            | us Affected       | None                                                                                                                                                                                                       |  |  |  |  |  |

| Enco                                             | oding:            | 1010 11ti ffff ffff                                                                                                                                                                                        |  |  |  |  |  |

| voltage<br>m <u>emory</u><br>If MCLR<br>the prog |                   | CLR/VPP = VDD<br>programming sequence of internal memory<br>be interrupted. A short write will occur (2<br>. The internal memory location will not be                                                      |  |  |  |  |  |

|                                                  | affec             | 3. The TBLPTR can be automati-                                                                                                                                                                             |  |  |  |  |  |

|                                                  |                   | cally incremented                                                                                                                                                                                          |  |  |  |  |  |

|                                                  |                   | If i = 1; TBLPTR is not<br>incremented                                                                                                                                                                     |  |  |  |  |  |

|                                                  |                   | If i = 0; TBLPTR is incremented                                                                                                                                                                            |  |  |  |  |  |

| Wor                                              | ds:               | 1                                                                                                                                                                                                          |  |  |  |  |  |

| Cycl                                             | es:               | 2 (many if write is to on-chip<br>EPROM program memory)                                                                                                                                                    |  |  |  |  |  |

| QC                                               | Q Cycle Activity: |                                                                                                                                                                                                            |  |  |  |  |  |

|                                                  | Q1                | Q2 Q3 Q4                                                                                                                                                                                                   |  |  |  |  |  |

|                                                  | Decode            | Read Process Write<br>register 'f' Data register<br>TBLATH or<br>TBLATL                                                                                                                                    |  |  |  |  |  |

|                                                  | No<br>operation   | NoNoNooperationoperationoperation(Table Pointer(Table Latch onon AddressAddress bus,bus)WR goes low)                                                                                                       |  |  |  |  |  |

## PIC17C7XX

NOTES:

| PIC17LC7XX-08                                              |       |                             | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature          |         |                              |                                   |                                                                                                                                                 |

|------------------------------------------------------------|-------|-----------------------------|-------------------------------------------------------------------------------------------|---------|------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| (Commercial, Industrial)                                   |       |                             | -40°C $\leq$ TA $\leq$ +85°C for industrial and 0°C $\leq$ TA $\leq$ +70°C for commercial |         |                              |                                   |                                                                                                                                                 |

|                                                            |       |                             | Standard<br>Operating                                                                     |         | ng Cond<br>ature<br>-4<br>-4 | itions (u<br>0°C ≤ TA<br>0°C ≤ T⁄ | nless otherwise stated)<br>$\leq +125^{\circ}$ C for extended<br>$A \leq +85^{\circ}$ C for industrial<br>$A \leq +70^{\circ}$ C for commercial |

| Param.<br>No.                                              | Sym   | Characteristic              | Min                                                                                       | Тур†    | Мах                          | Units                             | Conditions                                                                                                                                      |

| D010                                                       | Idd   | Supply Current (Note 2      | 2)                                                                                        |         |                              |                                   |                                                                                                                                                 |

|                                                            |       | PIC17LC7XX                  | —                                                                                         | 3       | 6                            | mA                                | Fosc = 4 MHz (Note 4)                                                                                                                           |

| D010                                                       |       | PIC17C7XX                   | —                                                                                         | 3       | 6                            | mA                                | Fosc = 4 MHz (Note 4)                                                                                                                           |

| D011                                                       |       | PIC17LC7XX                  | —                                                                                         | 5       | 10                           | mA                                | Fosc = 8 MHz                                                                                                                                    |

| D011<br>D012                                               |       | PIC17C7XX                   | _                                                                                         | 5<br>9  | 10<br>18                     | mA<br>mA                          | Fosc = 8 MHz<br>Fosc = 16 MHz                                                                                                                   |

| D014                                                       |       | PIC17LC7XX                  | —                                                                                         | 85      | 150                          | μΑ                                | Fosc = 32 kHz,<br>(EC osc configuration)                                                                                                        |

| D015                                                       |       | PIC17C7XX                   | —                                                                                         | 15      | 30                           | mA                                | Fosc = 33 MHz                                                                                                                                   |

| D021                                                       | IPD   | Power-down Current (        | Note 3)                                                                                   |         |                              |                                   |                                                                                                                                                 |

|                                                            |       | PIC17LC7XX                  | —                                                                                         | <1      | 5                            | μA                                | VDD = 3.0V, WDT disabled                                                                                                                        |

| D021<br>(commercial,<br>industrial)<br>D021A<br>(extended) |       | PIC17C7XX                   | _                                                                                         | <1<br>2 | 20<br>20                     | μΑ                                | VDD = 5.5V, WDT disabled<br>VDD = 5.5V, WDT disabled                                                                                            |

|                                                            |       | Module Differential Current |                                                                                           |         |                              |                                   |                                                                                                                                                 |

| D023                                                       | ∆lbor | BOR circuitry               | _                                                                                         | 75      | 150                          | μA                                | VDD = 4.5V, BODEN<br>enabled                                                                                                                    |

| D024                                                       | ∆IWDT | Watchdog Timer              | -                                                                                         | 10      | 35                           | μΑ                                | VDD = 5.5V                                                                                                                                      |

| D026                                                       | ΔIAD  | A/D converter               | _                                                                                         | 1       | -                            | μA                                | VDD = 5.5V, A/D not<br>converting                                                                                                               |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

<u>OSC1</u> = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD or VSS, T0CKI = VDD, MCLR = VDD; WDT disabled.

Current consumed from the oscillator and I/O's driving external capacitive or resistive loads needs to be considered.

For the RC oscillator, the current through the external pull-up resistor (R) can be estimated as:  $VDD/(2 \bullet R)$ .

For capacitive loads, the current can be estimated (for an individual I/O pin) as (CL  $\bullet$  VDD)  $\bullet$  f

CL = Total capacitive load on the I/O pin; f = average frequency the I/O pin switches.

The capacitive currents are most significant when the device is configured for external execution (includes Extended Microcontroller mode).

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSs.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula IR = VDD/2REXT (mA) with REXT in kOhm.

- **5:** This is the voltage where the device enters the Brown-out Reset. When BOR is enabled, the device (-16) will operate correctly to this trip point.

#### 20.3 Timing Parameter Symbology

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2ppS |                                      | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|-------------|--------------------------------------|-----------|----------------------------------------|

| 2. TppS     |                                      | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т           |                                      |           |                                        |

| F           | Frequency                            | Т         | Time                                   |

| Lowerc      | ase symbols (pp) and their meanings: |           |                                        |

| рр          |                                      |           |                                        |

| ad          | Address/Data                         | ost       | Oscillator Start-Up Timer              |

| al          | ALE                                  | pwrt      | Power-Up Timer                         |

| сс          | Capture1 and Capture2                | rb        | PORTB                                  |

| ck          | CLKOUT or clock                      | rd        | RD                                     |

| dt          | Data in                              | rw        | RD or WR                               |

| in          | INT pin                              | tO        | ТОСКІ                                  |

| io          | I/O port                             | t123      | TCLK12 and TCLK3                       |

| mc          | MCLR                                 | wdt       | Watchdog Timer                         |

| oe          | OE                                   | wr        | WR                                     |

| OS          | OSC1                                 |           |                                        |

| Upperc      | ase symbols and their meanings:      |           |                                        |

| S           |                                      |           |                                        |

| D           | Driven                               | L         | Low                                    |

| E           | Edge                                 | Р         | Period                                 |

| F           | Fall                                 | R         | Rise                                   |

| Н           | High                                 | V         | Valid                                  |

| I           | Invalid (Hi-impedance)               | Z         | Hi-impedance                           |

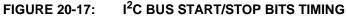

| TABLE 20-12: I <sup>2</sup> C | <b>BUS START/STOP</b> | BITS REQUIREMENTS |

|-------------------------------|-----------------------|-------------------|

|-------------------------------|-----------------------|-------------------|

| Param.<br>No. | Sym     | Charac          | teristic                  | Min              | Ту<br>р | Max | Units | Conditions                   |

|---------------|---------|-----------------|---------------------------|------------------|---------|-----|-------|------------------------------|

| 90            | Tsu:sta | START condition | 100 kHz mode              | 2(Tosc)(BRG + 1) | _       | _   | ns    | Only relevant for            |

|               |         | Setup time      | 400 kHz mode              | 2(Tosc)(BRG + 1) | _       | —   |       | Repeated Start condition     |

|               |         |                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _       | —   |       |                              |

| 91            | Thd:sta | START condition | 100 kHz mode              | 2(Tosc)(BRG + 1) | _       | —   | ns    | After this period, the first |

|               |         | Hold time       | 400 kHz mode              | 2(Tosc)(BRG + 1) |         | —   |       | clock pulse is generated     |

|               |         |                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) |         | —   |       |                              |

| 92            | Tsu:sto | STOP condition  | 100 kHz mode              | 2(Tosc)(BRG + 1) | _       | —   | ns    |                              |

|               |         | Setup time      | 400 kHz mode              | 2(Tosc)(BRG + 1) |         | —   |       |                              |

|               |         |                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) |         | —   |       |                              |

| 93            | Thd:sto | STOP condition  | 100 kHz mode              | 2(Tosc)(BRG + 1) | _       | —   | ns    |                              |

|               |         | Hold time       | 400 kHz mode              | 2(Tosc)(BRG + 1) | _       | —   |       |                              |

|               |         |                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _       | —   |       |                              |

**Note 1:** Maximum pin capacitance = 10 pF for all I<sup>2</sup>C pins.

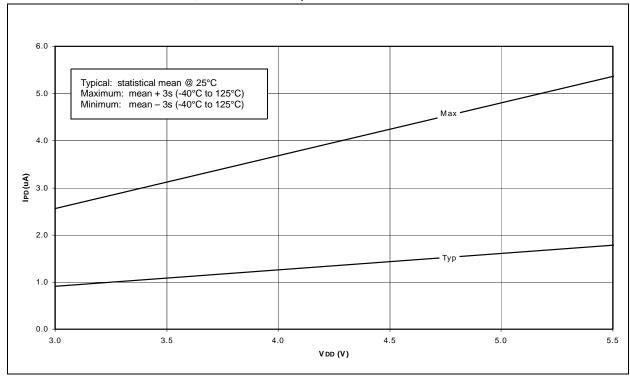

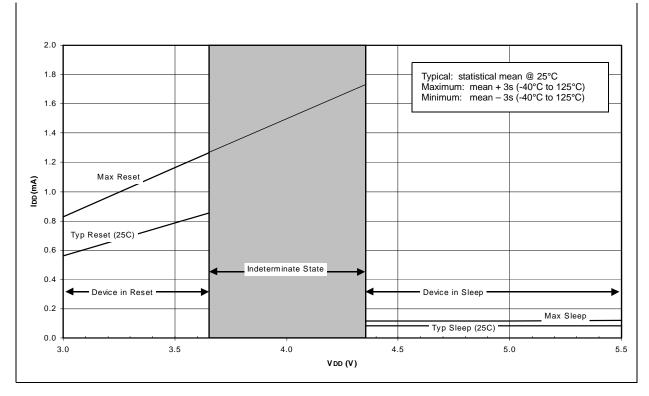

### 21.0 PIC17C7XX DC AND AC CHARACTERISTICS

The graphs and tables provided in this section are for design guidance and are not tested nor guaranteed. In some graphs or tables the data presented is outside specified operating range (e.g., outside specified VDD range). This is for information only and devices are ensured to operate properly only within the specified range.

The data presented in this section is a statistical summary of data collected on units from different lots over a period of time.

- Typ or Typical represents the mean of the distribution at 25°C.

- Max or Maximum represents (mean + 3 $\sigma$ ) over the temperature range of -40°C to 85°C.

- Min or Minimum represents (mean  $3\sigma$ ) over the temperature range of -40°C to  $85^{\circ}$ C.

- **Note:** Standard deviation is denoted by sigma ( $\sigma$ ).

#### TABLE 21-1: PIN CAPACITANCE PER PACKAGE TYPE

| Pin Name                            | Typical Capacitance (pF) |             |  |  |  |

|-------------------------------------|--------------------------|-------------|--|--|--|

|                                     | 68-pin PLCC              | 64-pin TQFP |  |  |  |

| All pins, except MCLR, VDD, and Vss | 10                       | 10          |  |  |  |

| MCLR pin                            | 20                       | 20          |  |  |  |

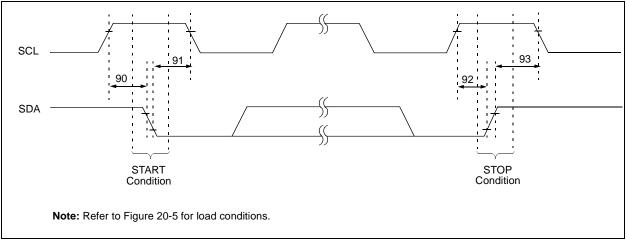

#### FIGURE 21-1: TYPICAL RC OSCILLATOR FREQUENCY vs. TEMPERATURE

FIGURE 21-11: TYPICAL AND MAXIMUM IPD vs. VDD (SLEEP MODE, ALL PERIPHERALS DISABLED, -40°C to +125°C)

FIGURE 21-12: TYPICAL AND MAXIMUM IPD vs. VDD (SLEEP MODE, BOR ENABLED, -40°C to +125°C)

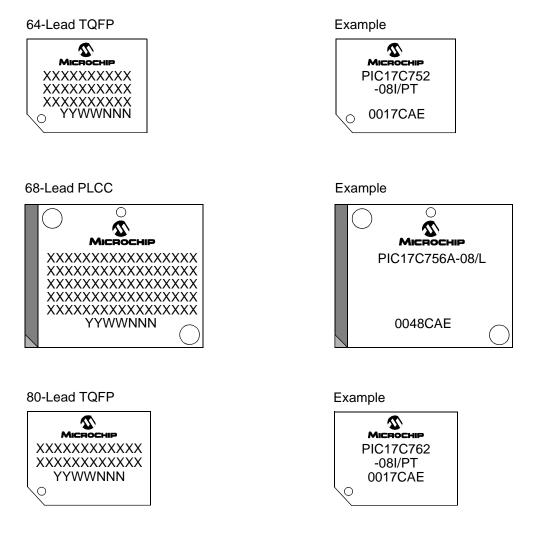

#### 22.0 PACKAGING INFORMATION

#### 22.1 Package Marking Information

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carrie                                | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                                                                                                                                                                                                  |