Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 33MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 50                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 902 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c756a-33e-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

NOTES:

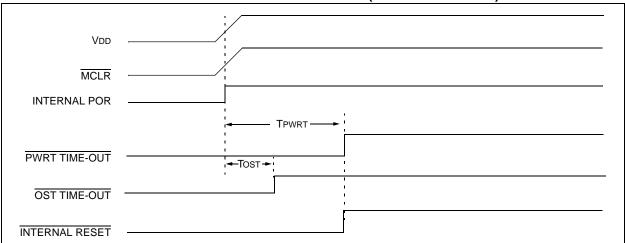

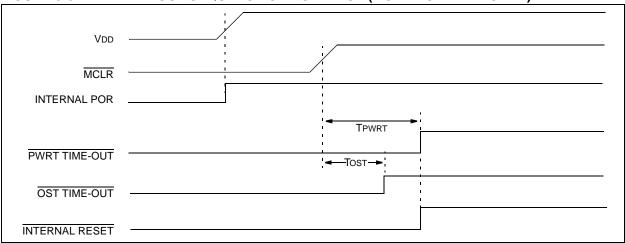

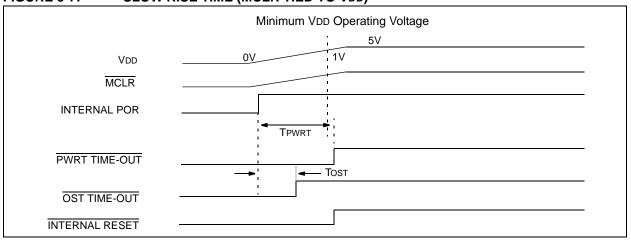

In Figure 5-5, Figure 5-6 and Figure 5-7, the TPWRT timer time-out is greater then the Tost timer time-out, as would be the case in higher frequency crystals. For lower frequency crystals (i.e., 32 kHz), Tost may be greater.

FIGURE 5-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

FIGURE 5-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD)

FIGURE 5-7: SLOW RISE TIME (MCLR TIED TO VDD)

# 6.3 Peripheral Interrupt Request Register1 (PIR1) and Register2 (PIR2)

These registers contains the individual flag bits for the peripheral interrupts.

These bits will be set by the specified condition, even if the corresponding interrupt enable bit is cleared (interrupt disabled), or the GLINTD bit is set (all interrupts disabled). Before enabling an interrupt, the user may wish to clear the interrupt flag to ensure that the program does not immediately branch to the peripheral Interrupt Service Routine.

#### REGISTER 6-4: PIR1 REGISTER (ADDRESS: 16h, BANK 1)

| R/W-x | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 | R-1   | R-0   |

|-------|--------|--------|--------|-------|-------|-------|-------|

| RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF | TX1IF | RC1IF |

| bit 7 |        |        |        |       |       |       | bit 0 |

Note:

- bit 7 RBIF: PORTB Interrupt-on-Change Flag bit

- 1 = One of the PORTB inputs changed (software must end the mismatch condition)

- 0 = None of the PORTB inputs have changed

- bit 6 TMR3IF: TMR3 Interrupt Flag bit

#### If Capture1 is enabled (CA1/PR3 = 1):

- 1 = TMR3 overflowed

- 0 = TMR3 did not overflow

#### If Capture 1 is disabled (CA1/ $\overline{PR3} = 0$ ):

- 1 = TMR3 value has rolled over to 0000h from equalling the period register (PR3H:PR3L) value

- 0 = TMR3 value has not rolled over to 0000h from equalling the period register (PR3H:PR3L) value

- bit 5 TMR2IF: TMR2 Interrupt Flag bit

- 1 = TMR2 value has rolled over to 0000h from equalling the period register (PR2) value

- 0 = TMR2 value has not rolled over to 0000h from equalling the period register (PR2) value

- bit 4 TMR1IF: TMR1 Interrupt Flag bit

#### If TMR1 is in 8-bit mode (T16 = 0):

- 1 = TMR1 value has rolled over to 0000h from equalling the period register (PR1) value

- 0 = TMR1 value has not rolled over to 0000h from equalling the period register (PR1) value

#### If Timer1 is in 16-bit mode (T16 = 1):

- 1 = TMR2:TMR1 value has rolled over to 0000h from equalling the period register (PR2:PR1) value

- 0 = TMR2:TMR1 value has not rolled over to 0000h from equalling the period register (PR2:PR1) value

- bit 3 CA2IF: Capture2 Interrupt Flag bit

- 1 = Capture event occurred on RB1/CAP2 pin

- 0 = Capture event did not occur on RB1/CAP2 pin

- bit 2 CA1IF: Capture1 Interrupt Flag bit

- 1 = Capture event occurred on RB0/CAP1 pin

- 0 = Capture event did not occur on RB0/CAP1 pin

- bit 1 **TX1IF**: USART1 Transmit Interrupt Flag bit (state controlled by hardware)

- 1 = USART1 Transmit buffer is empty

- 0 = USART1 Transmit buffer is full

- bit 0 RC1IF: USART1 Receive Interrupt Flag bit (state controlled by hardware)

- 1 = USART1 Receive buffer is full

- 0 = USART1 Receive buffer is empty

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR Reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### FIGURE 7-5: PIC17C7XX REGISTER FILE MAP

| Addr | Unbanked              | ]                     |                       |                         |                       |                       |                       |                       |                         |

|------|-----------------------|-----------------------|-----------------------|-------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------------------------|

| 00h  | INDF0                 |                       |                       |                         |                       |                       |                       |                       |                         |

| 01h  | FSR0                  |                       |                       |                         |                       |                       |                       |                       |                         |

| 02h  | PCL                   |                       |                       |                         |                       |                       |                       |                       |                         |

| 03h  | PCLATH                |                       |                       |                         |                       |                       |                       |                       |                         |

| 04h  | ALUSTA                |                       |                       |                         |                       |                       |                       |                       |                         |

| 05h  | TOSTA                 |                       |                       |                         |                       |                       |                       |                       |                         |

| 06h  | CPUSTA                |                       |                       |                         |                       |                       |                       |                       |                         |

| 07h  | INTSTA                |                       |                       |                         |                       |                       |                       |                       |                         |

| 08h  | INDF1                 |                       |                       |                         |                       |                       |                       |                       |                         |

| 09h  | FSR1                  |                       |                       |                         |                       |                       |                       |                       |                         |

| 0Ah  | WREG                  |                       |                       |                         |                       |                       |                       |                       |                         |

| 0Bh  | TMR0L                 |                       |                       |                         |                       |                       |                       |                       |                         |

| 0Ch  | TMR0H                 |                       |                       |                         |                       |                       |                       |                       |                         |

| 0Dh  | TBLPTRL               |                       |                       |                         |                       |                       |                       |                       |                         |

| 0Eh  | TBLPTRH               |                       |                       |                         |                       |                       |                       |                       |                         |

| 0Fh  | BSR                   |                       |                       |                         |                       |                       |                       |                       |                         |

|      | Bank 0                | Bank 1 <sup>(1)</sup> | Bank 2 <sup>(1)</sup> | Bank 3 <sup>(1)</sup>   | Bank 4 <sup>(1)</sup> | Bank 5 <sup>(1)</sup> | Bank 6 <sup>(1)</sup> | Bank 7 <sup>(1)</sup> | Bank 8 <sup>(1,4)</sup> |

| 10h  | PORTA                 | DDRC                  | TMR1                  | PW1DCL                  | PIR2                  | DDRF                  | SSPADD                | PW3DCL                | DDRH                    |

| 11h  | DDRB                  | PORTC                 | TMR2                  | PW2DCL                  | PIE2                  | PORTF                 | SSPCON1               | PW3DCH                | PORTH                   |

| 12h  | PORTB                 | DDRD                  | TMR3L                 | PW1DCH                  | _                     | DDRG                  | SSPCON2               | CA3L                  | DDRJ                    |

| 13h  | RCSTA1                | PORTD                 | TMR3H                 | PW2DCH                  | RCSTA2                | PORTG                 | SSPSTAT               | CA3H                  | PORTJ                   |

| 14h  | RCREG1                | DDRE                  | PR1                   | CA2L                    | RCREG2                | ADCON0                | SSPBUF                | CA4L                  | _                       |

| 15h  | TXSTA1                | PORTE                 | PR2                   | CA2H                    | TXSTA2                | ADCON1                | _                     | CA4H                  | _                       |

| 16h  | TXREG1                | PIR1                  | PR3L/CA1L             | TCON1                   | TXREG2                | ADRESL                | _                     | TCON3                 | _                       |

| 17h  | SPBRG1                | PIE1                  | PR3H/CA1H             | TCON2                   | SPBRG2                | ADRESH                | _                     | _                     | _                       |

|      | Unbanked              |                       |                       |                         |                       |                       |                       |                       |                         |

| 18h  | PRODL                 |                       |                       |                         |                       |                       |                       |                       |                         |

| 19h  | PRODH                 |                       |                       |                         |                       |                       |                       |                       |                         |

| 1Ah  | General               |                       |                       |                         |                       |                       |                       |                       |                         |

|      | Purpose               |                       |                       |                         |                       |                       |                       |                       |                         |

| 1Fh  | RAM                   |                       | <del></del>           |                         | 1                     |                       |                       |                       |                         |

|      | Bank 0 <sup>(2)</sup> | Bank 1 <sup>(2)</sup> | Bank 2 <sup>(2)</sup> | Bank 3 <sup>(2,3)</sup> |                       |                       |                       |                       |                         |

| 20h  |                       |                       |                       |                         |                       |                       |                       |                       |                         |

|      | General               | General               | General               | General                 |                       |                       |                       |                       |                         |

|      | Purpose               | Purpose               | Purpose               | Purpose                 |                       |                       |                       |                       |                         |

|      | RAM                   | RAM                   | RAM                   | RAM                     |                       |                       |                       |                       |                         |

|      |                       |                       |                       |                         |                       |                       |                       |                       |                         |

| FFh  |                       |                       |                       |                         |                       |                       |                       |                       |                         |

| Note | 1: SFR file           | locations 10          | 0h - 17h are ba       | anked. The lo           | wer nibble            | of the BSR            | specifies the         | bank. All ur          | banked                  |

- **Note 1:** SFR file locations 10h 17h are banked. The lower nibble of the BSR specifies the bank. All unbanked SFRs ignore the Bank Select Register (BSR) bits.

- 2: General Purpose Registers (GPR) locations 20h FFh, 120h 1FFh, 220h 2FFh, and 320h 3FFh are banked. The upper nibble of the BSR specifies this bank. All other GPRs ignore the Bank Select Register (BSR) bits.

- **3:** RAM bank 3 is not implemented on the PIC17C752 and the PIC17C762. Reading any unimplemented register reads '0's.

- 4: Bank 8 is only implemented on the PIC17C76X devices.

TABLE 7-3: SPECIAL FUNCTION REGISTERS

| Address            | Name                   | Bit 7        | Bit 6                               | Bit 5           | Bit 4           | Bit 3           | Bit 2          | Bit 1          | Bit 0        | Value on<br>POR,<br>BOR | MCLR,<br>WDT |

|--------------------|------------------------|--------------|-------------------------------------|-----------------|-----------------|-----------------|----------------|----------------|--------------|-------------------------|--------------|

| Unbanke            | d                      |              | •                                   |                 |                 | •               |                | •              | •            | •                       | •            |

| 00h                | INDF0                  | Uses conte   | ents of FSR                         | 0 to address    | Data Memor      | ry (not a phy   | sical register | r)             |              |                         |              |

| 01h                | FSR0                   | Indirect Da  | irect Data Memory Address Pointer 0 |                 |                 |                 |                |                |              |                         | uuuu uuuu    |

| 02h                | PCL                    | Low order    | 8-bits of PC                        | ;               |                 |                 |                |                |              | 0000 0000               | 0000 0000    |

| 03h <sup>(1)</sup> | PCLATH                 | Holding Re   | egister for u                       | oper 8-bits o   | f PC            |                 |                |                |              | 0000 0000               | uuuu uuuu    |

| 04h                | ALUSTA                 | FS3          | FS2                                 | FS1             | FS0             | OV              | Z              | DC             | С            | 1111 xxxx               | 1111 uuuu    |

| 05h                | T0STA                  | INTEDG       | T0SE                                | T0CS            | T0PS3           | T0PS2           | T0PS1          | T0PS0          | _            | 0000 000-               | 0000 000-    |

| 06h <sup>(2)</sup> | CPUSTA                 | _            | _                                   | STKAV           | GLINTD          | TO              | PD             | POR            | BOR          | 11 11qq                 | 11 qquu      |

| 07h                | INTSTA                 | PEIF         | T0CKIF                              | TOIF            | INTF            | PEIE            | T0CKIE         | TOIE           | INTE         | 0000 0000               | 0000 0000    |

| 08h                | INDF1                  | Uses conte   | ents of FSR                         | 1 to address    | Data Memor      | ry (not a phy   | sical register | r)             |              |                         |              |

| 09h                | FSR1                   | Indirect Da  | ta Memory                           | Address Poi     | nter 1          |                 |                |                |              | xxxx xxxx               | uuuu uuuu    |

| 0Ah                | WREG                   | Working R    | egister                             |                 |                 |                 |                |                |              | xxxx xxxx               | uuuu uuuu    |

| 0Bh                | TMR0L                  | TMR0 Reg     | gister; Low E                       | Byte            |                 |                 |                |                |              | xxxx xxxx               | uuuu uuuu    |

| 0Ch                | TMR0H                  | TMR0 Reg     | gister; High I                      | Byte            |                 |                 |                |                |              | xxxx xxxx               | uuuu uuuu    |

| 0Dh                | TBLPTRL                | Low Byte o   | of Program I                        | Memory Tab      | le Pointer      |                 |                |                |              | 0000 0000               | 0000 0000    |

| 0Eh                | TBLPTRH                | High Byte    | of Program                          | Memory Tab      | le Pointer      |                 |                |                |              | 0000 0000               | 0000 0000    |

| 0Fh                | BSR                    | Bank Sele    | ct Register                         |                 |                 |                 |                |                |              | 0000 0000               | 0000 0000    |

| Bank 0             |                        |              |                                     |                 |                 |                 |                |                |              |                         |              |

| 10h                | PORTA <sup>(4,6)</sup> | RBPU         | _                                   | RA5/TX1/<br>CK1 | RA4/RX1/<br>DT1 | RA3/SDI/<br>SDA | RA2/SS/<br>SCL | RA1/T0CKI      | RA0/INT      | 0-xx 11xx               | 0-uu 11uu    |

| 11h                | DDRB                   | Data Direc   | tion Registe                        | r for PORTE     | 3               | •               |                | •              | •            | 1111 1111               | 1111 1111    |

| 12h                | PORTB <sup>(4)</sup>   | RB7/<br>SDO  | RB6/<br>SCK                         | RB5/<br>TCLK3   | RB4/<br>TCLK12  | RB3/<br>PWM2    | RB2/<br>PWM1   | RB1/<br>CAP2   | RB0/<br>CAP1 | xxxx xxxx               | uuuu uuuu    |

| 13h                | RCSTA1                 | SPEN         | RX9                                 | SREN            | CREN            | _               | FERR           | OERR           | RX9D         | 0000 -00x               | 0000 -00u    |

| 14h                | RCREG1                 | Serial Port  | Receive Re                          | egister         | •               | •               |                |                |              | xxxx xxxx               | uuuu uuuu    |

| 15h                | TXSTA1                 | CSRC         | TX9                                 | TXEN            | SYNC            | _               | _              | TRMT           | TX9D         | 00001x                  | 00001u       |

| 16h                | TXREG1                 | Serial Port  | Transmit R                          | egister (for L  | JSART1)         | •               |                | •              | •            | xxxx xxxx               | uuuu uuuu    |

| 17h                | SPBRG1                 | Baud Rate    | Generator                           | Register (for   | USART1)         |                 |                |                |              | 0000 0000               | 0000 0000    |

| Bank 1             |                        |              |                                     |                 |                 |                 |                |                |              |                         |              |

| 10h                | DDRC <sup>(5)</sup>    | Data Direc   | tion Registe                        | er for PORTO    | ;               |                 |                |                |              | 1111 1111               | 1111 1111    |

| 11h                | PORTC <sup>(4,5)</sup> |              | RC6/AD6                             |                 | RC4/AD4         | RC3/AD3         | RC2/AD2        | RC1/AD1        | RC0/AD0      | xxxx xxxx               | uuuu uuuu    |

| 12h                | DDRD <sup>(5)</sup>    | Data Direc   | tion Registe                        | r for PORTE     | )<br>)          | l               |                |                |              | 1111 1111               | 1111 1111    |

| 13h                | PORTD <sup>(4,5)</sup> | RD7/<br>AD15 | RD6/<br>AD14                        | RD5/<br>AD13    | RD4/<br>AD12    | RD3/<br>AD11    | RD2/<br>AD10   | RD1/AD9        | RD0/AD8      | xxxx xxxx               | uuuu uuuu    |

| 14h                | DDRE <sup>(5)</sup>    | Data Direc   | tion Registe                        | r for PORTE     | <u> </u>        | <u>l</u>        |                | I              |              | 1111                    | 1111         |

| 15h                | PORTE <sup>(4,5)</sup> | _            | _                                   | _               | _               | RE3/<br>CAP4    | RE2/WR         | RE1/OE         | RE0/ALE      | xxxx                    | uuuu         |

| i                  | i e                    |              |                                     |                 | TME             | 04015           |                | <b>=</b> >///= | 50.05        | <del></del>             | ł            |

| 16h                | PIR1                   | RBIF         | TMR3IF                              | TMR2IF          | TMR1IF          | CA2IF           | CA1IF          | TX1IF          | RC1IF        | x000 0010               | u000 0010    |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0', q = value depends on condition.

Shaded cells are unimplemented, read as '0'.

- Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<15:8> whose contents are updated from, or transferred to, the upper byte of the program counter.

- 2: The TO and PD status bits in CPUSTA are not affected by a MCLR Reset.

- 3: Bank 8 and associated registers are only implemented on the PIC17C76X devices.

- 4: This is the value that will be in the port output latch.

- 5: When the device is configured for Microprocessor or Extended Microcontroller mode, the operation of this port does not rely on these registers.

- 6: On any device RESET, these pins are configured as inputs.

### 7.4.2 INDIRECT ADDRESSING OPERATION

The indirect addressing capability has been enhanced over that of the PIC16CXX family. There are two control bits associated with each FSR register. These two bits configure the FSR register to:

- Auto-decrement the value (address) in the FSR after an indirect access

- Auto-increment the value (address) in the FSR after an indirect access

- No change to the value (address) in the FSR after an indirect access

These control bits are located in the ALUSTA register. The FSR1 register is controlled by the FS3:FS2 bits and FSR0 is controlled by the FS1:FS0 bits.

When using the auto-increment or auto-decrement features, the effect on the FSR is not reflected in the ALUSTA register. For example, if the indirect address causes the FSR to equal '0', the Z bit will not be set.

If the FSR register contains a value of 0h, an indirect read will read 0h (Zero bit is set) while an indirect write will be equivalent to a NOP (status bits are not affected).

Indirect addressing allows single cycle data transfers within the entire data space. This is possible with the use of the MOVPF and MOVPF instructions, where either 'p' or 'f' is specified as INDF0 (or INDF1).

If the source or destination of the indirect address is in banked memory, the location accessed will be determined by the value in the BSR.

A simple program to clear RAM from 20h - FFh is shown in Example 7-1.

#### **EXAMPLE 7-1: INDIRECT ADDRESSING**

```

MOVLW 0x20

; FSR0 = 20h

MOVWF FSR0

ALUSTA, FS1 ; Increment FSR

BCF

BSF

ALUSTA, FSO ; after access

BCF

ALUSTA, C

; C = 0

MOVLW END RAM + 1 ;

; Addr(FSR) = 0

CLRF INDFO, F

CPFSEQ FSR0

; FSR0 = END RAM+1?

; NO, clear next

; YES, All RAM is

; cleared

```

### 7.5 Table Pointer (TBLPTRL and TBLPTRH)

File registers TBLPTRL and TBLPTRH form a 16-bit pointer to address the 64K program memory space. The table pointer is used by instructions TABLWT and TABLRD.

The TABLRD and the TABLWT instructions allow transfer of data between program and data space. The table pointer serves as the 16-bit address of the data word within the program memory. For a more complete description of these registers and the operation of Table Reads and Table Writes, see Section 8.0.

#### 7.6 Table Latch (TBLATH, TBLATL)

The table latch (TBLAT) is a 16-bit register, with TBLATH and TBLATL referring to the high and low bytes of the register. It is not mapped into data or program memory. The table latch is used as a temporary holding latch during data transfer between program and data memory (see TABLRD, TABLWT, TLRD and TLWT instruction descriptions). For a more complete description of these registers and the operation of Table Reads and Table Writes, see Section 8.0.

#### REGISTER 13-2: TCON2 REGISTER (ADDRESS: 17h, BANK 3)

| R-0    | R-0    | R/W-0  | R/W-0  | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|--------|--------|--------|--------|---------|--------|--------|--------|

| CA2OVF | CA10VF | PWM2ON | PWM10N | CA1/PR3 | TMR3ON | TMR2ON | TMR10N |

| bit 7  |        |        |        |         |        |        | bit 0  |

bit 7 CA2OVF: Capture2 Overflow Status bit

This bit indicates that the capture value had not been read from the capture register pair (CA2H:CA2L) before the next capture event occurred. The capture register retains the oldest unread capture value (last capture before overflow). Subsequent capture events will not update the capture register with the TMR3 value until the capture register has been read (both bytes).

- 1 = Overflow occurred on Capture2 register

- 0 = No overflow occurred on Capture2 register

- bit 6 CA10VF: Capture1 Overflow Status bit

This bit indicates that the capture value had not been read from the capture register pair (PR3H/CA1H:PR3L/CA1L), before the next capture event occurred. The capture register retains the oldest unread capture value (last capture before overflow). Subsequent capture events will not update the capture register with the TMR3 value until the capture register has been read (both bytes).

- 1 = Overflow occurred on Capture1 register

- 0 = No overflow occurred on Capture1 register

- bit 5 **PWM2ON**: PWM2 On bit

- 1 = PWM2 is enabled

- (The RB3/PWM2 pin ignores the state of the DDRB<3> bit.)

- 0 = PWM2 is disabled

(The RB3/PWM2 pin uses the state of the DDRB<3> bit for data direction.)

- bit 4 **PWM1ON**: PWM1 On bit

- 1 = PWM1 is enabled

- (The RB2/PWM1 pin ignores the state of the DDRB<2> bit.)

- 0 = PWM1 is disabled

(The RB2/PWM1 pin uses the state of the DDRB<2> bit for data direction.)

- bit 3 CA1/PR3: CA1/PR3 Register Mode Select bit

- 1 = Enables Capture1

(PR3H/CA1H:PR3L/CA1L is the Capture1 register. Timer3 runs without a period register.)

0 = Enables the Period register

(PR3H/CA1H:PR3L/CA1L is the Period register for Timer3.)

- bit 2 TMR3ON: Timer3 On bit

- 1 = Starts Timer3

- 0 = Stops Timer3

- bit 1 TMR2ON: Timer2 On bit

This bit controls the incrementing of the TMR2 register. When TMR2:TMR1 form the 16-bit timer (T16 is set), TMR2ON must be set. This allows the MSB of the timer to increment.

- 1 = Starts Timer2 (must be enabled if the T16 bit (TCON1<3>) is set)

- 0 = Stops Timer2

- bit 0 TMR10N: Timer1 On bit

When T16 is set (in 16-bit Timer mode):

- 1 = Starts 16-bit TMR2:TMR1

- 0 = Stops 16-bit TMR2:TMR1

When T16 is clear (in 8-bit Timer mode:

- 1 = Starts 8-bit Timer1

- 0 = Stops 8-bit Timer1

| Le | g | е | n | d | • |

|----|---|---|---|---|---|

|    |   |   |   |   |   |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR Reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

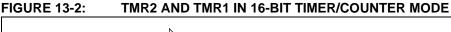

#### 13.1.2 TIMER1 AND TIMER2 IN 16-BIT MODE

To select 16-bit mode, set the T16 bit. In this mode, TMR2 and TMR1 are concatenated to form a 16-bit timer (TMR2:TMR1). The 16-bit timer increments until it matches the 16-bit period register (PR2:PR1). On the following timer clock, the timer value is reset to 0h, and the TMR1IF bit is set.

When selecting the clock source for the 16-bit timer, the TMR1CS bit controls the entire 16-bit timer and TMR2CS is a "don't care", however, ensure that TMR2ON is set (allows TMR2 to increment). When TMR1CS is clear, the timer increments once every instruction cycle (Fosc/4). When TMR1CS is set, the timer increments on every falling edge of the RB4/ TCLK12 pin. For the 16-bit timer to increment, both TMR1ON and TMR2ON bits must be set (Table 13-2).

**TABLE 13-2: TURNING ON 16-BIT TIMER**

| T16 | TMR2ON | TMR10N | Result                         |

|-----|--------|--------|--------------------------------|

| 1   | 1      | 1      | 16-bit timer<br>(TMR2:TMR1) ON |

| 1   | 0      | 1      | Only TMR1 increments           |

| 1   | х      | 0      | 16-bit timer OFF               |

| 0   | 1      | 1      | Timers in 8-bit mode           |

#### 13.1.2.1 External Clock Input for TMR2:TMR1

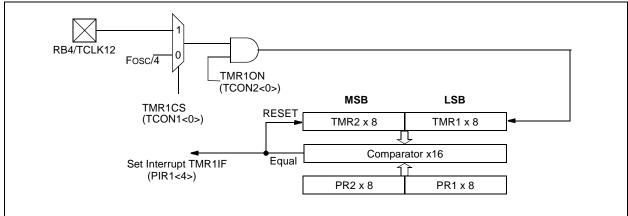

When TMR1CS is set, the 16-bit TMR2:TMR1 increments on the falling edge of clock input TCLK12. The input on the RB4/TCLK12 pin is sampled and synchronized by the internal phase clocks twice every instruction cycle. This causes a delay from the time a falling edge appears on RB4/TCLK12 to the time TMR2:TMR1 is actually incremented. For the external clock input timing requirements, see the Electrical Specification section.

### 13.2.4 EXTERNAL CLOCK INPUT FOR TIMER3

When TMR3CS is set, the 16-bit TMR3 increments on the falling edge of clock input TCLK3. The input on the RB5/TCLK3 pin is sampled and synchronized by the internal phase clocks, twice every instruction cycle. This causes a delay from the time a falling edge appears on TCLK3 to the time TMR3 is actually incremented. For the external clock input timing requirements, see the Electrical Specification section. Figure 13-7 shows the timing diagram when operating from an external clock.

#### 13.2.5 READING/WRITING TIMER3

Since Timer3 is a 16-bit timer and only 8-bits at a time can be read or written, care should be taken when reading or writing while the timer is running. The best method is to stop the timer, perform any read or write operation and then restart Timer3 (using the TMR3ON bit). However, if it is necessary to keep Timer3 freerunning, care must be taken. For writing to the 16-bit TMR3, Example 13-2 may be used. For reading the 16-bit TMR3, Example 13-3 may be used. Interrupts must be disabled during this routine.

#### **EXAMPLE 13-2: WRITING TO TMR3**

```

BSF CPUSTA, GLINTD ; Disable interrupts

MOVFP RAM_L, TMR3L ;

MOVFP RAM_H, TMR3H ;

BCF CPUSTA, GLINTD ; Done, enable interrupts

```

#### **EXAMPLE 13-3: READING FROM TMR3**

```

; read low TMR3

MOVPF

TMR3L, TMPLO

MOVPF

TMR3H, TMPHI

; read high TMR3

MOVFP

TMPLO, WREG

; tmplo -> wreg

CPFSLT

TMR3L

; TMR3L < wreg?

RETURN

; no then return

MOVPF

TMR3L, TMPLO

: read low TMR3

MOVPF

TMR3H, TMPHI

; read high TMR3

RETURN

; return

```

#### FIGURE 13-7: TIMER1, TIMER2 AND TIMER3 OPERATION (IN COUNTER MODE)

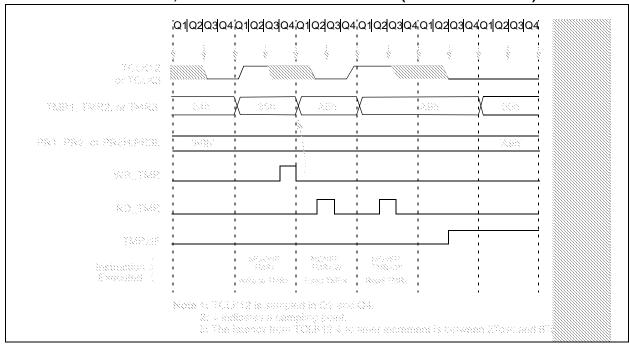

The SSPSTAT register gives the status of the data transfer. This information includes detection of a START or STOP bit, specifies if the received byte was data or address if the next byte is the completion of 10-bit address and if this will be a read or write data transfer.

The SSPBUF is the register to which transfer data is written to or read from. The SSPSR register shifts the data in or out of the device. In receive operations, the SSPBUF and SSPSR create a doubled buffered receiver. This allows reception of the next byte to begin before reading the last byte of received data. When the complete byte is received, it is transferred to the SSPBUF register and flag bit SSPIF is set. If another complete byte is received before the SSPBUF register is read, a receiver overflow has occurred and bit SSPOV (SSPCON1<6>) is set and the byte in the SSPSR is lost.

The SSPADD register holds the slave address. In 10-bit mode, the user needs to write the high byte of the address (1111  $\,^{0}$  A9 A8  $\,^{0}$ ). Following the high byte address match, the low byte of the address needs to be loaded (A7:A0).

#### 15.2.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs. The MSSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched or the data transfer after an address match is received, the hardware automatically will generate the acknowledge (ACK) pulse and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the MSSP module not to give this  $\overline{ACK}$  pulse. These are if either (or both):

- The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- The overflow bit SSPOV (SSPCON1<6>) was set before the transfer was received.

If the BF bit is set, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF and SSPOV are set. Table 15-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low time for proper operation. The high and low times of the I<sup>2</sup>C specification, as well as the requirement of the MSSP module, are shown in timing parameter #100 and parameter #101 of the Electrical Specifications.

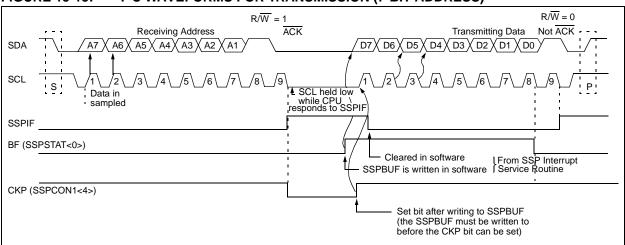

#### 15.2.1.3 Slave Transmission

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The  $\overline{ACK}$  pulse will be sent on the ninth bit, and the SCL pin is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then SCL pin should be enabled by setting bit CKP (SSPCON1<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 15-13).

An SSP interrupt is generated for each data transfer byte. The SSPIF flag bit must be cleared in software, and the SSPSTAT register is used to determine the status of the byte transfer. The SSPIF flag bit is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the not  $\overline{ACK}$  is latched by the slave, the slave logic is reset and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, the SCL pin should be enabled by setting the CKP bit.

#### FIGURE 15-12: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

### FIGURE 15-13: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

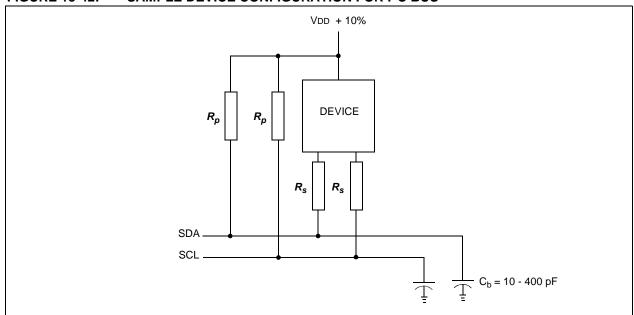

### 15.3 Connection Considerations for I<sup>2</sup>C Bus

For standard mode  $I^2C$  bus devices, the values of resistors  $R_p$   $R_s$  in Figure 15-42 depends on the following parameters:

- · Supply voltage

- · Bus capacitance

- Number of connected devices (input current + leakage current)

The supply voltage limits the minimum value of resistor  $R_p$  due to the specified minimum sink current of 3 mA at Vol max = 0.4V for the specified output stages. For

example, with a supply voltage of VDD = 5V  $\pm 10\%$  and VOL max = 0.4V at 3 mA,  $R_p$  min = (5.5-0.4)/0.003 = 1.7 k $\Omega$ . VDD as a function of  $R_p$  is shown in Figure 15-42. The desired noise margin of 0.1 VDD for the low level, limits the maximum value of  $R_s$ . Series resistors are optional and used to improve ESD susceptibility.

The bus capacitance is the total capacitance of wire, connections and pins. This capacitance limits the maximum value of  $R_p$  due to the specified rise time (Figure 15-42).

The SMP bit is the slew rate control enabled bit. This bit is in the SSPSTAT register and controls the slew rate of the I/O pins when in I<sup>2</sup>C mode (master or slave).

FIGURE 15-42: SAMPLE DEVICE CONFIGURATION FOR I<sup>2</sup>C BUS

**Note:** I<sup>2</sup>C devices with input levels related to VDD must have one common supply line to which the pull-up resistor is also connected.

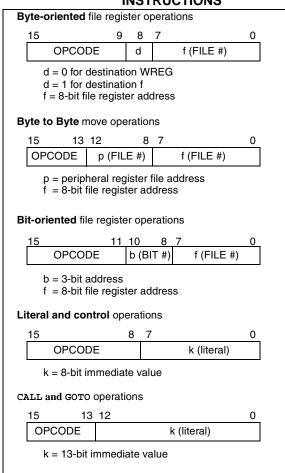

Table 18-2 lists the instructions recognized by the MPASM assembler.

**Note 1:** Any unused opcode is Reserved. Use of any reserved opcode may cause unexpected operation.

All instruction examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

To represent a binary number:

0000 0100b

where b signifies a binary string.

### FIGURE 18-1: GENERAL FORMAT FOR INSTRUCTIONS

### 18.1 Special Function Registers as Source/Destination

The PIC17C7XX's orthogonal instruction set allows read and write of all file registers, including special function registers. There are some special situations the user should be aware of:

#### 18.1.1 ALUSTA AS DESTINATION

If an instruction writes to ALUSTA, the Z, C, DC and OV bits may be set or cleared as a result of the instruction and overwrite the original data bits written. For example, executing CLRF ALUSTA will clear register ALUSTA and then set the Z bit leaving 0000 0100b in the register.

#### 18.1.2 PCL AS SOURCE OR DESTINATION

Read, write or read-modify-write on PCL may have the following results:

Read PC:  $PCH \rightarrow PCLATH$ ;  $PCL \rightarrow dest$

Write PCL: PCLATH  $\rightarrow$  PCH;

8-bit destination value → PCL

Read-Modify-Write: PCL→ ALU operand

PCLATH → PCH; 8-bit result → PCL

Where PCH = program counter high byte (not an addressable register), PCLATH = Program counter high holding latch, dest = destination, WREG or f.

#### 18.1.3 BIT MANIPULATION

All bit manipulation instructions are done by first reading the entire register, operating on the selected bit and writing the result back (read-modify-write (R-M-W)). The user should keep this in mind when operating on some special function registers, such as ports.

Note: Status bits that are manipulated by the device (including the interrupt flag bits) are set or cleared in the Q1 cycle. So, there is no issue on doing R-M-W instructions on registers which contain these bits

NOTES:

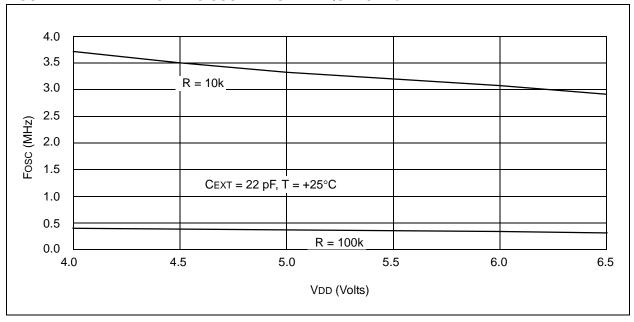

#### PIC17C7XX ELECTRICAL CHARACTERISTICS

#### **Absolute Maximum Ratings †**

| Ambient temperature under bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55°C to +125°C                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Storage temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 65°C to +150°C                      |

| Voltage on VDD with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0 V to +7.5 V                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0.3 V to +14 V                      |

| Voltage on RA2 and RA3 with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.3 V to +8.5 V                     |

| Voltage on all other pins with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.3 V to VDD + 0.3 V                |

| Total power dissipation (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.0 W                               |

| Maximum current out of Vss pin(s) - total (@ 70°C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 500 mA                              |

| Maximum current into VDD pin(s) - total (@ 70°C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 500 mA                              |

| Input clamp current, Iik (VI < 0 or VI > VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ±20 mA                              |

| Output clamp current, IOK (Vo < 0 or Vo > VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ±20 mA                              |

| Maximum output current sunk by any I/O pin (except RA2 and RA3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35 mA                               |