Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 16MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 50                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 902 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 12x10b                                                                   |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-TQFP                                                                      |

| Supplier Device Package    | 64-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c756at-16e-pt |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

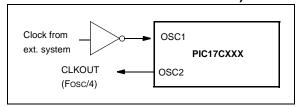

## 4.1.4 EXTERNAL CLOCK OSCILLATOR

In the EC oscillator mode, the OSC1 input can be driven by CMOS drivers. In this mode, the OSC1/ CLKIN pin is hi-impedance and the OSC2/CLKOUT pin is the CLKOUT output (4 Tosc).

### 4.1.5 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

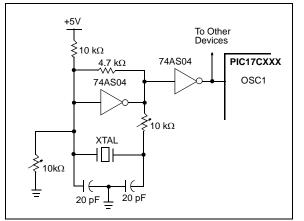

Either a prepackaged oscillator can be used, or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with series resonance, or one with parallel resonance.

Figure 4-5 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometer biases the 74AS04 in the linear region. This could be used for external oscillator designs.

### FIGURE 4-5:

#### EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

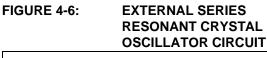

Figure 4-6 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330  $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

# 5.1 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Reset (BOR)

## 5.1.1 POWER-ON RESET (POR)

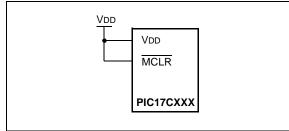

The Power-on Reset circuit holds the device in RESET until VDD is above the trip point (in the range of 1.4V -2.3V). The devices produce an internal RESET for both rising and <u>falling</u> VDD. To take advantage of the POR, just tie the MCLR/VPP pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A minimum rise time for VDD is required. See Electrical Specifications for details.

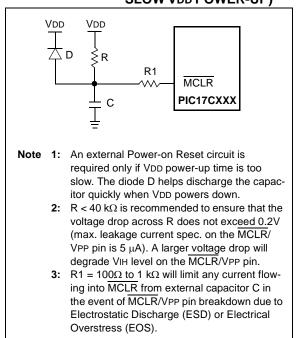

Figure 5-2 and Figure 5-3 show two possible POR circuits.

## FIGURE 5-2: USING ON-CHIP POR

### FIGURE 5-3: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

## 5.1.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 96 ms time-out (nominal) on power-up. This occurs from the rising edge of the internal POR signal if VDD and MCLR are tied, or after the first rising edge of MCLR (detected high). The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. In most cases, the PWRT delay allows VDD to rise to an acceptable level.

The power-up time delay will vary from chip to chip and with VDD and temperature. See DC parameters for details.

## 5.1.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (1024Tosc) delay whenever the PWRT is invoked, or a wake-up from SLEEP event occurs in XT or LF mode. The PWRT and OST operate in parallel.

The OST counts the oscillator pulses on the OSC1/ CLKIN pin. The counter only starts incrementing after the amplitude of the signal reaches the oscillator input thresholds. This delay allows the crystal oscillator or resonator to stabilize before the device exits RESET. The length of the time-out is a function of the crystal/ resonator frequency.

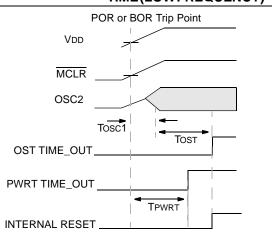

Figure 5-4 shows the operation of the OST circuit. In this figure, the oscillator is of such a low frequency that although enabled simultaneously, the OST does not time-out until after the Power-up Timer time-out.

## FIGURE 5-4: OSCILLATOR START-UP TIME(LOWFREQUENCY)

This figure shows in greater detail the timings involved with the oscillator start-up timer. In this example, the low frequency crystal start-up time is larger than power-up time (TPWRT).

Tosc1 = time for the crystal oscillator to react to an oscillation level detectable by the Oscillator Start-up Timer (OST).

TOST = 1024TOSC.

# REGISTER 6-3: PIE2 REGISTER (ADDRESS: 11h, BANK 4)

|         | R/W-0                                                                                                           | R/W-0                                       |               |                                                  |          |                 |             |       |  |

|---------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------|--------------------------------------------------|----------|-----------------|-------------|-------|--|

|         |                                                                                                                 |                                             | R/W-0         | U-0                                              | R/W-0    | R/W-0           | R/W-0       | R/W-0 |  |

|         | SSPIE                                                                                                           | BCLIE                                       | ADIE          | —                                                | CA4IE    | CA3IE           | TX2IE       | RC2IE |  |

| bi      | it 7                                                                                                            |                                             |               |                                                  |          |                 |             | bit 0 |  |

|         |                                                                                                                 |                                             |               |                                                  |          |                 |             |       |  |

| 1       | = Enable                                                                                                        | nchronous S<br>SSP interru<br>SSP interru   | pt            | errupt Enable                                    | e bit    |                 |             |       |  |

|         |                                                                                                                 |                                             | iterrupt Enab | le hit                                           |          |                 |             |       |  |

| 1       | = Enable                                                                                                        | bus collision<br>bus collision              | n interrupt   |                                                  |          |                 |             |       |  |

| 1       | = Enable                                                                                                        | Module Inter<br>A/D module<br>A/D module    |               | bit                                              |          |                 |             |       |  |

| bit 4 U | nimplem                                                                                                         | ented: Read                                 | l as '0'      |                                                  |          |                 |             |       |  |

| 1       | <b>CA4IE</b> : Capture4 Interrupt Enable bit<br>1 = Enable Capture4 interrupt<br>0 = Disable Capture4 interrupt |                                             |               |                                                  |          |                 |             |       |  |

| 1       | = Enable                                                                                                        | pture3 Interr<br>Capture3 in<br>Capture3 ir |               | vit                                              |          |                 |             |       |  |

| 1       | = Enable                                                                                                        | USART2 Tr                                   |               | Enable bit<br>r empty interi<br>er empty inter   | •        |                 |             |       |  |

| 1       | = Enable                                                                                                        | USART2 Re                                   |               | Enable bit<br>full interrupt<br>r full interrupt |          |                 |             |       |  |

| Le      | egend:                                                                                                          |                                             |               |                                                  |          |                 |             | ]     |  |

| R       | = Readat                                                                                                        | ole bit                                     | W = W         | ritable bit                                      | U = Unin | nplemented bit, | read as '0' |       |  |

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |  |

|--------------------------|------------------|----------------------|--------------------|--|

| - n = Value at POR Reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

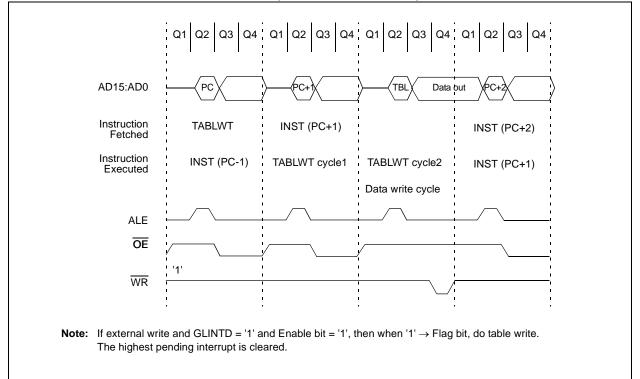

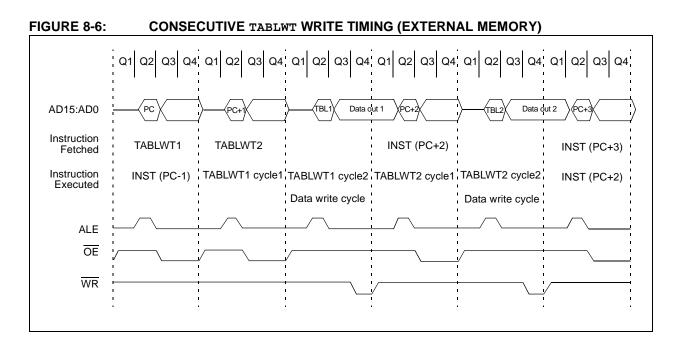

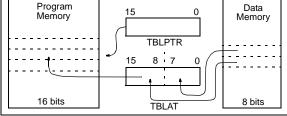

## 8.2 Table Writes to External Memory

Table writes to external memory are always two-cycle instructions. The second cycle writes the data to the external memory location. The sequence of events for an external memory write are the same for an internal write.

## 8.2.1 TABLE WRITE CODE

The "i" operand of the TABLWT instruction can specify that the value in the 16-bit TBLPTR register is automatically incremented (for the next write). In Example 8-1, the TBLPTR register is not automatically incremented.

# EXAMPLE 8-1: TABLE WRITE

| CLRWDT |                 | ; | Clear WDT      |

|--------|-----------------|---|----------------|

| MOVLW  | HIGH (TBL_ADDR) | ; | Load the Table |

| MOVWF  | TBLPTRH         | ; | address        |

| MOVLW  | LOW (TBL_ADDR)  | ; |                |

| MOVWF  | TBLPTRL         | ; |                |

| MOVLW  | HIGH (DATA)     | ; | Load HI byte   |

| TLWT   | 1, WREG         | ; | in TABLATH     |

| MOVLW  | LOW (DATA)      | ; | Load LO byte   |

| TABLWT | 0,0,WREG        | ; | in TABLATL     |

|        |                 | ; | and write to   |

|        |                 | ; | program memory |

|        |                 | ; | (Ext. SRAM)    |

|        |                 |   |                |

## FIGURE 8-5: TABLWT WRITE TIMING (EXTERNAL MEMORY)

# 9.0 HARDWARE MULTIPLIER

All PIC17C7XX devices have an 8 x 8 hardware multiplier included in the ALU of the device. By making the multiply a hardware operation, it completes in a single instruction cycle. This is an unsigned multiply that gives a 16-bit result. The result is stored into the 16-bit Product register (PRODH:PRODL). The multiplier does not affect any flags in the ALUSTA register.

Making the 8 x 8 multiplier execute in a single cycle gives the following advantages:

- Higher computational throughput

- Reduces code size requirements for multiply algorithms

The performance increase allows the device to be used in applications previously reserved for Digital Signal Processors.

Table 9-1 shows a performance comparison between PIC17CXXX devices using the single cycle hardware multiply and performing the same function without the hardware multiply.

Example 9-1 shows the sequence to do an  $8 \times 8$  unsigned multiply. Only one instruction is required when one argument of the multiply is already loaded in the WREG register.

Example 9-2 shows the sequence to do an 8 x 8 signed multiply. To account for the sign bits of the arguments, each argument's most significant bit (MSb) is tested and the appropriate subtractions are done.

## EXAMPLE 9-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

| MOVFP | ARG1, WREG | ;                |

|-------|------------|------------------|

| MULWF | ARG2       | ; ARG1 * ARG2 -> |

|       |            | ; PRODH:PRODL    |

|       |            |                  |

## EXAMPLE 9-2: 8 x 8 SIGNED MULTIPLY ROUTINE

| MOVFP | ARG1, WREG |                  |

|-------|------------|------------------|

| MULWF | ARG2       | ; ARG1 * ARG2 -> |

|       |            | ; PRODH:PRODL    |

| BTFSC | ARG2, SB   | ; Test Sign Bit  |

| SUBWF | PRODH, F   | ; PRODH = PRODH  |

|       |            | ; - ARG1         |

| MOVFP | ARG2, WREG |                  |

| BTFSC | ARG1, SB   | ; Test Sign Bit  |

| SUBWF | PRODH, F   | ; PRODH = PRODH  |

|       |            | ; - ARG2         |

|       |            |                  |

|                  |                           | Program           | Cycles | Time      |          |          |  |

|------------------|---------------------------|-------------------|--------|-----------|----------|----------|--|

| Routine          | Multiply Method           | Memory<br>(Words) | (Max)  | @ 33 MHz  | @ 16 MHz | @ 8 MHz  |  |

| 8 x 8 unsigned   | Without hardware multiply | 13                | 69     | 8.364 μs  | 17.25 μs | 34.50 μs |  |

|                  | Hardware multiply         | 1                 | 1      | 0.121 μs  | 0.25 μs  | 0.50 μs  |  |

| 8 x 8 signed     | Without hardware multiply | —                 | _      | —         | _        | _        |  |

|                  | Hardware multiply         | 6                 | 6      | 0.727 μs  | 1.50 μs  | 3.0 μs   |  |

| 16 x 16 unsigned | Without hardware multiply | 21                | 242    | 29.333 μs | 60.50 μs | 121.0 μs |  |

|                  | Hardware multiply         | 24                | 24     | 2.91 μs   | 6.0 μs   | 12.0 μs  |  |

| 16 x 16 signed   | Without hardware multiply | 52                | 254    | 30.788 μs | 63.50 μs | 127.0 μs |  |

|                  | Hardware multiply         | 36                | 36     | 4.36 μs   | 9.0 μs   | 18.0 μs  |  |

## TABLE 9-1: PERFORMANCE COMPARISON

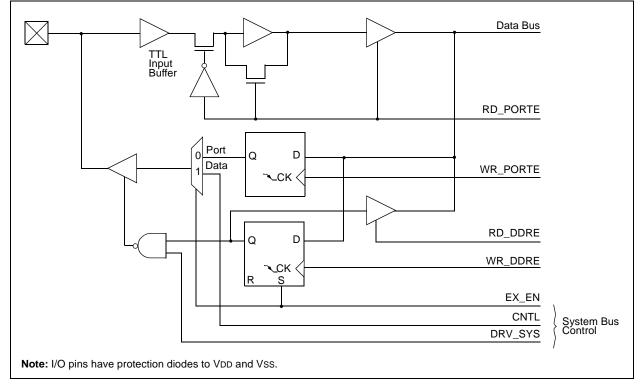

# 10.5 PORTE and DDRE Register

PORTE is a 4-bit bi-directional port. The corresponding data direction register is DDRE. A '1' in DDRE configures the corresponding port pin as an input. A '0' in the DDRE register configures the corresponding port pin as an output. Reading PORTE reads the status of the pins, whereas writing to PORTE will write to the port latch. PORTE is multiplexed with the system bus. When operating as the system bus, PORTE contains the control signals for the address/data bus (AD15:AD0). These control signals are Address Latch Enable (ALE), Output Enable (OE) and Write (WR). The control signals OE and WR are active low signals. The timing for the system bus is shown in the Electrical Specifications section.

**Note:** Three pins of this port are configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. The other pin is a general purpose I/O or Capture4 pin. In the two other microcontroller modes, RE2:RE0 are general purpose I/O pins. Example 10-5 shows an instruction sequence to initialize PORTE. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized. The following example uses the MOVLB instruction to load the BSR register for bank selection.

## EXAMPLE 10-5: INITIALIZING PORTE

| MOVLB | 1      |   | ; | Select Bank 1            |

|-------|--------|---|---|--------------------------|

| CLRF  | PORTE, | F | ; | Initialize PORTE data    |

|       |        |   | ; | latches before setting   |

|       |        |   | ; | the data direction       |

|       |        |   | ; | register                 |

| MOVLW | 0x03   |   | ; | Value used to initialize |

|       |        |   | ; | data direction           |

| MOVWF | DDRE   |   | ; | Set RE<1:0> as inputs    |

|       |        |   | ; | RE<3:2> as outputs       |

|       |        |   | ; | RE<7:4> are always       |

|       |        |   | ; | read as '0'              |

|       |        |   |   |                          |

## FIGURE 10-11: BLOCK DIAGRAM OF RE2:RE0 (IN I/O PORT MODE)

# PIC17C7XX

NOTES:

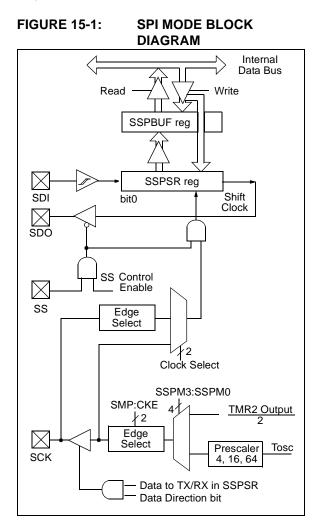

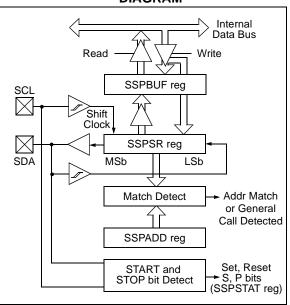

# 15.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit<sup>™</sup> (I<sup>2</sup>C)

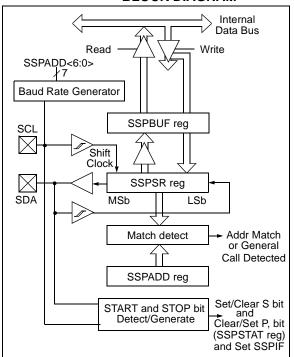

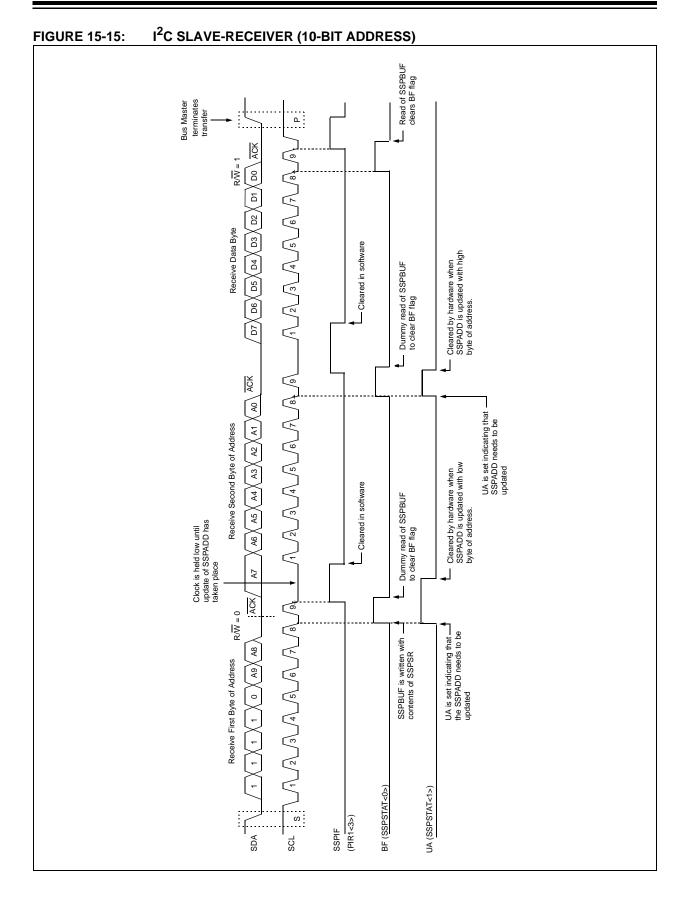

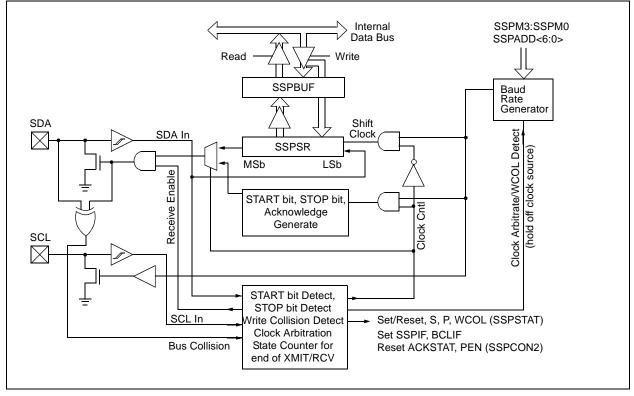

Figure 15-1 shows a block diagram for the SPI mode, while Figure 15-2 and Figure 15-3 show the block diagrams for the two different  $I^2C$  modes of operation.

# FIGURE 15-2:

## I<sup>2</sup>C SLAVE MODE BLOCK DIAGRAM

#### I<sup>2</sup>C MASTER MODE BLOCK DIAGRAM

# PIC17C7XX

## 15.2.5 MASTER MODE

Master mode of operation is supported by interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET, or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is idle, with both the S and P bits clear.

In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated Start

# FIGURE 15-17: SSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

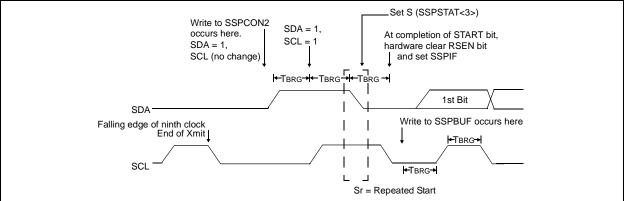

# 15.2.10 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C module is in the idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the baud rate generator is loaded with the contents of SSPADD<6:0> and begins counting. The SDA pin is released (brought high) for one baud rate generator count (TBRG). When the baud rate generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA is low) for one TBRG while SCL is high. Following this, the RSEN bit in the SSPCON2 register will be automatically cleared and the baud rate generator is not reloaded, leaving the SDA pin held low. As soon as a START condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the baud rate generator has timed out.

- Note 1: If the RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low to high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode), or eight bits of data (7-bit mode).

## 15.2.10.1 WCOL status flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

**Note:** Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

# FIGURE 15-22: REPEAT START CONDITION WAVEFORM

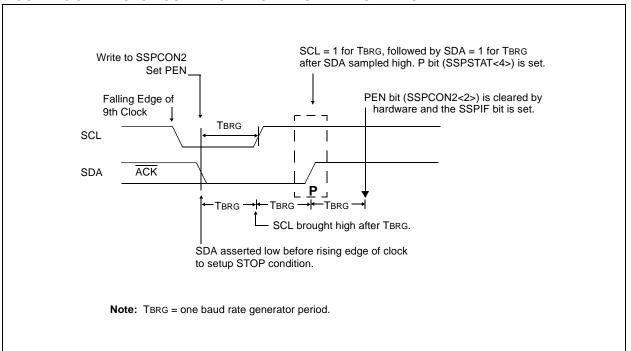

## 15.2.14 STOP CONDITION TIMING

A STOP bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit PEN (SSPCON2<2>). At the end of a receive/ transmit the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the baud rate generator is reloaded and counts down to '0'. When the baud rate generator times out, the SCL pin will be brought high and one TBRG (baud rate generator rollover count) later, the SDA pin will be de-asserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 15-31).

Whenever the firmware decides to take control of the bus, it will first determine if the bus is busy by checking the S and P bits in the SSPSTAT register. If the bus is busy, then the CPU can be interrupted (notified) when a STOP bit is detected (i.e., bus is free).

## 15.2.14.1 WCOL Status Flag

If the user writes the SSPBUF when a STOP sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 15-31: STOP CONDITION RECEIVE OR TRANSMIT MODE

## EXAMPLE 15-2: INTERFACING TO A 24LC01B SERIAL EEPROM (USING MPLAB C17)

```

// Writes the byte data to 24LC01B at the specified address

void ByteWrite(static unsigned char address, static unsigned char data)

{

StartI2C();

// Send start bit

// Wait for idle condition

IdleI2C();

WriteI2C(CONTROL);

// Send control byte

IdleI2C();

// Wait for idle condition

if (!SSPCON2bits.ACKSTAT)

// If 24LC01B ACKs

{

WriteI2C(address);

// Send control byte

IdleI2C();

// Wait for idle condition

// If 24LC01B ACKs

if (!SSPCON2bits.ACKSTAT)

WriteI2C(data);

// Send data

}

IdleI2C();

// Wait for idle condition

StopI2C();

// Send stop bit

// Wait for idle condition

IdleI2C();

return;

// Reads a byte of data from 24LC01B at the specified address

unsigned char ByteRead(static unsigned char address)

// Send start bit

StartI2C();

IdleI2C();

// Wait for idle condition

WriteI2C(CONTROL);

// Send control byte

IdleI2C();

// Wait for idle condition

if (!SSPCON2bits.ACKSTAT)

// If the 24LC01B ACKs

{

// Send address

WriteI2C(address);

// Wait for idle condition

IdleI2C();

if (!SSPCON2bits.ACKSTAT) // If the 24LC01B ACKs

{

RestartI2C();

// Send restart

IdleI2C();

// Wait for idle condition

// Send control byte with R/W set

WriteI2C(CONTROL+1);

IdleI2C();

// Wait for idle condition

// If the 24LC01B ACKs

if (!SSPCON2bits.ACKSTAT)

{

// Read a byte of data from 24LC01B

getcI2C();

// Wait for idle condition

IdleI2C();

NotAckI2C();

// Send a NACK to 24LC01B

IdleI2C();

// Wait for idle condition

// Send stop bit

StopI2C();

IdleI2C();

// Wait for idle condition

}

}

}

return(SSPBUF);

```

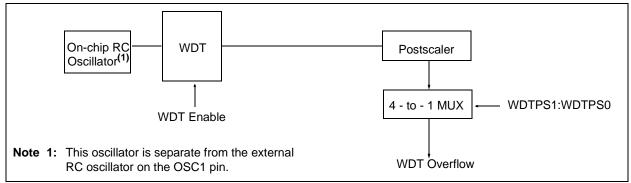

# 17.3 Watchdog Timer (WDT)

The Watchdog Timer's function is to recover from software malfunction, or to reset the device while in SLEEP mode. The WDT uses an internal free running on-chip RC oscillator for its clock source. This does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device RESET. The WDT can be permanently disabled by programming the configuration bits WDTPS1:WDTPS0 as '00' (Section 17.1).

Under normal operation, the WDT must be cleared on a regular interval. This time must be less than the minimum WDT overflow time. Not clearing the WDT in this time frame will cause the WDT to overflow and reset the device.

## 17.3.1 WDT PERIOD

The WDT has a nominal time-out period of 12 ms (with postscaler = 1). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, configuration bits should be used to enable the WDT with a greater prescale. Thus, typical time-out periods up to 3.0 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and its postscale setting and prevent it from timing out, thus generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the CPUSTA register will be cleared upon a WDT time-out.

## FIGURE 17-1: WATCHDOG TIMER BLOCK DIAGRAM

## TABLE 17-2: REGISTERS/BITS ASSOCIATED WITH THE WATCHDOG TIMER

|                                                                           | POR, BOR | MCLR, WDT |

|---------------------------------------------------------------------------|----------|-----------|

| Config See Figure 17-1 for location of WDTPSx bits in Configuration Word. | (Note 1) | (Note 1)  |

| 06h, Unbanked CPUSTA – – STKAV GLINTD TO PD POR BOR                       | 11 11qq  | 11 qquu   |

**Note** 1: This value will be as the device was programmed, or if unprogrammed, will read as all '1's.

The WDT and postscaler are cleared when:

- The device is in the RESET state

- A SLEEP instruction is executed

- A CLRWDT instruction is executed

- Wake-up from SLEEP by an interrupt

The WDT counter/postscaler will start counting on the first edge after the device exits the RESET state.

# 17.3.3 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., Max. WDT postscaler), it may take several seconds before a WDT time-out occurs.

The WDT and postscaler become the Power-up Timer whenever the PWRT is invoked.

## 17.3.4 WDT AS NORMAL TIMER

When the WDT is selected as a normal timer, the clock source is the device clock. Neither the WDT nor the postscaler are directly readable or writable. The overflow time is 65536 Tosc cycles. On overflow, the TO bit is cleared (device is not RESET). The CLRWDT instruction can be used to set the TO bit. This allows the WDT to be a simple overflow timer. The simple timer does not increment when in SLEEP.

## 17.4.2 MINIMIZING CURRENT CONSUMPTION

To minimize current consumption, all I/O pins should be either at VDD, or VSS, with no external circuitry drawing current from the I/O pin. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should be at VDD or VSS. The contributions from on-chip pull-ups on PORTB should also be considered and disabled, when possible.

# 17.5 Code Protection

The code in the program memory can be protected by selecting the microcontroller in Code Protected mode (PM2:PM0 = '000').

In this mode, instructions that are in the on-chip program memory space, can continue to read or write the program memory. An instruction that is executed outside of the internal program memory range will be inhibited from writing to, or reading from, program memory.

**Note:** Microchip does not recommend code protecting windowed devices.

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| LCA         | LL                             | Long Call                                                                                                                                                                                                                                                                                                                                                                                                     | l                                                                            |       |                       |  |  |  |  |

|-------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------|-----------------------|--|--|--|--|

| Synt        | ax:                            | [ label ]                                                                                                                                                                                                                                                                                                                                                                                                     | [ <i>label</i> ] LCALL k                                                     |       |                       |  |  |  |  |

| Ope         | rands:                         | $0 \le k \le 25$                                                                                                                                                                                                                                                                                                                                                                                              | $0 \le k \le 255$                                                            |       |                       |  |  |  |  |

| Ope         | ration:                        |                                                                                                                                                                                                                                                                                                                                                                                                               | PC + 1 $\rightarrow$ TOS;<br>k $\rightarrow$ PCL, (PCLATH) $\rightarrow$ PCH |       |                       |  |  |  |  |

| Statu       | us Affected:                   | None                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                              |       |                       |  |  |  |  |

| Enco        | oding:                         | 1011                                                                                                                                                                                                                                                                                                                                                                                                          | 0111                                                                         | kkk   | k kkkk                |  |  |  |  |

| Des         | cription:                      | LCALL allows an unconditional subr<br>tine call to anywhere within the 64K<br>program memory space.<br>First, the return address (PC + 1) is<br>pushed onto the stack. A 16-bit des<br>nation address is then loaded into th<br>program counter. The lower 8-bits of<br>the destination address are embedd<br>in the instruction. The upper 8-bits of<br>PC are loaded from PC high holding<br>latch, PCLATH. |                                                                              |       |                       |  |  |  |  |

| Wor         | ds:                            | 1                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                              |       |                       |  |  |  |  |

| Cycl        | es:                            | 2                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                              |       |                       |  |  |  |  |

| QC          | ycle Activity:                 |                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                              |       |                       |  |  |  |  |

|             | Q1                             | Q2                                                                                                                                                                                                                                                                                                                                                                                                            | Q3                                                                           | 3     | Q4                    |  |  |  |  |

|             | Decode                         | Read<br>literal 'k'                                                                                                                                                                                                                                                                                                                                                                                           | Proce<br>Dat                                                                 |       | Write<br>register PCL |  |  |  |  |

|             | No<br>operation                | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                               | No<br>opera                                                                  |       | No<br>operation       |  |  |  |  |

| <u>Exar</u> | <u>mple</u> :                  | MOVPF WI                                                                                                                                                                                                                                                                                                                                                                                                      | IGH(SUE<br>REG, PC<br>OW(SUBF                                                | LATH  |                       |  |  |  |  |

|             | Before Instru<br>SUBROUT<br>PC | TINE = 16<br>= ?                                                                                                                                                                                                                                                                                                                                                                                              | -bit Addr                                                                    | ess   |                       |  |  |  |  |

|             | After Instruct<br>PC           |                                                                                                                                                                                                                                                                                                                                                                                                               | ldress (                                                                     | SUBRC | OUTINE)               |  |  |  |  |

# PIC17C7XX

| TABLWT            | Table Writ    | е     |         |      |

|-------------------|---------------|-------|---------|------|

| Example1:         | TABLWT 1      | , 1,  | REG     |      |

| Before Instruc    | tion          |       |         |      |

| REG               |               | =     | 0x53    |      |

| TBLATH            |               | =     | 0xAA    |      |

| TBLATL            |               | =     | 0x55    | •    |

| TBLPTR            |               | =     | 0xA35   | -    |

| MEMORY(           | ,             | =     | 0xFFF   | -    |

| After Instruction | on (table wri | te co |         | n)   |

| REG               |               | =     | 0x53    |      |

| TBLATH            |               | =     | 0x53    |      |

| TBLATL            |               | =     | 0x55    | _    |

| TBLPTR            |               | =     | 0xA35   |      |

| MEMORY(           | TBLPTR - 1)   | =     | 0x535   | 5    |

| Example 2:        | TABLWT 0      | , 0,  | REG     |      |

| Before Instruc    | tion          |       |         |      |

| REG               |               | =     | 0x53    |      |

| TBLATH            |               | =     | 0xAA    |      |

| TBLATL            |               | =     | 0x55    |      |

| TBLPTR            |               | =     | 0xA35   | 6    |

| MEMORY(           | (TBLPTR)      | =     | 0xFFF   | F    |

| After Instruction | on (table wri | te co | mpletic | n)   |

| REG               |               | =     | 0x53    |      |

| TBLATH            |               | =     | 0xAA    |      |

| TBLATL            |               | =     | 0x53    |      |

| TBLPTR            |               | =     | 0xA35   | 6    |

| MEMORY(           | TBLPTR)       | =     | 0xAA5   | 3    |

|                   |               |       |         |      |

|                   | 1             |       |         |      |

| Program<br>Memory | 15            |       | 0       | Data |

| TLRD                   | Table Late                                                                                                                                                         | ch Read                            |                       |  |  |  |  |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|--|--|--|--|--|

| Syntax:                | ax: [label] TLRD t,f                                                                                                                                               |                                    |                       |  |  |  |  |  |

| Operands:              | 0 ≤ f ≤ 255<br>t ∈ [0,1]                                                                                                                                           | $0 \le f \le 255$<br>t $\in [0,1]$ |                       |  |  |  |  |  |

| Operation:             | If $t = 0$ ,<br>TBLATL $\rightarrow$ f;<br>If $t = 1$ ,                                                                                                            |                                    |                       |  |  |  |  |  |

| TBLATH $\rightarrow$ f |                                                                                                                                                                    |                                    |                       |  |  |  |  |  |

| Status Affected:       | Status Affected: None                                                                                                                                              |                                    |                       |  |  |  |  |  |

| Encoding:              | incoding: 1010 00tx ffff fff                                                                                                                                       |                                    |                       |  |  |  |  |  |

| Description:           | n: Read data from 16-bit table latch<br>(TBLAT) into file register 'f'. Table Latch<br>is unaffected.<br>If t = 1; high byte is read<br>If t = 0; low byte is read |                                    |                       |  |  |  |  |  |

|                        | This instruction is used in conjunction<br>with TABLRD to transfer data from pro-<br>gram memory to data memory.                                                   |                                    |                       |  |  |  |  |  |

| Words:                 | 1                                                                                                                                                                  |                                    |                       |  |  |  |  |  |

| Cycles:                | 1                                                                                                                                                                  |                                    |                       |  |  |  |  |  |

| Q Cycle Activity       |                                                                                                                                                                    |                                    |                       |  |  |  |  |  |

| Q1                     | Q2                                                                                                                                                                 | Q3                                 | Q4                    |  |  |  |  |  |

| Decode                 | Read<br>register<br>TBLATH or<br>TBLATL                                                                                                                            | Process<br>Data                    | Write<br>register 'f' |  |  |  |  |  |

| Example:               | TLRD t                                                                                                                                                             | , RAM                              |                       |  |  |  |  |  |

| Before Instr           |                                                                                                                                                                    |                                    |                       |  |  |  |  |  |

| t<br>RAM<br>TBLAT      | = 0<br>= ?<br>= 0x00AF                                                                                                                                             | = ?                                |                       |  |  |  |  |  |

| After Instruc          | ction                                                                                                                                                              |                                    |                       |  |  |  |  |  |

| RAM<br>TBLAT           | = 0xAF<br>= 0x00AF                                                                                                                                                 | (TBLATH =<br>(TBLATL =             |                       |  |  |  |  |  |

| Before Instr           |                                                                                                                                                                    |                                    |                       |  |  |  |  |  |

| t<br>RAM<br>TBLAT      | = 1<br>= ?<br>= 0x00AF                                                                                                                                             | (TBLATH =<br>(TBLATL =             |                       |  |  |  |  |  |

| After Instruc          | ction                                                                                                                                                              |                                    |                       |  |  |  |  |  |

| RAM<br>TBLAT           | = 0x00<br>= 0x00AF                                                                                                                                                 | (TBLATH =<br>(TBLATL =             | ,                     |  |  |  |  |  |

| Program<br>Memory      | 15                                                                                                                                                                 | 0                                  | Data<br>Memory        |  |  |  |  |  |

| TBLPTR<br>15 8 7 0     |                                                                                                                                                                    |                                    |                       |  |  |  |  |  |

| 16 bits TBLAT 8 bits   |                                                                                                                                                                    |                                    |                       |  |  |  |  |  |

© 1998-2013 Microchip Technology Inc.

| Standard Operating Conditions (unless otherwise stated) Operating temperature |       |                                       |                                                                                                                                                                                                                                                                                                                                                            |      |               |        | s otherwise stated)                                                                               |  |

|-------------------------------------------------------------------------------|-------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|--------|---------------------------------------------------------------------------------------------------|--|

| DC CHARACTERISTICS                                                            |       |                                       | $\begin{array}{rl} -40^{\circ}\text{C} &\leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ -40^{\circ}\text{C} &\leq \text{TA} \leq +85^{\circ}\text{C} \text{ for industrial} \\ 0^{\circ}\text{C} &\leq \text{TA} \leq +70^{\circ}\text{C} \text{ for commercial} \\ \end{array}$ Operating voltage VDD range as described in Section 20.1 |      |               |        |                                                                                                   |  |

| Param.<br>No.                                                                 | Sym   | Characteristic                        | Min                                                                                                                                                                                                                                                                                                                                                        | Тур† | Max           | Units  | Conditions                                                                                        |  |

|                                                                               |       | Input Leakage Current<br>(Notes 2, 3) |                                                                                                                                                                                                                                                                                                                                                            |      |               |        |                                                                                                   |  |

| D060                                                                          | lι∟   | I/O ports (except RA2, RA3)           | _                                                                                                                                                                                                                                                                                                                                                          | _    | ±1            | μΑ     | Vss ≤ VPIN ≤ VDD,<br>I/O Pin (in digital mode) at<br>hi-impedance PORTB<br>weak pull-ups disabled |  |

| D061                                                                          |       | MCLR, TEST                            | -                                                                                                                                                                                                                                                                                                                                                          | -    | ±2            | μΑ     | VPIN = Vss or VPIN = VDD                                                                          |  |

| D062                                                                          |       | RA2, RA3                              |                                                                                                                                                                                                                                                                                                                                                            |      | ±2            | μΑ     | $Vss \leq VRA2, \ VRA3 \leq 12V$                                                                  |  |

| D063                                                                          |       | OSC1 (EC, RC modes)                   | -                                                                                                                                                                                                                                                                                                                                                          | -    | ±1            | μΑ     | $V\text{ss} \leq V\text{PIN} \leq V\text{DD}$                                                     |  |

| D063B                                                                         |       | OSC1 (XT, LF modes)                   | -                                                                                                                                                                                                                                                                                                                                                          | -    | VPIN          | μΑ     | $R{\sf F} \geq 1~M\Omega$                                                                         |  |

| D064                                                                          |       | MCLR, TEST                            | _                                                                                                                                                                                                                                                                                                                                                          | _    | 25            | μΑ     | VMCLR = VPP = 12V<br>(when not programming)                                                       |  |

| D070                                                                          | IPURB | PORTB Weak Pull-up Current            | 85                                                                                                                                                                                                                                                                                                                                                         | 130  | 260           | μΑ     | $VPIN = VSS, \overline{RBPU} = 0$<br>4.5V $\leq VDD \leq 5.5V$                                    |  |

|                                                                               |       | Output Low Voltage                    |                                                                                                                                                                                                                                                                                                                                                            |      |               |        |                                                                                                   |  |

| D080                                                                          | Vol   | I/O ports                             |                                                                                                                                                                                                                                                                                                                                                            |      |               |        | IOL = VDD/1.250 mA                                                                                |  |

|                                                                               |       |                                       | -                                                                                                                                                                                                                                                                                                                                                          | -    | 0.1Vdd        | V      | $4.5V \leq V\text{DD} \leq 5.5V$                                                                  |  |

| D004                                                                          |       |                                       | -                                                                                                                                                                                                                                                                                                                                                          | -    | 0.1VDD        | V      | VDD = 3.0V                                                                                        |  |

| D081                                                                          |       | with TTL buffer                       | _                                                                                                                                                                                                                                                                                                                                                          | -    | 0.4           | V      | IOL = 6 mA, VDD = 4.5V<br>(Note 6)                                                                |  |

| D082                                                                          |       | RA2 and RA3                           | -                                                                                                                                                                                                                                                                                                                                                          | _    | 3.0           | V<br>V | IOL = 60.0  mA, VDD = 5.5 V                                                                       |  |

| D083                                                                          |       | OSC2/CLKOUT                           | _                                                                                                                                                                                                                                                                                                                                                          | _    | 0.6<br>0.4    | v<br>V | IOL = 60.0 mA, VDD = 4.5V<br>IOL = 1 mA, VDD = 4.5V                                               |  |

| D083<br>D084                                                                  |       | (RC and EC osc modes)                 | _                                                                                                                                                                                                                                                                                                                                                          | -    | 0.4<br>0.1Vdd | V<br>V | IOL = 1  IIIA, VDD = 4.5V<br>IOL = VDD/5  mA<br>(PIC17LC7XX only)                                 |  |

|                                                                               |       | Output High Voltage (Note 3)          |                                                                                                                                                                                                                                                                                                                                                            |      |               |        |                                                                                                   |  |

| D090                                                                          | Vон   | I/O ports (except RA2 and RA3)        | 0.9Vdd                                                                                                                                                                                                                                                                                                                                                     | _    | _             | V      | IOH = -VDD/2.5 mA<br>$4.5V \le VDD \le 5.5V$                                                      |  |

|                                                                               |       |                                       | 0.9Vdd                                                                                                                                                                                                                                                                                                                                                     | _    | _             | V      | VDD = 3.0V                                                                                        |  |

| D091                                                                          |       | with TTL buffer                       | 2.4                                                                                                                                                                                                                                                                                                                                                        | -    | _             | V      | IOH = -6.0 mA, VDD = 4.5V<br>(Note 6)                                                             |  |

| D093                                                                          |       | OSC2/CLKOUT                           | 2.4                                                                                                                                                                                                                                                                                                                                                        | _    | _             | V      | IOH = -5 mA, VDD = 4.5V                                                                           |  |

| D094                                                                          |       | (RC and EC osc modes)                 | 0.9Vdd                                                                                                                                                                                                                                                                                                                                                     | -    | _             | V      | IOH = -VDD/5 mA<br>(PIC17LC7XX only)                                                              |  |

Data in "Typ" column is at 5V, 25°C unless otherwise stated.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC17CXXX devices be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

4: These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17C7XX Programming Specifications (Literature number DS TBD).

5: The MCLR/VPP pin may be kept in this range at times other than programming, but is not recommended.

6: For TTL buffers, the better of the two specifications may be used.

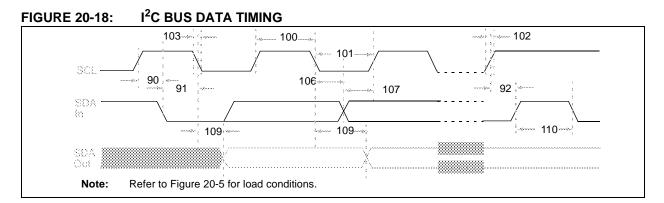

# TABLE 20-13: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Param<br>No. | Sym                     | Characteristic            |                           | Min              | Max  | Units                    | Conditions                   |

|--------------|-------------------------|---------------------------|---------------------------|------------------|------|--------------------------|------------------------------|

| 100 Thigh    | Thigh                   | Clock high time           | 100 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms                       |                              |

|              |                         |                           | 400 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms                       |                              |

|              |                         |                           | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms                       |                              |

| 101 Tlow     | Clock low time          | 100 kHz mode              | 2(Tosc)(BRG + 1)          | —                | ms   |                          |                              |

|              |                         | 400 kHz mode              | 2(Tosc)(BRG + 1)          | —                | ms   |                          |                              |

|              |                         | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1)          | —                | ms   |                          |                              |

| 102          | 102 Tr                  | SDA and SCL rise time     | 100 kHz mode              | —                | 1000 | ns                       | Cb is specified to be from   |

|              |                         | 400 kHz mode              | 20 + 0.1Cb                | 300              | ns   | 10 to 400 pF             |                              |

|              |                         | 1 MHz mode <sup>(1)</sup> | _                         | 300              | ns   |                          |                              |

| 103          | 103 Tf                  | SDA and SCL fall time     | 100 kHz mode              | _                | 300  | ns                       | Cb is specified to be from   |

|              |                         |                           | 400 kHz mode              | 20 + 0.1Cb       | 300  | ns                       | 10 to 400 pF                 |

|              |                         | 1 MHz mode <sup>(1)</sup> | _                         | 10               | ns   |                          |                              |

| 90           | 90 Tsu:sta              | START condition setup     | 100 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms                       | Only relevant for Repeated   |

|              | time                    | 400 kHz mode              | 2(Tosc)(BRG + 1)          | —                | ms   | Start condition          |                              |

|              |                         | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1)          | —                | ms   |                          |                              |

| 91           | 91 Thd:sta              | START condition hold      | 100 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms                       | After this period, the first |

|              | time                    | 400 kHz mode              | 2(Tosc)(BRG + 1)          | —                | ms   | clock pulse is generated |                              |

|              |                         | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1)          | —                | ms   |                          |                              |

| 106 Thd:dat  | t Data input hold time  | 100 kHz mode              | 0                         | —                | ns   |                          |                              |

|              |                         | 400 kHz mode              | 0                         | 0.9              | ms   |                          |                              |

|              |                         | 1 MHz mode <sup>(1)</sup> | 0                         | —                | ns   |                          |                              |

| 107 Tsu:dat  | t Data input setup time | 100 kHz mode              | 250                       | —                | ns   | (Note 2)                 |                              |

|              |                         | 400 kHz mode              | 100                       | —                | ns   |                          |                              |

|              |                         | 1 MHz mode <sup>(1)</sup> | 100                       | —                | ns   |                          |                              |

| 92 Tsu:sto   | STOP condition          | 100 kHz mode              | 2(Tosc)(BRG + 1)          | —                | ms   |                          |                              |

|              |                         | setup time                | 400 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms                       |                              |

|              |                         |                           | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms                       |                              |

| 109          | Таа                     | Output valid from clock   | 100 kHz mode              |                  | 3500 | ns                       |                              |

|              |                         |                           | 400 kHz mode              |                  | 1000 | ns                       |                              |

|              |                         |                           | 1 MHz mode <sup>(1)</sup> | _                | 400  | ns                       |                              |

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C$  pins.

2: A fast mode (400 KHz) I<sup>2</sup>C bus device can be used in a standard mode I<sup>2</sup>C bus system, but the parameter # 107 ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line. Parameter #102 + #107 = 1000 + 250 = 1250 ns (for 100 kHz mode) before the SCL line is released.

**3:**  $C_b$  is specified to be from 10-400pF. The minimum specifications are characterized with  $C_b=10pF$ . The rise time spec (t<sub>r</sub>) is characterized with  $R_p=R_p$  min. The minimum fall time specification (t<sub>f</sub>) is characterized with  $C_b=10pF$ , and  $R_p=R_p$  max. These are only valid for fast mode operation (VDD=4.5-5.5V) and where the SPM bit (SSPSTAT<7>) =1.)

4: Max specifications for these parameters are valid for falling edge only. Specs are characterized with R<sub>p</sub>=R<sub>p</sub> min and C<sub>b</sub>=400pF for standard mode, 200pF for fast mode, and 10pF for 1MHz mode.