Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Decails                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 33MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 902 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 68-LCC (J-Lead)                                                            |

| Supplier Device Package    | 68-PLCC (24.23x24.23)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c756at-33-l |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 DEVICE VARIETIES

Each device has a variety of frequency ranges and packaging options. Depending on application and production requirements, the proper device option can be selected using the information in the PIC17C7XX Product Selection System section at the end of this data sheet. When placing orders, please use the "PIC17C7XX Product Identification System" at the back of this data sheet to specify the correct part number. When discussing the functionality of the device, memory technology and voltage range does not matter.

There are two memory type options. These are specified in the middle characters of the part number.

- 1. **C**, as in PIC17**C**756A. These devices have EPROM type memory.

- 2. **CR**, as in PIC17**CR**756A. These devices have ROM type memory.

All these devices operate over the standard voltage range. Devices are also offered which operate over an extended voltage range (and reduced frequency range). Table 2-1 shows all possible memory types and voltage range designators for a particular device. These designators are in **bold** typeface.

| Memory Type                                                              | Voltage Range      |             |  |  |  |  |  |  |

|--------------------------------------------------------------------------|--------------------|-------------|--|--|--|--|--|--|

| memory type                                                              | Standard           | Extended    |  |  |  |  |  |  |

| EPROM                                                                    | PIC17 <b>C</b> XXX | PIC17LCXXX  |  |  |  |  |  |  |

| ROM                                                                      | PIC17CRXXX         | PIC17LCRXXX |  |  |  |  |  |  |

| Note: Not all memory technologies are available for a particular device. |                    |             |  |  |  |  |  |  |

### 2.1 UV Erasable Devices

The UV erasable version, offered in CERQUAD package, is optimal for prototype development and pilot programs.

The UV erasable version can be erased and reprogrammed to any of the configuration modes. Third party programmers also are available; refer to the *Third Party Guide* for a list of sources.

### 2.2 One-Time-Programmable (OTP) Devices

The availability of OTP devices is especially useful for customers expecting frequent code changes and updates.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must be programmed.

### 2.3 Quick-Turnaround-Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

### 2.4 Serialized Quick-Turnaround Production (SQTP<sup>sm</sup>) Devices

Microchip offers a unique programming service, where a few user defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry code, password or ID number.

## 2.5 Read Only Memory (ROM) Devices

Microchip offers masked ROM versions of several of the highest volume parts, thus giving customers a low cost option for high volume, mature products.

ROM devices do not allow serialization information in the program memory space.

For information on submitting ROM code, please contact your regional sales office.

Note: Presently, NO ROM versions of the PIC17C7XX devices are available.

# PIC17C7XX

NOTES:

### 7.2.2.3 TMR0 Status/Control Register (T0STA)

This register contains various control bits. Bit7 (INTEDG) is used to control the edge upon which a signal on the RA0/INT pin will set the RA0/INT interrupt flag. The other bits configure Timer0, it's prescaler and clock source.

### REGISTER 7-3: T0STA REGISTER (ADDRESS: 05h, UNBANKED)

| R/W-0                                         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0   |  |  |  |

|-----------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| INTEDG                                        | T0SE  | T0CS  | T0PS3 | T0PS2 | T0PS1 | T0PS0 |       |  |  |  |

| bit 7                                         |       |       |       |       |       |       | bit 0 |  |  |  |

|                                               |       |       |       |       |       |       |       |  |  |  |

| INTEDG: RA0/INT Pin Interrupt Edge Select bit |       |       |       |       |       |       |       |  |  |  |

| bit 7<br>bit 6 | This bit selects<br>1 = Rising edge<br>0 = Falling edge<br><b>T0SE</b> : Timer0 E | <ul> <li>INTEDG: RA0/INT Pin Interrupt Edge Select bit</li> <li>This bit selects the edge upon which the interrupt is detected.</li> <li>1 = Rising edge of RA0/INT pin generates interrupt</li> <li>0 = Falling edge of RA0/INT pin generates interrupt</li> <li>TOSE: Timer0 External Clock Input Edge Select bit</li> <li>This bit selects the edge upon which TMR0 will increment.</li> </ul> |  |  |  |  |  |  |  |  |

|----------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|                | 1 = Rising edge                                                                   | <u>) (External Clock):</u><br>of RA1/T0CKI pin increments TMR0 and/or sets the T0CKIF bit<br>of RA1/T0CKI pin increments TMR0 and/or sets a T0CKIF bit                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

|                | <u>When T0CS = 1</u><br>Don't care                                                | I (Internal Clock):                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| bit 5          | This bit selects<br>1 = Internal inst                                             | <b>TOCS</b> : Timer0 Clock Source Select bit<br>This bit selects the clock source for Timer0.<br>1 = Internal instruction clock cycle (TcY)<br>0 = External clock input on the T0CKI pin                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| bit 4-1        |                                                                                   | Timer0 Prescale Selection bits<br>ct the prescale value for Timer0.                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

|                | T0PS3:T0PS0                                                                       | Prescale Value                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|                | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1xxx              | 1:1<br>1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

bit 0

Unimplemented: Read as '0'

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR Reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

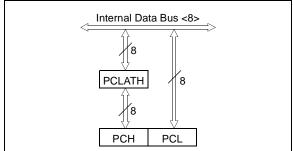

### 7.7 Program Counter Module

The Program Counter (PC) is a 16-bit register. PCL, the low byte of the PC, is mapped in the data memory. PCL is readable and writable just as is any other register. PCH is the high byte of the PC and is not directly addressable. Since PCH is not mapped in data or program memory, an 8-bit register PCLATH (PC high latch) is used as a holding latch for the high byte of the PC. PCLATH is mapped into data memory. The user can read or write PCH through PCLATH.

The 16-bit wide PC is incremented after each instruction fetch during Q1 unless:

- Modified by a GOTO, CALL, LCALL, RETURN, RETLW, or RETFIE instruction

- · Modified by an interrupt response

- Due to destination write to PCL by an instruction

"Skips" are equivalent to a forced NOP cycle at the skipped address.

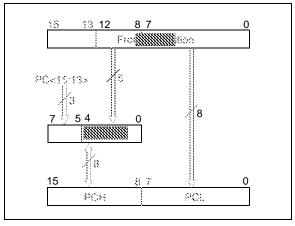

Figure 7-7 and Figure 7-8 show the operation of the program counter for various situations.

### FIGURE 7-7: PROGRAM COUNTER OPERATION

### FIGURE 7-8: PROGRAM COUNTER USING THE CALL AND GOTO INSTRUCTIONS

Using Figure 7-7, the operations of the PC and PCLATH for different instructions are as follows:

- a) <u>LCALL instructions</u>: An 8-bit destination address is provided in the instruction (opcode). PCLATH is unchanged. PCLATH → PCH Opcode<7:0> → PCL

- b) Read instructions on PCL: Any instruction that reads PCL. PCL  $\rightarrow$  data bus  $\rightarrow$  ALU or destination PCH  $\rightarrow$  PCLATH

- c) Write instructions on PCL: Any instruction that writes to PCL.

8-bit data → data bus → PCL PCLATH → PCH

- d) <u>Read-Modify-Write instructions on PCL:</u> Any instruction that does a read-write-modify operation on PCL, such as ADDWF PCL. Read: PCL → data bus → ALU Write: 8-bit result → data bus → PCL

- PCLATH  $\rightarrow$  PCH e) <u>RETURN instruction:</u> Stack<MRU>  $\rightarrow$  PC<15:0>

Using Figure 7-8, the operation of the PC and PCLATH for GOTO and CALL instructions is as follows:

CALL, GOTO instructions: A 13-bit destination address is provided in the instruction (opcode). Opcode<12:0>  $\rightarrow$  PC<12:0> PC<15:13>  $\rightarrow$  PCLATH<7:5> Opcode<12:8>  $\rightarrow$  PCLATH<4:0>

The read-modify-write only affects the PCL with the result. PCH is loaded with the value in the PCLATH. For example, ADDWF PCL will result in a jump within the current page. If PC = 03F0h, WREG = 30h and PCLATH = 03h before instruction, PC = 0320h after the instruction. To accomplish a true 16-bit computed jump, the user needs to compute the 16-bit destination address, write the high byte to PCLATH and then write the low value to PCL.

The following PC related operations do not change PCLATH:

- a) LCALL, RETLW, and RETFIE instructions.

- b) Interrupt vector is forced onto the PC.

- c) Read-modify-write instructions on PCL (e.g. BSF PCL).

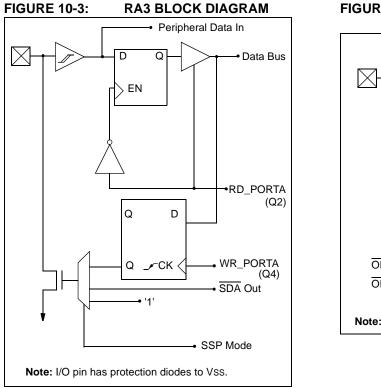

#### TABLE 10-1: **PORTA FUNCTIONS**

## FIGURE 10-4: **RA4 AND RA5 BLOCK** DIAGRAM Serial Port Input Signal Data Bus RD PORTA (Q2) Serial Port Output Signals OE = SPEN, SYNC, TXEN, CREN, SREN for RA4 $\overline{OE}$ = SPEN ( $\overline{SYNC}$ +SYNC, $\overline{CSRC}$ ) for RA5 Note: I/O pins have protection diodes to VDD and Vss.

| Name        | Bit0 | Buffer Type | Function                                                                                                                |

|-------------|------|-------------|-------------------------------------------------------------------------------------------------------------------------|

| RA0/INT     | bit0 | ST          | Input or external interrupt input.                                                                                      |

| RA1/T0CKI   | bit1 | ST          | Input or clock input to the TMR0 timer/counter and/or an external interrupt input.                                      |

| RA2/SS/SCL  | bit2 | ST          | Input/output or slave select input for the SPI, or clock input for the I <sup>2</sup> C bus. Output is open drain type. |

| RA3/SDI/SDA | bit3 | ST          | Input/output or data input for the SPI, or data for the I <sup>2</sup> C bus.<br>Output is open drain type.             |

| RA4/RX1/DT1 | bit4 | ST          | Input or USART1 Asynchronous Receive input, or USART1 Synchronous Data input/output.                                    |

| RA5/TX1/CK1 | bit5 | ST          | Input or USART1 Asynchronous Transmit output, or USART1 Synchronous Clock input/output.                                 |

| RBPU        | bit7 | —           | Control bit for PORTB weak pull-ups.                                                                                    |

Legend: ST = Schmitt Trigger input

#### **TABLE 10-2: REGISTERS/BITS ASSOCIATED WITH PORTA**

| Address       | Name                 | Bit 7  | Bit 6 | Bit 5           | Bit 4           | Bit 3           | Bit 2          | Bit 1     | Bit 0   | Value on<br>POR,<br>BOR | MCLR, WDT |

|---------------|----------------------|--------|-------|-----------------|-----------------|-----------------|----------------|-----------|---------|-------------------------|-----------|

| 10h, Bank 0   | PORTA <sup>(1)</sup> | RBPU   | _     | RA5/<br>TX1/CK1 | RA4/<br>RX1/DT1 | RA3/<br>SDI/SDA | RA2/<br>SS/SCL | RA1/T0CKI | RA0/INT | 0-xx 11xx               | 0-uu 11uu |

| 05h, Unbanked | TOSTA                | INTEDG | T0SE  | TOCS            | T0PS3           | T0PS2           | T0PS1          | T0PS0     |         | 0000 000-               | 0000 000- |

| 13h, Bank 0   | RCSTA1               | SPEN   | RX9   | SREN            | CREN            | _               | FERR           | OERR      | RX9D    | 0000 -00x               | 0000 -00u |

| 15h, Bank 0   | TXSTA1               | CSRC   | TX9   | TXEN            | SYNC            | _               | _              | TRMT      | TX9D    | 00001x                  | 00001u    |

Legend: x = unknown, u = unchanged, - = unimplemented, reads as '0'. Shaded cells are not used by PORTA. **Note 1:** On any device RESET, these pins are configured as inputs.

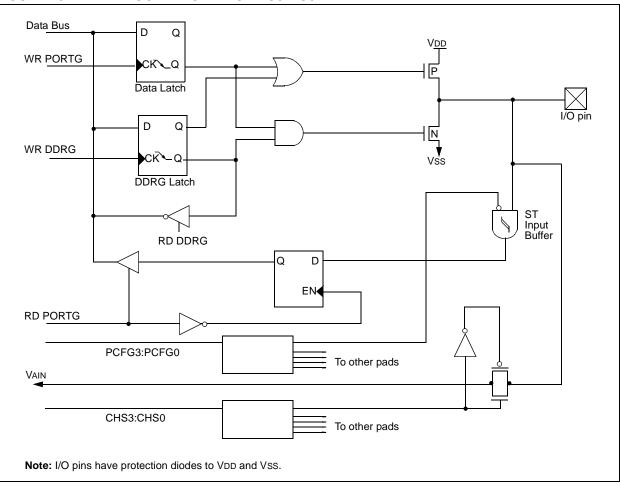

### 10.7 PORTG and DDRG Registers

PORTG is an 8-bit wide, bi-directional port. The corresponding data direction register is DDRG. A '1' in DDRG configures the corresponding port pin as an input. A '0' in the DDRG register configures the corresponding port pin as an output. Reading PORTG reads the status of the pins, whereas writing to PORTG will write to the port latch.

The lower four bits of PORTG are multiplexed with four channels of the 10-bit A/D converter.

The remaining bits of PORTG are multiplexed with peripheral output and inputs. RG4 is multiplexed with the CAP3 input, RG5 is multiplexed with the PWM3 output, RG6 and RG7 are multiplexed with the USART2 functions.

Upon RESET, RG3:RG0 is automatically configured as analog inputs and must be configured in software to be a digital I/O.

Example 10-7 shows the instruction sequence to initialize PORTG. The Bank Select Register (BSR) must be selected to Bank 5 for the port to be initialized. The following example uses the MOVLB instruction to load the BSR register for bank selection.

### EXAMPLE 10-7: INITIALIZING PORTG

| MOVLB | 5            | ; Select Bank 5         |

|-------|--------------|-------------------------|

| MOVLW | 0x0E         | ; Configure PORTG as    |

| MOVPF | WREG, ADCON1 | ; digital               |

| CLRF  | PORTG, F     | ; Initialize PORTG data |

|       |              | ; latches before        |

|       |              | ; the data direction    |

|       |              | ; register              |

| MOVLW | 0x03         | ; Value used to init    |

|       |              | ; data direction        |

| MOVWF | DDRG         | ; Set RG<1:0> as inputs |

|       |              | ; RG<7:2> as outputs    |

|       |              |                         |

### FIGURE 10-14: BLOCK DIAGRAM OF RG3:RG0

# PIC17C7XX

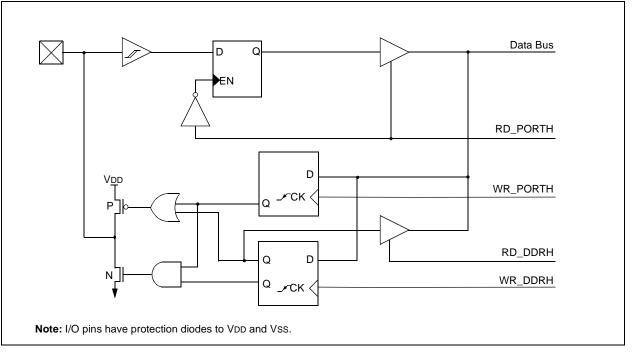

### FIGURE 10-18: RH3:RH0 BLOCK DIAGRAM

### TABLE 10-15: PORTH FUNCTIONS

| Name     | Bit  | Buffer Type | Function                         |

|----------|------|-------------|----------------------------------|

| RH0      | bit0 | ST          | Input/output.                    |

| RH1      | bit1 | ST          | Input/output.                    |

| RH2      | bit2 | ST          | Input/output.                    |

| RH3      | bit3 | ST          | Input/output.                    |

| RH4/AN12 | bit4 | ST          | Input/output or analog input 12. |

| RH5/AN13 | bit5 | ST          | Input/output or analog input 13. |

| RH6/AN14 | bit6 | ST          | Input/output or analog input 14. |

| RH7/AN15 | bit7 | ST          | Input/output or analog input 15. |

Legend: ST = Schmitt Trigger input

### TABLE 10-16: REGISTERS/BITS ASSOCIATED WITH PORTH

| Address     | Name   | Bit 7                             | Bit 6        | Bit 5        | Bit 4        | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | MCLR, WDT |

|-------------|--------|-----------------------------------|--------------|--------------|--------------|-------|-------|-------|-------|-------------------------|-----------|

| 10h, Bank 8 | DDRH   | Data Direction Register for PORTH |              |              |              |       |       |       |       | 1111 1111               | 1111 1111 |

| 11h, Bank 8 | PORTH  | RH7/<br>AN15                      | RH6/<br>AN14 | RH5/<br>AN13 | RH4/<br>AN12 | RH3   | RH2   | RH1   | RH0   | 0000 xxxx               | 0000 uuuu |

| 15h, Bank 5 | ADCON1 | ADCS1                             | ADCS0        | ADFM         | _            | PCFG3 | PCFG2 | PCFG1 | PCFG0 | 000- 0000               | 000- 0000 |

Legend: x = unknown, u = unchanged

# PIC17C7XX

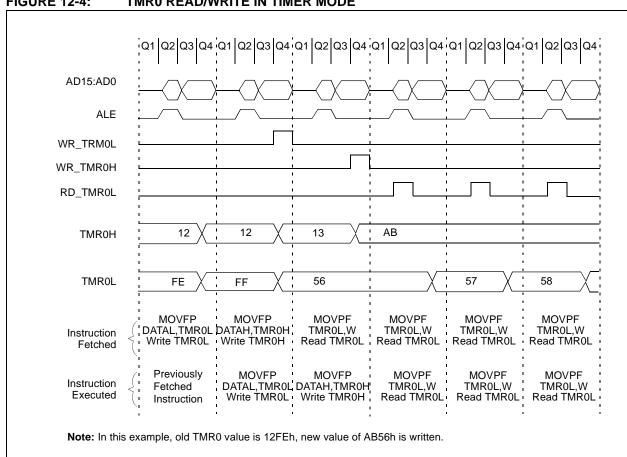

#### FIGURE 12-4: **TMR0 READ/WRITE IN TIMER MODE**

#### **TABLE 12-1: REGISTERS/BITS ASSOCIATED WITH TIMER0**

| Address       | Name   | Bit 7    | Bit 6                   | Bit 5 | Bit 4  | Bit 3 | Bit 2  | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | MCLR, WDT |

|---------------|--------|----------|-------------------------|-------|--------|-------|--------|-------|-------|-------------------------|-----------|

| 05h, Unbanked | TOSTA  | INTEDG   | TOSE                    | T0CS  | T0PS3  | T0PS2 | T0PS1  | T0PS0 | —     | 0000 000-               | 0000 000- |

| 06h, Unbanked | CPUSTA | -        | -                       | STKAV | GLINTD | TO    | PD     | POR   | BOR   | 11 11qq                 | 11 qquu   |

| 07h, Unbanked | INTSTA | PEIF     | TOCKIF                  | T0IF  | INTF   | PEIE  | TOCKIE | TOIE  | INTE  | 0000 0000               | 0000 0000 |

| 0Bh, Unbanked | TMR0L  | TMR0 Reg | TMR0 Register; Low Byte |       |        |       |        |       |       |                         | uuuu uuuu |

| 0Ch, Unbanked | TMR0H  | TMR0 Reg | MR0 Register; High Byte |       |        |       |        |       |       |                         | uuuu uuuu |

Legend: x = unknown, u = unchanged, - = unimplemented, read as a '0', q = value depends on condition. Shaded cells are not used by Timer0.

|         | U-0                                                               | R-0                                                                              | R-0                                                          | R/W-0                                                          | R/W-0                                         | R/W-0                                                          | R/W-0                        | R/W-0                    |

|---------|-------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------|------------------------------|--------------------------|

|         |                                                                   | CA40VF                                                                           | CA3OVF                                                       | CA4ED1                                                         | CA4ED0                                        | CA3ED1                                                         | CA3ED0                       | PWM3ON                   |

|         | bit 7                                                             |                                                                                  |                                                              |                                                                |                                               |                                                                |                              | bit 0                    |

| bit 7   | Unimplen                                                          | nented: Rea                                                                      | d as '0'                                                     |                                                                |                                               |                                                                |                              |                          |

| bit 6   | This bit in<br>(CA4H:CA<br>unread ca<br>the captur<br>1 = Overfl  | ndicates that<br>AL) before to<br>pture value (<br>e register wi<br>ow occurred  | the next cap<br>(last capture)<br>th the TMR3<br>on Capture  | e value had<br>ture event of<br>before overf<br>value until th | ccurred. The<br>low). Subsec<br>ne capture re | ead from the<br>capture reg<br>quent capture<br>gister has be  | ister retains<br>events will | the oldest not update    |

| bit 5   | This bit in<br>(CA3H:CA<br>unread ca<br>the captur<br>1 = Overfle | ndicates that<br>(3L) before to<br>pture value (<br>e register wi<br>ow occurred | the next cap<br>(last capture)<br>th the TMR3<br>on Capture3 | e value had<br>ture event of<br>before overf<br>value until th | ccurred. The<br>low). Subsec<br>ne capture re | ead from the<br>capture reg<br>quent capture<br>egister has be | ister retains<br>events will | the oldest<br>not update |

| bit 4-3 | <b>CA4ED1:0</b><br>00 = Capt<br>01 = Capt<br>10 = Capt            | <b>CA4ED0</b> : Ca<br>ure on every<br>ure on every<br>ure on every               | apture4 Mode<br>falling edge                                 | e Select bits<br>dge                                           |                                               |                                                                |                              |                          |

| bit 2-1 | 00 = Capt<br>01 = Capt<br>10 = Capt                               | ure on every<br>ure on every<br>ure on every                                     | falling edge                                                 | dge                                                            |                                               |                                                                |                              |                          |

| bit 0   | 1 = PWM3                                                          |                                                                                  | (the RG5/PV                                                  |                                                                |                                               | of the DDRC<br>the DDRG<5                                      |                              | a direction)             |

|         | Legend:                                                           |                                                                                  |                                                              |                                                                |                                               |                                                                |                              |                          |

'1' = Bit is set

'0' = Bit is cleared

## REGISTER 13-3: TCON3 REGISTER (ADDRESS: 16h, BANK 7)

- n = Value at POR Reset

x = Bit is unknown

| Address       | Name   | Bit 7      | Bit 6         | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | MCLR, WDT |

|---------------|--------|------------|---------------|--------|--------|---------|--------|--------|--------|-------------------------|-----------|

| 16h, Bank 3   | TCON1  | CA2ED1     | CA2ED0        | CA1ED1 | CA1ED0 | T16     | TMR3CS | TMR2CS | TMR1CS | 0000 0000               | 0000 0000 |

| 17h, Bank 3   | TCON2  | CA2OVF     | CA10VF        | PWM2ON | PWM10N | CA1/PR3 | TMR3ON | TMR2ON | TMR10N | 0000 0000               | 0000 0000 |

| 16h, Bank 7   | TCON3  | —          | CA4OVF        | CA3OVF | CA4ED1 | CA4ED0  | CA3ED1 | CA3ED0 | PWM3ON | -000 0000               | -000 0000 |

| 10h, Bank 2   | TMR1   | Timer1's F | Register      | •      |        |         |        |        |        | XXXX XXXX               | uuuu uuuu |

| 11h, Bank 2   | TMR2   | Timer2's F | Register      |        |        |         |        |        |        | xxxx xxxx               | uuuu uuuu |

| 16h, Bank 1   | PIR1   | RBIF       | TMR3IF        | TMR2IF | TMR1IF | CA2IF   | CA1IF  | TX1IF  | RC1IF  | x000 0010               | u000 0010 |

| 17h, Bank 1   | PIE1   | RBIE       | TMR3IE        | TMR2IE | TMR1IE | CA2IE   | CA1IE  | TX1IE  | RC1IE  | 0000 0000               | 0000 0000 |

| 07h, Unbanked | INTSTA | PEIF       | T0CKIF        | T0IF   | INTF   | PEIE    | T0CKIE | TOIE   | INTE   | 0000 0000               | 0000 0000 |

| 06h, Unbanked | CPUSTA | —          | —             | STKAV  | GLINTD | TO      | PD     | POR    | BOR    | 11 11qq                 | 11 qquu   |

| 14h, Bank 2   | PR1    | Timer1 Pe  | eriod Registe | er     |        |         |        |        |        | XXXX XXXX               | uuuu uuuu |

| 15h, Bank 2   | PR2    | Timer2 Pe  | eriod Registe | er     |        |         |        |        |        | XXXX XXXX               | uuuu uuuu |

| 10h, Bank 3   | PW1DCL | DC1        | DC0           | —      | —      | —       | —      | —      | —      | xx                      | uu        |

| 11h, Bank 3   | PW2DCL | DC1        | DC0           | TM2PW2 | _      | _       |        | —      | —      | xx0                     | uu0       |

| 10h, Bank 7   | PW3DCL | DC1        | DC0           | TM2PW3 | _      | _       |        | —      | —      | xx0                     | uu0       |

| 12h, Bank 3   | PW1DCH | DC9        | DC8           | DC7    | DC6    | DC5     | DC4    | DC3    | DC2    | XXXX XXXX               | uuuu uuuu |

| 13h, Bank 3   | PW2DCH | DC9        | DC8           | DC7    | DC6    | DC5     | DC4    | DC3    | DC2    | XXXX XXXX               | uuuu uuuu |

| 11h, Bank 7   | PW3DCH | DC9        | DC8           | DC7    | DC6    | DC5     | DC4    | DC3    | DC2    | xxxx xxxx               | uuuu uuuu |

### TABLE 13-3: SUMMARY OF TIMER1, TIMER2 AND TIMER3 REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented, read as a '0', q = value depends on condition. Shaded cells are not used by Timer1 or Timer2.

### 13.1.3 USING PULSE WIDTH MODULATION (PWM) OUTPUTS WITH TIMER1 AND TIMER2

Three high speed pulse width modulation (PWM) outputs are provided. The PWM1 output uses Timer1 as its time base, while PWM2 and PWM3 may independently be software configured to use either Timer1 or Timer2 as the time base. The PWM outputs are on the RB2/PWM1, RB3/PWM2 and RG5/PWM3 pins.

Each PWM output has a maximum resolution of 10bits. At 10-bit resolution, the PWM output frequency is 32.2 kHz (@ 32 MHz clock) and at 8-bit resolution the PWM output frequency is 128.9 kHz. The duty cycle of the output can vary from 0% to 100%.

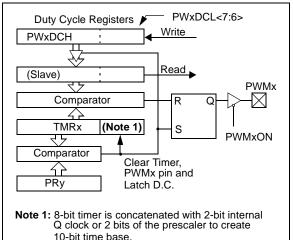

Figure 13-3 shows a simplified block diagram of a PWM module.

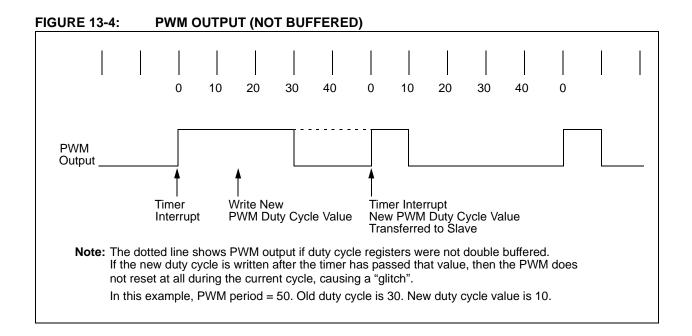

The duty cycle registers are double buffered for glitch free operation. Figure 13-4 shows how a glitch could occur if the duty cycle registers were not double buffered.

The user needs to set the PWM1ON bit (TCON2<4>) to enable the PWM1 output. When the PWM1ON bit is set, the RB2/PWM1 pin is configured as PWM1 output and forced as an output, irrespective of the data direction bit (DDRB<2>). When the PWM1ON bit is clear, the pin behaves as a port pin and its direction is controlled by its data direction bit (DDRB<2>). Similarly, the PWM2ON (TCON2<5>) bit controls the configuration of the RB3/PWM2 pin and the PWM3ON (TCON3<0>) bit controls the configuration of the RG5/PWM3 pin.

### FIGURE 13-3: SIMPLIFIED PWM BLOCK DIAGRAM

### 13.2.3 READING THE CAPTURE REGISTERS

The Capture overflow status flag bits are double buffered. The master bit is set if one captured word is already residing in the Capture register and another "event" has occurred on the CAPx pin. The new event will not transfer the TMR3 value to the capture register, protecting the previous unread capture value. When the user reads both the high and the low bytes (in any order) of the Capture register, the master overflow bit is transferred to the slave overflow bit (CAxOVF) and then the master bit is reset. The user can then read TCONx to determine the value of CAxOVF.

An example of an instruction sequence to read capture registers and capture overflow flag bits is shown in Example 13-1. Depending on the capture source, different registers will need to be read.

### EXAMPLE 13-1: SEQUENCE TO READ CAPTURE REGISTERS

; Select Bank 3

```

MOVLB 3

MOVPF CA2L, LO_BYTE

MOVPF CA2H, HI_BYTE

MOVPF TCON2, STAT_VAL

```

; Read Capture2 low byte, store in LO\_BYTE ; Read Capture2 high byte, store in HI\_BYTE

```

N2, STAT_VAL ; Read TCON2 into file STAT_VAL

```

| Address       | Name      | Bit 7     | Bit 6         | Bit 5         | Bit 4         | Bit 3        | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | MCLR, WDT |

|---------------|-----------|-----------|---------------|---------------|---------------|--------------|--------|--------|--------|-------------------------|-----------|

| 16h, Bank 3   | TCON1     | CA2ED1    | CA2ED0        | CA1ED1        | CA1ED0        | T16          | TMR3CS | TMR2CS | TMR1CS | 0000 0000               | 0000 0000 |

| 17h, Bank 3   | TCON2     | CA2OVF    | CA10VF        | PWM2ON        | PWM10N        | CA1/PR3      | TMR3ON | TMR2ON | TMR1ON | 0000 0000               | 0000 0000 |

| 16h, Bank 7   | TCON3     | —         | CA40VF        | CA3OVF        | CA4ED1        | CA4ED0       | CA3ED1 | CA3ED0 | PWM3ON | -000 0000               | -000 0000 |

| 12h, Bank 2   | TMR3L     | Holding R | egister for t | he Low Byte   | of the 16-bit | TMR3 Reg     | ister  |        |        | xxxx xxxx               | uuuu uuuu |

| 13h, Bank 2   | TMR3H     | Holding R | egister for t | he High Byte  | of the 16-bit | TMR3 Reg     | gister |        |        | XXXX XXXX               | uuuu uuuu |

| 16h, Bank 1   | PIR1      | RBIF      | TMR3IF        | TMR2IF        | TMR1IF        | CA2IF        | CA1IF  | TX1IF  | RC1IF  | x000 0010               | u000 0010 |

| 17h, Bank 1   | PIE1      | RBIE      | TMR3IE        | TMR2IE        | TMR1IE        | CA2IE        | CA1IE  | TX1IE  | RC1IE  | 0000 0000               | 0000 0000 |

| 10h, Bank 4   | PIR2      | SSPIF     | BCLIF         | ADIF          | _             | CA4IF        | CA3IF  | TX2IF  | RC2IF  | 000- 0010               | 000- 0010 |

| 11h, Bank 4   | PIE2      | SSPIE     | BCLIE         | ADIE          | _             | CA4IE        | CA3IE  | TX2IE  | RC2IE  | 000- 0000               | 000- 0000 |

| 07h, Unbanked | INTSTA    | PEIF      | T0CKIF        | T0IF          | INTF          | PEIE         | T0CKIE | T0IE   | INTE   | 0000 0000               | 0000 0000 |

| 06h, Unbanked | CPUSTA    | _         | _             | STKAV         | GLINTD        | TO           | PD     | POR    | BOR    | 11 11qq                 | 11 qquu   |

| 16h, Bank 2   | PR3L/CA1L | Timer3 Pe | riod Regist   | er, Low Byte/ | Capture1 Re   | gister, Low  | Byte   |        | •      | xxxx xxxx               | uuuu uuuu |

| 17h, Bank 2   | PR3H/CA1H | Timer3 Pe | riod Regist   | er, High Byte | /Capture1 Re  | egister, Hig | h Byte |        |        | xxxx xxxx               | uuuu uuuu |

| 14h, Bank 3   | CA2L      | Capture2  | Low Byte      |               |               |              |        |        |        | xxxx xxxx               | uuuu uuuu |

| 15h, Bank 3   | CA2H      | Capture2  | High Byte     |               |               |              |        |        |        | xxxx xxxx               | uuuu uuuu |

| 12h, Bank 7   | CA3L      | Capture3  | Low Byte      |               |               |              |        |        |        | xxxx xxxx               | uuuu uuuu |

| 13h, Bank 7   | CA3H      | Capture3  | High Byte     |               |               |              |        |        |        | xxxx xxxx               | uuuu uuuu |

| 14h, Bank 7   | CA4L      | Capture4  | Low Byte      |               |               |              |        |        |        | xxxx xxxx               | uuuu uuuu |

| 15h, Bank 7   | CA4H      | Capture4  | High Byte     |               |               |              |        |        |        | xxxx xxxx               | uuuu uuuu |

### TABLE 13-6: REGISTERS ASSOCIATED WITH CAPTURE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0', q = value depends on condition. Shaded cells are not used by Capture.

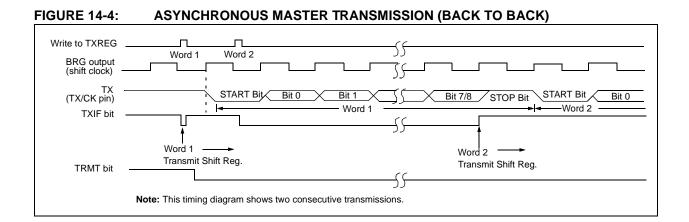

### TABLE 14-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address     | Name   | Bit 7       | Bit 6                                  | Bit 5       | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | MCLR, WDT |

|-------------|--------|-------------|----------------------------------------|-------------|----------|-------|-------|-------|-------|-------------------------|-----------|

| 16h, Bank 1 | PIR1   | RBIF        | TMR3IF                                 | TMR2IF      | TMR1IF   | CA2IF | CA1IF | TX1IF | RC1IF | x000 0010               | u000 0010 |

| 17h, Bank 1 | PIE1   | RBIE        | TMR3IE                                 | TMR2IE      | TMR1IE   | CA2IE | CA1IE | TX1IE | RC1IE | 0000 0000               | 0000 0000 |

| 13h, Bank 0 | RCSTA1 | SPEN        | RX9                                    | SREN        | CREN     |       | FERR  | OERR  | RX9D  | x00-000x                | 0000 -00u |

| 16h, Bank 0 | TXREG1 | Serial Port | Transmit I                             | Register (L | JSART1)  |       |       |       |       | xxxx xxxx               | uuuu uuuu |

| 15h, Bank 0 | TXSTA1 | CSRC        | TX9                                    | TXEN        | SYNC     | _     | —     | TRMT  | TX9D  | 00001x                  | 00001u    |

| 17h, Bank 0 | SPBRG1 | Baud Rate   | Generato                               | r Register  | (USART1) |       |       |       |       | 0000 0000               | 0000 0000 |

| 10h, Bank 4 | PIR2   | SSPIF       | BCLIF                                  | ADIF        | _        | CA4IF | CA3IF | TX2IF | RC2IF | 000- 0010               | 000- 0010 |

| 11h, Bank 4 | PIE2   | SSPIE       | BCLIE                                  | ADIE        |          | CA4IE | CA3IE | TX2IE | RC2IE | 000- 0000               | 000- 0000 |

| 13h, Bank 4 | RCSTA2 | SPEN        | RX9                                    | SREN        | CREN     |       | FERR  | OERR  | RX9D  | x00- 0000               | 0000 -00u |

| 16h, Bank 4 | TXREG2 | Serial Port | Serial Port Transmit Register (USART2) |             |          |       |       |       |       | xxxx xxxx               | uuuu uuuu |

| 15h, Bank 4 | TXSTA2 | CSRC        | TX9                                    | TXEN        | SYNC     | _     | —     | TRMT  | TX9D  | 00001x                  | 00001u    |

| 17h, Bank 4 | SPBRG2 | Baud Rate   | Generato                               | r Register  | (USART2) |       |       |       | -     | 0000 0000               | 0000 0000 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as a '0'. Shaded cells are not used for asynchronous transmission.

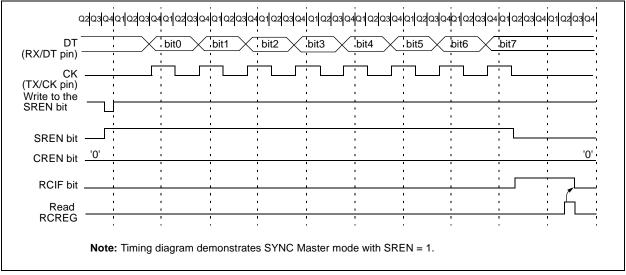

### 14.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either the SREN (RCSTA<5>) bit or the CREN (RCSTA<4>) bit. Data is sampled on the RX/ DT pin on the falling edge of the clock. If SREN is set, then only a single word is received. If CREN is set, the reception is continuous until CREN is reset. If both bits are set, then CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to RCREG (if it is empty). If the transfer is complete, the interrupt bit RCIF is set. The actual interrupt can be enabled/disabled by setting/clearing the RCIE bit. RCIF is a read only bit which is reset by the hardware. In this case, it is reset when RCREG has been read and is empty. RCREG is a double buffered register; i.e., it is a two deep FIFO. It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR. On the clocking of the last bit of the third byte, if RCREG is still full, then the overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. RCREG can be read twice to retrieve the two bytes in the FIFO. The OERR bit has to be cleared in software. This is done by clearing the CREN bit. If OERR is set, transfers from RSR to RCREG are inhibited, so it is essential to clear the OERR bit if it is set. The 9th receive bit is buffered the same way as the receive data. Reading the RCREG register will allow the RX9D and FERR bits to be loaded with values for the next received data; therefore, it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old FERR and RX9D information.

Steps to follow when setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. See Section 14.1 for details.

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, then set the RCIE bit.

- 4. If 9-bit reception is desired, then set the RX9 bit.

- 5. If a single reception is required, set bit SREN. For continuous reception set bit CREN.

- 6. The RCIF bit will be set when reception is complete and an interrupt will be generated if the RCIE bit was set.

- 7. Read RCSTA to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading RCREG.

- 9. If any error occurred, clear the error by clearing CREN.

Note: To terminate a reception, either clear the SREN and CREN bits, or the SPEN bit. This will reset the receive logic so that it will be in the proper state when receive is re-enabled.

### FIGURE 14-10: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

A typical transmit sequence would go as follows:

- a) The user generates a START Condition by setting the START enable bit (SEN) in SSPCON2.

- b) SSPIF is set. The module will wait the required START time before any other operation takes place.

- c) The user loads the SSPBUF with address to transmit.

- d) Address is shifted out the SDA pin until all 8 bits are transmitted.

- e) The MSSP Module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- f) The module generates an interrupt at the end of the ninth clock cycle by setting SSPIF.

- g) The user loads the SSPBUF with eight bits of data.

- h) DATA is shifted out the SDA pin until all 8 bits are transmitted.

- i) The MSSP Module shifts in the ACK bit from the slave device, and writes its value into the SSPCON2 register (SSPCON2<6>).

- j) The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- k) The user generates a STOP condition by setting the STOP enable bit PEN in SSPCON2.

- I) Interrupt is generated once the STOP condition is complete.

### 15.2.8 BAUD RATE GENERATOR

In I<sup>2</sup>C Master mode, the reload value for the BRG is located in the lower 7 bits of the SSPADD register (Figure 15-18). When the BRG is loaded with this value, the BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (Tcr), on the Q2 and Q4 clock.

In I<sup>2</sup>C Master mode, the BRG is reloaded automatically. If Clock Arbitration is taking place, for instance, the BRG will be reloaded when the SCL pin is sampled high (Figure 15-19).

### FIGURE 15-18: BAUD RATE GENERATOR BLOCK DIAGRAM

#### SDA DX DX-1 SCL allowed to transition high. SCL de-asserted but slave holds SCL low (clock arbitration). SCL BRG decrements (on Q2 and Q4 cycles). BRG 03h 02h 01h 00h (hold off) 02h 03h Value SCL is sampled high, reload takes place and BRG starts its count. BRG Reload

### FIGURE 15-19: BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

# PIC17C7XX

| NEG                      | W                             | Negate W                                                                                                                                                                                          | 1                 |            |                                                        |  |  |

|--------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------|--------------------------------------------------------|--|--|

| Synt                     | ax:                           | [ <i>label</i> ] N                                                                                                                                                                                | EGW               | f,s        |                                                        |  |  |

| Ope                      | rands:                        | $0 \le f \le 255$<br>s $\in [0,1]$                                                                                                                                                                | 5                 |            |                                                        |  |  |

| Ope                      | ration:                       | WREG + 2<br>WREG + 2                                                                                                                                                                              |                   |            |                                                        |  |  |

| Statu                    | Status Affected: OV, C, DC, Z |                                                                                                                                                                                                   |                   |            |                                                        |  |  |

| Encoding: 0010 110s ffff |                               |                                                                                                                                                                                                   |                   |            | ffff                                                   |  |  |

| Des                      | cription:                     | WREG is negated using two's comple-<br>ment. If 's' is 0, the result is placed in<br>WREG and data memory location 'f'. If<br>'s' is 1, the result is placed only in data<br>memory location 'f'. |                   |            |                                                        |  |  |

| Wor                      | ds:                           | 1                                                                                                                                                                                                 |                   |            |                                                        |  |  |

| Cycl                     | es:                           | 1                                                                                                                                                                                                 |                   |            |                                                        |  |  |

| QC                       | vcle Activity:                |                                                                                                                                                                                                   |                   |            |                                                        |  |  |

|                          | Q1                            | Q2                                                                                                                                                                                                | Q3                | 3          | Q4                                                     |  |  |

|                          | Decode                        | Read<br>register 'f'                                                                                                                                                                              | Proce<br>Dat      | a re<br>ar | Write<br>gister 'f'<br>nd other<br>pecified<br>egister |  |  |

|                          |                               |                                                                                                                                                                                                   | •                 | •          |                                                        |  |  |

| <u>Exar</u>              | <u>mple</u> :                 | NEGW R                                                                                                                                                                                            | EG,0              |            |                                                        |  |  |

|                          | Before Instru<br>WREG         | = 0011 1                                                                                                                                                                                          | .010 <b>[0x</b> : |            |                                                        |  |  |

| NOF   | )              | No Opera        | ation       |     |    |                |  |

|-------|----------------|-----------------|-------------|-----|----|----------------|--|

| Synt  | ax:            | [ label ]       | NOP         |     |    |                |  |

| Ope   | rands:         | None            |             |     |    |                |  |

| Ope   | ration:        | No operation    |             |     |    |                |  |

| Statu | us Affected:   | None            |             |     |    |                |  |

| Enco  | oding:         | 0000            | 0000        | 000 | 0  | 0000           |  |

| Des   | cription:      | No operati      | on.         |     |    |                |  |

| Wor   | ds:            | 1               |             |     |    |                |  |

| Cycl  | es:            | 1               |             |     |    |                |  |

| QC    | vcle Activity: |                 |             |     |    |                |  |

|       | Q1             | Q2              | Q           | 3   |    | Q4             |  |

|       | Decode         | No<br>operation | No<br>opera |     | ор | No<br>peration |  |

### Example:

None.

| WREG           | =    | 0011 | 1010 <b>[0x3A]</b> , |

|----------------|------|------|----------------------|

| REG            | =    | 1010 | 1011 <b>[0xAB]</b>   |

| After Instruct | tion |      |                      |

| WREG           | =    | 1100 | 0110 <b>[0xC6]</b>   |

| REG            | =    | 1100 | 0110 <b>[0xC6]</b>   |

| RLNCF                     | Rotate L                                           | eft f (no c                                                                                                                                                               | carry) | 1                       | RRC         |  |  |

|---------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------|-------------|--|--|

| Syntax:                   | [ label ]                                          | RLNCF                                                                                                                                                                     | f,d    |                         | Synt        |  |  |

| Operands:                 | 0 ≤ f ≤ 25<br>d ∈ [0,1]                            | 5                                                                                                                                                                         |        |                         | Ope         |  |  |

| Operation:                | $f < n > \rightarrow d$<br>$f < 7 > \rightarrow d$ | ,                                                                                                                                                                         |        |                         | Ope         |  |  |

| Status Affected:          | None                                               |                                                                                                                                                                           |        |                         |             |  |  |

| Encoding:                 | 0010                                               | 0010 001d ffff ffff                                                                                                                                                       |        |                         |             |  |  |

| Description:              | one bit to t<br>placed in \                        | The contents of register 'f' are rotated<br>one bit to the left. If 'd' is 0, the result is<br>placed in WREG. If 'd' is 1, the result is<br>stored back in register 'f'. |        |                         |             |  |  |

|                           |                                                    | regis                                                                                                                                                                     | ster f |                         |             |  |  |

| Words:                    | 1                                                  |                                                                                                                                                                           |        |                         |             |  |  |

| Cycles:                   | 1                                                  |                                                                                                                                                                           |        |                         | 14/         |  |  |

| Q Cycle Activity:         |                                                    |                                                                                                                                                                           |        |                         | Wor         |  |  |

| Q1                        | Q2                                                 | Q3                                                                                                                                                                        |        | Q4                      | Cycl        |  |  |

| Decode                    | Read<br>register 'f'                               | Process<br>Data                                                                                                                                                           | -      | Write to<br>destination | QC          |  |  |

|                           |                                                    |                                                                                                                                                                           |        |                         |             |  |  |

| Example:                  | RLNCF                                              | REG,                                                                                                                                                                      | , 1    |                         |             |  |  |

| Before Instr              | uction                                             |                                                                                                                                                                           |        |                         | Буа         |  |  |

| C<br>REG                  | = 0<br>= 1110 1                                    | .011                                                                                                                                                                      |        |                         | <u>Exar</u> |  |  |

| After Instruc<br>C<br>REG | tion<br>=<br>= 1101 0                              | 111                                                                                                                                                                       |        |                         |             |  |  |

| RCF                    | Rotate Ri                                                                               | ght f th                                                   | rough C                   | arry                   |  |  |

|------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------|------------------------|--|--|

| Syntax:                | [ label ]                                                                               | RRCF                                                       | f,d                       |                        |  |  |

| )perands:              | $0 \le f \le 255$<br>$d \in [0,1]$                                                      | 5                                                          |                           |                        |  |  |

| Operation:             | $f < n > \rightarrow d < n-1 >;$<br>$f < 0 > \rightarrow C;$<br>$C \rightarrow d < 7 >$ |                                                            |                           |                        |  |  |

| Status Affected:       | С                                                                                       |                                                            |                           |                        |  |  |

| ncoding:               | 0001                                                                                    | 100d                                                       | ffff                      | ffff                   |  |  |

| Description:<br>Vords: | The conten<br>one bit to th<br>Flag. If 'd' is<br>WREG. If 'c<br>back in reg            | ne right the r<br>s 0, the r<br>t' is 1, the<br>ister 'f'. | hrough the<br>esult is pl | e Carry<br>aced in     |  |  |

| Cycles:                | 1                                                                                       |                                                            |                           |                        |  |  |

| Q Cycle Activity:      | •                                                                                       |                                                            |                           |                        |  |  |

| Q1                     | Q2                                                                                      | Q                                                          | 3                         | Q4                     |  |  |

| Decode                 | Read<br>register 'f'                                                                    | Proce<br>Dat                                               |                           | Write to<br>estination |  |  |

|                        |                                                                                         |                                                            |                           |                        |  |  |

| xample:                | RRCF REG                                                                                | 1,0                                                        |                           |                        |  |  |

| Before Instru          | ction                                                                                   |                                                            |                           |                        |  |  |

REG1 = 1110 0110

WREG = 0111 0011

= 0

= 0

1110 0110

С

С

After Instruction REG1 =

| TABLRD          | Table Re    | ead      |        |

|-----------------|-------------|----------|--------|

| Example1:       | TABLRD      | 1, 1,    | REG ;  |

| Before Instruc  | ction       |          |        |

| REG             |             | =        | 0x53   |

| TBLATH          |             | =        | 0xAA   |

| TBLATL          |             | =        | 0x55   |

| TBLPTR          |             | =        | 0xA356 |

| MEMORY          | (TBLPTR)    | =        | 0x1234 |

| After Instructi | on (table v | write co |        |

| REG             |             | =        | 0xAA   |

| TBLATH          |             | =        | 0x12   |

| TBLATL          |             | =        | 0x34   |

| TBLPTR          |             | =        | 0xA357 |

| MEMORY          | (TBLPTR)    | =        | 0x5678 |

| Example2:       | TABLRD      | 0, 0,    | REG ;  |

| Before Instruc  | ction       |          |        |

| REG             |             | =        | 0x53   |

| TBLATH          |             | =        | 0xAA   |

| TBLATL          |             | =        | 0x55   |

| TBLPTR          |             | =        | 0xA356 |

| MEMORY          | (TBLPTR)    | =        | 0x1234 |

| After Instructi | on (table v | write co |        |

| REG             |             | =        | 0x55   |

| TBLATH          |             | =        | 0x12   |

| TBLATL          |             | =        | 0x34   |

| TBLPTR          |             | =        | 0xA356 |

| MEMORY          | (TBLPTR)    | =        | 0x1234 |

|                 |             |          |        |

|                 |             |          |        |

|                 |             |          |        |

|                 |             |          |        |

|                 |             |          |        |

|                 |             |          |        |

|                 |             |          |        |

|                 |             |          |        |

| TABLWT                                                                                                               | Table Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                                                                                              | [ label ] TABLWT t,i,f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                |  |  |  |  |  |

| Operands:                                                                                                            | $0 \le f \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                |  |  |  |  |  |

|                                                                                                                      | ı ∈ [0,1]<br>t ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $i \in [0,1]$                                                                  |  |  |  |  |  |