Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 33MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 50                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 902 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 12x10b                                                                   |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-TQFP                                                                      |

| Supplier Device Package    | 64-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c756at-33e-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC17C7XX

| Address | Name                              | Bit 7           | Bit 6           | Bit 5          | Bit 4          | Bit 3        | Bit 2       | Bit 1       | Bit 0       | Value on<br>POR,<br>BOR | MCLR,<br>WDT |

|---------|-----------------------------------|-----------------|-----------------|----------------|----------------|--------------|-------------|-------------|-------------|-------------------------|--------------|

| Bank 2  |                                   |                 |                 |                |                |              |             |             |             |                         |              |

| 10h     | TMR1                              | Timer1's R      | legister        |                |                |              |             |             |             | xxxx xxxx               | uuuu uuuu    |

| 11h     | TMR2                              | Timer2's R      | legister        |                |                |              |             |             |             | xxxx xxxx               | uuuu uuuu    |

| 12h     | TMR3L                             | Timer3's R      | egister; Lov    | v Byte         |                |              |             |             |             | xxxx xxxx               | uuuu uuuu    |

| 13h     | TMR3H                             | Timer3's R      | egister; Hig    | h Byte         |                |              |             |             |             | xxxx xxxx               | uuuu uuuu    |

| 14h     | PR1                               | Timer1's P      | eriod Regis     | ter            |                |              |             |             |             | xxxx xxxx               | uuuu uuuu    |

| 15h     | PR2                               | Timer2's P      | eriod Regis     | ter            |                |              |             |             |             | xxxx xxxx               | uuuu uuuu    |

| 16h     | PR3L/CA1L                         | Timer3's P      | eriod Regis     | ter - Low Byt  | te/Capture1 F  | Register; Lo | w Byte      |             |             | xxxx xxxx               | uuuu uuuu    |

| 17h     | PR3H/CA1H                         | Timer3's P      | eriod Regis     | ter - High By  | te/Capture1    | Register; Hi | gh Byte     |             |             | xxxx xxxx               | uuuu uuuu    |

| Bank 3  |                                   |                 |                 |                |                |              |             |             |             |                         |              |

| 10h     | PW1DCL                            | DC1             | DC0             | —              | —              | —            | —           | —           | —           | xx                      | uu           |

| 11h     | PW2DCL                            | DC1             | DC0             | TM2PW2         | —              | —            | —           | —           | —           | xx0                     | uu0          |

| 12h     | PW1DCH                            | DC9             | DC8             | DC7            | DC6            | DC5          | DC4         | DC3         | DC2         | xxxx xxxx               | uuuu uuuu    |

| 13h     | PW2DCH                            | DC9             | DC8             | DC7            | DC6            | DC5          | DC4         | DC3         | DC2         | xxxx xxxx               | uuuu uuuu    |

| 14h     | CA2L                              | Capture2 I      | low Byte        | •              | •              |              |             |             |             | XXXX XXXX               | uuuu uuuu    |

| 15h     | CA2H                              | Capture2 I      | High Byte       |                |                |              |             |             |             | XXXX XXXX               | uuuu uuuu    |

| 16h     | TCON1                             | CA2ED1          | CA2ED0          | CA1ED1         | CA1ED0         | T16          | TMR3CS      | TMR2CS      | TMR1CS      | 0000 0000               | 0000 0000    |

| 17h     | TCON2                             | CA2OVF          | CA10VF          | PWM2ON         | PWM1ON         | CA1/PR3      | TMR3ON      | TMR2ON      | TMR10N      | 0000 0000               | 0000 0000    |

| Bank 4  |                                   |                 |                 |                |                |              |             |             |             |                         |              |

| 10h     | PIR2                              | SSPIF           | BCLIF           | ADIF           | —              | CA4IF        | CA3IF       | TX2IF       | RC2IF       | 000- 0010               | 000- 0010    |

| 11h     | PIE2                              | SSPIE           | BCLIE           | ADIE           | —              | CA4IE        | CA3IE       | TX2IE       | RC2IE       | 000- 0000               | 000- 0000    |

| 12h     | Unimplemented                     | —               | —               | —              | —              | —            | —           | —           | —           |                         |              |

| 13h     | RCSTA2                            | SPEN            | RX9             | SREN           | CREN           | —            | FERR        | OERR        | RX9D        | 0000 -00x               | 0000 -00u    |

| 14h     | RCREG2                            | Serial Port     | Receive Re      | egister for US | SART2          |              |             |             |             | xxxx xxxx               | uuuu uuuu    |

| 15h     | TXSTA2                            | CSRC            | TX9             | TXEN           | SYNC           | _            | _           | TRMT        | TX9D        | 00001x                  | 0000lu       |

| 16h     | TXREG2                            | Serial Port     | Transmit R      | egister for U  | SART2          |              |             |             |             | xxxx xxxx               | uuuu uuuu    |

| 17h     | SPBRG2                            | Baud Rate       | Generator       | for USART2     |                |              |             |             |             | 0000 0000               | 0000 0000    |

| Bank 5: |                                   |                 |                 |                |                |              |             |             |             |                         |              |

| 10h     | DDRF                              | Data Direc      | tion Registe    | er for PORTF   | :              |              |             |             |             | 1111 1111               | 1111 1111    |

| 11h     | PORTF <sup>(4)</sup>              | RF7/<br>AN11    | RF6/<br>AN10    | RF5/<br>AN9    | RF4/<br>AN8    | RF3/<br>AN7  | RF2/<br>AN6 | RF1/<br>AN5 | RF0/<br>AN4 | 0000 0000               | 0000 0000    |

| 12h     | DDRG                              | Data Direc      | tion Registe    | er for PORTO   | 6              |              |             |             |             | 1111 1111               | 1111 1111    |

| 13h     | PORTG <sup>(4)</sup>              | RG7/<br>TX2/CK2 | RG6/<br>RX2/DT2 | RG5/<br>PWM3   | RG4/<br>CAP3   | RG3/<br>AN0  | RG2/<br>AN1 | RG1/<br>AN2 | RG0/<br>AN3 | xxxx 0000               | uuuu 0000    |

| 14h     | ADCON0                            | CHS3            | CHS2            | CHS1           | CHS0           | —            | GO/DONE     | —           | ADON        | 0000 -0-0               | 0000 -0-0    |

| 15h     | ADCON1                            | ADCS1           | ADCS0           | ADFM           | —              | PCFG3        | PCFG2       | PCFG1       | PCFG0       | 000- 0000               | 000- 0000    |

| 16h     | ADRESL                            | A/D Result      | t Register Lo   | ow Byte        |                |              |             |             |             | xxxx xxxx               | uuuu uuuu    |

| 17h     | ADRESH                            | A/D Result      | t Register H    | igh Byte       |                |              |             |             |             | xxxx xxxx               | uuuu uuuu    |

| Legend: | x = unknown, u<br>Shaded cells at | -               |                 | •              | , read as '0', | q = value d  | epends on c | ondition.   |             |                         |              |

#### TABLE 7-3: SPECIAL FUNCTION REGISTERS (CONTINUED)

Shaded cells are unimplemented, read as '0'.

**Note** 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<15:8> whose contents are updated from, or transferred to, the upper byte of the program counter.

2: The TO and PD status bits in CPUSTA are not affected by a MCLR Reset.

3: Bank 8 and associated registers are only implemented on the PIC17C76X devices.

4: This is the value that will be in the port output latch.

5: When the device is configured for Microprocessor or Extended Microcontroller mode, the operation of this port does not rely on these registers.

6: On any device RESET, these pins are configured as inputs.

| Address               | Name                                                       | Bit 7        | Bit 6         | Bit 5                     | Bit 4        | Bit 3     | Bit 2       | Bit 1                       | Bit 0         | Value on<br>POR,<br>BOR | MCLR,<br>WDT |

|-----------------------|------------------------------------------------------------|--------------|---------------|---------------------------|--------------|-----------|-------------|-----------------------------|---------------|-------------------------|--------------|

| Bank 6                | •                                                          |              | •             |                           |              |           |             |                             |               |                         |              |

| 10h                   | SSPADD                                                     | SSP Addre    | ess Register  | in I <sup>2</sup> C Slave | e mode. SSF  | Baud Rate | Reload Regi | ster in I <sup>2</sup> C Ma | aster mode    | 0000 0000               | 0000 0000    |

| 11h                   | SSPCON1                                                    | WCOL         | SSPOV         | SSPEN                     | CKP          | SSPM3     | SSPM2       | SSPM1                       | SSPM0         | 0000 0000               | 0000 0000    |

| 12h                   | SSPCON2                                                    | GCEN         | AKSTAT        | AKDT                      | AKEN         | RCEN      | PEN         | RSEN                        | SEN           | 0000 0000               | 0000 0000    |

| 13h                   | SSPSTAT                                                    | SMP          | CKE           | D/A                       | Р            | S         | R/W         | UA                          | BF            | 0000 0000               | 0000 0000    |

| 14h                   | SSPBUF                                                     | Synchrono    | ous Serial Po | •                         | xxxx xxxx    | uuuu uuuu |             |                             |               |                         |              |

| 15h                   | Unimplemented                                              | _            | —             | —                         | —            | _         | —           | —                           | _             |                         |              |

| 16h                   | Unimplemented                                              | _            | _             | _                         | _            | _         | _           | _                           | _             |                         |              |

| 17h                   | Unimplemented                                              | _            | _             |                           | _            | _         | _           | _                           | _             |                         |              |

| Bank 7                | •                                                          |              |               |                           |              | •         |             |                             | •             |                         |              |

| 10h                   | PW3DCL                                                     | DC1          | DC0           | TM2PW3                    | _            | _         | _           | _                           | _             | xx0                     | uu0          |

| 11h                   | PW3DCH                                                     | DC9          | DC8           | DC7                       | DC6          | DC5       | DC4         | DC3                         | DC2           | xxxx xxxx               | uuuu uuuu    |

| 12h                   | CA3L                                                       | Capture3 I   | _ow Byte      |                           |              |           |             |                             |               | xxxx xxxx               | uuuu uuuu    |

| 13h                   | САЗН                                                       | Capture3 I   |               |                           |              |           |             |                             |               | xxxx xxxx               | uuuu uuuu    |

| 14h                   | CA4L                                                       | Capture4 I   | _ow Byte      |                           |              |           |             |                             |               | xxxx xxxx               | uuuu uuuu    |

| 15h                   | CA4H                                                       | Capture4 I   | High Byte     |                           |              |           |             |                             |               | xxxx xxxx               | uuuu uuuu    |

| 16h                   | TCON3                                                      |              | CA40VF        | CA30VF                    | CA4ED1       | CA4ED0    | CA3ED1      | CA3ED0                      | <b>PWM3ON</b> | -000 0000               | -000 0000    |

| 17h                   | Unimplemented                                              | _            |               | _                         |              | _         | _           | _                           | _             |                         |              |

| Bank 8 <sup>(3)</sup> |                                                            |              |               |                           |              | •         |             |                             | •             |                         |              |

| 10h <sup>(3)</sup>    | DDRH                                                       | Data Direc   | tion Registe  | r for PORTH               | 1            |           |             |                             |               | 1111 1111               | 1111 1111    |

|                       | PORTH <sup>(4)</sup>                                       | RH7/<br>AN15 | RH6/<br>AN14  | RH5/<br>AN13              | RH4/<br>AN12 | RH3       | RH2         | RH1                         | RH0           | xxxx xxxx               | uuuu uuuu    |

| 12h <sup>(3)</sup>    | DDRJ                                                       | Data Direc   | tion Registe  | r for PORTJ               |              |           |             |                             |               | 1111 1111               | 1111 1111    |

| 13h <sup>(3)</sup>    | PORTJ <sup>(4)</sup>                                       | RJ7          | RJ6           | RJ5                       | RJ4          | RJ3       | RJ2         | RJ1                         | RJ0           | xxxx xxxx               | uuuu uuuu    |

| 14h <sup>(3)</sup>    | Unimplemented                                              | _            | _             | _                         | _            | _         |             | _                           | _             |                         |              |

| 15h <sup>(3)</sup>    | Unimplemented                                              |              | _             | _                         | _            | _         | _           | _                           | _             |                         |              |

| 16h <sup>(3)</sup>    | Unimplemented                                              |              |               | _                         | _            | _         | _           | _                           | _             |                         |              |

| 17h <sup>(3)</sup>    | Unimplemented                                              |              |               | _                         |              | _         |             |                             | _             |                         |              |

| Unbanke               |                                                            |              | 1             |                           |              |           |             |                             |               |                         |              |

| 18h                   | PRODL Low Byte of 16-bit Product (8 x 8 Hardware Multiply) |              |               |                           |              |           |             |                             |               | XXXX XXXX               | uuuu uuuu    |

| 19h                   | PRODH                                                      | -            |               |                           | Hardware Mu  |           |             |                             |               | xxxx xxxx               | uuuu uuuu    |

#### SPECIAL FUNCTION REGISTERS (CONTINUED) TABLE 7-3

Shaded cells are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<15:8> whose

contents are updated from, or transferred to, the upper byte of the program counter.

2: The TO and PD status bits in CPUSTA are not affected by a MCLR Reset.

3: Bank 8 and associated registers are only implemented on the PIC17C76X devices.

4: This is the value that will be in the port output latch.

5: When the device is configured for Microprocessor or Extended Microcontroller mode, the operation of this port does not rely on these registers.

6: On any device RESET, these pins are configured as inputs.

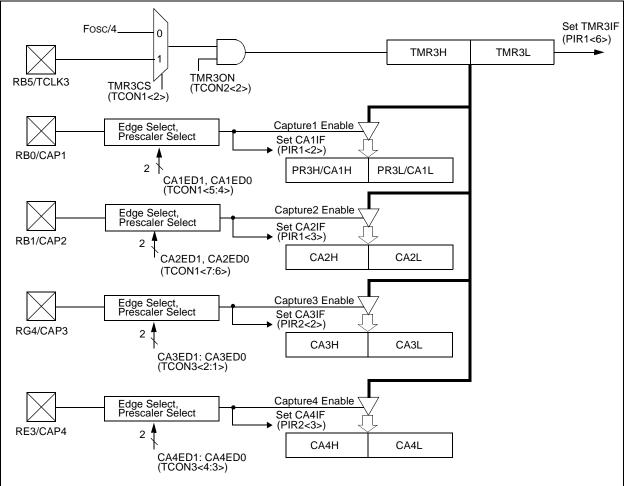

#### 13.2.2 FOUR CAPTURE MODE

This mode is selected by setting bit CA1/PR3. A block diagram is shown in Figure 13-6. In this mode, TMR3 runs without a period register and increments from 0000h to FFFFh and rolls over to 0000h. The TMR3 interrupt Flag (TMR3IF) is set on this rollover. The TMR3IF bit must be cleared in software.

Registers PR3H/CA1H and PR3L/CA1L make a 16-bit capture register (Capture1). It captures events on pin RB0/CAP1. Capture mode is configured by the CA1ED1 and CA1ED0 bits. Capture1 Interrupt Flag bit (CA1IF) is set upon detection of the capture event. The corresponding interrupt mask bit is CA1IE. The Capture1 Overflow Status bit is CA1OVF.

All the captures operate in the same manner. Refer to Section 13.2.1 for the operation of capture.

#### FIGURE 13-6: TIMER3 WITH FOUR CAPTURES BLOCK DIAGRAM

|            | <b>F</b> aat |                |           | <b>F</b>           |       |             | <b>F</b> |                    |           | <b>F</b>  |        |                    |

|------------|--------------|----------------|-----------|--------------------|-------|-------------|----------|--------------------|-----------|-----------|--------|--------------------|

| BAUD       | FOSC         | = 33 MHz       | SPBRG     | FOSC = 25 Mł       | 1Z    | SPBRG       | FOSC = 2 | 0 MHz              | SPBRG     | FOSC = 1  | 6 MHz  | SPBRG              |

| RATE       |              |                | VALUE     |                    |       | VALUE       |          | **                 | VALUE     |           | **     | VALUE              |

| (K)        | KBAL         |                | (DECIMAL) |                    | RROR  | (DECIMAL)   |          | %ERROR             | (DECIMAL) | KBAUD     | %ERROR | (DECIMAL)          |

| 0.3        | NA           | . —            | —         | NA                 | -     | _           | NA       | _                  | —         | NA        | _      | _                  |

| 1.2        | NA           | . —            | —         | NA                 | _     | _           | NA       | _                  | _         | NA        | _      | _                  |

| 2.4        | NA           | . —            | —         | NA                 | _     | _           | NA       | _                  | _         | NA        | _      | _                  |

| 9.6        | NA           | . —            | —         | NA                 | —     | —           | NA       | —                  | —         | NA        | —      | —                  |

| 19.2       | NA           | . —            | —         | NA                 | —     | —           | 19.53    | +1.73              | 255       | 19.23     | +0.16  | 207                |

| 76.8       | 77.1         | 0 +0.39        | 106       | 77.16 -            | +0.47 | 80          | 76.92    | +0.16              | 64        | 76.92     | +0.16  | 51                 |

| 96         | 95.9         | 3 -0.07        | 85        | 96.15 -            | -0.16 | 64          | 96.15    | +0.16              | 51        | 95.24     | -0.79  | 41                 |

| 300        | 294.6        | 64 -1.79       | 27        | 297.62             | 0.79  | 20          | 294.1    | -1.96              | 16        | 307.69    | +2.56  | 12                 |

| 500        | 485.2        | 29 -2.94       | 16        | 480.77             | -3.85 | 12          | 500      | 0                  | 9         | 500       | 0      | 7                  |

| HIGH       | 825          | 0 —            | 0         | 6250               | _     | 0           | 5000     | _                  | 0         | 4000      | _      | 0                  |

| LOW        | 32.2         | 2 —            | 255       | 24.41              | _     | 255         | 19.53    | —                  | 255       | 15.625    | —      | 255                |

| 5.41       | 15           | Fosc = 10 MHz  | Z         | 00000              | Fosc  | = 7.159 MHz |          | 00000              | Fosc = 5  | .068 MHz  |        | 00000              |

| BAU<br>RAT |              |                |           | SPBRG<br>VALUE     |       |             |          | SPBRG<br>VALUE     |           |           |        | SPBRG<br>VALUE     |

| (K         |              | KBAUD          | %ERROR    | (DECIMAL)          | KB    | AUD %       | ERROR    | (DECIMAL)          | KBAUI     | D %E      | RROR   | (DECIMAL)          |

| 0.3        | 3            | NA             |           |                    | Ν     | NA          | _        | _                  | NA        |           | -      | —                  |

| 1.2        | 2            | NA             | —         | _                  | Ν     | ٨A          | _        | —                  | NA        |           | _      | _                  |

| 2.4        | 4            | NA             | _         | —                  | Ν     | ١A          | _        | —                  | NA        |           | -      | _                  |

| 9.0        | 6            | 9.766          | +1.73     | 255                | 9.    | 622         | +0.23    | 185                | 9.6       |           | 0      | 131                |

| 19.        | .2           | 19.23          | +0.16     | 129                | 19    | .24         | +0.23    | 92                 | 19.2      |           | 0      | 65                 |

| 76.        | .8           | 75.76          | -1.36     | 32                 | 77    | .82         | +1.32    | 22                 | 79.2      | +         | 3.13   | 15                 |

| 96         | 6            | 96.15          | +0.16     | 25                 | 94    | .20         | -1.88    | 18                 | 97.48     | +         | 1.54   | 12                 |

| 30         | 0            | 312.5          | +4.17     | 7                  | 29    | 98.3        | -0.57    | 5                  | 316.8     | +         | 5.60   | 3                  |

| 50         | 0            | 500            | 0         | 4                  | Ν     | ١A          | _        | —                  | NA        |           | -      | _                  |

| HIG        | θH           | 2500           | —         | 0                  | 17    | 89.8        | _        | 0                  | 1267      |           | _      | 0                  |

| LO         | W            | 9.766          | —         | 255                | 6.9   | 991         | _        | 255                | 4.950     |           | _      | 255                |

|            |              | Fosc = 3.579 M | IH7       |                    | Fosc  | = 1 MHz     |          |                    | FOSC = 3  | 2.768 kHz |        |                    |

| BAU        |              |                |           | SPBRG              |       |             |          | SPBRG              |           |           |        | SPBRG              |

| RAT<br>(K  |              | KBAUD          | %ERROR    | VALUE<br>(DECIMAL) | KB    | AUD %       | ERROR    | VALUE<br>(DECIMAL) | KBAU      | D %E      | RROR   | VALUE<br>(DECIMAL) |

| 0.3        | 3            | NA             |           |                    | N     | NA          | _        |                    | 0.303     | +         | 1.14   | 26                 |

| 1.2        |              | NA             | _         | _                  |       |             | +0.16    | 207                | 1.170     |           | 2.48   | 6                  |

| 2.4        |              | NA             | _         | _                  |       |             | +0.16    | 103                | NA        |           | _      |                    |

| 9.6        |              | 9.622          | +0.23     | 92                 |       |             | +0.16    | 25                 | NA        |           | _      | _                  |

| 19.        |              | 19.04          | -0.83     | 46                 |       |             | +0.16    | 12                 | NA        |           | _      | _                  |

| 76.        |              | 74.57          | -2.90     | 10                 | -     |             | +8.51    | 2                  | NA        |           | _      | _                  |

| 96         |              | 99.43          | _3.57     | 8                  |       | NA          | _        | _                  | NA        |           | _      | _                  |

|            | -            | 00.10          | _0.07     | -                  | 1 .   |             |          |                    |           |           |        |                    |

| TABLE 14-4: | BAUD RATES FOR SYNCHRONOUS MODE |

|-------------|---------------------------------|

|-------------|---------------------------------|

298.3

NA

894.9

3.496

-0.57

\_

\_

2

—

0

255

NA

NA

250

0.976

—

\_

\_

\_

\_

0

255

NA

NA

8.192

0.032

\_

\_

\_

\_

\_

\_

0

255

300

500

HIGH

LOW

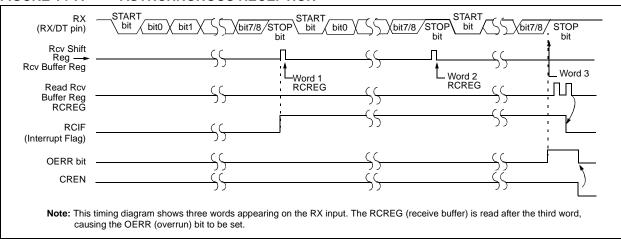

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the RCIE bit.

- 4. If 9-bit reception is desired, then set the RX9 bit.

- 5. Enable the reception by setting the CREN bit.

- 6. The RCIF bit will be set when reception completes and an interrupt will be generated if the RCIE bit was set.

- 7. Read RCSTA to get the ninth bit (if enabled) and FERR bit to determine if any error occurred during reception.

- 8. Read RCREG for the 8-bit received data.

- 9. If an overrun error occurred, clear the error by clearing the OERR bit.

- Note: To terminate a reception, either clear the SREN and CREN bits, or the SPEN bit. This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

#### FIGURE 14-7: ASYNCHRONOUS RECEPTION

#### TABLE 14-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address     | Name   | Bit 7     | Bit 6    | Bit 5      | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | MCLR, WDT |

|-------------|--------|-----------|----------|------------|--------|-------|-------|-------|-------|-------------------------|-----------|

| 16h, Bank 1 | PIR1   | RBIF      | TMR3IF   | TMR2IF     | TMR1IF | CA2IF | CA1IF | TX1IF | RC1IF | x000 0010               | u000 0010 |

| 17h, Bank 1 | PIE1   | RBIE      | TMR3IE   | TMR2IE     | TMR1IE | CA2IE | CA1IE | TX1IE | RC1IE | 0000 0000               | 0000 0000 |

| 13h, Bank 0 | RCSTA1 | SPEN      | RX9      | SREN       | CREN   |       | FERR  | OERR  | RX9D  | 0000 -00x               | 0000 -00u |

| 14h, Bank 0 | RCREG1 | RX7       | RX6      | RX5        | RX4    | RX3   | RX2   | RX1   | RX0   | xxxx xxxx               | uuuu uuuu |

| 15h, Bank 0 | TXSTA1 | CSRC      | TX9      | TXEN       | SYNC   | _     | _     | TRMT  | TX9D  | 00001x                  | 00001u    |

| 17h, Bank 0 | SPBRG1 | Baud Rate | Generato | r Register |        |       |       |       |       | 0000 0000               | 0000 0000 |

| 10h, Bank 4 | PIR2   | SSPIF     | BCLIF    | ADIF       | —      | CA4IF | CA3IF | TX2IF | RC2IF | 000- 0010               | 000- 0010 |

| 11h, Bank 4 | PIE2   | SSPIE     | BCLIE    | ADIE       | _      | CA4IE | CA3IE | TX2IE | RC2IE | 000- 0000               | 000- 0000 |

| 13h, Bank 4 | RCSTA2 | SPEN      | RX9      | SREN       | CREN   | _     | FERR  | OERR  | RX9D  | 0000 -00x               | 0000 -00u |

| 14h, Bank 4 | RCREG2 | RX7       | RX6      | RX5        | RX4    | RX3   | RX2   | RX1   | RX0   | xxxx xxxx               | uuuu uuuu |

| 15h, Bank 4 | TXSTA2 | CSRC      | TX9      | TXEN       | SYNC   |       | —     | TRMT  | TX9D  | 00001x                  | 00001u    |

| 17h, Bank 4 | SPBRG2 | Baud Rate | Generato | r Register |        |       |       |       |       | 0000 0000               | 0000 0000 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as a '0'. Shaded cells are not used for asynchronous reception.

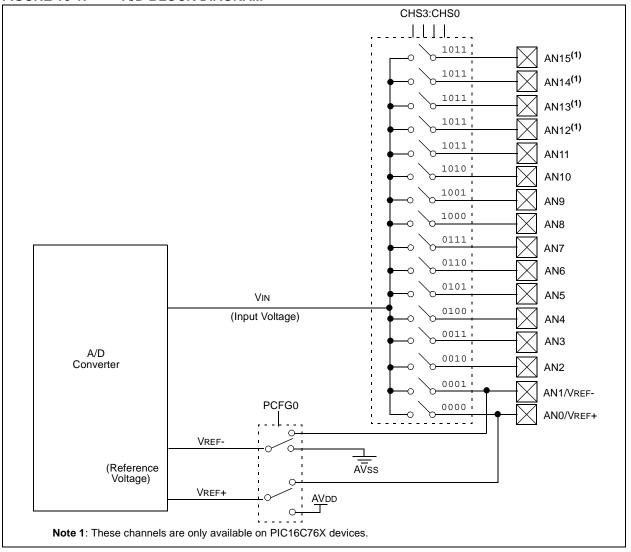

The ADRESH:ADRESL registers contain the 10-bit result of the A/D conversion. When the A/D conversion is complete, the result is loaded into this A/D result register pair, the GO/DONE bit (ADCON0<2>) is cleared and A/D interrupt flag bit, ADIF is set. The block diagrams of the A/D module are shown in Figure 16-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding DDR bits selected as inputs. To determine sample time, see Section 16.1. After this acquisition time has elapsed, the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- a) Configure analog pins/voltage reference/ and digital I/O (ADCON1)

- b) Select A/D input channel (ADCON0)

- c) Select A/D conversion clock (ADCON0)

- d) Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- a) Clear ADIF bit

- b) Set ADIE bit

- c) Clear GLINTD bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- a) Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- a) Polling for the GO/DONE bit to be cleared OR

- b) Waiting for the A/D interrupt

- 6. Read A/D Result register pair (ADRESH:ADRESL), clear bit ADIF, if required.

- 7. For next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

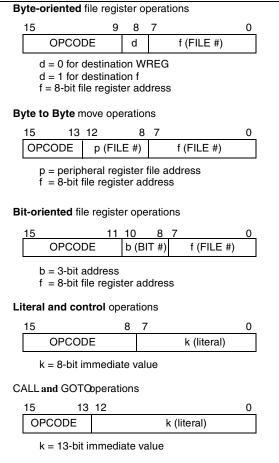

Table 18-2 lists the instructions recognized by the MPASM assembler.

**Note 1:** Any unused opcode is Reserved. Use of any reserved opcode may cause unexpected operation.

All instruction examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

To represent a binary number:

0000 0100b

where b signifies a binary string.

## FIGURE 18-1: GENERAL FORMAT FOR INSTRUCTIONS

#### 18.1 Special Function Registers as Source/Destination

The PIC17C7XX's orthogonal instruction set allows read and write of all file registers, including special function registers. There are some special situations the user should be aware of:

#### 18.1.1 ALUSTA AS DESTINATION

If an instruction writes to ALUSTA, the Z, C, DC and OV bits may be set or cleared as a result of the instruction and overwrite the original data bits written. For example, executing CLRF ALUSTA will clear register ALUSTA and then set the Z bit leaving 0000 0100b in the register.

#### 18.1.2 PCL AS SOURCE OR DESTINATION

Read, write or read-modify-write on PCL may have the following results:

| Read PC:           | $PCH \to PCLATH;  PCL \to dest$                                                              |

|--------------------|----------------------------------------------------------------------------------------------|

| Write PCL:         | PCLATH $\rightarrow$ PCH;<br>8-bit destination value $\rightarrow$ PCL                       |

| Read-Modify-Write: | PCL $\rightarrow$ ALU operand<br>PCLATH $\rightarrow$ PCH;<br>8-bit result $\rightarrow$ PCL |

Where PCH = program counter high byte (not an addressable register), PCLATH = Program counter high holding latch, dest = destination, WREG or f.

#### 18.1.3 BIT MANIPULATION

All bit manipulation instructions are done by first reading the entire register, operating on the selected bit and writing the result back (read-modify-write (R-M-W)). The user should keep this in mind when operating on some special function registers, such as ports.

#### TABLE 18-2: PIC17CXXX INSTRUCTION SET

| Mnemonic | ,     | Description                           | Cycles |      | 16-bit C | Opcode | 1    | Status    | Nete- |

|----------|-------|---------------------------------------|--------|------|----------|--------|------|-----------|-------|

| Operands |       | Description                           | Cycles | MSb  |          |        | LSb  | Affected  | Notes |

| BYTE-ORI | ENTED | FILE REGISTER OPERATIONS              |        |      |          |        |      | 1         |       |

| ADDWF    | f,d   | ADD WREG to f                         | 1      | 0000 | 111d     | ffff   | ffff | OV,C,DC,Z |       |

| ADDWFC   | f,d   | ADD WREG and Carry bit to f           | 1      | 0001 | 000d     | ffff   | ffff | OV,C,DC,Z |       |

| ANDWF    | f,d   | AND WREG with f                       | 1      | 0000 | 101d     | ffff   | ffff | Z         |       |

| CLRF     | f,s   | Clear f, or Clear f and Clear WREG    | 1      | 0010 | 100s     | ffff   | ffff | None      | 3     |

| COMF     | f,d   | Complement f                          | 1      | 0001 | 001d     | ffff   | ffff | Z         |       |

| CPFSEQ   | f     | Compare f with WREG, skip if f = WREG | 1 (2)  | 0011 | 0001     | ffff   | ffff | None      | 6,8   |

| CPFSGT   | f     | Compare f with WREG, skip if f > WREG | 1 (2)  | 0011 | 0010     | ffff   | ffff | None      | 2,6,8 |

| CPFSLT   | f     | Compare f with WREG, skip if f < WREG | 1 (2)  | 0011 | 0000     | ffff   | ffff | None      | 2,6,8 |

| DAW      | f,s   | Decimal Adjust WREG Register          | 1      | 0010 | 111s     | ffff   | ffff | С         | 3     |

| DECF     | f,d   | Decrement f                           | 1      | 0000 | 011d     | ffff   | ffff | OV,C,DC,Z |       |

| DECFSZ   | f,d   | Decrement f, skip if 0                | 1 (2)  | 0001 | 011d     | ffff   | ffff | None      | 6,8   |

| DCFSNZ   | f,d   | Decrement f, skip if not 0            | 1 (2)  | 0010 | 011d     | ffff   | ffff | None      | 6,8   |

| INCF     | f,d   | Increment f                           | 1      | 0001 | 010d     | ffff   | ffff | OV,C,DC,Z |       |

| INCFSZ   | f,d   | Increment f, skip if 0                | 1 (2)  | 0001 | 111d     | ffff   | ffff | None      | 6,8   |

| INFSNZ   | f,d   | Increment f, skip if not 0            | 1 (2)  | 0010 | 010d     | ffff   | ffff | None      | 6,8   |

| IORWF    | f,d   | Inclusive OR WREG with f              | 1      | 0000 | 100d     | ffff   | ffff | Z         |       |

| MOVFP    | f,p   | Move f to p                           | 1      | 011p | pppp     | ffff   | ffff | None      |       |

| MOVPF    | p,f   | Move p to f                           | 1      | 010p | pppp     | ffff   | ffff | Z         |       |

| MOVWF    | f     | Move WREG to f                        | 1      | 0000 | 0001     | ffff   | ffff | None      |       |

| MULWF    | f     | Multiply WREG with f                  | 1      | 0011 | 0100     | ffff   | ffff | None      |       |

| NEGW     | f,s   | Negate WREG                           | 1      | 0010 | 110s     | ffff   | ffff | OV,C,DC,Z | 1,3   |

| NOP      | _     | No Operation                          | 1      | 0000 | 0000     | 0000   | 0000 | None      |       |

| RLCF     | f,d   | Rotate left f through Carry           | 1      | 0001 | 101d     | ffff   | ffff | С         |       |

| RLNCF    | f,d   | Rotate left f (no carry)              | 1      | 0010 | 001d     | ffff   | ffff | None      |       |

| RRCF     | f,d   | Rotate right f through Carry          | 1      | 0001 | 100d     | ffff   | ffff | С         |       |

| RRNCF    | f,d   | Rotate right f (no carry)             | 1      | 0010 | 000d     | ffff   | ffff | None      |       |

| SETF     | f,s   | Set f                                 | 1      | 0010 | 101s     | ffff   | ffff | None      | 3     |

| SUBWF    | f,d   | Subtract WREG from f                  | 1      | 0000 | 010d     | ffff   | ffff | OV,C,DC,Z | 1     |

| SUBWFB   | f,d   | Subtract WREG from f with Borrow      | 1      | 0000 | 001d     | ffff   | ffff | OV,C,DC,Z | 1     |

| SWAPF    | f,d   | Swap f                                | 1      | 0001 | 110d     | ffff   | ffff | None      |       |

| TABLRD   | t,i,f | Table Read                            | 2 (3)  | 1010 | 10ti     | ffff   | ffff | None      | 7     |

| TABLWT   | t,i,f | Table Write                           | 2      | 1010 | 11ti     | ffff   | ffff | None      | 5     |

| TLRD     | t,f   | Table Latch Read                      | 1      | 1010 | 00tx     | ffff   | ffff | None      |       |

| TLWT     | t,f   | Table Latch Write                     | 1      | 1010 | 01tx     | ffff   | ffff | None      |       |

Legend: Refer to Table 18-1 for opcode field descriptions.

Note 1: 2's Complement method.

**2:** Unsigned arithmetic.

**3:** If s = '1', only the file is affected: If s = '0', both the WREG register and the file are affected; If only the Working register (WREG) is required to be affected, then f = WREG must be specified.

4: During an LCALL, the contents of PCLATH are loaded into the MSB of the PC and kkkk kkkk is loaded into the LSB of the PC (PCL).

5: Multiple cycle instruction for EPROM programming when table pointer selects internal EPROM. The instruction is terminated by an interrupt event. When writing to external program memory, it is a two-cycle instruction.

**6:** Two-cycle instruction when condition is true, else single cycle instruction.

7: Two-cycle instruction except for TABLRD to PCL (program counter low byte), in which case it takes 3 cycles.

8: A "skip" means that instruction fetched during execution of current instruction is not executed, instead a NOP is executed.

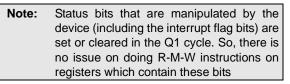

#### TABLE 20-10: SPI MODE REQUIREMENTS (SLAVE MODE TIMING, CKE = 0)

| Param.<br>No. | Symbol                | Characteristic                  |             | Min          | Тур† | Max | Units | Conditions |

|---------------|-----------------------|---------------------------------|-------------|--------------|------|-----|-------|------------|

| 70            | TssL2scH,<br>TssL2scL | SS pto SCK por SCK ninput       |             | Тсу          | —    | —   | ns    |            |

| 71            | TscH                  | SCK input high time             | Continuous  | 1.25Tcy + 30 | _    | _   | ns    |            |

| 71A           |                       | (Slave mode)                    | Single Byte | 40           | _    | _   | ns    | (Note 1)   |

| 72            | TscL                  | SCK input low time              | Continuous  | 1.25Tcy + 30 | _    | _   | ns    |            |

| 72A           |                       | (Slave mode)                    | Single Byte | 40           | _    | _   | ns    | (Note 1)   |

| 73            | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to | SCK edge    | 100          | _    | _   | ns    |            |

| 73A           | Тв2в                  |                                 |             |              |      |     |       |            |

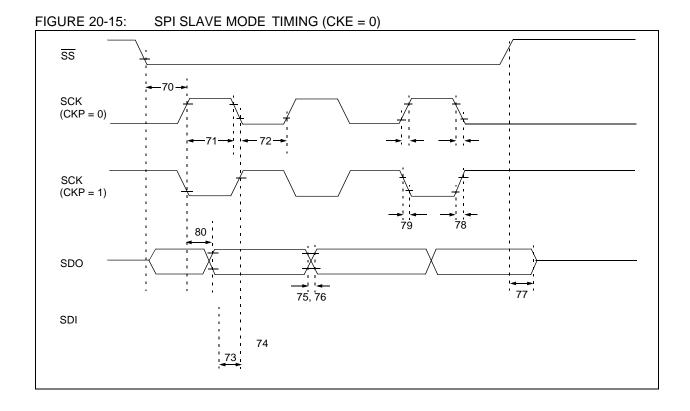

### TABLE 20-13: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Param<br>No. | Sym     | Character               | istic                     | Min              | Max  | Units | Conditions                   |

|--------------|---------|-------------------------|---------------------------|------------------|------|-------|------------------------------|

| 100          | Thigh   | Clock high time         | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                              |

|              |         |                         | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                              |

|              |         |                         | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                              |

| 101          | Tlow    | Clock low time          | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                              |

|              |         |                         | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                              |

|              |         |                         | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | ms    |                              |

| 102          | Tr      | SDA and SCL rise time   | 100 kHz mode              | —                | 1000 | ns    | Cb is specified to be from   |

|              |         |                         | 400 kHz mode              | 20 + 0.1Cb       | 300  | ns    | 10 to 400 pF                 |

|              |         |                         | 1 MHz mode <sup>(1)</sup> | _                | 300  | ns    |                              |

| 103          | Tf      | SDA and SCL fall time   | 100 kHz mode              | _                | 300  | ns    | Cb is specified to be from   |

|              |         |                         | 400 kHz mode              | 20 + 0.1Cb       | 300  | ns    | 10 to 400 pF                 |

|              |         |                         | 1 MHz mode <sup>(1)</sup> | _                | 10   | ns    |                              |

| 90           | Tsu:sta | START condition setup   | 100 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms    | Only relevant for Repeated   |

|              |         | time                    | 400 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms    | Start condition              |

|              |         |                         | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                              |

| 91           | Thd:sta | START condition hold    | 100 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms    | After this period, the first |

|              |         | time                    | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    | clock pulse is generated     |

|              |         |                         | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | ms    |                              |

| 106          | Thd:dat | Data input hold time    | 100 kHz mode              | 0                | _    | ns    |                              |

|              |         |                         | 400 kHz mode              | 0                | 0.9  | ms    |                              |

|              |         |                         | 1 MHz mode <sup>(1)</sup> | 0                | _    | ns    |                              |

| 107          | Tsu:dat | Data input setup time   | 100 kHz mode              | 250              | _    | ns    | (Note 2)                     |

|              |         |                         | 400 kHz mode              | 100              | _    | ns    |                              |

|              |         |                         | 1 MHz mode <sup>(1)</sup> | 100              | _    | ns    |                              |

| 92           | Tsu:sto | STOP condition          | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                              |

|              |         | setup time              | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                              |

|              |         |                         | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | ms    |                              |

| 109          | Таа     | Output valid from clock | 100 kHz mode              |                  | 3500 | ns    |                              |

|              |         |                         | 400 kHz mode              |                  | 1000 | ns    |                              |

|              |         |                         | 1 MHz mode <sup>(1)</sup> | _                | 400  | ns    |                              |

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C$  pins.

2: A fast mode (400 KHz) I<sup>2</sup>C bus device can be used in a standard mode I<sup>2</sup>C bus system, but the parameter # 107 ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line. Parameter #102 + #107 = 1000 + 250 = 1250 ns (for 100 kHz mode) before the SCL line is released.

**3:**  $C_b$  is specified to be from 10-400pF. The minimum specifications are characterized with  $C_b=10pF$ . The rise time spec (t<sub>r</sub>) is characterized with  $R_p=R_p$  min. The minimum fall time specification (t<sub>f</sub>) is characterized with  $C_b=10pF$ , and  $R_p=R_p$  max. These are only valid for fast mode operation (VDD=4.5-5.5V) and where the SPM bit (SSPSTAT<7>) =1.)

4: Max specifications for these parameters are valid for falling edge only. Specs are characterized with R<sub>p</sub>=R<sub>p</sub> min and C<sub>b</sub>=400pF for standard mode, 200pF for fast mode, and 10pF for 1MHz mode.

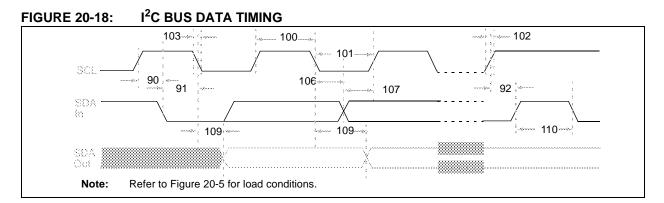

#### 64-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |      | INCHES |      | MILLIMETERS* |       |       |  |

|--------------------------|----------|------|--------|------|--------------|-------|-------|--|

| Dimensior                | n Limits | MIN  | NOM    | MAX  | MIN          | NOM   | MAX   |  |

| Number of Pins           | n        |      | 64     |      |              | 64    |       |  |

| Pitch                    | р        |      | .020   |      |              | 0.50  |       |  |

| Pins per Side            | n1       |      | 16     |      |              | 16    |       |  |

| Overall Height           | А        | .039 | .043   | .047 | 1.00         | 1.10  | 1.20  |  |

| Molded Package Thickness | A2       | .037 | .039   | .041 | 0.95         | 1.00  | 1.05  |  |

| Standoff §               | A1       | .002 | .006   | .010 | 0.05         | 0.15  | 0.25  |  |

| Foot Length              | L        | .018 | .024   | .030 | 0.45         | 0.60  | 0.75  |  |

| Footprint (Reference)    | (F)      |      | .039   |      |              | 1.00  |       |  |

| Foot Angle               | ¢        | 0    | 3.5    | 7    | 0            | 3.5   | 7     |  |

| Overall Width            | Е        | .463 | .472   | .482 | 11.75        | 12.00 | 12.25 |  |

| Overall Length           | D        | .463 | .472   | .482 | 11.75        | 12.00 | 12.25 |  |

| Molded Package Width     | E1       | .390 | .394   | .398 | 9.90         | 10.00 | 10.10 |  |

| Molded Package Length    | D1       | .390 | .394   | .398 | 9.90         | 10.00 | 10.10 |  |

| Lead Thickness           | С        | .005 | .007   | .009 | 0.13         | 0.18  | 0.23  |  |

| Lead Width               | В        | .007 | .009   | .011 | 0.17         | 0.22  | 0.27  |  |

| Pin 1 Corner Chamfer     | СН       | .025 | .035   | .045 | 0.64         | 0.89  | 1.14  |  |

| Mold Draft Angle Top     | α        | 5    | 10     | 15   | 5            | 10    | 15    |  |

| Mold Draft Angle Bottom  | β        | 5    | 10     | 15   | 5            | 10    | 15    |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-026

Drawing No. C04-085

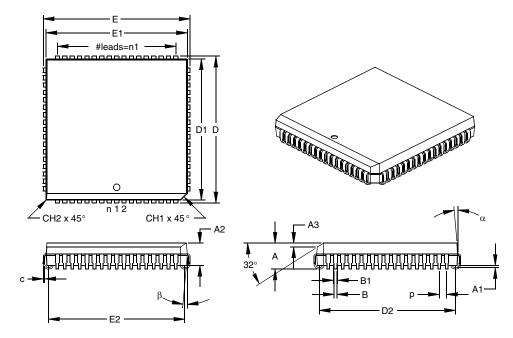

#### 84-Lead Plastic Leaded Chip Carrier (L) – Square (PLCC)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                          | Units     |      | INCHES* |      | Ν     | <b>IILLIMETERS</b> | 6     |

|--------------------------|-----------|------|---------|------|-------|--------------------|-------|

| Dimensi                  | on Limits | MIN  | NOM     | MAX  | MIN   | NOM                | MAX   |

| Number of Pins           | n         |      | 68      |      |       | 68                 |       |

| Pitch                    | р         |      | .050    |      |       | 1.27               |       |

| Pins per Side            | n1        |      | 17      |      |       | 17                 |       |

| Overall Height           | Α         | .165 | .173    | .180 | 4.19  | 4.39               | 4.57  |

| Molded Package Thickness | A2        | .145 | .153    | .160 | 3.68  | 3.87               | 4.06  |

| Standoff §               | A1        | .020 | .028    | .035 | 0.51  | 0.71               | 0.89  |

| Side 1 Chamfer Height    | A3        | .024 | .029    | .034 | 0.61  | 0.74               | 0.86  |

| Corner Chamfer 1         | CH1       | .040 | .045    | .050 | 1.02  | 1.14               | 1.27  |

| Corner Chamfer (others)  | CH2       | .000 | .005    | .010 | 0.00  | 0.13               | 0.25  |

| Overall Width            | E         | .985 | .990    | .995 | 25.02 | 25.15              | 25.27 |

| Overall Length           | D         | .985 | .990    | .995 | 25.02 | 25.15              | 25.27 |

| Molded Package Width     | E1        | .950 | .954    | .958 | 24.13 | 24.23              | 24.33 |

| Molded Package Length    | D1        | .950 | .954    | .958 | 24.13 | 24.23              | 24.33 |

| Footprint Width          | E2        | .890 | .920    | .930 | 22.61 | 23.37              | 23.62 |

| Footprint Length         | D2        | .890 | .920    | .930 | 22.61 | 23.37              | 23.62 |

| Lead Thickness           | С         | .008 | .011    | .013 | 0.20  | 0.27               | 0.33  |

| Upper Lead Width         | B1        | .026 | .029    | .032 | 0.66  | 0.74               | 0.81  |

| Lower Lead Width         | В         | .013 | .020    | .021 | 0.33  | 0.51               | 0.53  |

| Mold Draft Angle Top     | α         | 0    | 5       | 10   | 0     | 5                  | 10    |

| Mold Draft Angle Bottom  | β         | 0    | 5       | 10   | 0     | 5                  | 10    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-047 Drawing No. C04-093