Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 33MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 50                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 902 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 68-LCC (J-Lead)                                                             |

| Supplier Device Package    | 68-PLCC (24.23x24.23)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c756at-33i-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 5.0 RESET

The PIC17CXXX differentiates between various kinds of RESET:

- Power-on Reset (POR)

- Brown-out Reset

- MCLR Reset

- WDT Reset

Some registers are not affected in any RESET condition, their status is unknown on POR and unchanged in any other RESET. Most other registers are forced to a "RESET state". The TO and PD bits are set or cleared differently in different RESET situations, as indicated in Table 5-3. These bits, in conjunction with the POR and BOR bits, are used in software to determine the nature of the RESET. See Table 5-4 for a full description of the RESET states of all registers.

When the device enters the "RESET state", the Data Direction registers (DDR) are forced set, which will make the I/O hi-impedance inputs. The RESET state of some peripheral modules may force the I/O to other operations, such as analog inputs or the system bus.

**Note:** While the device is in a RESET state, the internal phase clock is held in the Q1 state. Any processor mode that allows external execution will force the RE0/ALE pin as a low output and the RE1/OE and RE2/WR pins as high outputs.

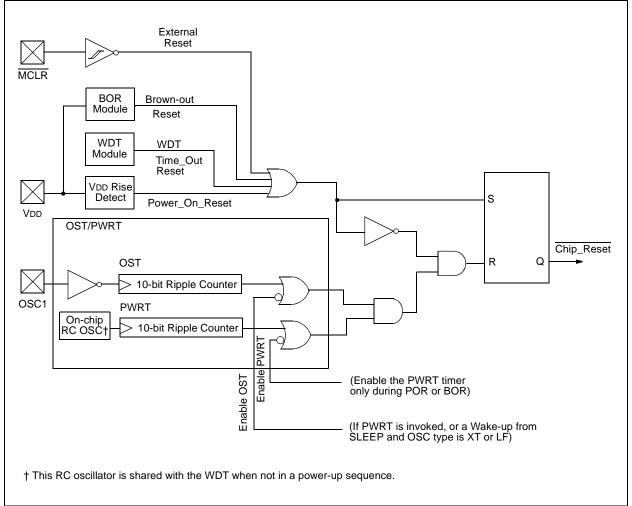

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 5-1.

# FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

# 5.1.5 BROWN-OUT RESET (BOR)

PIC17C7XX devices have on-chip Brown-out Reset circuitry. This circuitry places the device into a RESET when the device voltage falls below a trip point (BVDD). This ensures that the device does not continue program execution outside the valid operation range of the device. Brown-out Resets are typically used in AC line applications, or large battery applications, where large loads may be switched in (such as automotive).

| Note: | Before using the on-chip Brown-out for a |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|

|       | voltage supervisory function, please     |  |  |  |  |  |  |

|       | review the electrical specifications to  |  |  |  |  |  |  |

|       | ensure that they meet your requirements. |  |  |  |  |  |  |

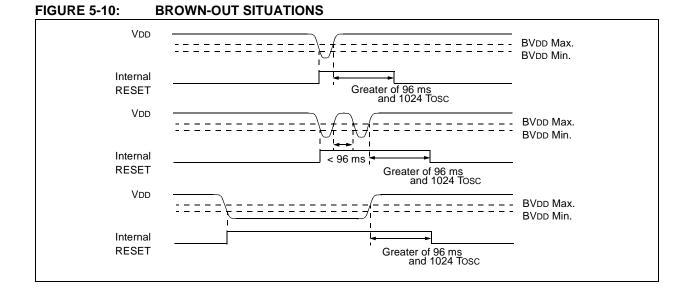

The BODEN configuration bit can disable (if clear/ programmed), or enable (if set) the Brown-out Reset circuitry. If VDD falls below BVDD (typically 4.0 V, paramter #D005 in electrical specification section), for greater than parameter #35, the Brown-out situation will reset the chip. A RESET is not guaranteed to occur if VDD falls below BVDD for less than paramter #35. The chip will remain in Brown-out Reset until VDD rises above BVDD. The Power-up Timer and Oscillator Startup Timer will then be invoked. This will keep the chip in RESET the greater of 96 ms and 1024 Tosc. If VDD drops below BVDD while the Power-up Timer/Oscillator Start-up Timer is running, the chip will go back into a Brown-out Reset. The Power-up Timer/Oscillator Startup Timer will be initialized. Once VDD rises above BVDD, the Power-up Timer/Oscillator Start-up Timer will start their time delays. Figure 5-10 shows typical Brown-out situations.

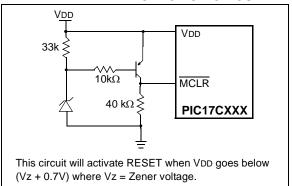

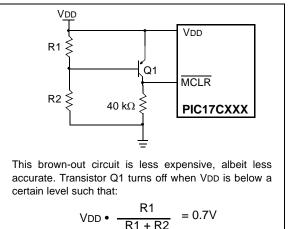

In some applications, the Brown-out Reset trip point of the device may not be at the desired level. Figure 5-8 and Figure 5-9 are two examples of external circuitry that may be implemented. Each needs to be evaluated to determine if they match the requirements of the application.

#### EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

FIGURE 5-9:

#### EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

© 1998-2013 Microchip Technology Inc.

# PIC17C7XX

NOTES:

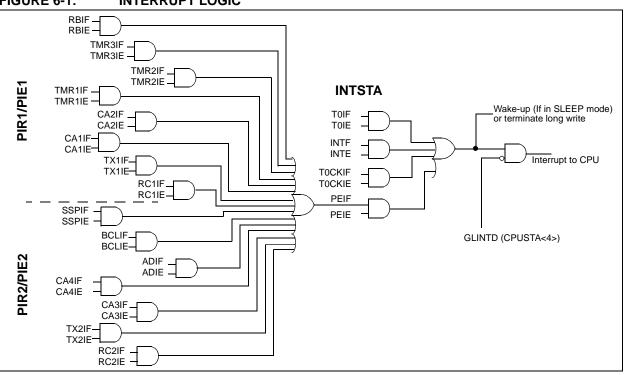

# 6.0 INTERRUPTS

PIC17C7XX devices have 18 sources of interrupt:

- External interrupt from the RA0/INT pin

- Change on RB7:RB0 pins

- TMR0 Overflow

- TMR1 Overflow

- TMR2 Overflow

- TMR3 Overflow

- USART1 Transmit buffer empty

- USART1 Receive buffer full

- USART2 Transmit buffer empty

- USART2 Receive buffer full

- SSP Interrupt

- SSP I<sup>2</sup>C bus collision interrupt

- A/D conversion complete

- Capture1

- Capture2

- Capture3

- Capture4

- T0CKI edge occurred

There are six registers used in the control and status of interrupts. These are:

- CPUSTA

- INTSTA

- PIE1

- PIR1

- PIE2

- PIR2

The CPUSTA register contains the GLINTD bit. This is the Global Interrupt Disable bit. When this bit is set, all interrupts are disabled. This bit is part of the controller core functionality and is described in the Section 6.4.

FIGURE 6-1: INTERRUPT LOGIC

When an interrupt is responded to, the GLINTD bit is automatically set to disable any further interrupts, the return address is pushed onto the stack and the PC is loaded with the interrupt vector address. There are four interrupt vectors. Each vector address is for a specific interrupt source (except the peripheral interrupts, which all vector to the same address). These sources are:

- External interrupt from the RA0/INT pin

- TMR0 Overflow

- T0CKI edge occurred

- Any peripheral interrupt

When program execution vectors to one of these interrupt vector addresses (except for the peripheral interrupts), the interrupt flag bit is automatically cleared. Vectoring to the peripheral interrupt vector address does not automatically clear the source of the interrupt. In the peripheral Interrupt Service Routine, the source(s) of the interrupt can be determined by testing the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid infinite interrupt requests.

When an interrupt condition is met, that individual interrupt flag bit will be set, regardless of the status of its corresponding mask bit or the GLINTD bit.

For external interrupt events, there will be an interrupt latency. For two-cycle instructions, the latency could be one instruction cycle longer.

The "return from interrupt" instruction, RETFIE, can be used to mark the end of the Interrupt Service Routine. When this instruction is executed, the stack is "POPed" and the GLINTD bit is cleared (to re-enable interrupts).

### TABLE 7-1: MODE MEMORY ACCESS

| Operating<br>Mode            | Internal<br>Program<br>Memory | Configuration Bits,<br>Test Memory,<br>Boot ROM |  |

|------------------------------|-------------------------------|-------------------------------------------------|--|

| Microprocessor               | No Access                     | No Access                                       |  |

| Microcontroller              | Access                        | Access                                          |  |

| Extended<br>Microcontroller  | Access                        | No Access                                       |  |

| Protected<br>Microcontroller | Access                        | Access                                          |  |

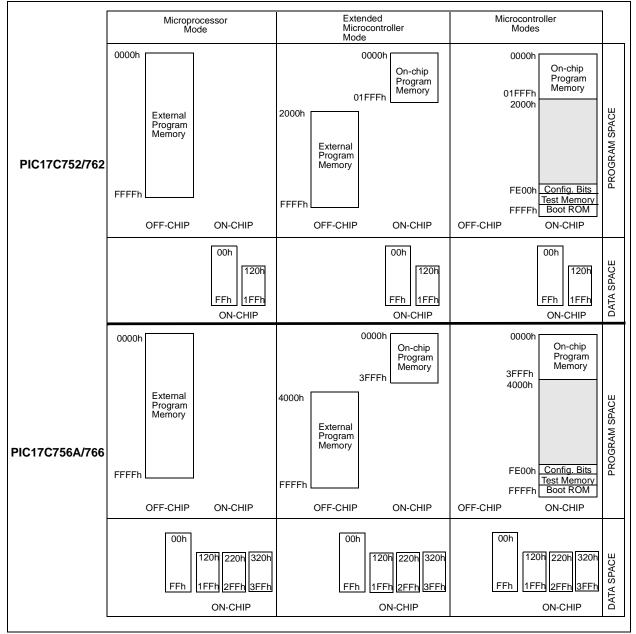

The PIC17C7XX can operate in modes where the program memory is off-chip. They are the Microprocessor and Extended Microcontroller modes. The Microprocessor mode is the default for an unprogrammed device.

Regardless of the processor mode, data memory is always on-chip.

### FIGURE 7-2: MEMORY MAP IN DIFFERENT MODES

Bank 8<sup>(1,4)</sup>

DDRH PORTH

DDRJ

PORTJ

\_

\_

\_

\_

#### FIGURE 7-5: PIC17C7XX REGISTER FILE MAP

| Addr | Unbanked              |                       |                       |                         |      |

|------|-----------------------|-----------------------|-----------------------|-------------------------|------|

| 00h  | INDF0                 |                       |                       |                         |      |

| 01h  | FSR0                  |                       |                       |                         |      |

| 02h  | PCL                   |                       |                       |                         |      |

| 03h  | PCLATH                |                       |                       |                         |      |

| 04h  | ALUSTA                |                       |                       |                         |      |

| 05h  | TOSTA                 |                       |                       |                         |      |

| 06h  | CPUSTA                |                       |                       |                         |      |

| 07h  | INTSTA                |                       |                       |                         |      |

| 08h  | INDF1                 |                       |                       |                         |      |

| 09h  | FSR1                  |                       |                       |                         |      |

| 0Ah  | WREG                  |                       |                       |                         |      |

| 0Bh  | TMR0L                 |                       |                       |                         |      |

| 0Ch  | TMR0H                 |                       |                       |                         |      |

| 0Dh  | TBLPTRL               |                       |                       |                         |      |

| 0Eh  | TBLPTRH               |                       |                       |                         |      |

| 0Fh  | BSR                   |                       |                       |                         |      |

|      | Bank 0                | Bank 1 <sup>(1)</sup> | Bank 2 <sup>(1)</sup> | Bank 3 <sup>(1)</sup>   | Bank |

| 10h  | PORTA                 | DDRC                  | TMR1                  | PW1DCL                  | PIR  |

| 11h  | DDRB                  | PORTC                 | TMR2                  | PW2DCL                  | PIE  |

| 12h  | PORTB                 | DDRD                  | TMR3L                 | PW1DCH                  | —    |

| 13h  | RCSTA1                | PORTD                 | TMR3H                 | PW2DCH                  | RCST |

| 14h  | RCREG1                | DDRE                  | PR1                   | CA2L                    | RCRE |

| 15h  | TXSTA1                | PORTE                 | PR2                   | CA2H                    | TXST |

| 16h  | TXREG1                | PIR1                  | PR3L/CA1L             | TCON1                   | TXRE |

| 17h  | SPBRG1                | PIE1                  | PR3H/CA1H             | TCON2                   | SPBR |

|      | Unbanked              |                       |                       |                         |      |

| 18h  | PRODL                 |                       |                       |                         |      |

| 19h  | PRODH                 |                       |                       |                         |      |

| 1Ah  | General               |                       |                       |                         |      |

|      | Purpose               |                       |                       |                         |      |

| 1Fh  | RAM                   |                       | 1                     |                         | 1    |

|      | Bank 0 <sup>(2)</sup> | Bank 1 <sup>(2)</sup> | Bank 2 <sup>(2)</sup> | Bank 3 <sup>(2,3)</sup> |      |

| 20h  |                       |                       |                       |                         | 1    |

|      | General               | General               | General               | General                 |      |

|      | Purpose               | Purpose               | Purpose               | Purpose                 |      |

|      | RAM                   | RAM                   | RAM                   | RAM                     |      |

|      |                       |                       |                       |                         |      |

| FFh  |                       |                       |                       |                         |      |

Note 1: SFR file locations 10h - 17h are banked. The lower nibble of the BSR specifies the bank. All unbanked SFRs ignore the Bank Select Register (BSR) bits.

2: General Purpose Registers (GPR) locations 20h - FFh, 120h - 1FFh, 220h - 2FFh, and 320h - 3FFh are banked. The upper nibble of the BSR specifies this bank. All other GPRs ignore the Bank Select Register (BSR) bits.

Bank 5<sup>(1)</sup>

DDRF

PORTF

DDRG

PORTG

ADCON0

ADCON1

ADRESL

ADRESH

Bank 6<sup>(1)</sup>

SSPADD

SSPCON1

SSPCON2

SSPSTAT

SSPBUF

\_

\_

\_

Bank 7<sup>(1)</sup>

PW3DCL

PW3DCH

CA3L

CA3H

CA4L

CA4H

TCON3

\_

3: RAM bank 3 is not implemented on the PIC17C752 and the PIC17C762. Reading any unimplemented register reads '0's.

4: Bank 8 is only implemented on the PIC17C76X devices.

| Address            | Name                   | Bit 7              | Bit 6          | Bit 5                   | Bit 4           | Bit 3           | Bit 2          | Bit 1        | Bit 0        | Value on<br>POR,<br>BOR | MCLR,<br>WDT        |

|--------------------|------------------------|--------------------|----------------|-------------------------|-----------------|-----------------|----------------|--------------|--------------|-------------------------|---------------------|

| Unbanke            | ed                     |                    |                |                         |                 |                 |                |              |              |                         |                     |

| 00h                | INDF0                  | Uses conte         | ents of FSR    | 0 to address            | Data Memo       | ry (not a phy   | sical registe  | r)           |              |                         |                     |

| 01h                | FSR0                   | Indirect Da        | ata Memory     | Address Poi             | nter 0          |                 |                |              |              | XXXX XXXX               | uuuu uuuu           |

| 02h                | PCL                    | Low order          | 8-bits of PC   | ;                       |                 |                 |                |              |              | 0000 0000               | 0000 0000           |

| 03h <sup>(1)</sup> | PCLATH                 | Holding Re         | egister for u  | pper 8-bits o           | f PC            |                 |                |              |              | 0000 0000               | uuuu uuuu           |

| 04h                | ALUSTA                 | FS3                | FS2            | FS1                     | FS0             | OV              | Z              | DC           | С            | 1111 xxxx               | 1111 uuuu           |

| 05h                | TOSTA                  | INTEDG             | T0SE           | TOCS                    | T0PS3           | T0PS2           | T0PS1          | T0PS0        |              | 0000 000-               | 0000 000-           |

| 06h <sup>(2)</sup> | CPUSTA                 |                    | _              | STKAV                   | GLINTD          | TO              | PD             | POR          | BOR          | 11 11qq                 | 11 qqui             |

| 07h                | INTSTA                 | PEIF               | T0CKIF         | T0IF                    | INTF            | PEIE            | TOCKIE         | T0IE         | INTE         | 0000 0000               | 0000 0000           |

| 08h                | INDF1                  | Uses conte         | ents of FSR    | 1 to address            | Data Memo       | ry (not a phy   | sical registe  | r)           |              |                         |                     |

| 09h                | FSR1                   | Indirect Da        | ata Memory     | Address Poi             | nter 1          |                 | -              |              |              | XXXX XXXX               | uuuu uuuu           |

| 0Ah                | WREG                   | Working R          | egister        |                         |                 |                 |                |              |              | XXXX XXXX               | uuuu uuuu           |

| 0Bh                | TMR0L                  | TMR0 Reg           | gister; Low E  | Byte                    |                 |                 |                |              |              | XXXX XXXX               | uuuu uuuu           |

| 0Ch                | TMR0H                  | TMR0 Reg           | jister; High I | Byte                    |                 |                 |                |              |              | XXXX XXXX               | uuuu uuuu           |

| 0Dh                | TBLPTRL                | Low Byte of        | of Program     | Memory Tab              | le Pointer      |                 |                |              |              | 0000 0000               | 0000 0000           |

| 0Eh                | TBLPTRH                | High Byte          | of Program     | Memory Tab              | le Pointer      |                 |                |              |              | 0000 0000               | 0000 0000           |

| 0Fh                | BSR                    | Bank Sele          | ct Register    |                         |                 |                 |                |              |              | 0000 0000               | 0000 0000           |

| Bank 0             | •                      |                    |                |                         |                 |                 |                |              |              | •                       |                     |

| 10h                | PORTA <sup>(4,6)</sup> | RBPU               | —              | RA5/TX1/<br>CK1         | RA4/RX1/<br>DT1 | RA3/SDI/<br>SDA | RA2/SS/<br>SCL | RA1/T0CKI    | RA0/INT      | 0-xx 11xx               | 0-uu 11uu           |

| 11h                | DDRB                   | Data Direc         | tion Registe   | er for PORTE            | 3               |                 |                |              |              | 1111 1111               | 1111 1111           |

| 12h                | PORTB <sup>(4)</sup>   | RB7/               | RB6/           | RB5/                    | RB4/            | RB3/            | RB2/           | RB1/         | RB0/         | xxxx xxxx               | uuuu uuuu           |

| 13h                | RCSTA1                 | SDO<br>SPEN        | SCK<br>RX9     | TCLK3<br>SREN           | TCLK12<br>CREN  | PWM2            | PWM1<br>FERR   | CAP2<br>OERR | CAP1<br>RX9D | 0000 -00x               | 0000 -000           |

| 13h                | RCREG1                 | -                  | Receive Re     |                         | CREN            | _               | FERR           | OEKK         | KA9D         |                         |                     |

| 140<br>15h         | TXSTA1                 | CSRC               | TX9            | TXEN                    | SYNC            |                 |                | TRMT         | TX9D         | xxxx xxxx<br>00001x     | uuuu uuuu<br>00001u |

| 16h                | TXREG1                 |                    | -              | egister (for L          |                 | _               | _              |              | 1 Yan        | xxxx xxxx               | uuuu uuuu           |

| 17h                | SPBRG1                 |                    |                | Register (for           | ,               |                 |                |              |              | 0000 0000               | 0000 0000           |

| Bank 1             | SFBRGT                 | Dauu Nale          | Generator      |                         | USARTI)         |                 |                |              |              | 0000 0000               | 0000 0000           |

|                    | DDRC <sup>(5)</sup>    | Data Direa         | tion Desists   |                         | <b>`</b>        |                 |                |              |              |                         |                     |

| 10h<br>11h         | PORTC <sup>(4,5)</sup> |                    | 0              | er for PORTC<br>RC5/AD5 | ,<br>RC4/AD4    | RC3/AD3         | RC2/AD2        | RC1/AD1      | RC0/AD0      | 1111 1111               | 1111 1111           |

|                    | DDRD <sup>(5)</sup>    |                    |                |                         |                 | RC3/AD3         | RUZ/ADZ        | RC1/AD1      | RCU/ADU      | XXXX XXXX               | uuuu uuuu           |

| 12h                |                        | Data Direc<br>RD7/ | RD6/           | er for PORTE<br>RD5/    | RD4/            | RD3/            | RD2/           |              | [            | 1111 1111               | 1111 1111           |

| 13h                | PORTD <sup>(4,5)</sup> | AD15               | AD14           | AD13                    | AD12            | AD11            | AD10           | RD1/AD9      | RD0/AD8      | xxxx xxxx               | սսսս սսսս           |

| 14h                | DDRE <sup>(5)</sup>    | Data Direc         | tion Registe   | er for PORTE            |                 |                 |                |              |              | 1111                    | 1112                |

| 15h                | PORTE <sup>(4,5)</sup> | -                  | —              | —                       | —               | RE3/<br>CAP4    | RE2/WR         | RE1/OE       | RE0/ALE      | xxxx                    | uuui                |

| 16h                | PIR1                   | RBIF               | TMR3IF         | TMR2IF                  | TMR1IF          | CA2IF           | CA1IF          | TX1IF        | RC1IF        | x000 0010               | u000 001            |

| 17h                | PIE1                   | RBIE               | TMR3IE         | TMR2IE                  | TMR1IE          | CA2IE           | CA1IE          | TX1IE        | RC1IE        | 0000 0000               | 0000 0000           |

#### TABLE 7-3: SPECIAL FUNCTION REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0', q = value depends on condition.

Shaded cells are unimplemented, read as '0'.

**Note** 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<15:8> whose contents are updated from, or transferred to, the upper byte of the program counter.

2: The TO and PD status bits in CPUSTA are not affected by a MCLR Reset.

3: Bank 8 and associated registers are only implemented on the PIC17C76X devices.

4: This is the value that will be in the port output latch.

5: When the device is configured for Microprocessor or Extended Microcontroller mode, the operation of this port does not rely on these registers.

6: On any device RESET, these pins are configured as inputs.

### 7.2.2.3 TMR0 Status/Control Register (T0STA)

This register contains various control bits. Bit7 (INTEDG) is used to control the edge upon which a signal on the RA0/INT pin will set the RA0/INT interrupt flag. The other bits configure Timer0, it's prescaler and clock source.

# REGISTER 7-3: T0STA REGISTER (ADDRESS: 05h, UNBANKED)

| R/W-0                                         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 |  |  |

|-----------------------------------------------|-------|-------|-------|-------|-------|-------|-----|--|--|

| INTEDG                                        | T0SE  | T0CS  | T0PS3 | T0PS2 | T0PS1 | T0PS0 |     |  |  |

| bit 7                                         |       |       |       |       |       |       |     |  |  |

|                                               |       |       |       |       |       |       |     |  |  |

| INTEDG: RA0/INT Pin Interrupt Edge Select bit |       |       |       |       |       |       |     |  |  |

| bit 7<br>bit 6 | This bit selects<br>1 = Rising edge<br>0 = Falling edge<br><b>T0SE</b> : Timer0 E | <b>TEDG</b> : RA0/INT Pin Interrupt Edge Select bit<br>is bit selects the edge upon which the interrupt is detected.<br>e Rising edge of RA0/INT pin generates interrupt<br>= Falling edge of RA0/INT pin generates interrupt<br><b>SE</b> : Timer0 External Clock Input Edge Select bit<br>is bit selects the edge upon which TMR0 will increment. |  |  |  |  |  |

|----------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                | 1 = Rising edge                                                                   | <u>) (External Clock):</u><br>of RA1/T0CKI pin increments TMR0 and/or sets the T0CKIF bit<br>of RA1/T0CKI pin increments TMR0 and/or sets a T0CKIF bit                                                                                                                                                                                              |  |  |  |  |  |

|                | <u>When T0CS = 1</u><br>Don't care                                                | I (Internal Clock):                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| bit 5          | This bit selects<br>1 = Internal inst                                             | Clock Source Select bit<br>the clock source for Timer0.<br>ruction clock cycle (TcY)<br>ck input on the T0CKI pin                                                                                                                                                                                                                                   |  |  |  |  |  |

| bit 4-1        |                                                                                   | Timer0 Prescale Selection bits<br>ct the prescale value for Timer0.                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|                | T0PS3:T0PS0                                                                       | Prescale Value                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|                | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1xxx              | 1:1<br>1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

bit 0

Unimplemented: Read as '0'

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR Reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

Example 9-3 shows the sequence to do a 16 x 16 unsigned multiply. Equation 9-1 shows the algorithm that is used. The 32-bit result is stored in 4 registers, RES3:RES0.

#### EQUATION 9-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| -         |   |                                        |      |

|-----------|---|----------------------------------------|------|

| RES3:RES0 | = | ARG1H:ARG1L • ARG2H:AF                 | RG2L |

|           | = | $(ARG1H \bullet ARG2H \bullet 2^{16})$ | +    |

|           |   | $(ARG1H \bullet ARG2L \bullet 2^8)$    | +    |

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8)$    | +    |

|           |   | $(ARG1L \bullet ARG2L)$                |      |

|           |   |                                        |      |

#### EXAMPLE 9-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVFP  | ARG1L, WREG |   |                  |

|---|--------|-------------|---|------------------|

|   | MULWF  | ARG2L       | ; | ARG1L * ARG2L -> |

|   |        |             | ; | PRODH: PRODL     |

|   | MOVPF  | PRODH, RES1 | ; |                  |

|   | MOVPF  | PRODL, RESO | ; |                  |

| ; |        |             |   |                  |

|   | MOVFP  | ARG1H, WREG |   |                  |

|   | MULWF  | ARG2H       | ; | ARG1H * ARG2H -> |

|   |        |             | ; | PRODH: PRODL     |

|   | MOVPF  | PRODH, RES3 | ; |                  |

|   | MOVPF  | PRODL, RES2 | ; |                  |

| ; |        |             |   |                  |

|   | MOVFP  | -           |   |                  |

|   | MULWF  | ARG2H       |   | ARG1L * ARG2H -> |

|   |        |             |   | PRODH:PRODL      |

|   | MOVFP  | PRODL, WREG |   |                  |

|   | ADDWF  | ,           |   |                  |

|   |        | PRODH, WREG | ; | products         |

|   | ADDWFC |             | ; |                  |

|   |        | WREG, F     |   |                  |

|   | ADDWFC | RES3, F     | ; |                  |

| ; |        |             |   |                  |

|   | MOVFP  | •           |   |                  |

|   | MULWF  | ARG2L       |   | ARG1H * ARG2L -> |

|   |        |             |   | PRODH: PRODL     |

|   | MOVFP  | PRODL, WREG |   |                  |

|   | ADDWF  |             |   |                  |

|   |        | PRODH, WREG |   | products         |

|   |        | RES2, F     |   |                  |

|   |        | WREG, F     |   |                  |

|   | ADDWFC | RES3, F     | ; |                  |

|   |        |             |   |                  |

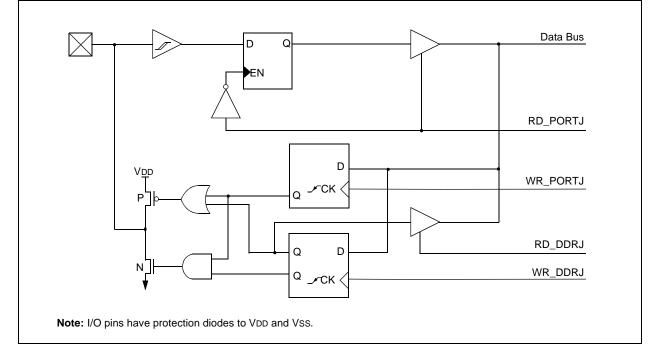

# 10.9 PORTJ and DDRJ Registers (PIC17C76X only)

PORTJ is an 8-bit wide, bi-directional port. The corresponding data direction register is DDRJ. A '1' in DDRJ configures the corresponding port pin as an input. A '0' in the DDRJ register configures the corresponding port pin as an output. Reading PORTJ reads the status of the pins, whereas writing to PORTJ will write to the respective port latch.

PORTJ is a general purpose I/O port.

#### EXAMPLE 10-9: INITIALIZING PORTJ

| MOVLB | 8      | ;  | Select Bank 8            |

|-------|--------|----|--------------------------|

| CLRF  | PORTJ, | F; | Initialize PORTJ data    |

|       |        | ;  | latches before setting   |

|       |        | ;  | the data direction       |

|       |        | ;  | register                 |

| MOVLW | 0xCF   | ;  | Value used to initialize |

|       |        | ;  | data direction           |

| MOVWF | DDRJ   | ;  | Set RJ<3:0> as inputs    |

|       |        | ;  | RJ<5:4> as outputs       |

|       |        | ;  | RJ<7:6> as inputs        |

|       |        |    |                          |

# 10.10 I/O Programming Considerations

#### 10.10.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read, followed by a write operation. For example, the BCF and BSF instructions read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB, will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g. bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Reading a port reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (BCF, BSF, BTG, etc.) on a port, the value of the port pins is read, the desired operation is performed with this value and the value is then written to the port latch.

Example 10-10 shows the possible effect of two sequential read-modify-write instructions on an I/O port.

# EXAMPLE 10-10: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

| <pre>; Initial PORT sett ; ; PORTB&lt;7:6&gt; have p ; not connected to</pre> | PORTB<3:0<br>ull-ups and are | )> Outputs             |

|-------------------------------------------------------------------------------|------------------------------|------------------------|

| ;<br>;<br>;                                                                   | PORT latch                   | PORT pins              |

| ,<br>BCF PORTB, 7<br>BCF PORTB, 6                                             | ; 10pp pppp                  |                        |

| BCF DDRB, 7<br>BCF DDRB, 6<br>;                                               | ; 10pp pppp<br>; 10pp pppp   | 11pp pppp<br>10pp pppp |

| ; Note that the use<br>; pin values to be<br>; caused RB7 to be<br>; (High).  | 00pp pppp. The               | 2nd BCF                |

**Note:** A pin actively outputting a Low or High should not be driven from external devices, in order to change the level on this pin (i.e., "wired-or", "wired-and"). The resulting high output currents may damage the device.

# PIC17C7XX

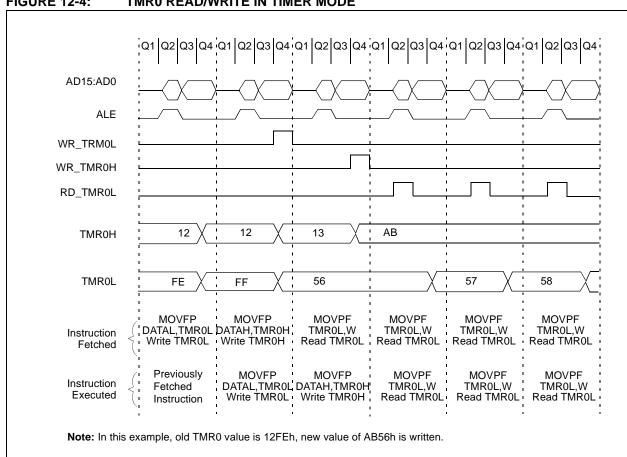

#### FIGURE 12-4: **TMR0 READ/WRITE IN TIMER MODE**

#### **TABLE 12-1: REGISTERS/BITS ASSOCIATED WITH TIMER0**

| Address       | Name                               | Bit 7  | Bit 6  | Bit 5 | Bit 4  | Bit 3 | Bit 2     | Bit 1     | Bit 0 | Value on<br>POR,<br>BOR | MCLR, WDT |

|---------------|------------------------------------|--------|--------|-------|--------|-------|-----------|-----------|-------|-------------------------|-----------|

| 05h, Unbanked | TOSTA                              | INTEDG | TOSE   | TOCS  | T0PS3  | T0PS2 | T0PS1     | T0PS0     | —     | 0000 000-               | 0000 000- |

| 06h, Unbanked | CPUSTA                             | -      | -      | STKAV | GLINTD | TO    | PD        | POR       | BOR   | 11 11qq                 | 11 qquu   |

| 07h, Unbanked | INTSTA                             | PEIF   | TOCKIF | T0IF  | INTF   | PEIE  | TOCKIE    | TOIE      | INTE  | 0000 0000               | 0000 0000 |

| 0Bh, Unbanked | nked TMR0L TMR0 Register; Low Byte |        |        |       |        |       | xxxx xxxx | uuuu uuuu |       |                         |           |

| 0Ch, Unbanked | TMR0H TMR0 Register; High Byte     |        |        |       |        |       | xxxx xxxx | uuuu uuuu |       |                         |           |

Legend: x = unknown, u = unchanged, - = unimplemented, read as a '0', q = value depends on condition. Shaded cells are not used by Timer0.

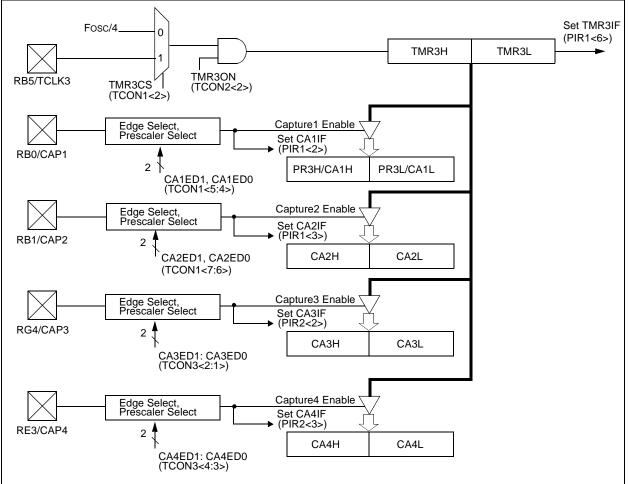

## 13.2.2 FOUR CAPTURE MODE

This mode is selected by setting bit CA1/PR3. A block diagram is shown in Figure 13-6. In this mode, TMR3 runs without a period register and increments from 0000h to FFFFh and rolls over to 0000h. The TMR3 interrupt Flag (TMR3IF) is set on this rollover. The TMR3IF bit must be cleared in software.

Registers PR3H/CA1H and PR3L/CA1L make a 16-bit capture register (Capture1). It captures events on pin RB0/CAP1. Capture mode is configured by the CA1ED1 and CA1ED0 bits. Capture1 Interrupt Flag bit (CA1IF) is set upon detection of the capture event. The corresponding interrupt mask bit is CA1IE. The Capture1 Overflow Status bit is CA1OVF.

All the captures operate in the same manner. Refer to Section 13.2.1 for the operation of capture.

### FIGURE 13-6: TIMER3 WITH FOUR CAPTURES BLOCK DIAGRAM

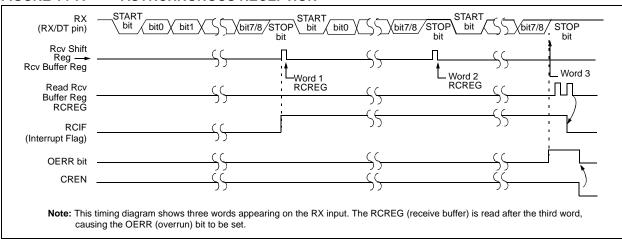

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the RCIE bit.

- 4. If 9-bit reception is desired, then set the RX9 bit.

- 5. Enable the reception by setting the CREN bit.

- 6. The RCIF bit will be set when reception completes and an interrupt will be generated if the RCIE bit was set.

- 7. Read RCSTA to get the ninth bit (if enabled) and FERR bit to determine if any error occurred during reception.

- 8. Read RCREG for the 8-bit received data.

- 9. If an overrun error occurred, clear the error by clearing the OERR bit.

- Note: To terminate a reception, either clear the SREN and CREN bits, or the SPEN bit. This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

## FIGURE 14-7: ASYNCHRONOUS RECEPTION

## TABLE 14-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address     | Name   | Bit 7     | Bit 6    | Bit 5      | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | MCLR, WDT |

|-------------|--------|-----------|----------|------------|--------|-------|-------|-------|-------|-------------------------|-----------|

| 16h, Bank 1 | PIR1   | RBIF      | TMR3IF   | TMR2IF     | TMR1IF | CA2IF | CA1IF | TX1IF | RC1IF | x000 0010               | u000 0010 |

| 17h, Bank 1 | PIE1   | RBIE      | TMR3IE   | TMR2IE     | TMR1IE | CA2IE | CA1IE | TX1IE | RC1IE | 0000 0000               | 0000 0000 |

| 13h, Bank 0 | RCSTA1 | SPEN      | RX9      | SREN       | CREN   |       | FERR  | OERR  | RX9D  | 0000 - 00x              | 0000 -00u |

| 14h, Bank 0 | RCREG1 | RX7       | RX6      | RX5        | RX4    | RX3   | RX2   | RX1   | RX0   | xxxx xxxx               | uuuu uuuu |

| 15h, Bank 0 | TXSTA1 | CSRC      | TX9      | TXEN       | SYNC   | _     | —     | TRMT  | TX9D  | 00001x                  | 00001u    |

| 17h, Bank 0 | SPBRG1 | Baud Rate | Generato | r Register |        |       |       |       | •     | 0000 0000               | 0000 0000 |

| 10h, Bank 4 | PIR2   | SSPIF     | BCLIF    | ADIF       | —      | CA4IF | CA3IF | TX2IF | RC2IF | 000- 0010               | 000- 0010 |

| 11h, Bank 4 | PIE2   | SSPIE     | BCLIE    | ADIE       | _      | CA4IE | CA3IE | TX2IE | RC2IE | 000- 0000               | 000- 0000 |

| 13h, Bank 4 | RCSTA2 | SPEN      | RX9      | SREN       | CREN   | _     | FERR  | OERR  | RX9D  | x00-000x                | 0000 -00u |

| 14h, Bank 4 | RCREG2 | RX7       | RX6      | RX5        | RX4    | RX3   | RX2   | RX1   | RX0   | xxxx xxxx               | uuuu uuuu |

| 15h, Bank 4 | TXSTA2 | CSRC      | TX9      | TXEN       | SYNC   |       | —     | TRMT  | TX9D  | 00001x                  | 00001u    |

| 17h, Bank 4 | SPBRG2 | Baud Rate | Generato | r Register |        |       |       |       |       | 0000 0000               | 0000 0000 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as a '0'. Shaded cells are not used for asynchronous reception.

#### REGISTER 15-2: SSPCON1: SYNC SERIAL PORT CONTROL REGISTER1 (ADDRESS 11h, BANK 6)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WCOL  | SSPOV | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7 WCOL: Write Collision Detect bit

Master mode:

1 = A write to the SSPBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started

0 = No collision

<u>Slave mode:</u>

1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)

0 = No collision

bit 6

SSPOV: Receive Overflow Indicator bit

In SPI mode:

- 1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in Slave mode. In Slave mode, the user must read the SSPBUF, even if only transmitting data, to avoid setting overflow. In Master mode, the overflow bit is not set, since each new reception (and transmission) is initiated by writing to the SSPBUF register. (Must be cleared in software.)

- 0 = No overflow

- In I<sup>2</sup>C mode:

- 1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit mode. (Must be cleared in software.)

- 0 = No overflow

bit 5 SSPEN: Synchronous Serial Port Enable bit

In both modes, when enabled, these pins must be properly configured as input or output.

In SPI mode:

1 = Enables serial port and configures SCK, SDO, SDI and  $\overline{SS}$  as the source of the serial port pins 0 = Disables serial port and configures these pins as I/O port pins

In I<sup>2</sup>C mode:

- 1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins 0 = Disables serial port and configures these pins as I/O port pins

- **Note:** In SPI mode, these pins must be properly configured as input or output.

bit 4 CKP: Clock Polarity Select bit

In SPI mode: 1 =Idle state for clock is a high level 0 =Idle state for clock is a low level

- In I<sup>2</sup>C Slave mode: SCK release control

- 1 = Enable clock

0 = Holds clock low (clock stretch). (Used to ensure data setup time.)

In I<sup>2</sup>C Master mode:

Unused in this mode

bit 3-0 SSPM3:SSPM0: Synchronous Serial Port Mode Select bits

- 0000 = SPI Master mode, clock = Fosc/4

- 0001 = SPI Master mode, clock = Fosc/16

- 0010 = SPI Master mode, clock = FOSC/64

- 0011 = SPI Master mode, clock = TMR2 output/2

- 0100 = SPI Slave mode, clock = SCK pin,  $\overline{SS}$  pin control enabled

- 0101 =SPI Slave mode, clock = SCK pin,  $\overline{SS}$  pin control disabled,  $\overline{SS}$  can be used as I/O pin

- $0110 = I^2C$  Slave mode, 7-bit address

- $0111 = I^2C$  Slave mode, 10-bit address

- 1000 = I<sup>2</sup>C Master mode, clock = Fosc / (4 \* (SSPADD+1))

- 1xx1 = Reserved

- lxlx = Reserved

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented I  | oit, read as '0'   |

| - n = Value at POR Reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# PIC17C7XX

| DCF                                               | SNZ                                                          | Decreme                                                                            | Decrement f, skip if not 0                                                                                                                                                                                                                                                                                                        |                                   |                        |  |  |  |

|---------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------|--|--|--|

| Synt                                              | ax:                                                          | [ <i>label</i> ] D                                                                 | [ <i>label</i> ] DCFSNZ f,d                                                                                                                                                                                                                                                                                                       |                                   |                        |  |  |  |

| Ope                                               | rands:                                                       | $0 \le f \le 25$<br>$d \in [0,1]$                                                  | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                   |                                   |                        |  |  |  |

| Ope                                               | ration:                                                      |                                                                                    | (f) $-1 \rightarrow$ (dest);<br>skip if not 0                                                                                                                                                                                                                                                                                     |                                   |                        |  |  |  |

| Statu                                             | us Affected:                                                 | None                                                                               |                                                                                                                                                                                                                                                                                                                                   |                                   |                        |  |  |  |

| Enco                                              | oding:                                                       | 0010                                                                               | 011d                                                                                                                                                                                                                                                                                                                              | ffff                              | ffff                   |  |  |  |

| Des                                               | cription:                                                    | mented. If<br>WREG. If<br>back in reg<br>If the resul<br>tion, which<br>carded and | The contents of register 'f' are decre-<br>mented. If 'd' is 0, the result is placed in<br>WREG. If 'd' is 1, the result is placed<br>back in register 'f'.<br>If the result is not 0, the next instruc-<br>tion, which is already fetched is dis-<br>carded and a NOP is executed instead,<br>making it a two-cycle instruction. |                                   |                        |  |  |  |

| Wor                                               | ds:                                                          | 1                                                                                  |                                                                                                                                                                                                                                                                                                                                   |                                   |                        |  |  |  |

| Cycl                                              | es:                                                          | 1(2)                                                                               | 1(2)                                                                                                                                                                                                                                                                                                                              |                                   |                        |  |  |  |

| QC                                                | vcle Activity:                                               |                                                                                    |                                                                                                                                                                                                                                                                                                                                   |                                   |                        |  |  |  |

|                                                   | Q1                                                           | Q2                                                                                 | Q                                                                                                                                                                                                                                                                                                                                 | 3                                 | Q4                     |  |  |  |

|                                                   | Decode                                                       | Read<br>register 'f'                                                               | Proce<br>Dat                                                                                                                                                                                                                                                                                                                      |                                   | Write to<br>estination |  |  |  |

| lf ski                                            | ip:                                                          |                                                                                    |                                                                                                                                                                                                                                                                                                                                   |                                   |                        |  |  |  |

|                                                   | Q1                                                           | Q2                                                                                 | Q                                                                                                                                                                                                                                                                                                                                 | 3                                 | Q4                     |  |  |  |

|                                                   | No<br>operation                                              | No<br>operation                                                                    | No<br>opera                                                                                                                                                                                                                                                                                                                       |                                   | No<br>peration         |  |  |  |

| Example: HERE DCFSNZ TEMP, 1<br>ZERO :<br>NZERO : |                                                              |                                                                                    |                                                                                                                                                                                                                                                                                                                                   |                                   | 1                      |  |  |  |

|                                                   | Before Instru<br>TEMP_V                                      |                                                                                    | ?                                                                                                                                                                                                                                                                                                                                 |                                   |                        |  |  |  |

|                                                   | After Instruct<br>TEMP_V<br>If TEMP_<br>PC<br>If TEMP_<br>PC | ALUE =<br>VALUE =<br>=                                                             | 0;<br>Addre<br>0;                                                                                                                                                                                                                                                                                                                 | P_VALUE<br>ess (zero<br>ess (nzer | )                      |  |  |  |

| GOT   | ю                                                                                                                                                                                                                                                                     | Uncondit            | Unconditional Branch                                                                                   |        |                |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------|--------|----------------|--|--|--|

| Synt  | ax:                                                                                                                                                                                                                                                                   | [ label ]           | [ <i>label</i> ] GOTO k                                                                                |        |                |  |  |  |

| Ope   | rands:                                                                                                                                                                                                                                                                | $0 \leq k \leq 81$  | 91                                                                                                     |        |                |  |  |  |

| Ope   | ration:                                                                                                                                                                                                                                                               | k<12:8> -           | $k \rightarrow PC<12:0>;$<br>$k<12:8> \rightarrow PCLATH<4:0>,$<br>$PC<15:13> \rightarrow PCLATH<7:5>$ |        |                |  |  |  |

| Statu | us Affected:                                                                                                                                                                                                                                                          | None                |                                                                                                        |        |                |  |  |  |

| Enco  | oding:                                                                                                                                                                                                                                                                | 110k                | kkkk                                                                                                   | kkkk   | kkkk           |  |  |  |

| Des   | Bescription: GOTO allows an unconditional branch<br>anywhere within an 8K page boundar<br>The thirteen-bit immediate value is<br>loaded into PC bits <12:0>. Then the<br>upper eight bits of PC are loaded into<br>PCLATH. GOTO is always a two-cycle<br>instruction. |                     |                                                                                                        |        |                |  |  |  |

| Wor   | ds:                                                                                                                                                                                                                                                                   | 1                   | 1                                                                                                      |        |                |  |  |  |

| Cycl  | es:                                                                                                                                                                                                                                                                   | 2                   | 2                                                                                                      |        |                |  |  |  |

| QC    | vcle Activity:                                                                                                                                                                                                                                                        |                     |                                                                                                        |        |                |  |  |  |

|       | Q1                                                                                                                                                                                                                                                                    | Q2                  | Q3                                                                                                     |        | Q4             |  |  |  |

|       | Decode                                                                                                                                                                                                                                                                | Read literal<br>'k' | Proce<br>Data                                                                                          |        | ite to PC      |  |  |  |

|       | No<br>operation                                                                                                                                                                                                                                                       | No<br>operation     | No<br>operat                                                                                           | ion oj | No<br>peration |  |  |  |

Example:

After Instruction

PC = Address (THERE)

GOTO THERE

| RLNCF                     | Rotate L                                           | Rotate Left f (no carry)             |                      |                                               |             |  |  |

|---------------------------|----------------------------------------------------|--------------------------------------|----------------------|-----------------------------------------------|-------------|--|--|

| Syntax:                   | [ label ]                                          | RLNCF                                | f,d                  |                                               | Synt        |  |  |

| Operands:                 | 0 ≤ f ≤ 25<br>d ∈ [0,1]                            | $0 \le f \le 255$ O<br>d $\in [0,1]$ |                      |                                               |             |  |  |

| Operation:                | $f < n > \rightarrow d$<br>$f < 7 > \rightarrow d$ | ,                                    |                      |                                               | Ope         |  |  |

| Status Affected:          | None                                               |                                      |                      |                                               |             |  |  |

| Encoding:                 | 0010                                               | 001d                                 | fff                  | f ffff                                        | Statu       |  |  |

| Description:              | one bit to t<br>placed in \                        | he left. If 'c                       | d' is 0,<br>d' is 1, | are rotated<br>the result is<br>the result is | D 000       |  |  |

|                           |                                                    | regis                                | ster f               |                                               |             |  |  |

| Words:                    | 1                                                  |                                      |                      |                                               |             |  |  |

| Cycles:                   | 1                                                  |                                      |                      |                                               | 14/         |  |  |

| Q Cycle Activity:         |                                                    |                                      |                      |                                               | Wor         |  |  |

| Q1                        | Q2                                                 | Q3                                   |                      | Q4                                            | Cycl        |  |  |

| Decode                    | Read<br>register 'f'                               | Process<br>Data                      | -                    | Write to<br>destination                       | QC          |  |  |

|                           |                                                    |                                      |                      |                                               |             |  |  |

| Example:                  | RLNCF                                              | REG,                                 | , 1                  |                                               |             |  |  |

| Before Instr              | uction                                             |                                      |                      |                                               | Буа         |  |  |

| C<br>REG                  | = 0<br>= 1110 1                                    | .011                                 |                      |                                               | <u>Exar</u> |  |  |

| After Instruc<br>C<br>REG | tion<br>=<br>= 1101 0                              | 111                                  |                      |                                               |             |  |  |

| RCF                    | Rotate Right f through Carry                                                                                                                                                                         |                  |      |                        |  |  |  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|------------------------|--|--|--|

| Syntax:                | [ label ]                                                                                                                                                                                            | [label] RRCF f,d |      |                        |  |  |  |

| )perands:              | $0 \le f \le 255$<br>$d \in [0,1]$                                                                                                                                                                   | 5                |      |                        |  |  |  |

| Operation:             | $f < n > \rightarrow d < n-1 >;$<br>$f < 0 > \rightarrow C;$<br>$C \rightarrow d < 7 >$                                                                                                              |                  |      |                        |  |  |  |

| Status Affected:       | С                                                                                                                                                                                                    |                  |      |                        |  |  |  |

| ncoding:               | 0001                                                                                                                                                                                                 | 100d             | ffff | ffff                   |  |  |  |

| Description:<br>Vords: | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>WREG. If 'd' is 1, the result is placed<br>back in register 'f'. |                  |      |                        |  |  |  |

| Cycles:                | 1                                                                                                                                                                                                    |                  |      |                        |  |  |  |

| Q Cycle Activity:      | •                                                                                                                                                                                                    |                  |      |                        |  |  |  |

| Q1                     | Q2                                                                                                                                                                                                   | Q                | 3    | Q4                     |  |  |  |

| Decode                 | Read<br>register 'f'                                                                                                                                                                                 | Proce<br>Dat     |      | Write to<br>estination |  |  |  |

|                        |                                                                                                                                                                                                      |                  |      |                        |  |  |  |

| xample:                | xample: RRCF REG1,0                                                                                                                                                                                  |                  |      |                        |  |  |  |

| Before Instruction     |                                                                                                                                                                                                      |                  |      |                        |  |  |  |

REG1 = 1110 0110

WREG = 0111 0011

= 0

= 0

1110 0110

С

С

After Instruction REG1 =

# **19.0 DEVELOPMENT SUPPORT**

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC<sup>™</sup> In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD for PIC16F87X

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup>1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ<sup>®</sup> Demonstration Board

# 19.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup>-based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor

- A project manager

- Customizable toolbar and key mapping

- A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the cost-effective simulator to a full-featured emulator with minimal retraining.

# 19.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCU's.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

# 19.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

# 20.3 Timing Parameter Symbology

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2 | ppS                                  | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|----------|--------------------------------------|-----------|----------------------------------------|

| 2. TppS  |                                      | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т        |                                      |           |                                        |

| F        | Frequency                            | Т         | Time                                   |

| Lowerc   | ase symbols (pp) and their meanings: |           |                                        |

| рр       |                                      |           |                                        |

| ad       | Address/Data                         | ost       | Oscillator Start-Up Timer              |

| al       | ALE                                  | pwrt      | Power-Up Timer                         |

| сс       | Capture1 and Capture2                | rb        | PORTB                                  |

| ck       | CLKOUT or clock                      | rd        | RD                                     |

| dt       | Data in                              | rw        | RD or WR                               |

| in       | INT pin                              | tO        | ТОСКІ                                  |

| io       | I/O port                             | t123      | TCLK12 and TCLK3                       |

| mc       | MCLR                                 | wdt       | Watchdog Timer                         |

| oe       | OE                                   | wr        | WR                                     |

| OS       | OSC1                                 |           |                                        |

| Upperc   | ase symbols and their meanings:      |           |                                        |

| S        |                                      |           |                                        |