Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 33MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 50                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 902 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 12x10b                                                                   |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-TQFP                                                                      |

| Supplier Device Package    | 64-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c756at-33i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 5-4:             | INITIALIZATIO | N CONDITIONS FOR SP               | ECIAL FUNCTION REC      | GISTERS (CONTINUED)                     |

|------------------------|---------------|-----------------------------------|-------------------------|-----------------------------------------|

| Register               | Address       | Power-on Reset<br>Brown-out Reset | MCLR Reset<br>WDT Reset | Wake-up from SLEEP<br>through Interrupt |

| Bank 1                 |               |                                   |                         |                                         |

| DDRC <sup>(5)</sup>    | 10h           | 1111 1111                         | 1111 1111               | սսսս սսսս                               |

| PORTC <sup>(4,5)</sup> | 11h           | xxxx xxxx                         | uuuu uuuu               | นนนน นนนน                               |

| DDRD <sup>(5)</sup>    | 12h           | 1111 1111                         | 1111 1111               | นนนน นนนน                               |

| PORTD <sup>(4,5)</sup> | 13h           | xxxx xxxx                         | uuuu uuuu               | นนนน นนนน                               |

| DDRE <sup>(5)</sup>    | 14h           | 1111                              | 1111                    | uuuu                                    |

| PORTE <sup>(4,5)</sup> | 15h           | xxxx                              | uuuu                    | uuuu                                    |

| PIR1                   | 16h           | x000 0010                         | u000 0010               | սսսս սսսս(1)                            |

| PIE1                   | 17h           | 0000 0000                         | 0000 0000               | uuuu uuuu                               |

| Bank 2                 |               |                                   |                         |                                         |

| TMR1                   | 10h           | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |

| TMR2                   | 11h           | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |

| TMR3L                  | 12h           | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |

| TMR3H                  | 13h           | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |

| PR1                    | 14h           | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |

| PR2                    | 15h           | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |

| PR3/CA1L               | 16h           | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |

| PR3/CA1H               | 17h           | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |

| Bank 3                 |               |                                   |                         |                                         |

| PW1DCL                 | 10h           | xx                                | uu                      | uu                                      |

| PW2DCL                 | 11h           | xx0                               | uu0                     | uuu                                     |

| PW1DCH                 | 12h           | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |

| PW2DCH                 | 13h           | xxxx xxxx                         | uuuu uuuu               | นนนน นนนน                               |

| CA2L                   | 14h           | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |

| CA2H                   | 15h           | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |

| TCON1                  | 16h           | 0000 0000                         | 0000 0000               | uuuu uuuu                               |

| TCON2                  | 17h           | 0000 0000                         | 0000 0000               | uuuu uuuu                               |

#### TABLE 5-4: INITIALIZATION CONDITIONS FOR SPECIAL FUNCTION REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented, read as '0', q = value depends on condition

Note 1: One or more bits in INTSTA, PIR1, PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GLINTD bit is cleared, the PC is loaded with the interrupt vector.

3: See Table 5-3 for RESET value of specific condition.

4: This is the value that will be in the port output latch.

**5:** When the device is configured for Microprocessor or Extended Microcontroller mode, the operation of this port does not rely on these registers.

6: On any device RESET, these pins are configured as inputs.

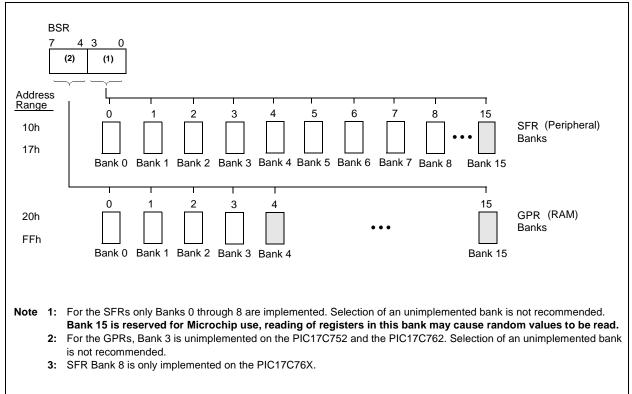

## 7.8 Bank Select Register (BSR)

The BSR is used to switch between banks in the data memory area (Figure 7-9). In the PIC17C7XX devices, the entire byte is implemented. The lower nibble is used to select the peripheral register bank. The upper nibble is used to select the general purpose memory bank.

All the Special Function Registers (SFRs) are mapped into the data memory space. In order to accommodate the large number of registers, a banking scheme has been used. A segment of the SFRs, from address 10h to address 17h, is banked. The lower nibble of the bank select register (BSR) selects the currently active "peripheral bank." Effort has been made to group the peripheral registers of related functionality in one bank. However, it will still be necessary to switch from bank to bank in order to address all peripherals related to a single task. To assist this, a MOVLB bank instruction has been included in the instruction set.

The need for a large general purpose memory space dictated a general purpose RAM banking scheme. The upper nibble of the BSR selects the currently active general purpose RAM bank. To assist this, a MOVLR bank instruction has been provided in the instruction set.

If the currently selected bank is not implemented (such as Bank 13), any read will read all '0's. Any write is completed to the bit bucket and the ALU status bits will be set/cleared as appropriate.

Note: Registers in Bank 15 in the Special Function Register area, are reserved for Microchip use. Reading of registers in this bank may cause random values to be read.

#### FIGURE 7-9: BSR OPERATION

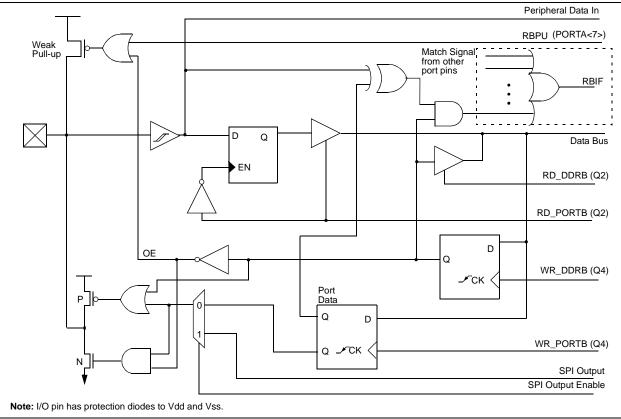

#### FIGURE 10-7: BLOCK DIAGRAM OF RB6 PORT PIN

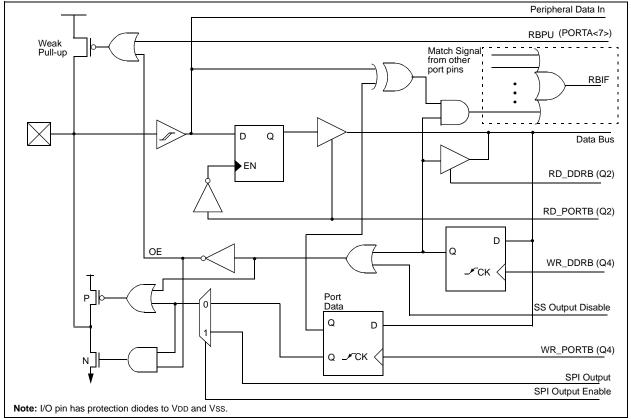

#### FIGURE 10-8: BLOCK DIAGRAM OF RB7 PORT PIN

#### TABLE 10-13: PORTG FUNCTIONS

| Name          | Bit  | Buffer Type | Function                                                                                  |

|---------------|------|-------------|-------------------------------------------------------------------------------------------|

| RG0/AN3       | bit0 | ST          | Input/output or analog input 3.                                                           |

| RG1/AN2       | bit1 | ST          | Input/output or analog input 2.                                                           |

| RG2/AN1/VREF- | bit2 | ST          | Input/output or analog input 1 or the ground reference voltage.                           |

| RG3/AN0/VREF+ | bit3 | ST          | Input/output or analog input 0 or the positive reference voltage.                         |

| RG4/CAP3      | bit4 | ST          | Input/output or the Capture3 input pin.                                                   |

| RG5/PWM3      | bit5 | ST          | Input/output or the PWM3 output pin.                                                      |

| RG6/RX2/DT2   | bit6 | ST          | Input/output or the USART2 (SCI) Asynchronous Receive or USART2 (SCI) Synchronous Data.   |

| RG7/TX2/CK2   | bit7 | ST          | Input/output or the USART2 (SCI) Asynchronous Transmit or USART2 (SCI) Synchronous Clock. |

Legend: ST = Schmitt Trigger input

#### TABLE 10-14: REGISTERS/BITS ASSOCIATED WITH PORTG

| Address     | Name                                             | Bit 7           | Bit 6           | Bit 5        | Bit 4        | Bit 3       | Bit 2       | Bit 1       | Bit 0       | Value on<br>POR,<br>BOR | MCLR, WDT |

|-------------|--------------------------------------------------|-----------------|-----------------|--------------|--------------|-------------|-------------|-------------|-------------|-------------------------|-----------|

| 12h, Bank 5 | I, Bank 5 DDRG Data Direction Register for PORTG |                 |                 |              |              |             |             |             | 1111 1111   | 1111 1111               |           |

| 13h, Bank 5 | PORTG                                            | RG7/<br>TX2/CK2 | RG6/<br>RX2/DT2 | RG5/<br>PWM3 | RG4/<br>CAP3 | RG3/<br>AN0 | RG2/<br>AN1 | RG1/<br>AN2 | RG0/<br>AN3 | xxxx 0000               | uuuu 0000 |

| 15h, Bank 5 | ADCON1                                           | ADCS1           | ADCS0           | ADFM         | —            | PCFG3       | PCFG2       | PCFG1       | PCFG0       | 000- 0000               | 000- 0000 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTG.

#### 10.10 I/O Programming Considerations

#### 10.10.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read, followed by a write operation. For example, the BCF and BSF instructions read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB, will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g. bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Reading a port reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (BCF, BSF, BTG, etc.) on a port, the value of the port pins is read, the desired operation is performed with this value and the value is then written to the port latch.

Example 10-10 shows the possible effect of two sequential read-modify-write instructions on an I/O port.

#### EXAMPLE 10-10: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

| <pre>; Initial PORT sett ; ; PORTB&lt;7:6&gt; have p ; not connected to</pre> | PORTB<3:0<br>ull-ups and are | )> Outputs             |

|-------------------------------------------------------------------------------|------------------------------|------------------------|

| ;<br>;<br>;                                                                   | PORT latch                   | PORT pins              |

| ,<br>BCF PORTB, 7<br>BCF PORTB, 6                                             | ; 10pp pppp                  |                        |

| BCF DDRB, 7<br>BCF DDRB, 6<br>;                                               | ; 10pp pppp<br>; 10pp pppp   | 11pp pppp<br>10pp pppp |

| ; Note that the use<br>; pin values to be<br>; caused RB7 to be<br>; (High).  | 00pp pppp. The               | 2nd BCF                |

**Note:** A pin actively outputting a Low or High should not be driven from external devices, in order to change the level on this pin (i.e., "wired-or", "wired-and"). The resulting high output currents may damage the device.

# PIC17C7XX

NOTES:

| BAUD       | FOSC  | = 33 MHz       | SPBRG     | FOSC = 25 Mł       | 1Z    | SPBRG       | FOSC = 2 | 0 MHz              | SPBRG     | FOSC = 1  | 6 MHz  | SPBRG              |

|------------|-------|----------------|-----------|--------------------|-------|-------------|----------|--------------------|-----------|-----------|--------|--------------------|

| RATE       |       |                | VALUE     |                    |       | VALUE       |          | **                 | VALUE     |           | **     | VALUE              |

| (K)        | KBAL  |                | (DECIMAL) |                    | RROR  | (DECIMAL)   |          | %ERROR             | (DECIMAL) | KBAUD     | %ERROR | (DECIMAL)          |

| 0.3        | NA    | . —            | —         | NA                 | -     | _           | NA       | _                  | —         | NA        | _      | _                  |

| 1.2        | NA    | . —            | —         | NA                 | _     | _           | NA       | _                  | _         | NA        | _      | _                  |

| 2.4        | NA    | . —            | —         | NA                 | _     | _           | NA       | _                  | _         | NA        | _      | _                  |

| 9.6        | NA    | . —            | —         | NA                 | —     | —           | NA       | —                  | —         | NA        | —      | —                  |

| 19.2       | NA    | . —            | —         | NA                 | —     | —           | 19.53    | +1.73              | 255       | 19.23     | +0.16  | 207                |

| 76.8       | 77.1  | 0 +0.39        | 106       | 77.16 -            | +0.47 | 80          | 76.92    | +0.16              | 64        | 76.92     | +0.16  | 51                 |

| 96         | 95.9  | 3 -0.07        | 85        | 96.15 -            | -0.16 | 64          | 96.15    | +0.16              | 51        | 95.24     | -0.79  | 41                 |

| 300        | 294.6 | 64 -1.79       | 27        | 297.62             | 0.79  | 20          | 294.1    | -1.96              | 16        | 307.69    | +2.56  | 12                 |

| 500        | 485.2 | 29 -2.94       | 16        | 480.77             | -3.85 | 12          | 500      | 0                  | 9         | 500       | 0      | 7                  |

| HIGH       | 825   | 0 —            | 0         | 6250               | _     | 0           | 5000     | _                  | 0         | 4000      | _      | 0                  |

| LOW        | 32.2  | 2 —            | 255       | 24.41              | _     | 255         | 19.53    | —                  | 255       | 15.625    | —      | 255                |

| 5.41       | 15    | Fosc = 10 MHz  | Z         | 00000              | Fosc  | = 7.159 MHz |          | 00000              | Fosc = 5  | .068 MHz  |        | 00000              |

| BAU<br>RAT |       |                |           | SPBRG<br>VALUE     |       |             |          | SPBRG<br>VALUE     |           |           |        | SPBRG<br>VALUE     |

| (K         |       | KBAUD          | %ERROR    | (DECIMAL)          | KB    | AUD %       | ERROR    | (DECIMAL)          | KBAUI     | D %E      | RROR   | (DECIMAL)          |

| 0.3        | 3     | NA             |           |                    | Ν     | NA          | _        | _                  | NA        |           | -      | —                  |

| 1.2        | 2     | NA             | —         | _                  | Ν     | NA          | _        | —                  | NA        |           | _      | _                  |

| 2.4        | 4     | NA             | _         | —                  | Ν     | ١A          | _        | —                  | NA        |           | -      | _                  |

| 9.0        | 6     | 9.766          | +1.73     | 255                | 9.    | 622         | +0.23    | 185                | 9.6       |           | 0      | 131                |

| 19.        | .2    | 19.23          | +0.16     | 129                | 19    | .24         | +0.23    | 92                 | 19.2      |           | 0      | 65                 |

| 76.        | .8    | 75.76          | -1.36     | 32                 | 77    | .82         | +1.32    | +1.32 22 79        |           | +         | 3.13   | 15                 |

| 96         | 6     | 96.15          | +0.16     | 25                 | 94    | .20         | -1.88    | 18                 | 97.48     | +         | 1.54   | 12                 |

| 30         | 0     | 312.5          | +4.17     | 7                  | 29    | 98.3        | -0.57    | 5                  | 316.8     | 6.8 +5.60 |        | 3                  |

| 50         | 0     | 500            | 0         | 4                  | Ν     | ١A          | _        | —                  | NA        | NA —      |        | _                  |

| HIG        | θH    | 2500           | —         | 0                  | 17    | 89.8        | _        | 0                  | 1267      |           | _      | 0                  |

| LO         | W     | 9.766          | —         | 255                | 6.9   | 991         | _        | 255                | 4.950     |           | _      | 255                |

|            |       | Fosc = 3.579 M | IH7       |                    | Fosc  | = 1 MHz     |          |                    | FOSC = 3  | 2.768 kHz |        |                    |

| BAU        |       |                |           | SPBRG              |       |             |          | SPBRG              |           |           |        | SPBRG              |

| RAT<br>(K  |       | KBAUD          | %ERROR    | VALUE<br>(DECIMAL) | KB    | AUD %       | ERROR    | VALUE<br>(DECIMAL) | KBAU      | D %E      | RROR   | VALUE<br>(DECIMAL) |

| 0.3        | 3     | NA             |           |                    | N     | NA          | _        |                    | 0.303     | +         | 1.14   | 26                 |

| 1.2        |       | NA             | _         | _                  |       |             | +0.16    | 207                | 1.170     |           | 2.48   | 6                  |

| 2.4        |       | NA             | _         | _                  |       |             | +0.16    | 103                | NA        |           | _      |                    |

| 9.6        |       | 9.622          | +0.23     | 92                 |       |             | +0.16    | 25                 | NA        |           | _      | _                  |

| 19.        |       | 19.04          | -0.83     | 46                 |       |             | +0.16    | 12                 | NA        |           | _      | _                  |

| 76.        |       | 74.57          | -2.90     | 10                 | -     |             | +8.51    | 2                  | NA        |           | _      | _                  |

| 96         |       | 99.43          | _3.57     | 8                  |       | NA          | _        | _                  | NA        |           | _      | _                  |

|            | -     | 00.10          | _0.07     | -                  | 1 .   |             |          |                    |           |           |        |                    |

| TABLE 14-4: | BAUD RATES FOR SYNCHRONOUS MODE |

|-------------|---------------------------------|

|-------------|---------------------------------|

298.3

NA

894.9

3.496

-0.57

\_

\_

2

—

0

255

NA

NA

250

0.976

—

\_

\_

\_

\_

0

255

NA

NA

8.192

0.032

\_

\_

\_

\_

\_

\_

0

255

300

500

HIGH

LOW

## 14.4 USART Synchronous Slave Mode

The Synchronous Slave mode differs from the Master mode, in the fact that the shift clock is supplied externally at the TX/CK pin (instead of being supplied internally in the Master mode). This allows the device to transfer or receive data in the SLEEP mode. The Slave mode is entered by clearing the CSRC (TXSTA<7>) bit.

#### 14.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the SYNC Master and Slave modes are identical except in the case of the SLEEP mode.

If two words are written to TXREG and then the SLEEP instruction executes, the following will occur. The first word will immediately transfer to the TSR and will transmit as the shift clock is supplied. The second word will remain in TXREG. TXIF will not be set. When the first word has been shifted out of TSR, TXREG will transfer the second word to the TSR and the TXIF flag will now be set. If TXIE is enabled, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, then the program will branch to the interrupt vector (0020h).

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting the SYNC and SPEN bits and clearing the CSRC bit.

- 2. Clear the CREN bit.

- 3. If interrupts are desired, then set the TXIE bit.

- 4. If 9-bit transmission is desired, then set the TX9 bit.

- 5. If 9-bit transmission is selected, the ninth bit should be loaded in TX9D.

- 6. Start transmission by loading data to TXREG.

- 7. Enable the transmission by setting TXEN.

Writing the transmit data to the TXREG, then enabling the transmit (setting TXEN), allows transmission to start sooner than doing these two events in the reverse order.

#### 14.4.2 USART SYNCHRONOUS SLAVE RECEPTION

Operation of the Synchronous Master and Slave modes are identical except in the case of the SLEEP mode. Also, SREN is a "don't care" in Slave mode.

If receive is enabled (CREN) prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR will transfer the data to RCREG (setting RCIF) and if the RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0020h).

Steps to follow when setting up a Synchronous Slave Reception:

- 1. Enable the synchronous master serial port by setting the SYNC and SPEN bits and clearing the CSRC bit.

- 2. If interrupts are desired, then set the RCIE bit.

- 3. If 9-bit reception is desired, then set the RX9 bit.

- 4. To enable reception, set the CREN bit.

- The RCIF bit will be set when reception is complete and an interrupt will be generated if the RCIE bit was set.

- 6. Read RCSTA to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading RCREG.

- 8. If any error occurred, clear the error by clearing the CREN bit.

**Note:** To abort reception, either clear the SPEN bit, or the CREN bit (when in Continuous Receive mode). This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

#### REGISTER 15-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS: 13h, BANK 6) R/W-0 R/W-0 R-0 R-0 R-0 R-0 R-0 R-0 SMP CKE D/A Р S R/W UA BF bit 7 bit 0 bit 7 SMP: Sample bit SPI Master mode: 1 = Input data sampled at end of data output time 0 = Input data sampled at middle of data output time SPI Slave mode: SMP must be cleared when SPI is used in Slave mode In I<sup>2</sup>C Master or Slave mode: 1 = Slew rate control disabled for Standard Speed mode (100 kHz and 1 MHz) 0 = Slew rate control enabled for High Speed mode (400 kHz) bit 6 CKE: SPI Clock Edge Select (Figure 15-6, Figure 15-8 and Figure 15-9) CKP = 0: 1 = Data transmitted on rising edge of SCK 0 = Data transmitted on falling edge of SCK CKP = 1: 1 = Data transmitted on falling edge of SCK 0 = Data transmitted on rising edge of SCK bit 5 D/A: Data/Address bit (I<sup>2</sup>C mode only) 1 = Indicates that the last byte received or transmitted was data 0 = Indicates that the last byte received or transmitted was address P: STOP bit bit 4 $(l^2C \text{ mode only})$ . This bit is cleared when the MSSP module is disabled, SSPEN is cleared.) 1 = Indicates that a STOP bit has been detected last (this bit is '0' on RESET) 0 = STOP bit was not detected last bit 3 S: START bit (I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.) 1 = Indicates that a START bit has been detected last (this bit is '0' on RESET) 0 = START bit was not detected last **R/W**: Read/Write bit Information (I<sup>2</sup>C mode only) bit 2 This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to the next START bit, STOP bit, or not ACK bit. In I<sup>2</sup>C Slave mode: 1 = Read 0 = WriteIn I<sup>2</sup>C Master mode: 1 = Transmit is in progress 0 = Transmit is not in progress Or'ing this bit with SEN, RSEN, PEN, RCEN, or ACKEN will indicate if the MSSP is in IDLE mode. bit 1 **UA**: Update Address (10-bit I<sup>2</sup>C mode only) 1 = Indicates that the user needs to update the address in the SSPADD register 0 = Address does not need to be updated bit 0 BF: Buffer Full Status bit Receive (SPI and I<sup>2</sup>C modes) 1 = Receive complete, SSPBUF is full 0 = Receive not complete, SSPBUF is empty Transmit (I<sup>2</sup>C mode only) 1 = Data transmit in progress (does not include the ACK and STOP bits), SSPBUF is full 0 = Data transmit complete (does not include the $\overline{ACK}$ and STOP bits), SSPBUF is empty Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

'1' = Bit is set

n = Value at POR Reset

x = Bit is unknown

'0' = Bit is cleared

#### 15.2.1.1 Addressing

Once the MSSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register on the falling edge of the 8th SCL pulse.

- b) The buffer full bit, BF, is set on the falling edge of the 8th SCL pulse.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR2<7>), is set (interrupt is generated if enabled) - on the falling edge of the 9th SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for a 10-bit address is as follows, with steps 7- 9 for slave-transmitter:

- 1. Receive first (high) byte of Address (bits SSPIF, BF and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of Address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of Address. This will clear bit UA and release the SCL line.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

**Note:** Following the Repeated Start condition (step 7) in 10-bit mode, the user only needs to match the first 7-bit address. The user does not update the SSPADD for the second half of the address.

#### 15.2.1.2 Slave Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON1<6>) is set.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR2<7>) must be cleared in software. The SSPSTAT register is used to determine the status of the received byte.

Note: The SSPBUF will be loaded if the SSPOV bit is set and the BF flag is cleared. If a read of the SSPBUF was performed, but the user did not clear the state of the SSPOV bit before the next receive occurred, the ACK is not sent and the SSP-BUF is updated.

|    | ts as Data<br>s Received | SSPSR $ ightarrow$ SSPBUF | Generate ACK<br>Pulse | Set bit SSPIF<br>(SSP Interrupt occurs |  |  |

|----|--------------------------|---------------------------|-----------------------|----------------------------------------|--|--|

| BF | SSPOV                    |                           | Fuise                 | if enabled)                            |  |  |

| 0  | 0                        | Yes                       | Yes                   | Yes                                    |  |  |

| 1  | 0                        | No                        | No                    | Yes                                    |  |  |

| 1  | 1                        | No                        | No                    | Yes                                    |  |  |

| 0  | 1                        | Yes                       | No                    | Yes                                    |  |  |

#### TABLE 15-2: DATA TRANSFER RECEIVED BYTE ACTIONS

Note 1: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

### 15.2.6 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET, or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the STOP condition occurs.

In Multi-Master operation, the SDA line must be monitored for arbitration, to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A START Condition

- A Repeated Start Condition

- An Acknowledge Condition

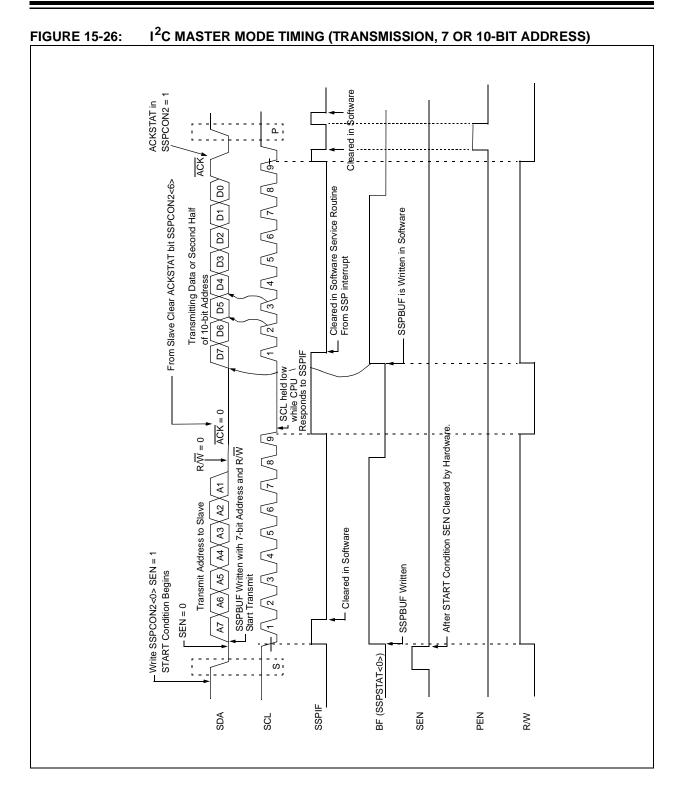

#### 15.2.7 I<sup>2</sup>C MASTER MODE SUPPORT

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. Once Master mode is enabled, the user has six options.

- · Assert a START condition on SDA and SCL.

- Assert a Repeated Start condition on SDA and SCL.

- Write to the SSPBUF register initiating transmission of data/address.

- Generate a STOP condition on SDA and SCL.

- Configure the I<sup>2</sup>C port to receive data.

- Generate an Acknowledge condition at the end of a received byte of data.

| Note: | The MSSP Module, when configured in I <sup>2</sup> C |

|-------|------------------------------------------------------|

|       | Master mode, does not allow queueing of              |

|       | events. For instance: The user is not                |

|       | allowed to initiate a START condition and            |

|       | immediately write the SSPBUF register to             |

|       | initiate transmission before the START               |

|       | condition is complete. In this case, the             |

|       | SSPBUF will not be written to and the                |

|       | WCOL bit will be set, indicating that a write        |

|       | to the SSPBUF did not occur.                         |

### 15.2.7.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an acknowledge bit is received. START and STOP conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address, followed by a '1' to indicate receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an acknowledge bit is transmitted. START and STOP conditions indicate the beginning and end of transmission.

The baud rate generator used for SPI mode operation is now used to set the SCL clock frequency for either 100 kHz, 400 kHz, or 1 MHz I<sup>2</sup>C operation. The baud rate generator reload value is contained in the lower 7 bits of the SSPADD register. The baud rate generator will automatically begin counting on a write to the SSP-BUF. Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state

# 15.2.12 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the receive enable bit, RCEN (SSPCON2<3>).

| Note: | The SSP Module must be in an IDLE        |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|

|       | STATE before the RCEN bit is set, or the |  |  |  |  |  |  |

|       | RCEN bit will be disregarded.            |  |  |  |  |  |  |

The baud rate generator begins counting and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag is set, the SSPIF is set and the baud rate generator is suspended from counting, holding SCL low. The SSP is now in IDLE state, awaiting the next command. When the buffer is read by the CPU, the BF flag is automatically cleared. The user can then send an acknowledge bit at the end of reception, by setting the acknowledge sequence enable bit, ACKEN (SSPCON2<4>).

#### 15.2.12.1 BF Status Flag

In receive operation, BF is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when SSPBUF is read.

#### 15.2.12.2 SSPOV Status Flag

In receive operation, SSPOV is set when 8 bits are received into the SSPSR, and the BF flag is already set from a previous reception.

#### 15.2.12.3 WCOL Status Flag

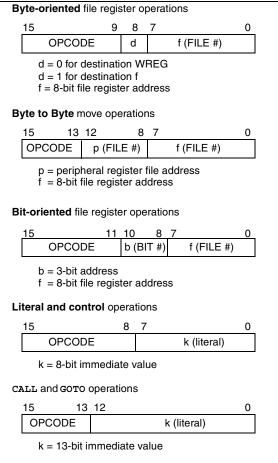

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur). Table 18-2 lists the instructions recognized by the MPASM assembler.

**Note 1:** Any unused opcode is Reserved. Use of any reserved opcode may cause unexpected operation.

All instruction examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

To represent a binary number:

0000 0100b

where b signifies a binary string.

# FIGURE 18-1: GENERAL FORMAT FOR INSTRUCTIONS

# 18.1 Special Function Registers as Source/Destination

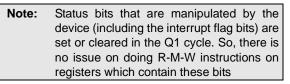

The PIC17C7XX's orthogonal instruction set allows read and write of all file registers, including special function registers. There are some special situations the user should be aware of:

#### 18.1.1 ALUSTA AS DESTINATION

If an instruction writes to ALUSTA, the Z, C, DC and OV bits may be set or cleared as a result of the instruction and overwrite the original data bits written. For example, executing CLRF ALUSTA will clear register ALUSTA and then set the Z bit leaving 0000 0100b in the register.

#### 18.1.2 PCL AS SOURCE OR DESTINATION

Read, write or read-modify-write on PCL may have the following results:

| Read PC:           | $PCH \to PCLATH;  PCL \to dest$                                                              |

|--------------------|----------------------------------------------------------------------------------------------|

| Write PCL:         | PCLATH $\rightarrow$ PCH;<br>8-bit destination value $\rightarrow$ PCL                       |

| Read-Modify-Write: | PCL $\rightarrow$ ALU operand<br>PCLATH $\rightarrow$ PCH;<br>8-bit result $\rightarrow$ PCL |

Where PCH = program counter high byte (not an addressable register), PCLATH = Program counter high holding latch, dest = destination, WREG or f.

#### 18.1.3 BIT MANIPULATION

All bit manipulation instructions are done by first reading the entire register, operating on the selected bit and writing the result back (read-modify-write (R-M-W)). The user should keep this in mind when operating on some special function registers, such as ports.

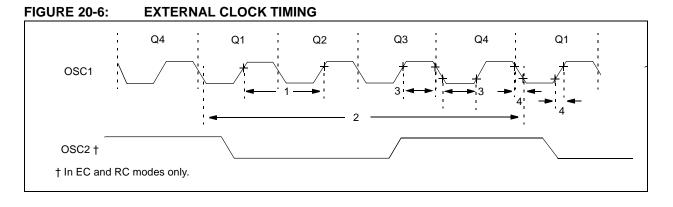

## 20.4 Timing Diagrams and Specifications

### TABLE 20-1: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic         | Min   | Тур†   | Max   | Units | Conditions                                      |

|--------------|-------|------------------------|-------|--------|-------|-------|-------------------------------------------------|

|              | Fosc  | External CLKIN         | DC    |        | 8     | MHz   | EC osc mode - 08 devices (8 MHz devices)        |

|              |       | Frequency (Note 1)     | DC    | —      | 16    | MHz   | - 16 devices (16 MHz devices)                   |

|              |       |                        | DC    | —      | 33    | MHz   | - 33 devices (33 MHz devices)                   |

|              |       | Oscillator Frequency   | DC    | _      | 4     | MHz   | RC osc mode                                     |

|              |       | (Note 1)               | 2     | —      | 8     | MHz   | XT osc mode - 08 devices (8 MHz devices)        |

|              |       |                        | 2     | —      | 16    | MHz   | - 16 devices (16 MHz devices)                   |

|              |       |                        | 2     | —      | 33    | MHz   | - 33 devices (33 MHz devices)                   |

|              |       |                        | DC    | —      | 2     | MHz   | LF osc mode                                     |

| 1            | Tosc  | External CLKIN Period  | 125   | Ι      |       | ns    | EC osc mode - 08 devices (8 MHz devices)        |

|              |       | (Note 1)               | 62.5  | —      | —     | ns    | - 16 devices (16 MHz devices)                   |

|              |       |                        | 30.3  | _      | —     | ns    | - 33 devices (33 MHz devices)                   |

|              |       | Oscillator Period      | 250   |        |       | ns    | RC osc mode                                     |

|              |       | (Note 1)               | 125   | —      | 1,000 | ns    | XT osc mode - 08 devices (8 MHz devices)        |

|              |       |                        | 62.5  | —      | 1,000 | ns    | <ul> <li>16 devices (16 MHz devices)</li> </ul> |

|              |       |                        | 30.3  | —      | 1,000 | ns    | - 33 devices (33 MHz devices)                   |

|              |       |                        | 500   | —      | —     | ns    | LF osc mode                                     |

| 2            | Тсү   | Instruction Cycle Time | 121.2 | 4/Fosc | DC    | ns    |                                                 |

|              |       | (Note 1)               |       |        |       |       |                                                 |

| 3            | TosL, | Clock in (OSC1)        | 10    | _      | _     | ns    | EC oscillator                                   |

|              | TosH  | High or Low Time       |       |        |       |       |                                                 |

| 4            | TosR, | Clock in (OSC1)        | _     | _      | 5     | ns    | EC oscillator                                   |

|              | TosF  | Rise or Fall Time      |       |        |       |       |                                                 |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

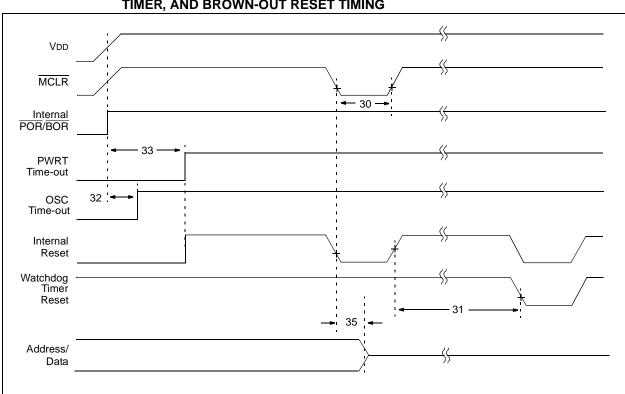

#### **FIGURE 20-8:** RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET TIMING

#### **TABLE 20-3**: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

| Param.<br>No. | Sym                                                            | Characteristic                                    |                     | Min | Тур†     | Max | Units | Conditions                                 |

|---------------|----------------------------------------------------------------|---------------------------------------------------|---------------------|-----|----------|-----|-------|--------------------------------------------|

| 30            | TmcL                                                           | MCLR Pulse Width (low)                            |                     | 100 | _        | _   | ns    | Vdd = 5V                                   |

| 31            | Twdt                                                           | Watchdog Timer Time-out Period<br>(Postscale = 1) |                     | 5   | 12       | 25  | ms    | VDD = 5V                                   |

| 32            | Tost                                                           | Oscillation Start-up Timer Period                 |                     | —   | 1024Tosc | _   | ms    | Tosc = OSC1 period                         |

| 33            | TPWRT                                                          | Power-up Timer Period                             |                     | 40  | 96       | 200 | ms    | VDD = 5V                                   |

| 34            | Tioz                                                           | MCLR to I/O hi-impedance                          |                     | 100 | _        | _   | ns    | Depends on pin load                        |

| 35            | TmcL2adI                                                       | MCLR to System                                    | PIC17 <b>C</b> 7XX  | _   | _        | 100 | ns    |                                            |

|               |                                                                | Interface bus<br>(AD15:AD0>) invalid              | PIC17 <b>LC</b> 7XX | —   | —        | 120 | ns    |                                            |

| 36            | TBOR                                                           | Brown-out Reset Pulse Width (low)                 |                     | 100 | —        | —   | ns    | VDD within VBOR limits<br>(parameter D005) |

| †             | † Data in "Typ" column is at 5V, 25°C unless otherwise stated. |                                                   |                     |     |          |     |       |                                            |

.

| Param.<br>No. | Sym                 | Charac                                         | teristic   | Min            | Тур†                      | Max            | Units                                                                                   | Conditions                                                                              |

|---------------|---------------------|------------------------------------------------|------------|----------------|---------------------------|----------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| A01           | NR Resolution       |                                                | _          | _              | 10                        | bit            | $\label{eq:VREF+} \begin{array}{l} VDD = 5.12V,\\ VSS \leq VAIN \leq VREF+ \end{array}$ |                                                                                         |

|               |                     |                                                |            | _              | _                         | 10             | bit                                                                                     | $(VREF+ - VREF-) \ge 3.0V,$<br>$VREF- \le VAIN \le VREF+$                               |

| A02           | EABS Absolute error |                                                | _          | _              | < ±1                      | LSb            | $\label{eq:VREF+} \begin{array}{l} VDD = 5.12V,\\ VSS \leq VAIN \leq VREF+ \end{array}$ |                                                                                         |

|               |                     |                                                |            | —              | —                         | < ±1           | LSb                                                                                     | $(VREF+ - VREF-) \ge 3.0V,$<br>$VREF- \le VAIN \le VREF+$                               |

| A03           | EIL                 | Integral linearity error                       |            |                | -                         | < ±1           | LSb                                                                                     | VREF+ = VDD = 5.12V,<br>$VSS \le VAIN \le VREF+$                                        |

|               |                     |                                                |            | _              | -                         | < ±1           | LSb                                                                                     | $(VREF+ - VREF-) \ge 3.0V,$<br>$VREF- \le VAIN \le VREF+$                               |

| A04 EDL       |                     | Differential linearity error                   |            |                |                           | < ±1           | LSb                                                                                     | VREF+ = VDD = 5.12V,<br>$VSS \le VAIN \le VREF+$                                        |

|               |                     |                                                |            | _              | _                         | < ±1           | LSb                                                                                     | $(VREF+ - VREF-) \ge 3.0V,$<br>$VREF- \le VAIN \le VREF+$                               |

| A05 EFS       |                     | Full scale error                               |            | _              | _                         | < ±1           | LSb                                                                                     | $\label{eq:VREF+} \begin{array}{l} VDD = 5.12V,\\ VSS \leq VAIN \leq VREF+ \end{array}$ |

|               |                     |                                                |            | _              | _                         | < ±1           | LSb                                                                                     | $(VREF+ - VREF-) \ge 3.0V,$<br>$VREF- \le VAIN \le VREF+$                               |

| A06 EOFF      |                     | Offset error                                   |            | _              | _                         | < ±1           | LSb                                                                                     | $\label{eq:VREF+} \begin{array}{l} VDD = 5.12V,\\ VSS \leq VAIN \leq VREF+ \end{array}$ |

|               |                     |                                                |            | _              | _                         | < ±1           | LSb                                                                                     | $(VREF+ - VREF-) \ge 3.0V,$<br>$VREF- \le VAIN \le VREF+$                               |

| A10           | —                   | Monotonicity                                   |            | —              | guaranteed <sup>(3)</sup> | _              | —                                                                                       | $VSS \leq VAIN \leq VREF$                                                               |

| A20           | Vref                | Reference voltage<br>(VREF+ — VREF-)           |            | 0V             |                           | _              | V                                                                                       | VREF delta when changing voltage levels on VREF inputs                                  |

| A20A          |                     |                                                |            | 3V             | _                         | _              | V                                                                                       | Absolute minimum electrical spec.<br>to ensure 10-bit accuracy                          |

| A21           | VREF+               | Reference voltage high                         |            | Avss<br>+ 3.0V | —                         | AVDD +<br>0.3V | V                                                                                       |                                                                                         |

| A22           | VREF-               | Reference voltage low                          |            | Avss -<br>0.3V | _                         | Avdd -<br>3.0V | V                                                                                       |                                                                                         |

| A25           | VAIN                | Analog input voltage                           |            | Avss-<br>0.3V  |                           | Vref +<br>0.3V | V                                                                                       |                                                                                         |

| A30           | Zain                | Recommended impedance of analog voltage source |            | —              | _                         | 10.0           | kΩ                                                                                      |                                                                                         |

| A40           | IAD                 | A/D conversion<br>current (VDD)                | PIC17CXXX  | _              | 180                       |                | μΑ                                                                                      | Average current consumption when                                                        |

|               |                     |                                                | PIC17LCXXX | _              | 90                        | _              | μΑ                                                                                      | A/D is on <b>(Note 1)</b>                                                               |

| A50           | IREF                | VREF input current (Note 2)                    |            | 10             | —                         | 1000           | μΑ                                                                                      | During VAIN acquisition.<br>Based on differential of VHOLD to<br>VAIN                   |

|               |                     |                                                |            | _              | _                         | 10             | μΑ                                                                                      | During A/D conversion cycle                                                             |

| TABLE 20-18: A/D C | ONVERTER CHARACTERISTICS |

|--------------------|--------------------------|

|--------------------|--------------------------|

† Data in "Typ" column is at 5V, 25°C unless otherwise stated.

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RG0 and RG1 pins or AVDD and AVSS pins, whichever is selected as reference input.

3: The A/D conversion result never decreases with an increase in the Input Voltage and has no missing codes.

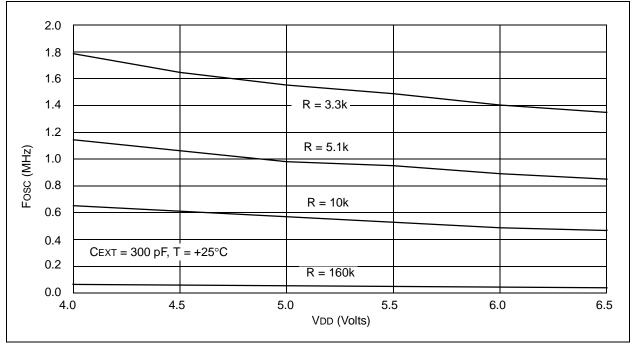

## TABLE 21-2: RC OSCILLATOR FREQUENCIES

| Сехт   | Rext | Ave<br>Fosc @ \$ |       |  |

|--------|------|------------------|-------|--|

| 22 pF  | 10k  | 3.33 MHz         | ± 12% |  |

|        | 100k | 353 kHz          | ± 13% |  |

| 100 pF | 3.3k | 3.54 MHz         | ± 10% |  |

|        | 5.1k | 2.43 MHz         | ± 14% |  |

|        | 10k  | 1.30 MHz         | ± 17% |  |

|        | 100k | 129 kHz          | ± 10% |  |

| 300 pF | 3.3k | 1.54 MHz         | ± 14% |  |

|        | 5.1k | 980 kHz          | ± 12% |  |

|        | 10k  | 564 kHz          | ± 16% |  |

|        | 160k | 35 kHz           | ± 18% |  |

# PIC17C7XX

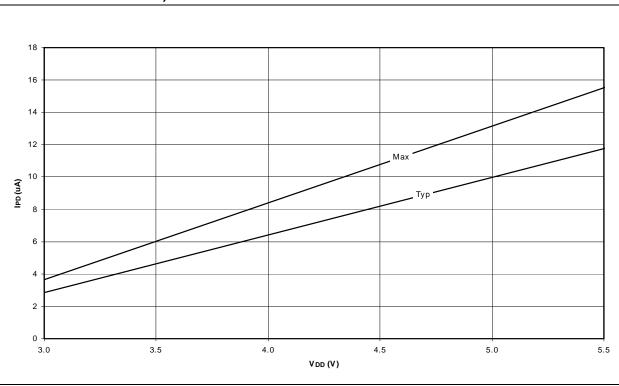

# FIGURE 21-13: TYPICAL AND MAXIMUM △IPD vs. VDD (SLEEP MODE, WDT ENABLED, -40°C to +125°C)

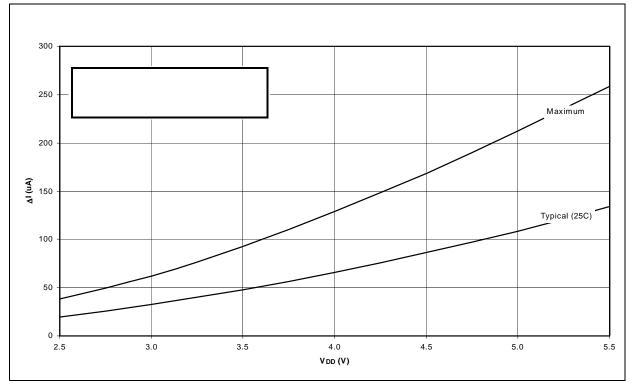

FIGURE 21-14: TYPICAL AND MAXIMUM △IRBPU vs. VDD (MEASURED PER INPUT PIN, -40°C TO +125°C)

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 1998-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769317

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.