Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 16MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 66                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 678 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                               |

| Data Converters            | A/D 16x10b                                                                |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 84-LCC (J-Lead)                                                           |

| Supplier Device Package    | 84-PLCC (29.31x29.31)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c762-16e-l |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 DEVICE VARIETIES

Each device has a variety of frequency ranges and packaging options. Depending on application and production requirements, the proper device option can be selected using the information in the PIC17C7XX Product Selection System section at the end of this data sheet. When placing orders, please use the "PIC17C7XX Product Identification System" at the back of this data sheet to specify the correct part number. When discussing the functionality of the device, memory technology and voltage range does not matter.

There are two memory type options. These are specified in the middle characters of the part number.

- 1. **C**, as in PIC17**C**756A. These devices have EPROM type memory.

- 2. **CR**, as in PIC17**CR**756A. These devices have ROM type memory.

All these devices operate over the standard voltage range. Devices are also offered which operate over an extended voltage range (and reduced frequency range). Table 2-1 shows all possible memory types and voltage range designators for a particular device. These designators are in **bold** typeface.

| Memory Type                                                              | Voltage Range      |             |  |  |

|--------------------------------------------------------------------------|--------------------|-------------|--|--|

| memory type                                                              | Standard           | Extended    |  |  |

| EPROM                                                                    | PIC17 <b>C</b> XXX | PIC17LCXXX  |  |  |

| ROM                                                                      | PIC17CRXXX         | PIC17LCRXXX |  |  |

| Note: Not all memory technologies are available for a particular device. |                    |             |  |  |

## 2.1 UV Erasable Devices

The UV erasable version, offered in CERQUAD package, is optimal for prototype development and pilot programs.

The UV erasable version can be erased and reprogrammed to any of the configuration modes. Third party programmers also are available; refer to the *Third Party Guide* for a list of sources.

## 2.2 One-Time-Programmable (OTP) Devices

The availability of OTP devices is especially useful for customers expecting frequent code changes and updates.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must be programmed.

## 2.3 Quick-Turnaround-Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

## 2.4 Serialized Quick-Turnaround Production (SQTP<sup>sm</sup>) Devices

Microchip offers a unique programming service, where a few user defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry code, password or ID number.

# 2.5 Read Only Memory (ROM) Devices

Microchip offers masked ROM versions of several of the highest volume parts, thus giving customers a low cost option for high volume, mature products.

ROM devices do not allow serialization information in the program memory space.

For information on submitting ROM code, please contact your regional sales office.

Note: Presently, NO ROM versions of the PIC17C7XX devices are available.

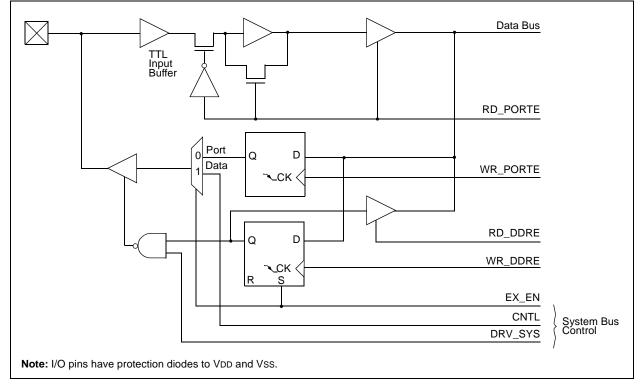

## 10.5 PORTE and DDRE Register

PORTE is a 4-bit bi-directional port. The corresponding data direction register is DDRE. A '1' in DDRE configures the corresponding port pin as an input. A '0' in the DDRE register configures the corresponding port pin as an output. Reading PORTE reads the status of the pins, whereas writing to PORTE will write to the port latch. PORTE is multiplexed with the system bus. When operating as the system bus, PORTE contains the control signals for the address/data bus (AD15:AD0). These control signals are Address Latch Enable (ALE), Output Enable (OE) and Write (WR). The control signals OE and WR are active low signals. The timing for the system bus is shown in the Electrical Specifications section.

**Note:** Three pins of this port are configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. The other pin is a general purpose I/O or Capture4 pin. In the two other microcontroller modes, RE2:RE0 are general purpose I/O pins. Example 10-5 shows an instruction sequence to initialize PORTE. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized. The following example uses the MOVLB instruction to load the BSR register for bank selection.

### EXAMPLE 10-5: INITIALIZING PORTE

| MOVLB | 1      |   | ; | Select Bank 1            |

|-------|--------|---|---|--------------------------|

| CLRF  | PORTE, | F | ; | Initialize PORTE data    |

|       |        |   | ; | latches before setting   |

|       |        |   | ; | the data direction       |

|       |        |   | ; | register                 |

| MOVLW | 0x03   |   | ; | Value used to initialize |

|       |        |   | ; | data direction           |

| MOVWF | DDRE   |   | ; | Set RE<1:0> as inputs    |

|       |        |   | ; | RE<3:2> as outputs       |

|       |        |   | ; | RE<7:4> are always       |

|       |        |   | ; | read as '0'              |

|       |        |   |   |                          |

## FIGURE 10-11: BLOCK DIAGRAM OF RE2:RE0 (IN I/O PORT MODE)

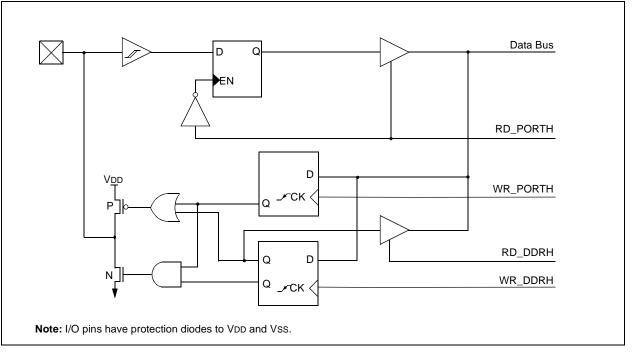

## FIGURE 10-18: RH3:RH0 BLOCK DIAGRAM

## TABLE 10-15: PORTH FUNCTIONS

| Name     | Bit  | Buffer Type | Function                         |  |

|----------|------|-------------|----------------------------------|--|

| RH0      | bit0 | ST          | Input/output.                    |  |

| RH1      | bit1 | ST          | Input/output.                    |  |

| RH2      | bit2 | ST          | Input/output.                    |  |

| RH3      | bit3 | ST          | Input/output.                    |  |

| RH4/AN12 | bit4 | ST          | Input/output or analog input 12. |  |

| RH5/AN13 | bit5 | ST          | Input/output or analog input 13. |  |

| RH6/AN14 | bit6 | ST          | Input/output or analog input 14. |  |

| RH7/AN15 | bit7 | ST          | Input/output or analog input 15. |  |

Legend: ST = Schmitt Trigger input

## TABLE 10-16: REGISTERS/BITS ASSOCIATED WITH PORTH

| Address     | Name   | Bit 7        | Bit 6                             | Bit 5        | Bit 4        | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | MCLR, WDT |

|-------------|--------|--------------|-----------------------------------|--------------|--------------|-------|-------|-------|-------|-------------------------|-----------|

| 10h, Bank 8 | DDRH   | Data Dire    | Data Direction Register for PORTH |              |              |       |       |       |       | 1111 1111               | 1111 1111 |

| 11h, Bank 8 | PORTH  | RH7/<br>AN15 | RH6/<br>AN14                      | RH5/<br>AN13 | RH4/<br>AN12 | RH3   | RH2   | RH1   | RH0   | 0000 xxxx               | 0000 uuuu |

| 15h, Bank 5 | ADCON1 | ADCS1        | ADCS0                             | ADFM         | _            | PCFG3 | PCFG2 | PCFG1 | PCFG0 | 000- 0000               | 000- 0000 |

Legend: x = unknown, u = unchanged

NOTES:

# 12.0 TIMER0

The Timer0 module consists of a 16-bit timer/counter, TMR0. The high byte is register TMR0H and the low byte is register TMR0L. A software programmable 8-bit prescaler makes Timer0 an effective 24-bit overflow timer. The clock source is software programmable as either the internal instruction clock, or an external clock on the RA1/T0CKI pin. The control bits for this module are in register T0STA (Figure 12-1).

## REGISTER 12-1: T0STA REGISTER (ADDRESS: 05h, UNBANKED)

|         | R/W-0                      | R/W-0                | R/W-0          | R/W-0         | R/W-0     | R/W-0                          | R/W-0       | U-0   |

|---------|----------------------------|----------------------|----------------|---------------|-----------|--------------------------------|-------------|-------|

|         | INTEDG                     | TOSE                 | TOCS           | T0PS3         | T0PS2     | T0PS1                          | T0PS0       | _     |

|         | bit 7                      |                      |                |               |           |                                |             | bit 0 |

|         |                            |                      |                |               |           |                                |             |       |

| bit 7   |                            | A0/INT Pin I         |                |               |           |                                |             |       |

|         |                            | ects the edge        |                |               |           | J.                             |             |       |

|         |                            | edge of RAC          |                |               |           |                                |             |       |

| bit 6   |                            | er0 Clock Inp        |                |               |           |                                |             |       |

|         | This bit sele              | ects the edge        | e upon whicł   | n TMR0 will i | ncrement. |                                |             |       |

|         |                            | S = 0 (Extern        |                | ·             |           |                                |             |       |

|         |                            |                      |                |               |           | sets the T0CK<br>sets the T0CK |             |       |

|         | -                          | <u>S = 1 (Intern</u> | -              |               |           |                                |             |       |

|         | Don't care                 | <u> </u>             | <u>a. 0.00</u> |               |           |                                |             |       |

| bit 5   |                            | er0 Clock So         |                |               |           |                                |             |       |

|         |                            | ects the cloc        |                |               |           |                                |             |       |

|         |                            | al clock input       |                |               |           |                                |             |       |

| bit 4-1 | T0PS3:T0F                  | <b>SO</b> : Timer0   | Prescale Se    | lection bits  |           |                                |             |       |

|         | These bits                 | select the pr        | escale value   | for TMR0.     |           |                                |             |       |

|         | T0PS3:T0                   | PS0 Presc            | ale Value      |               |           |                                |             |       |

|         | 0000                       | 1:                   |                |               |           |                                |             |       |

|         | 0001<br>0010               | 1:                   |                |               |           |                                |             |       |

|         | 0011                       | 1:                   | 8              |               |           |                                |             |       |

|         | 0100<br>0101               |                      | 16<br>32       |               |           |                                |             |       |

|         | 0110                       |                      | 64             |               |           |                                |             |       |

|         | 0111                       |                      | 128            |               |           |                                |             |       |

|         | 1xxx                       |                      | 256            |               |           |                                |             |       |

| bit 0   | Unimplemented: Read as '0' |                      |                |               |           |                                |             |       |

|         |                            |                      |                |               |           |                                |             |       |

|         | Legend:                    |                      |                |               |           |                                |             |       |

|         | R = Readat                 | ole bit              | W = W          | ritable bit   | U = Unin  | nplemented bit,                | read as '0' |       |

'1' = Bit is set

'0' = Bit is cleared

- n = Value at POR Reset

x = Bit is unknown

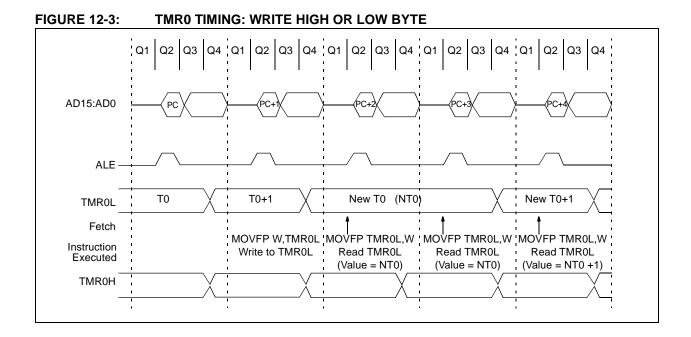

## 12.3 Read/Write Consideration for TMR0

Although TMR0 is a 16-bit timer/counter, only 8-bits at a time can be read or written during a single instruction cycle. Care must be taken during any read or write.

## 12.3.1 READING 16-BIT VALUE

The problem in reading the entire 16-bit value is that after reading the low (or high) byte, its value may change from FFh to 00h.

Example 12-1 shows a 16-bit read. To ensure a proper read, interrupts must be disabled during this routine.

EXAMPLE 12-1: 16-BIT READ

| MOVPF  | TMROL, | TMPLO | ;read low tmr0  |

|--------|--------|-------|-----------------|

| MOVPF  | TMROH, | TMPHI | ;read high tmr0 |

| MOVFP  | TMPLO, | WREG  | ;tmplo -> wreg  |

| CPFSLT | TMROL  |       | ;tmr0l < wreg?  |

| RETURN |        |       | ;no then return |

| MOVPF  | TMROL, | TMPLO | ;read low tmr0  |

| MOVPF  | TMROH, | TMPHI | ;read high tmr0 |

| RETURN |        |       | ;return         |

|        |        |       |                 |

## 12.3.2 WRITING A 16-BIT VALUE TO TMR0

Since writing to either TMR0L or TMR0H will effectively inhibit increment of that half of the TMR0 in the next cycle (following write), but not inhibit increment of the other half, the user must write to TMR0L first and TMR0H second, in two consecutive instructions, as shown in Example 12-2. The interrupt must be disabled. Any write to either TMR0L or TMR0H clears the prescaler.

### EXAMPLE 12-2: 16-BIT WRITE

| BSF   | CPUSTA, GLINTD ; Disable interrupts |

|-------|-------------------------------------|

| MOVFP | RAM_L, TMROL ;                      |

| MOVFP | RAM_H, TMROH ;                      |

| BCF   | CPUSTA, GLINTD ; Done, enable       |

|       | ; interrupts                        |

|       |                                     |

## 12.4 Prescaler Assignments

Timer0 has an 8-bit prescaler. The prescaler selection is fully under software control; i.e., it can be changed "on the fly" during program execution. Clearing the prescaler is recommended before changing its setting. The value of the prescaler is "unknown" and assigning a value that is less than the present value, makes it difficult to take this unknown time into account.

|         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R-0         | R-0      | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|--------|--------|--------|--------|--------|

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CA4OVF      | CA3OVF   | CA4ED1 | CA4ED0 | CA3ED1 | CA3ED0 | PWM3ON |

|         | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |          |        |        |        |        | bit 0  |

| bit 7   | Unimplen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | nented: Rea | d as '0' |        |        |        |        |        |

| bit 6   | <b>CA4OVF</b> : Capture4 Overflow Status bit<br>This bit indicates that the capture value had not been read from the capture register pair<br>(CA4H:CA4L) before the next capture event occurred. The capture register retains the oldest<br>unread capture value (last capture before overflow). Subsequent capture events will not update<br>the capture register with the TMR3 value until the capture register has been read (both bytes).<br>1 = Overflow occurred on Capture4 registers<br>0 = No overflow occurred on Capture4 registers |             |          |        |        |        |        |        |

| bit 5   | <b>CA3OVF</b> : Capture3 Overflow Status bit<br>This bit indicates that the capture value had not been read from the capture register pair<br>(CA3H:CA3L) before the next capture event occurred. The capture register retains the oldest<br>unread capture value (last capture before overflow). Subsequent capture events will not update<br>the capture register with the TMR3 value until the capture register has been read (both bytes).<br>1 = Overflow occurred on Capture3 registers                                                   |             |          |        |        |        |        |        |

| bit 4-3 | <ul> <li>0 = No overflow occurred on Capture3 registers</li> <li>CA4ED1:CA4ED0: Capture4 Mode Select bits</li> <li>00 = Capture on every falling edge</li> <li>01 = Capture on every rising edge</li> <li>10 = Capture on every 4th rising edge</li> <li>11 = Capture on every 16th rising edge</li> </ul>                                                                                                                                                                                                                                      |             |          |        |        |        |        |        |

| bit 2-1 | CA3ED1:CA3ED0: Capture3 Mode Select bits<br>00 = Capture on every falling edge<br>01 = Capture on every rising edge<br>10 = Capture on every 4th rising edge<br>11 = Capture on every 16th rising edge                                                                                                                                                                                                                                                                                                                                          |             |          |        |        |        |        |        |

| bit 0   | <ul> <li>PWM3ON: PWM3 On bit</li> <li>PWM3 is enabled (the RG5/PWM3 pin ignores the state of the DDRG&lt;5&gt; bit)</li> <li>PWM3 is disabled (the RG5/PWM3 pin uses the state of the DDRG&lt;5&gt; bit for data direction)</li> </ul>                                                                                                                                                                                                                                                                                                          |             |          |        |        |        |        |        |

|         | Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |          |        |        |        |        |        |

'1' = Bit is set

'0' = Bit is cleared

# REGISTER 13-3: TCON3 REGISTER (ADDRESS: 16h, BANK 7)

- n = Value at POR Reset

x = Bit is unknown

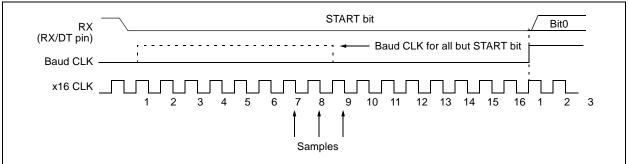

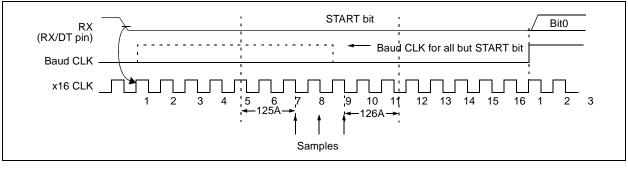

### 14.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 14-2. The data comes in the RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at 16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the receive (serial) shift register (RSR). After sampling the STOP bit, the received data in the RSR is transferred to the RCREG (if it is empty). If the transfer is complete, the interrupt bit, RCIF, is set. The actual interrupt can be enabled/ disabled by setting/clearing the RCIE bit. RCIF is a read only bit which is cleared by the hardware. It is cleared when RCREG has been read and is empty. RCREG is a double buffered register (i.e., it is a twodeep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte begin shifting to the RSR. On detection of the STOP bit of the third byte, if the RCREG is still full, then the overrun error bit, OERR (RCSTA<1>) will be set. The word in the RSR will be lost. RCREG can be read twice to retrieve the two bytes in the FIFO. The OERR bit has to be cleared in software which is done by reset-

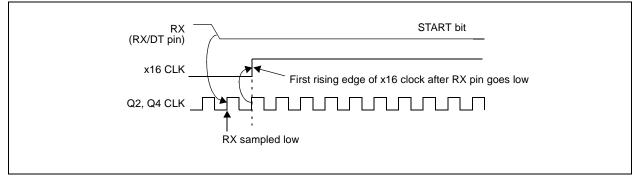

FIGURE 14-5: RX PIN SAMPLING SCHEME

ting the receive logic (CREN is set). If the OERR bit is set, transfers from the RSR to RCREG are inhibited, so it is essential to clear the OERR bit if it is set. The framing error bit FERR (RCSTA<2>) is set if a STOP bit is not detected.

Note: The FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG register will allow the RX9D and FERR bits to be loaded with values for the next received data. Therefore, it is essential for the user to read the RCSTA register before reading RCREG, in order not to lose the old FERR and RX9D information.

## 14.2.3 SAMPLING

The data on the RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX/DT pin. The sampling is done on the seventh, eighth and ninth falling edges of a x16 clock (Figure 14-5).

The x16 clock is a free running clock and the three sample points occur at a frequency of every 16 falling edges.

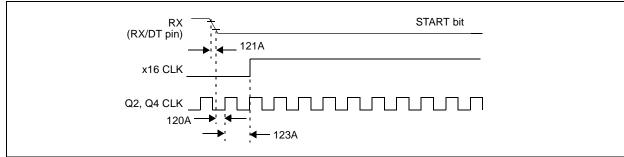

## FIGURE 14-6: START BIT DETECT

## 15.4 Example Program

Example 15-2 shows MPLAB<sup>®</sup> C17 'C' code for using the I<sup>2</sup>C module in Master mode to communicate with a 24LC01B serial EEPROM. This example uses the PIC<sup>®</sup> MCU 'C' libraries included with MPLAB C17.

### EXAMPLE 15-2: INTERFACING TO A 24LC01B SERIAL EEPROM (USING MPLAB C17)

```

// Include necessary header files

#include <p17c756.h>

// Processor header file

// Delay routines header file

// Standard Library header file

#include <delays.h>

#include <stdlib.h>

// Standard Lizzard

// I2C routines header file

#include <i2c16.h>

#define CONTROL 0xa0

// Control byte definition for 24LC01B

// Function declarations

void main(void);

void WritePORTD(static unsigned char data);

void ByteWrite(static unsigned char address, static unsigned char data);

unsigned char ByteRead(static unsigned char address);

void ACKPoll(void);

// Main program

void main(void)

{

static unsigned char address; // I2C address of 24LC01B

static unsigned char datao; // Data written to 24LC01B

static unsigned char datai;

// Data read from 24LC01B

// Preset address to 0

address = 0;

OpenI2C(MASTER,SLEW_ON);

// Configure I2C Module Master mode, Slew rate control on

SSPADD = 39;

// Configure clock for 100KHz

while(address<128)

// Loop 128 times, 24LC01B is 128x8

{

datao = PORTB;

do

{

ByteWrite(address,datao); // Write data to EEPROM

ACKPoll();

// Poll the 24LC01B for state

datai = ByteRead(address); // Read data from EEPROM into SSPBUF

while(datai != datao);

// Loop as long as data not correctly

11

written to 24LC01B

address++;

// Increment address

}

while(1)

// Done writing 128 bytes to 24LC01B, Loop forever

{

Nop();

}

```

NOTES:

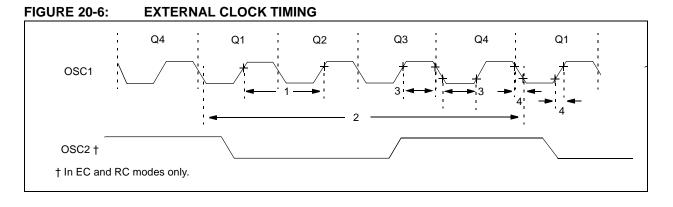

## 20.4 Timing Diagrams and Specifications

## TABLE 20-1: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic         | Min   | Тур†   | Max   | Units | Conditions                                      |

|--------------|-------|------------------------|-------|--------|-------|-------|-------------------------------------------------|

|              | Fosc  | External CLKIN         | DC    |        | 8     | MHz   | EC osc mode - 08 devices (8 MHz devices)        |

|              |       | Frequency (Note 1)     | DC    | —      | 16    | MHz   | - 16 devices (16 MHz devices)                   |

|              |       |                        | DC    | —      | 33    | MHz   | - 33 devices (33 MHz devices)                   |

|              |       | Oscillator Frequency   | DC    | _      | 4     | MHz   | RC osc mode                                     |

|              |       | (Note 1)               | 2     | —      | 8     | MHz   | XT osc mode - 08 devices (8 MHz devices)        |

|              |       |                        | 2     | —      | 16    | MHz   | - 16 devices (16 MHz devices)                   |

|              |       |                        | 2     | —      | 33    | MHz   | - 33 devices (33 MHz devices)                   |

|              |       |                        | DC    | —      | 2     | MHz   | LF osc mode                                     |

| 1            | Tosc  | External CLKIN Period  | 125   | Ι      |       | ns    | EC osc mode - 08 devices (8 MHz devices)        |

|              |       | (Note 1)               | 62.5  | —      | —     | ns    | - 16 devices (16 MHz devices)                   |

|              |       |                        | 30.3  | _      | —     | ns    | - 33 devices (33 MHz devices)                   |

|              |       | Oscillator Period      | 250   |        |       | ns    | RC osc mode                                     |

|              |       | (Note 1)               | 125   | —      | 1,000 | ns    | XT osc mode - 08 devices (8 MHz devices)        |

|              |       |                        | 62.5  | —      | 1,000 | ns    | <ul> <li>16 devices (16 MHz devices)</li> </ul> |

|              |       |                        | 30.3  | —      | 1,000 | ns    | - 33 devices (33 MHz devices)                   |

|              |       |                        | 500   | —      | —     | ns    | LF osc mode                                     |

| 2            | Тсү   | Instruction Cycle Time | 121.2 | 4/Fosc | DC    | ns    |                                                 |

|              |       | (Note 1)               |       |        |       |       |                                                 |

| 3            | TosL, | Clock in (OSC1)        | 10    | _      | _     | ns    | EC oscillator                                   |

|              | TosH  | High or Low Time       |       |        |       |       |                                                 |

| 4            | TosR, | Clock in (OSC1)        | _     | _      | 5     | ns    | EC oscillator                                   |

|              | TosF  | Rise or Fall Time      |       |        |       |       |                                                 |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

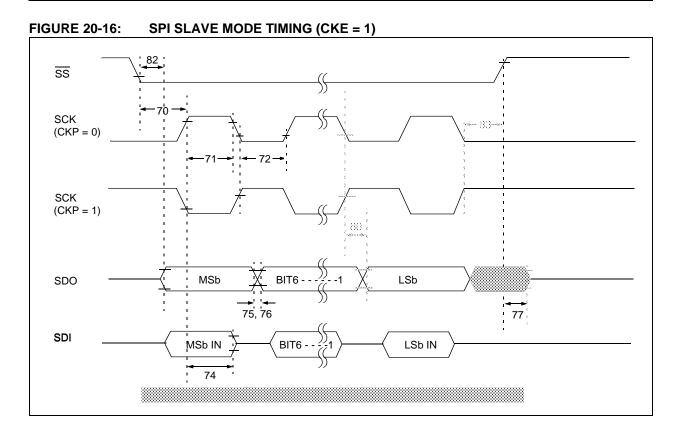

| TABLE 20-11: | SPI MODE REQUIREMENTS (SLAVE MODE, CKE = 1) |

|--------------|---------------------------------------------|

|--------------|---------------------------------------------|

| Param.<br>No. | Symbol                | Characteristic                                                        |             | Min          | Тур† | Max | Units | Conditions |

|---------------|-----------------------|-----------------------------------------------------------------------|-------------|--------------|------|-----|-------|------------|

| 70            | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | Тсу         | —            | —    | ns  |       |            |

| 71            | TscH                  | SCK input high time                                                   | Continuous  | 1.25Tcy + 30 |      | —   | ns    |            |

| 71A           |                       | (Slave mode)                                                          | Single Byte | 40           |      | —   | ns    | (Note 1)   |

| 72            | TscL                  | SCK input low time                                                    | Continuous  | 1.25Tcy + 30 |      | —   | ns    |            |

| 72A           |                       | (Slave mode)                                                          | Single Byte | 40           |      | _   | ns    | (Note 1)   |

| 73A           | Тв2в                  | Last clock edge of Byte1 to the 1st clock edge of Byte2               |             | 1.5Tcy + 40  | —    | _   | ns    | (Note 1)   |

| 74            | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                               |             | 100          | —    | _   | ns    |            |

| 75            | TdoR                  | SDO data output rise time                                             |             | _            | 10   | 25  | ns    |            |

| 76            | TdoF                  | SDO data output fall time                                             |             | _            | 10   | 25  | ns    |            |

| 77            | TssH2doZ              | SS <sup>↑</sup> to SDO output hi-impedan                              | се          | 10           |      | 50  | ns    |            |

| 80            | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge                                  |             |              | —    | 50  | ns    |            |

| 82            | TssL2doV              | SDO data output valid after SS                                        | _           | _            | 50   | ns  |       |            |

| 83            | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                                   | 1.5Tcy + 40 | —            | _    | ns  |       |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated.

**Note 1:** Specification 73A is only required if specifications 71A and 72A are used.

## FIGURE 20-21: USART ASYNCHRONOUS MODE START BIT DETECT

### TABLE 20-16: USART ASYNCHRONOUS MODE START BIT DETECT REQUIREMENTS

| Param<br>No. | Sym       | Characteristic                                                 |          | Min | Тур | Max      | Unit<br>s | Conditions |

|--------------|-----------|----------------------------------------------------------------|----------|-----|-----|----------|-----------|------------|

| 120A         | TdtL2ckH  | Time to ensure that the RX pin is sampled low                  |          |     | _   | TCY      | ns        |            |

| 121A         | TdtRF     | Data rise time and fall time                                   | Receive  | _   | —   | (Note 1) | ns        |            |

|              |           |                                                                | Transmit | _   | _   | 40       | ns        |            |

| 123A         | TckH2bckL | Time from RX pin sampled low to first rising edge of x16 clock |          | _   | _   | Тсү      | ns        |            |

Note 1: Schmitt trigger will determine logic level.

## FIGURE 20-22: USART ASYNCHRONOUS RECEIVE SAMPLING WAVEFORM

## TABLE 20-17: USART ASYNCHRONOUS RECEIVE SAMPLING REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                                  | Min | Тур | Max | Unit<br>s | Conditions |

|--------------|----------|-------------------------------------------------|-----|-----|-----|-----------|------------|

| 125A         | TdtL2ckH | Setup time of RX pin to first data sampled      | TCY | —   |     | ns        |            |

| 126A         | TdtL2ckH | Hold time of RX pin from last data sam-<br>pled | Тсү |     |     | ns        |            |

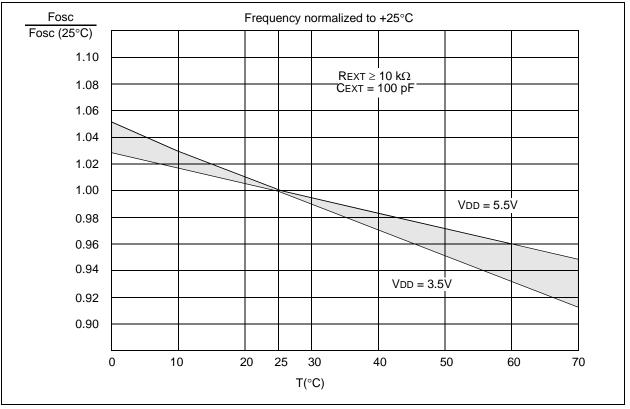

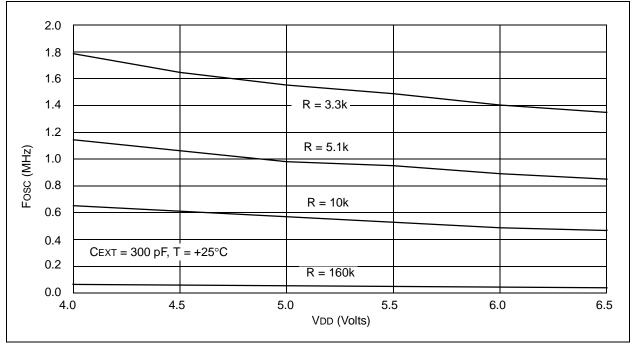

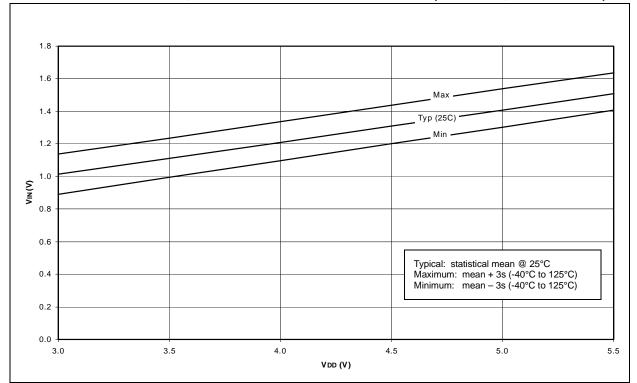

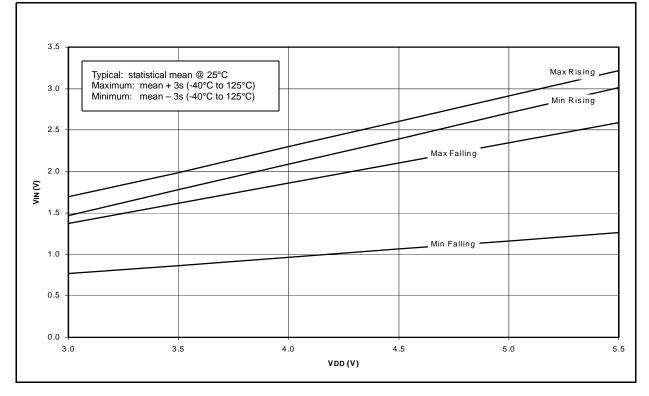

# 21.0 PIC17C7XX DC AND AC CHARACTERISTICS

The graphs and tables provided in this section are for design guidance and are not tested nor guaranteed. In some graphs or tables the data presented is outside specified operating range (e.g., outside specified VDD range). This is for information only and devices are ensured to operate properly only within the specified range.

The data presented in this section is a statistical summary of data collected on units from different lots over a period of time.

- Typ or Typical represents the mean of the distribution at 25°C.

- Max or Maximum represents (mean + 3 $\sigma$ ) over the temperature range of -40°C to 85°C.

- Min or Minimum represents (mean  $3\sigma$ ) over the temperature range of -40°C to  $85^{\circ}$ C.

- **Note:** Standard deviation is denoted by sigma ( $\sigma$ ).

### TABLE 21-1: PIN CAPACITANCE PER PACKAGE TYPE

| Pin Name                            | Typical Capacitance (pF) |             |  |  |  |

|-------------------------------------|--------------------------|-------------|--|--|--|

|                                     | 68-pin PLCC              | 64-pin TQFP |  |  |  |

| All pins, except MCLR, VDD, and Vss | 10                       | 10          |  |  |  |

| MCLR pin                            | 20                       | 20          |  |  |  |

### FIGURE 21-1: TYPICAL RC OSCILLATOR FREQUENCY vs. TEMPERATURE

## TABLE 21-2: RC OSCILLATOR FREQUENCIES

| Сехт   | Rext |          | rage<br>5V, +25°C |

|--------|------|----------|-------------------|

| 22 pF  | 10k  | 3.33 MHz | ± 12%             |

|        | 100k | 353 kHz  | ± 13%             |

| 100 pF | 3.3k | 3.54 MHz | ± 10%             |

|        | 5.1k | 2.43 MHz | ± 14%             |

|        | 10k  | 1.30 MHz | ± 17%             |

|        | 100k | 129 kHz  | ± 10%             |

| 300 pF | 3.3k | 1.54 MHz | ± 14%             |

|        | 5.1k | 980 kHz  | ± 12%             |

|        | 10k  | 564 kHz  | ± 16%             |

|        | 160k | 35 kHz   | ± 18%             |

FIGURE 21-21: TYPICAL, MAXIMUM AND MINIMUM VIN vs. VDD (TTL INPUT, -40°C to 125°C)

# Package Marking Information (Cont.)

84-Lead PLCC

Example

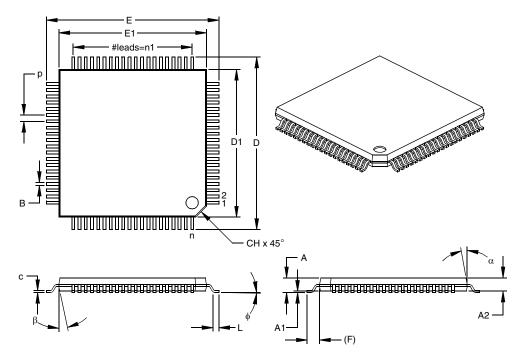

### 80-Lead Plastic Thin Quad Flatpack (PT) 12x12x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                          | Units |      |      | INCHES |       |       | MILLIMETERS* |  |  |  |

|--------------------------|-------|------|------|--------|-------|-------|--------------|--|--|--|

| Dimensio                 | MIN   | NOM  | MAX  | MIN    | NOM   | MAX   |              |  |  |  |

| Number of Pins           | n     |      | 80   |        |       | 80    |              |  |  |  |

| Pitch                    | р     |      | .020 |        |       | 0.50  |              |  |  |  |

| Pins per Side            | n1    |      | 20   |        |       | 20    |              |  |  |  |

| Overall Height           | Α     | .039 | .043 | .047   | 1.00  | 1.10  | 1.20         |  |  |  |

| Molded Package Thickness | A2    | .037 | .039 | .041   | 0.95  | 1.00  | 1.05         |  |  |  |

| Standoff §               | A1    | .002 | .004 | .006   | 0.05  | 0.10  | 0.15         |  |  |  |

| Foot Length              | L     | .018 | .024 | .030   | 0.45  | 0.60  | 0.75         |  |  |  |

| Footprint (Reference)    | (F)   |      | .039 |        |       | 1.00  |              |  |  |  |

| Foot Angle               | ф     | 0    | 3.5  | 7      | 0     | 3.5   | 7            |  |  |  |

| Overall Width            | Е     | .541 | .551 | .561   | 13.75 | 14.00 | 14.25        |  |  |  |

| Overall Length           | D     | .541 | .551 | .561   | 13.75 | 14.00 | 14.25        |  |  |  |

| Molded Package Width     | E1    | .463 | .472 | .482   | 11.75 | 12.00 | 12.25        |  |  |  |

| Molded Package Length    | D1    | .463 | .472 | .482   | 11.75 | 12.00 | 12.25        |  |  |  |

| Lead Thickness           | С     | .004 | .006 | .008   | 0.09  | 0.15  | 0.20         |  |  |  |

| Lead Width               | В     | .007 | .009 | .011   | 0.17  | 0.22  | 0.27         |  |  |  |

| Pin 1 Corner Chamfer     | CH    | .025 | .035 | .045   | 0.64  | 0.89  | 1.14         |  |  |  |

| Mold Draft Angle Top     | α     | 5    | 10   | 15     | 5     | 10    | 15           |  |  |  |

| Mold Draft Angle Bottom  | β     | 5    | 10   | 15     | 5     | 10    | 15           |  |  |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-026 Drawing No. C04-092

NOTES: