Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 33MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 66                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 678 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                               |

| Data Converters            | A/D 16x10b                                                                |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 84-LCC (J-Lead)                                                           |

| Supplier Device Package    | 84-PLCC (29.31x29.31)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c762-33e-l |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 5.0 RESET

The PIC17CXXX differentiates between various kinds of RESET:

- Power-on Reset (POR)

- Brown-out Reset

- MCLR Reset

- WDT Reset

Some registers are not affected in any RESET condition, their status is unknown on POR and unchanged in any other RESET. Most other registers are forced to a "RESET state". The TO and PD bits are set or cleared differently in different RESET situations, as indicated in Table 5-3. These bits, in conjunction with the POR and BOR bits, are used in software to determine the nature of the RESET. See Table 5-4 for a full description of the RESET states of all registers.

When the device enters the "RESET state", the Data Direction registers (DDR) are forced set, which will make the I/O hi-impedance inputs. The RESET state of some peripheral modules may force the I/O to other operations, such as analog inputs or the system bus.

**Note:** While the device is in a RESET state, the internal phase clock is held in the Q1 state. Any processor mode that allows external execution will force the RE0/ALE pin as a low output and the RE1/OE and RE2/WR pins as high outputs.

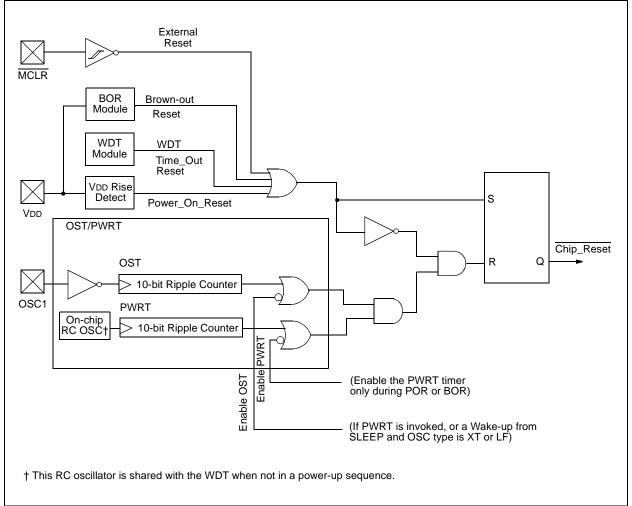

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 5-1.

# FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

Bank 8<sup>(1,4)</sup>

DDRH PORTH

DDRJ

PORTJ

\_

\_

\_

\_

#### FIGURE 7-5: PIC17C7XX REGISTER FILE MAP

| Addr | Unbanked              |                       |                       |                         |      |

|------|-----------------------|-----------------------|-----------------------|-------------------------|------|

| 00h  | INDF0                 |                       |                       |                         |      |

| 01h  | FSR0                  |                       |                       |                         |      |

| 02h  | PCL                   |                       |                       |                         |      |

| 03h  | PCLATH                |                       |                       |                         |      |

| 04h  | ALUSTA                |                       |                       |                         |      |

| 05h  | TOSTA                 |                       |                       |                         |      |

| 06h  | CPUSTA                |                       |                       |                         |      |

| 07h  | INTSTA                |                       |                       |                         |      |

| 08h  | INDF1                 |                       |                       |                         |      |

| 09h  | FSR1                  |                       |                       |                         |      |

| 0Ah  | WREG                  |                       |                       |                         |      |

| 0Bh  | TMR0L                 |                       |                       |                         |      |

| 0Ch  | TMR0H                 |                       |                       |                         |      |

| 0Dh  | TBLPTRL               |                       |                       |                         |      |

| 0Eh  | TBLPTRH               |                       |                       |                         |      |

| 0Fh  | BSR                   |                       |                       |                         |      |

|      | Bank 0                | Bank 1 <sup>(1)</sup> | Bank 2 <sup>(1)</sup> | Bank 3 <sup>(1)</sup>   | Bank |

| 10h  | PORTA                 | DDRC                  | TMR1                  | PW1DCL                  | PIR  |

| 11h  | DDRB                  | PORTC                 | TMR2                  | PW2DCL                  | PIE  |

| 12h  | PORTB                 | DDRD                  | TMR3L                 | PW1DCH                  | —    |

| 13h  | RCSTA1                | PORTD                 | TMR3H                 | PW2DCH                  | RCST |

| 14h  | RCREG1                | DDRE                  | PR1                   | CA2L                    | RCRE |

| 15h  | TXSTA1                | PORTE                 | PR2                   | CA2H                    | TXST |

| 16h  | TXREG1                | PIR1                  | PR3L/CA1L             | TCON1                   | TXRE |

| 17h  | SPBRG1                | PIE1                  | PR3H/CA1H             | TCON2                   | SPBR |

|      | Unbanked              |                       |                       |                         |      |

| 18h  | PRODL                 |                       |                       |                         |      |

| 19h  | PRODH                 |                       |                       |                         |      |

| 1Ah  | General               |                       |                       |                         |      |

|      | Purpose               |                       |                       |                         |      |

| 1Fh  | RAM                   |                       | 1                     |                         | 1    |

|      | Bank 0 <sup>(2)</sup> | Bank 1 <sup>(2)</sup> | Bank 2 <sup>(2)</sup> | Bank 3 <sup>(2,3)</sup> |      |

| 20h  |                       |                       |                       |                         | 1    |

|      | General               | General               | General               | General                 |      |

|      | Purpose               | Purpose               | Purpose               | Purpose                 |      |

|      | RAM                   | RAM                   | RAM                   | RAM                     |      |

|      |                       |                       |                       |                         |      |

| FFh  |                       |                       |                       |                         |      |

Note 1: SFR file locations 10h - 17h are banked. The lower nibble of the BSR specifies the bank. All unbanked SFRs ignore the Bank Select Register (BSR) bits.

2: General Purpose Registers (GPR) locations 20h - FFh, 120h - 1FFh, 220h - 2FFh, and 320h - 3FFh are banked. The upper nibble of the BSR specifies this bank. All other GPRs ignore the Bank Select Register (BSR) bits.

Bank 5<sup>(1)</sup>

DDRF

PORTF

DDRG

PORTG

ADCON0

ADCON1

ADRESL

ADRESH

Bank 6<sup>(1)</sup>

SSPADD

SSPCON1

SSPCON2

SSPSTAT

SSPBUF

\_

\_

\_

Bank 7<sup>(1)</sup>

PW3DCL

PW3DCH

CA3L

CA3H

CA4L

CA4H

TCON3

\_

3: RAM bank 3 is not implemented on the PIC17C752 and the PIC17C762. Reading any unimplemented register reads '0's.

4: Bank 8 is only implemented on the PIC17C76X devices.

# 7.3 Stack Operation

PIC17C7XX devices have a 16 x 16-bit hardware stack (Figure 7-1). The stack is not part of either the program or data memory space, and the stack pointer is neither readable nor writable. The PC (Program Counter) is "PUSH'd" onto the stack when a CALL or LCALL instruction is executed, or an interrupt is acknowledged. The stack is "POP'd" in the event of a RETURN, RETLW, or a RETFIE instruction execution. PCLATH is not affected by a "PUSH" or a "POP" operation.

The stack operates as a circular buffer, with the stack pointer initialized to '0' after all RESETS. There is a stack available bit (STKAV) to allow software to ensure that the stack will not overflow. The STKAV bit is set after a device RESET. When the stack pointer equals Fh, STKAV is cleared. When the stack pointer rolls over from Fh to 0h, the STKAV bit will be held clear until a device RESET.

- **Note 1:** There is not a status bit for stack underflow. The STKAV bit can be used to detect the underflow which results in the stack pointer being at the Top-of-Stack.

- 2: There are no instruction mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt vector.

- 3: After a RESET, if a "POP" operation occurs before a "PUSH" operation, the STKAV bit will be cleared. This will appear as if the stack is full (underflow has occurred). If a "PUSH" operation occurs next (before another "POP"), the STKAV bit will be locked clear. Only a device RESET will cause this bit to set.

After the device is "PUSH'd" sixteen times (without a "POP"), the seventeenth push overwrites the value from the first push. The eighteenth push overwrites the second push (and so on).

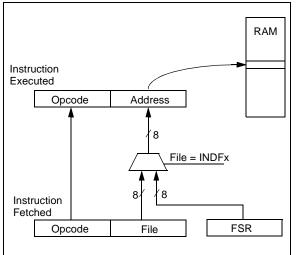

## 7.4 Indirect Addressing

Indirect addressing is a mode of addressing data memory where the data memory address in the instruction is not fixed. That is, the register that is to be read or written can be modified by the program. This can be useful for data tables in the data memory. Figure 7-6 shows the operation of indirect addressing. This depicts the moving of the value to the data memory address specified by the value of the FSR register.

Example 7-1 shows the use of indirect addressing to clear RAM in a minimum number of instructions. A similar concept could be used to move a defined number of bytes (block) of data to the USART transmit register (TXREG). The starting address of the block of data to be transmitted could easily be modified by the program.

## FIGURE 7-6: INDIRECT ADDRESSING

## 7.4.1 INDIRECT ADDRESSING REGISTERS

The PIC17C7XX has four registers for indirect addressing. These registers are:

- INDF0 and FSR0

- INDF1 and FSR1

Registers INDF0 and INDF1 are not physically implemented. Reading or writing to these registers activates indirect addressing, with the value in the corresponding FSR register being the address of the data. The FSR is an 8-bit register and allows addressing anywhere in the 256-byte data memory address range. For banked memory, the bank of memory accessed is specified by the value in the BSR.

If file INDF0 (or INDF1) itself is read indirectly via an FSR, all '0's are read (Zero bit is set). Similarly, if INDF0 (or INDF1) is written to indirectly, the operation will be equivalent to a NOP, and the status bits are not affected.

## TABLE 10-17: PORTJ FUNCTIONS

| Name | Bit  | Buffer Type | Function     |

|------|------|-------------|--------------|

| RJ0  | bit0 | ST          | Input/output |

| RJ1  | bit1 | ST          | Input/output |

| RJ2  | bit2 | ST          | Input/output |

| RJ3  | bit3 | ST          | Input/output |

| RJ4  | bit4 | ST          | Input/output |

| RJ5  | bit5 | ST          | Input/output |

| RJ6  | bit6 | ST          | Input/output |

| RJ7  | bit7 | ST          | Input/output |

Legend: ST = Schmitt Trigger input

# TABLE 10-18: REGISTERS/BITS ASSOCIATED WITH PORTJ

| Address     | Name  | Bit 7  | Bit 6                             | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on,<br>POR,<br>BOR | MCLR,<br>WDT |

|-------------|-------|--------|-----------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|--------------|

| 12h, Bank 8 | DDRJ  | Data D | Data Direction Register for PORTJ |       |       |       |       |       |       | 1111 1111                | 1111 1111    |

| 13h, Bank 8 | PORTJ | RJ7    | RJ6                               | RJ5   | RJ4   | RJ3   | RJ2   | RJ1   | RJ0   | xxxx xxxx                | uuuu uuuu    |

Legend: x = unknown, u = unchanged

# PIC17C7XX

NOTES:

# 12.0 TIMER0

The Timer0 module consists of a 16-bit timer/counter, TMR0. The high byte is register TMR0H and the low byte is register TMR0L. A software programmable 8-bit prescaler makes Timer0 an effective 24-bit overflow timer. The clock source is software programmable as either the internal instruction clock, or an external clock on the RA1/T0CKI pin. The control bits for this module are in register T0STA (Figure 12-1).

## REGISTER 12-1: T0STA REGISTER (ADDRESS: 05h, UNBANKED)

|         | R/W-0         | R/W-0                | R/W-0          | R/W-0         | R/W-0     | R/W-0                          | R/W-0       | U-0   |

|---------|---------------|----------------------|----------------|---------------|-----------|--------------------------------|-------------|-------|

|         | INTEDG        | TOSE                 | TOCS           | T0PS3         | T0PS2     | T0PS1                          | T0PS0       | _     |

|         | bit 7         |                      |                |               |           |                                |             | bit 0 |

|         |               |                      |                |               |           |                                |             |       |

| bit 7   |               | A0/INT Pin I         |                |               |           |                                |             |       |

|         |               | ects the edge        |                |               |           | J.                             |             |       |

|         |               | edge of RAC          |                |               |           |                                |             |       |

| bit 6   |               | er0 Clock Inp        |                |               |           |                                |             |       |

|         | This bit sele | ects the edge        | e upon whicł   | n TMR0 will i | ncrement. |                                |             |       |

|         |               | S = 0 (Extern        |                | ·             |           |                                |             |       |

|         |               |                      |                |               |           | sets the T0CK<br>sets the T0CK |             |       |

|         | -             | <u>S = 1 (Intern</u> | -              |               |           |                                |             |       |

|         | Don't care    | <u> </u>             | <u>a. 0.00</u> |               |           |                                |             |       |

| bit 5   |               | er0 Clock So         |                |               |           |                                |             |       |

|         |               | ects the cloc        |                |               |           |                                |             |       |

|         |               | al clock input       |                |               |           |                                |             |       |

| bit 4-1 | T0PS3:T0F     | <b>SO</b> : Timer0   | Prescale Se    | lection bits  |           |                                |             |       |

|         | These bits    | select the pr        | escale value   | for TMR0.     |           |                                |             |       |

|         | T0PS3:T0      | PS0 Presc            | ale Value      |               |           |                                |             |       |

|         | 0000          | 1:                   |                |               |           |                                |             |       |

|         | 0001<br>0010  | 1:                   |                |               |           |                                |             |       |

|         | 0011          | 1:                   | 8              |               |           |                                |             |       |

|         | 0100<br>0101  |                      | 16<br>32       |               |           |                                |             |       |

|         | 0110          |                      | 64             |               |           |                                |             |       |

|         | 0111          |                      | 128            |               |           |                                |             |       |

|         | 1xxx          |                      | 256            |               |           |                                |             |       |

| bit 0   | Unimplem      | ented: Read          | as '0'         |               |           |                                |             |       |

|         |               |                      |                |               |           |                                |             |       |

|         | Legend:       |                      |                |               |           |                                |             |       |

|         | R = Readat    | ole bit              | W = W          | ritable bit   | U = Unin  | nplemented bit,                | read as '0' |       |

'1' = Bit is set

'0' = Bit is cleared

- n = Value at POR Reset

x = Bit is unknown

### REGISTER 15-2: SSPCON1: SYNC SERIAL PORT CONTROL REGISTER1 (ADDRESS 11h, BANK 6)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WCOL  | SSPOV | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7 WCOL: Write Collision Detect bit

Master mode:

1 = A write to the SSPBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started

0 = No collision

<u>Slave mode:</u>

1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)

0 = No collision

bit 6

SSPOV: Receive Overflow Indicator bit

In SPI mode:

- 1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in Slave mode. In Slave mode, the user must read the SSPBUF, even if only transmitting data, to avoid setting overflow. In Master mode, the overflow bit is not set, since each new reception (and transmission) is initiated by writing to the SSPBUF register. (Must be cleared in software.)

- 0 = No overflow

- In I<sup>2</sup>C mode:

- 1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit mode. (Must be cleared in software.)

- 0 = No overflow

bit 5 SSPEN: Synchronous Serial Port Enable bit

In both modes, when enabled, these pins must be properly configured as input or output.

In SPI mode:

1 = Enables serial port and configures SCK, SDO, SDI and  $\overline{SS}$  as the source of the serial port pins 0 = Disables serial port and configures these pins as I/O port pins

In I<sup>2</sup>C mode:

- 1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins 0 = Disables serial port and configures these pins as I/O port pins

- **Note:** In SPI mode, these pins must be properly configured as input or output.

bit 4 **CKP**: Clock Polarity Select bit

In SPI mode: 1 = Idle state for clock is a high level 0 = Idle state for clock is a low level

- In I<sup>2</sup>C Slave mode: SCK release control

- 1 = Enable clock

0 = Holds clock low (clock stretch). (Used to ensure data setup time.)

In I<sup>2</sup>C Master mode:

Unused in this mode

bit 3-0 SSPM3:SSPM0: Synchronous Serial Port Mode Select bits

- 0000 = SPI Master mode, clock = Fosc/4

- 0001 = SPI Master mode, clock = FOSC/16

- 0010 = SPI Master mode, clock = FOSC/64

- 0011 = SPI Master mode, clock = TMR2 output/2

- 0100 = SPI Slave mode, clock = SCK pin,  $\overline{SS}$  pin control enabled

- 0101 =SPI Slave mode, clock = SCK pin,  $\overline{SS}$  pin control disabled,  $\overline{SS}$  can be used as I/O pin

- $0110 = I^2C$  Slave mode, 7-bit address

- $0111 = I^2C$  Slave mode, 10-bit address

- $1000 = I^2C$  Master mode, clock = Fosc / (4 \* (SSPADD+1))

- 1xx1 = Reserved

- 1x1x = Reserved

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| - n = Value at POR Reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

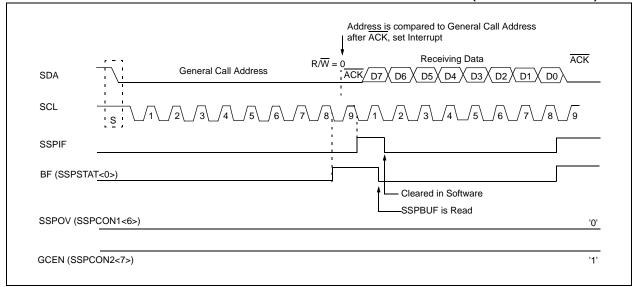

## 15.2.2 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the START condition usually determines which device will be the slave addressed by the master. The exception is the general call address, which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all 0's with R/W = 0.

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> is set). Following a START bit detect, 8-bits are shifted into SSPSR and the address is compared against SSPADD and is also compared to the general call address, fixed in hardware.

If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag is set (eighth bit) and on the falling edge of the ninth bit (ACK bit), the SSPIF flag is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF to determine if the address was device specific, or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when GCEN is set, while the slave is configured in 10-bit address mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the acknowledge (Figure 15-16).

FIGURE 15-16: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE (7 OR 10-BIT MODE)

# 15.2.6 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET, or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the STOP condition occurs.

In Multi-Master operation, the SDA line must be monitored for arbitration, to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A START Condition

- A Repeated Start Condition

- An Acknowledge Condition

## 15.2.7 I<sup>2</sup>C MASTER MODE SUPPORT

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. Once Master mode is enabled, the user has six options.

- · Assert a START condition on SDA and SCL.

- Assert a Repeated Start condition on SDA and SCL.

- Write to the SSPBUF register initiating transmission of data/address.

- Generate a STOP condition on SDA and SCL.

- Configure the I<sup>2</sup>C port to receive data.

- Generate an Acknowledge condition at the end of a received byte of data.

| Note: | The MSSP Module, when configured in I <sup>2</sup> C |  |  |  |  |  |  |

|-------|------------------------------------------------------|--|--|--|--|--|--|

|       | Master mode, does not allow queueing of              |  |  |  |  |  |  |

|       | events. For instance: The user is not                |  |  |  |  |  |  |

|       | allowed to initiate a START condition and            |  |  |  |  |  |  |

|       | immediately write the SSPBUF register to             |  |  |  |  |  |  |

|       | initiate transmission before the START               |  |  |  |  |  |  |

|       | condition is complete. In this case, the             |  |  |  |  |  |  |

|       | SSPBUF will not be written to and the                |  |  |  |  |  |  |

|       | WCOL bit will be set, indicating that a write        |  |  |  |  |  |  |

|       | to the SSPBUF did not occur.                         |  |  |  |  |  |  |

# 15.2.7.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an acknowledge bit is received. START and STOP conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address, followed by a '1' to indicate receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an acknowledge bit is transmitted. START and STOP conditions indicate the beginning and end of transmission.

The baud rate generator used for SPI mode operation is now used to set the SCL clock frequency for either 100 kHz, 400 kHz, or 1 MHz I<sup>2</sup>C operation. The baud rate generator reload value is contained in the lower 7 bits of the SSPADD register. The baud rate generator will automatically begin counting on a write to the SSP-BUF. Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state

#### 17.4 Power-down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction. This clears the Watchdog Timer and postscaler (if enabled). The PD bit is cleared and the TO bit is set (in the CPUSTA register). In SLEEP mode, the oscillator driver is turned off. The I/O ports maintain their status (driving high, low, or hi-impedance input).

The MCLR/VPP pin must be at a logic high level (VIHMC). A WDT time-out RESET does not drive the MCLR/VPP pin low.

#### 17.4.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- Power-on Reset

- · Brown-out Reset

- External RESET input on MCLR/VPP pin

- WDT Reset (if WDT was enabled)

- Interrupt from RA0/INT pin, RB port change, T0CKI interrupt, or some peripheral interrupts

The following peripheral interrupts can wake the device from SLEEP:

- Capture interrupts

- · USART synchronous slave transmit interrupts

- · USART synchronous slave receive interrupts

- A/D conversion complete

- · SPI slave transmit/receive complete

- I<sup>2</sup>C slave receive

Other peripherals cannot generate interrupts since during SLEEP, no on-chip Q clocks are present.

Any RESET event will cause a device RESET. Any interrupt event is considered a continuation of program execution. The TO and PD bits in the CPUSTA register can be used to determine the cause of a device RESET. The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The TO bit is cleared if WDT time-out occurred (and caused a RESET).

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GLINTD bit. If the GLINTD bit is set (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GLINTD bit is clear (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt vector address. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

| Note: | If the global interrupt is disabled (GLINTD            |

|-------|--------------------------------------------------------|

|       | is set), but any interrupt source has both its         |

|       | interrupt enable bit and the corresponding             |

|       | interrupt flag bit set, the device will imme-          |

|       | diately wake-up from SLEEP. The $\overline{TO}$ bit is |

|       | set and the $\overline{PD}$ bit is cleared.            |

The WDT is cleared when the device wakes from SLEEP, regardless of the source of wake-up.

#### 17.4.1.1 Wake-up Delay

When the oscillator type is configured in XT or LF mode, the Oscillator Start-up Timer (OST) is activated on wake-up. The OST will keep the device in RESET for 1024Tosc. This needs to be taken into account when considering the interrupt response time when coming out of SLEEP.

Q4

#### **FIGURE 17-2:** WAKE-UP FROM SLEEP THROUGH INTERRUPT Q1 | Q2 | Q3 | Q4 | Q1 Q2 Q3 OSC1 MMM Tost(2) CLKOUT<sup>(4)</sup> '0' or '1 INT (RA0/INT pin) Interrupt Latency(2) **INTF Flag** GLINTD bit Processor in SLEEP INSTRUCTION FLOW PC PC+2 0004h PC+1 0005h

Inst (PC+2) Inst (PC) = SLEEP Inst (PC+1) Fetched Instruction Inst (PC+1) SLEEP Inst (PC-1) Executed Note 1: XT or LF oscillator mode assumed.

2: TOST = 1024TOSC (drawing not to scale). This delay will not be there for RC osc mode.

3: When GLINTD = 0, processor jumps to interrupt routine after wake-up. If GLINTD = 1, execution will continue in line. 4: CLKOUT is not available in these osc modes, but shown here for timing reference.

Instruction

Dummy Cycle

| INCF              | Incremen                                                  | tf                          |             |                       |

|-------------------|-----------------------------------------------------------|-----------------------------|-------------|-----------------------|

| Syntax:           | [ label ]                                                 | INCF f                      | ,d          |                       |

| Operands:         |                                                           |                             |             |                       |

| Operation:        | (f) + 1 $\rightarrow$ (                                   | dest)                       |             |                       |

| Status Affected:  | OV, C, DC                                                 | ;, Z                        |             |                       |

| Encoding:         | 0001                                                      | 010d                        | ffff        | ffff                  |

| Description:      | The conten<br>mented. If '<br>WREG. If 'c<br>back in regi | d' is 0, th<br>l' is 1, the | e result is | placed in             |

| Words:            | 1                                                         |                             |             |                       |

| Cycles:           | 1                                                         |                             |             |                       |

| Q Cycle Activity: |                                                           |                             |             |                       |

| Q1                | Q2                                                        | Q3                          |             | Q4                    |

| Decode            | Read<br>register 'f'                                      | Proce<br>Dat                |             | Vrite to<br>stination |

| Example:          | INCF                                                      | CNT,                        | 1           |                       |

| Before Instr      |                                                           |                             |             |                       |

| CNT<br>Z<br>C     | = 0xFF<br>= 0<br>= ?                                      |                             |             |                       |

| After Instruc     | tion                                                      |                             |             |                       |

| CNT<br>Z<br>C     | = 0x00<br>= 1<br>= 1                                      |                             |             |                       |

|                   |                                                           |                             |             |                       |

| INC        | FSZ                                   | Incremen                                                                     | t f, skip if O                                                                                                                                                                                                                                                                                                           | )                    |  |  |  |  |

|------------|---------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|

| Synt       | ax:                                   | [ label ]                                                                    | INCFSZ f,o                                                                                                                                                                                                                                                                                                               | d                    |  |  |  |  |

| Ope        | rands:                                | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \end{array}$              | 5                                                                                                                                                                                                                                                                                                                        |                      |  |  |  |  |

| Ope        | ration:                               | (f) + 1 $\rightarrow$ (skip if resu                                          |                                                                                                                                                                                                                                                                                                                          |                      |  |  |  |  |

| State      | us Affected:                          | None                                                                         |                                                                                                                                                                                                                                                                                                                          |                      |  |  |  |  |

| Enco       | oding:                                | 0001                                                                         | 111d ff                                                                                                                                                                                                                                                                                                                  | ff ffff              |  |  |  |  |

| Des        | cription:                             | mented. If '<br>WREG. If 'c<br>back in regi<br>If the result<br>which is alr | The contents of register 'f' are incre-<br>mented. If 'd' is 0, the result is placed in<br>WREG. If 'd' is 1, the result is placed<br>back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched is discarded<br>and a NOP is executed instead, making<br>it a two sucle instruction |                      |  |  |  |  |

| Wor        | ds:                                   | 1                                                                            | 1                                                                                                                                                                                                                                                                                                                        |                      |  |  |  |  |

| Cycl       | es:                                   | 1(2)                                                                         | 1(2)                                                                                                                                                                                                                                                                                                                     |                      |  |  |  |  |

| QC         | ycle Activity:                        |                                                                              |                                                                                                                                                                                                                                                                                                                          |                      |  |  |  |  |

|            | Q1                                    | Q2                                                                           | Q3                                                                                                                                                                                                                                                                                                                       | Q4                   |  |  |  |  |

|            | Decode                                | Read<br>register 'f'                                                         | Process<br>Data                                                                                                                                                                                                                                                                                                          | Write to destination |  |  |  |  |

| lf sk      | ip:                                   |                                                                              |                                                                                                                                                                                                                                                                                                                          |                      |  |  |  |  |

|            | Q1                                    | Q2                                                                           | Q3                                                                                                                                                                                                                                                                                                                       | Q4                   |  |  |  |  |

|            | No                                    | No                                                                           | No                                                                                                                                                                                                                                                                                                                       | No                   |  |  |  |  |

|            | operation                             | operation                                                                    | operation                                                                                                                                                                                                                                                                                                                | operation            |  |  |  |  |

| <u>Exa</u> | <u>mple</u> :                         | NZERO                                                                        | INCFSZ C<br>:<br>:                                                                                                                                                                                                                                                                                                       | NT, 1                |  |  |  |  |

|            | Before Instru<br>PC                   |                                                                              | G (HERE)                                                                                                                                                                                                                                                                                                                 |                      |  |  |  |  |

|            | After Instruct<br>CNT<br>If CNT<br>PC | = CNT +<br>= 0;                                                              | <b>1</b><br>S(ZERO)                                                                                                                                                                                                                                                                                                      |                      |  |  |  |  |

- If CNT  $\neq$  0;

- PC = Address (NZERO)

# PIC17C7XX

| MO\   | /PF            | Move p t                                                                                                                                                                      | Move p to f                                                                                                                   |                                                                                                |                                                                                            |  |  |  |

|-------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|

| Synt  | ax:            | [ <i>label</i> ] N                                                                                                                                                            | [ <i>label</i> ] MOVPF p,f                                                                                                    |                                                                                                |                                                                                            |  |  |  |

| Ope   | rands:         | $0 \le f \le 25$<br>$0 \le p \le 31$                                                                                                                                          | -                                                                                                                             |                                                                                                |                                                                                            |  |  |  |

| Ope   | ration:        | $(p) \to (f)$                                                                                                                                                                 |                                                                                                                               |                                                                                                |                                                                                            |  |  |  |

| Statu | us Affected:   | Z                                                                                                                                                                             |                                                                                                                               |                                                                                                |                                                                                            |  |  |  |

| Enco  | oding:         | 010p                                                                                                                                                                          | pppp                                                                                                                          | ffff                                                                                           | ffff                                                                                       |  |  |  |

| Des   | cription:      | Move data<br>'p' to data n<br>'f' can be a<br>space (00h<br>to 1Fh.<br>Either 'p' o<br>special situ<br>MOVPF is p<br>ring a perip<br>or an I/O p<br>tion. Both '<br>addressed | memory lo<br>nywhere i<br>n to FFh),<br>r 'f' can bo<br>uation).<br>particularly<br>oheral reg<br>ort) to a c<br>f' and 'p' o | pocation 'f',<br>in the 256<br>while 'p' c<br>e WREG<br>y useful fo<br>jister (e.g<br>lata mem | Location<br>byte data<br>an be 00h<br>(a useful,<br>or transfer-<br>the timer<br>ory loca- |  |  |  |

| Wor   | ds:            | 1                                                                                                                                                                             |                                                                                                                               |                                                                                                |                                                                                            |  |  |  |

| Cycl  | es:            | 1                                                                                                                                                                             |                                                                                                                               |                                                                                                |                                                                                            |  |  |  |

| QC    | ycle Activity: |                                                                                                                                                                               |                                                                                                                               |                                                                                                |                                                                                            |  |  |  |

|       | Q1             | Q2                                                                                                                                                                            | Q3                                                                                                                            | 3                                                                                              | Q4                                                                                         |  |  |  |

|       | Decode         | Read<br>register 'p'                                                                                                                                                          | Proce<br>Dat                                                                                                                  |                                                                                                | Write<br>egister 'f'                                                                       |  |  |  |

|       |                |                                                                                                                                                                               |                                                                                                                               |                                                                                                |                                                                                            |  |  |  |

| Example:          | MOVPF | REG1, | REG2 |

|-------------------|-------|-------|------|

| Before Instruc    | tion  |       |      |

| REG1              | =     | 0x11  |      |

| REG2              | =     | 0x33  |      |

| After Instruction | on    |       |      |

=

=

0x11

0x11

REG1

REG2

| MOVWF             | Move WR                                  | Move WREG to f |      |                     |  |  |  |  |

|-------------------|------------------------------------------|----------------|------|---------------------|--|--|--|--|

| Syntax:           | [ label ]                                | MOVWF          | f    |                     |  |  |  |  |

| Operands:         | $0 \le f \le 255$                        | 5              |      |                     |  |  |  |  |

| Operation:        | (WREG) -                                 | → (f)          |      |                     |  |  |  |  |

| Status Affected:  | None                                     |                |      |                     |  |  |  |  |

| Encoding:         | 0000                                     | 0001           | ffff | ffff                |  |  |  |  |

| Description:      | Move data<br>Location 'f'<br>byte data s | can be an      | 0    |                     |  |  |  |  |

| Words:            | 1                                        |                |      |                     |  |  |  |  |

| Cycles:           | 1                                        |                |      |                     |  |  |  |  |

| Q Cycle Activity: |                                          |                |      |                     |  |  |  |  |

| Q1                | Q2                                       | Q3             |      | Q4                  |  |  |  |  |

| Decode            | Read<br>register 'f'                     | Proces<br>Data |      | Write<br>gister 'f' |  |  |  |  |

| Example:          | MOVWF                                    | REG            | ·    |                     |  |  |  |  |

| Before Instruction |      |      |  |  |  |  |  |  |

|--------------------|------|------|--|--|--|--|--|--|

| WREG               | =    | 0x4F |  |  |  |  |  |  |

| REG                | =    | 0xFF |  |  |  |  |  |  |

| After Instruc      | tion |      |  |  |  |  |  |  |

|      | lion |      |

|------|------|------|

| WREG | =    | 0x4F |

| REG  | =    | 0x4F |

# PIC17C7XX

| SWA        | APF                                                    | Swap f                                                                    |                         |                             |                       |  |  |

|------------|--------------------------------------------------------|---------------------------------------------------------------------------|-------------------------|-----------------------------|-----------------------|--|--|

| Synt       | tax:                                                   | [label]                                                                   | SWAPF                   | f,d                         |                       |  |  |

| Ope        | rands:                                                 | $\begin{array}{l} 0 \leq f \leq 25 \\ d \in \left[0,1\right] \end{array}$ | 5                       |                             |                       |  |  |

| Ope        | ration:                                                | $f<3:0> \rightarrow f<7:4> \rightarrow$                                   |                         | ,                           |                       |  |  |

| State      | us Affected:                                           | None                                                                      |                         |                             |                       |  |  |

| Enc        | oding:                                                 | 0001                                                                      | 110d                    | ffff                        | ffff                  |  |  |

| Des        | cription:                                              | The upper<br>'f' are exch<br>placed in V<br>placed in re                  | anged. If<br>VREG. If ' | 'd' is 0, th<br>d' is 1, th | e result is           |  |  |

| Wor        | ds:                                                    | 1                                                                         |                         |                             |                       |  |  |

| Cycl       | les:                                                   | 1                                                                         | 1                       |                             |                       |  |  |

| QC         | ycle Activity:                                         |                                                                           |                         |                             |                       |  |  |

|            | Q1                                                     | Q2                                                                        | Q2 Q3                   |                             | Q4                    |  |  |

|            | Decode                                                 | Read<br>register 'f'                                                      | Proce<br>Dat            |                             | Vrite to<br>stination |  |  |

| <u>Exa</u> | mple:<br>Before Instru<br>REG<br>After Instruct<br>REG | iction<br>= 0x53                                                          | REG,                    | 0                           |                       |  |  |

| ТАВ   | LRD          | Tab                                                                                                                                                                                                        | le Rea                    | ad                                 |                                                           |                               |  |

|-------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------------|-----------------------------------------------------------|-------------------------------|--|

| Synt  | ax:          | [ <i>la</i>                                                                                                                                                                                                | [ label ] TABLRD t,i,f    |                                    |                                                           |                               |  |

| Ope   | rands:       | i∈                                                                                                                                                                                                         | f ≤ 258<br>[0,1]<br>[0,1] | 5                                  |                                                           |                               |  |

| Ope   | ration:      | If t = 1,<br>TBLATH $\rightarrow$ f;<br>If t = 0,<br>TBLATL $\rightarrow$ f;<br>Prog Mem (TBLPTR) $\rightarrow$ TBLAT;<br>If i = 1,<br>TBLPTR + 1 $\rightarrow$ TBLPTR<br>If i = 0,<br>TBLPTR is unchanged |                           |                                    |                                                           |                               |  |

| Statu | us Affected  | : No                                                                                                                                                                                                       | ne                        |                                    |                                                           |                               |  |

| Enco  | oding:       | 1                                                                                                                                                                                                          | 010                       | 10ti                               | ffff                                                      | ffff                          |  |

| Desc  | cription:    | 1.                                                                                                                                                                                                         | is mov<br>If t = 1        | ved to reg<br>: the high           | ble latch (<br>ister file 'f'<br>byte is m<br>byte is mo  | oved;                         |  |

|       |              | 2.                                                                                                                                                                                                         | gram<br>by th<br>(TBLF    | memory lo<br>ne 16-bit<br>PTR) are | tents of t<br>ocation po<br>Table<br>loaded i<br>ch (TBLA | nted to<br>Pointer<br>nto the |  |

|       |              | 3.                                                                                                                                                                                                         |                           | : TBLPTI<br>: TBLPTI<br>increme    |                                                           | nented;                       |  |

| Wor   | ds:          | 1                                                                                                                                                                                                          |                           |                                    |                                                           |                               |  |

| Cycl  | es:          | 2 (3                                                                                                                                                                                                       | 8-cycle                   | if f = PC                          | L)                                                        |                               |  |

| QC    | cle Activity | /:                                                                                                                                                                                                         |                           |                                    |                                                           |                               |  |

|       | Q1           | Q                                                                                                                                                                                                          | 2                         | Q3                                 | (                                                         | Q4                            |  |

|       | Decode       | Re<br>regi:<br>TBLA                                                                                                                                                                                        | ster                      | Proces<br>Data                     | -                                                         | /rite<br>ister 'f'            |  |

| Decode    | Read           | Process   | Write         |

|-----------|----------------|-----------|---------------|

|           | register       | Data      | register 'f'  |

|           | TBLATH or      |           |               |

|           | TBLATL         |           |               |

| No        | No             | No        | No            |

| operation | operation      | operation | operation     |

|           | (Table Pointer |           | (OE goes low) |

|           | on Address     |           |               |

|           | bus)           |           |               |

# **19.0 DEVELOPMENT SUPPORT**

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC<sup>™</sup> In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD for PIC16F87X

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup>1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ<sup>®</sup> Demonstration Board

# 19.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup>-based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor

- · A project manager

- Customizable toolbar and key mapping

- A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the cost-effective simulator to a full-featured emulator with minimal retraining.

# 19.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCU's.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

# 19.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

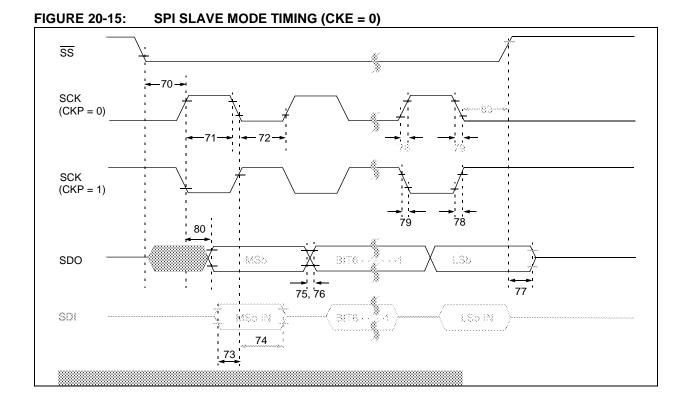

## TABLE 20-10: SPI MODE REQUIREMENTS (SLAVE MODE TIMING, CKE = 0)

| Param.<br>No. | Symbol                | Characteristic                                                        | Min            | Тур†         | Max | Units | Conditions |          |

|---------------|-----------------------|-----------------------------------------------------------------------|----------------|--------------|-----|-------|------------|----------|

| 70            | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input |                | Тсу          | —   | —     | ns         |          |

| 71            | TscH                  | SCK input high time                                                   | Continuous     | 1.25Tcy + 30 | —   | —     | ns         |          |

| 71A           |                       | (Slave mode)                                                          | Single Byte    | 40           |     | —     | ns         | (Note 1) |

| 72            | TscL                  | SCK input low time                                                    | Continuous     | 1.25Tcy + 30 | _   | _     | ns         |          |

| 72A           |                       | (Slave mode)                                                          | Single Byte    | 40           | —   | —     | ns         | (Note 1) |

| 73            | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to                                       | SCK edge       | 100          | —   | —     | ns         |          |

| 73A           | Тв2в                  | Last clock edge of Byte1 to the<br>of Byte2                           | 1.5Tcy + 40    | —            | —   | ns    | (Note 1)   |          |

| 74            | TscH2diL,<br>TscL2diL | Hold time of SDI data input to S                                      | SCK edge       | 100          | —   | _     | ns         |          |

| 75            | TdoR                  | SDO data output rise time                                             |                | _            | 10  | 25    | ns         |          |

| 76            | TdoF                  | SDO data output fall time                                             |                | _            | 10  | 25    | ns         |          |

| 77            | TssH2doZ              | SS <sup>↑</sup> to SDO output hi-impedan                              | се             | 10           | _   | 50    | ns         |          |

| 78            | TscR                  | SCK output rise time (Master m                                        | iode)          | _            | 10  | 25    | ns         |          |

| 79            | TscF                  | SCK output fall time (Master me                                       | ode)           | _            | 10  | 25    | ns         |          |

| 80            | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge                                  |                |              | —   | 50    | ns         |          |

| 83            | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                                   |                | 1.5Tcy + 40  | —   | —     | ns         |          |

| †             | Data in "Typ"         | column is at 5V, 25°C unless oth                                      | erwise stated. |              |     |       |            |          |

Note 1: Specification 73A is only required if specifications 71A and 72A are used.

| Param<br>No. | Sym  | Characteristic         |                           | Min | Max | Units | Conditions                |

|--------------|------|------------------------|---------------------------|-----|-----|-------|---------------------------|

| 110          | Tbuf | Bus free time          | 100 kHz mode              | 4.7 | —   | ms    | Time the bus must be free |

|              |      |                        | 400 kHz mode              | 1.3 | _   | ms    | before a new transmission |

|              |      |                        | 1 MHz mode <sup>(1)</sup> | 0.5 | —   | ms    | can start                 |

| D102         | Cb   | Bus capacitive loading |                           | _   | 400 | pF    |                           |

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C$  pins.

2: A fast mode (400 KHz) I<sup>2</sup>C bus device can be used in a standard mode I<sup>2</sup>C bus system, but the parameter # 107 ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line. Parameter #102 + #107 = 1000 + 250 = 1250 ns (for 100 kHz mode) before the SCL line is released.

**3:**  $C_b$  is specified to be from 10-400pF. The minimum specifications are characterized with  $C_b$ =10pF. The rise time spec ( $t_r$ ) is characterized with  $R_p$ = $R_p$  min. The minimum fall time specification ( $t_f$ ) is characterized with  $C_b$ =10pF,and  $R_p$ = $R_p$  max. These are only valid for fast mode operation (VDD=4.5-5.5V) and where the SPM bit (SSPSTAT<7>) =1.)

4: Max specifications for these parameters are valid for falling edge only. Specs are characterized with R<sub>p</sub>=R<sub>p</sub> min and C<sub>b</sub>=400pF for standard mode, 200pF for fast mode, and 10pF for 1MHz mode.

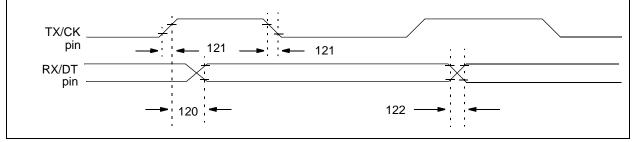

## FIGURE 20-19: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

## TABLE 20-14: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                    |                     |   | Тур† | Max | Units | Conditions |

|--------------|----------|-----------------------------------|---------------------|---|------|-----|-------|------------|

| 120          | TckH2dtV | SYNC XMIT (MASTER & SLAVE)        |                     |   |      |     |       |            |

|              |          | Clock high to data out valid      | PIC17 <b>C</b> XXX  | — | —    | 50  | ns    |            |

|              |          |                                   | PIC17LCXXX          | - | —    | 75  | ns    |            |

| 121          | TckRF    | Clock out rise time and fall time | PIC17 <b>C</b> XXX  | — | —    | 25  | ns    |            |

|              |          | (Master mode)                     | PIC17 <b>LC</b> XXX | — | —    | 40  | ns    |            |

| 122          | TdtRF    | Data out rise time and fall time  | PIC17 <b>C</b> XXX  | — | —    | 25  | ns    |            |

|              |          |                                   | PIC17 <b>LC</b> XXX | _ | _    | 40  | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated.

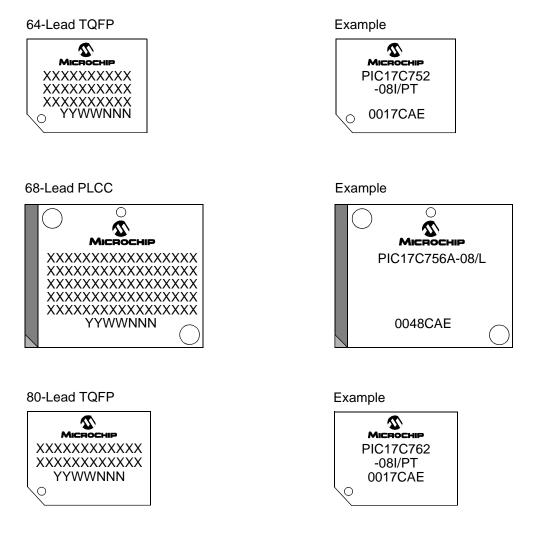

# 22.0 PACKAGING INFORMATION

# 22.1 Package Marking Information

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carrie                                | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                                                                                                                                                                                                  |

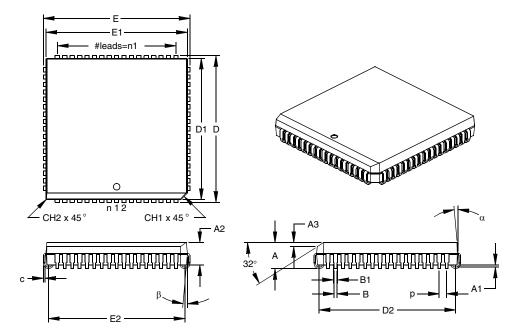

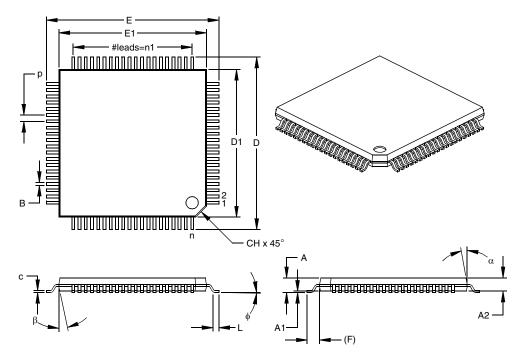

## 68-Lead Plastic Leaded Chip Carrier (L) – Square (PLCC)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |           | INCHES* |      |      | MILLIMETERS |       |       |

|--------------------------|-----------|---------|------|------|-------------|-------|-------|

| Dimensi                  | on Limits | MIN     | NOM  | MAX  | MIN         | NOM   | MAX   |

| Number of Pins           | n         |         | 68   |      |             | 68    |       |

| Pitch                    | р         |         | .050 |      |             | 1.27  |       |

| Pins per Side            | n1        |         | 17   |      |             | 17    |       |