Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

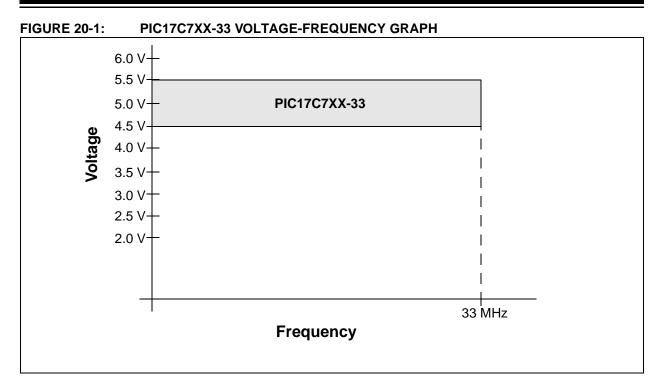

| Speed                      | 33MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 66                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 678 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                               |

| Data Converters            | A/D 16x10b                                                                |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 84-LCC (J-Lead)                                                           |

| Supplier Device Package    | 84-PLCC (29.31x29.31)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c762-33i-l |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Register             | Address | Power-on Reset<br>Brown-out Reset | MCLR Reset<br>WDT Reset | Wake-up from SLEEP<br>through Interrupt |

|----------------------|---------|-----------------------------------|-------------------------|-----------------------------------------|

| Bank 4               |         | ·                                 |                         | ·                                       |

| PIR2                 | 10h     | 000- 0010                         | 000- 0010               | uuu- uuuu <b>(1)</b>                    |

| PIE2                 | 11h     | 000- 0000                         | 000- 0000               | uuu- uuuu                               |

| Unimplemented        | 12h     |                                   |                         |                                         |

| RCSTA2               | 13h     | x00-0000                          | 0000 -00u               | uuuu -uuu                               |

| RCREG2               | 14h     | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |

| TXSTA2               | 15h     | 00001x                            | 00001u                  | uuuuuu                                  |

| TXREG2               | 16h     | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |

| SPBRG2               | 17h     | 0000 0000                         | 0000 0000               | นนนน นนนน                               |

| Bank 5               |         |                                   |                         |                                         |

| DDRF                 | 10h     | 1111 1111                         | 1111 1111               | uuuu uuuu                               |

| PORTF <sup>(4)</sup> | 11h     | 0000 0000                         | 0000 0000               | uuuu uuuu                               |

| DDRG                 | 12h     | 1111 1111                         | 1111 1111               | uuuu uuuu                               |

| PORTG <sup>(4)</sup> | 13h     | xxxx 0000                         | uuuu 0000               | uuuu uuuu                               |

| ADCON0               | 14h     | 0000 -0-0                         | 0000 -0-0               | uuuu uuuu                               |

| ADCON1               | 15h     | 000- 0000                         | 000- 0000               | uuuu uuuu                               |

| ADRESL               | 16h     | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |

| ADRESH               | 17h     | xxxx xxxx                         | uuuu uuuu               | นนนน นนนน                               |

| Bank 6               |         |                                   |                         |                                         |

| SSPADD               | 10h     | 0000 0000                         | 0000 0000               | uuuu uuuu                               |

| SSPCON1              | 11h     | 0000 0000                         | 0000 0000               | uuuu uuuu                               |

| SSPCON2              | 12h     | 0000 0000                         | 0000 0000               | uuuu uuuu                               |

| SSPSTAT              | 13h     | 0000 0000                         | 0000 0000               | uuuu uuuu                               |

| SSPBUF               | 14h     | XXXX XXXX                         | uuuu uuuu               | นนนน นนนน                               |

| Unimplemented        | 15h     |                                   |                         |                                         |

| Unimplemented        | 16h     |                                   |                         |                                         |

| Unimplemented        | 17h     |                                   |                         |                                         |

| TABLE 5-4: | INITIALIZATION CONDITIONS FOR SPECIAL FUNCTION REGISTERS ( | (CONTINUED) |  |

|------------|------------------------------------------------------------|-------------|--|

|            |                                                            |             |  |

Legend: u = unchanged, x = unknown, - = unimplemented, read as '0', q = value depends on condition

Note 1: One or more bits in INTSTA, PIR1, PIR2 will be affected (to cause wake-up).

**2:** When the wake-up is due to an interrupt and the GLINTD bit is cleared, the PC is loaded with the interrupt vector.

**3:** See Table 5-3 for RESET value of specific condition.

4: This is the value that will be in the port output latch.

**5:** When the device is configured for Microprocessor or Extended Microcontroller mode, the operation of this port does not rely on these registers.

6: On any device RESET, these pins are configured as inputs.

| TABLE 3-4. INTRALIZATION CONDITIONS FOR STECIAL FONCTION REGISTERS (CONTINUE |         |                                   |                         |                                         |  |  |  |  |

|------------------------------------------------------------------------------|---------|-----------------------------------|-------------------------|-----------------------------------------|--|--|--|--|

| Register                                                                     | Address | Power-on Reset<br>Brown-out Reset | MCLR Reset<br>WDT Reset | Wake-up from SLEEP<br>through Interrupt |  |  |  |  |

| Bank 7                                                                       |         |                                   |                         |                                         |  |  |  |  |

| PW3DCL                                                                       | 10h     | xx0                               | uu0                     | uuu                                     |  |  |  |  |

| PW3DCH                                                                       | 11h     | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| CA3L                                                                         | 12h     | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| САЗН                                                                         | 13h     | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| CA4L                                                                         | 14h     | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| CA4H                                                                         | 15h     | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| TCON3                                                                        | 16h     | -000 0000                         | -000 0000               | -uuu uuuu                               |  |  |  |  |

| Unimplemented                                                                | 17h     |                                   |                         |                                         |  |  |  |  |

| Bank 8                                                                       |         |                                   |                         |                                         |  |  |  |  |

| DDRH                                                                         | 10h     | 1111 1111                         | 1111 1111               | uuuu uuuu                               |  |  |  |  |

| PORTH <sup>(4)</sup>                                                         | 11h     | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| DDRJ                                                                         | 12h     | 1111 1111                         | 1111 1111               | uuuu uuuu                               |  |  |  |  |

| PORTJ <sup>(4)</sup>                                                         | 13h     | xxxx xxxx                         | uuuu uuuu               | սսսս սսսս                               |  |  |  |  |

| Unbanked                                                                     |         |                                   |                         |                                         |  |  |  |  |

| PRODL                                                                        | 18h     | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

| PRODH                                                                        | 19h     | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |  |  |

|                                                                              |         |                                   |                         |                                         |  |  |  |  |

#### TABLE 5-4: INITIALIZATION CONDITIONS FOR SPECIAL FUNCTION REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented, read as '0', q = value depends on condition

Note 1: One or more bits in INTSTA, PIR1, PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GLINTD bit is cleared, the PC is loaded with the interrupt vector.

3: See Table 5-3 for RESET value of specific condition.

4: This is the value that will be in the port output latch.

**5:** When the device is configured for Microprocessor or Extended Microcontroller mode, the operation of this port does not rely on these registers.

6: On any device RESET, these pins are configured as inputs.

|       | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                       | R/W-0                            | U-0             | R/W-0        | R/W-0                                  | R-1     | R-0       |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------|-----------------|--------------|----------------------------------------|---------|-----------|--|--|--|--|

|       | SSPIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | BCLIF                                                                       | ADIF                             | —               | CA4IF        | CA3IF                                  | TX2IF   | RC2IF     |  |  |  |  |

|       | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                             |                                  |                 |              |                                        |         | bit 0     |  |  |  |  |

| bit 7 | 1 = The S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                             | condition has                    | occurred ar     | nd must be c | leared in softw<br>vill set this bit a |         | returning |  |  |  |  |

|       | <u>SPI:</u><br>A trans                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <u>SPI:</u><br>A transmission/reception has taken place.                    |                                  |                 |              |                                        |         |           |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I <sup>2</sup> C Slave/Master:<br>A transmission/reception has taken place. |                                  |                 |              |                                        |         |           |  |  |  |  |

|       | A transmission/reception has taken place.<br><u>I<sup>2</sup>C Master:</u><br>The initiated START condition was completed by the SSP module.<br>The initiated STOP condition was completed by the SSP module.<br>The initiated Restart condition was completed by the SSP module.<br>The initiated Acknowledge condition was completed by the SSP module.<br>A START condition occurred while the SSP module was idle (Multi-master system).<br>A STOP condition occurred while the SSP module was idle (Multi-master system). |                                                                             |                                  |                 |              |                                        |         |           |  |  |  |  |

|       | 0 <b>= An SS</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | P interrupt co                                                              | ondition has                     | NOT occurre     | ed           |                                        |         |           |  |  |  |  |

| bit 6 | <b>BCLIF</b> : Bu<br>1 = A bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | s Collision In                                                              | nterrupt Flag<br>occurred in t   | bit             |              | d for I <sup>2</sup> C Maste           | er mode |           |  |  |  |  |

| bit 5 | 1 = An A/C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Module Inter<br>conversion<br>conversion                                    | is complete                      |                 |              |                                        |         |           |  |  |  |  |

| bit 4 | Unimplem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ented: Read                                                                 | as '0'                           |                 |              |                                        |         |           |  |  |  |  |

| bit 3 | 1 = Captur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | pture4 Interr<br>e event occu<br>e event did r                              | irred on RE3                     |                 | vin          |                                        |         |           |  |  |  |  |

| bit 2 | 1 = Captur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | pture3 Interr<br>e event occu<br>e event did r                              | irred on RG4                     |                 | bin          |                                        |         |           |  |  |  |  |

| bit 1 | <b>TX2IF</b> :US/<br>1 = USAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                             | nit Interrupt F<br>buffer is emp | lag bit (state  |              | oy hardware)                           |         |           |  |  |  |  |

| bit 0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             | ve Interrupt I<br>ouffer is full | -lag bit (state | e controlled | by hardware)                           |         |           |  |  |  |  |

# REGISTER 6-5: PIR2 REGISTER (ADDRESS: 10h, BANK 4)

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR Reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| Address            | Name                   | Bit 7              | Bit 6          | Bit 5                   | Bit 4           | Bit 3           | Bit 2          | Bit 1        | Bit 0        | Value on<br>POR,<br>BOR | MCLR,<br>WDT        |

|--------------------|------------------------|--------------------|----------------|-------------------------|-----------------|-----------------|----------------|--------------|--------------|-------------------------|---------------------|

| Unbanke            | ed                     |                    |                |                         |                 |                 |                |              |              |                         |                     |

| 00h                | INDF0                  | Uses conte         | ents of FSR    | 0 to address            | Data Memo       | ry (not a phy   | sical registe  | r)           |              |                         |                     |

| 01h                | FSR0                   | Indirect Da        | ata Memory     | Address Poi             | nter 0          |                 |                |              |              | XXXX XXXX               | uuuu uuuu           |

| 02h                | PCL                    | Low order          | 8-bits of PC   | ;                       |                 |                 |                |              |              | 0000 0000               | 0000 0000           |

| 03h <sup>(1)</sup> | PCLATH                 | Holding Re         | egister for u  | pper 8-bits o           | f PC            |                 |                |              |              | 0000 0000               | uuuu uuuu           |

| 04h                | ALUSTA                 | FS3                | FS2            | FS1                     | FS0             | OV              | Z              | DC           | С            | 1111 xxxx               | 1111 uuuu           |

| 05h                | TOSTA                  | INTEDG             | T0SE           | TOCS                    | T0PS3           | T0PS2           | T0PS1          | T0PS0        |              | 0000 000-               | 0000 000-           |

| 06h <sup>(2)</sup> | CPUSTA                 |                    | _              | STKAV                   | GLINTD          | TO              | PD             | POR          | BOR          | 11 11qq                 | 11 qqui             |

| 07h                | INTSTA                 | PEIF               | T0CKIF         | T0IF                    | INTF            | PEIE            | TOCKIE         | T0IE         | INTE         | 0000 0000               | 0000 0000           |

| 08h                | INDF1                  | Uses conte         | ents of FSR    | 1 to address            | Data Memo       | ry (not a phy   | sical registe  | r)           |              |                         |                     |

| 09h                | FSR1                   | Indirect Da        | ata Memory     | Address Poi             | nter 1          |                 | -              |              |              | XXXX XXXX               | uuuu uuuu           |

| 0Ah                | WREG                   | Working R          | egister        |                         |                 |                 |                |              |              | XXXX XXXX               | uuuu uuuu           |

| 0Bh                | TMR0L                  | TMR0 Reg           | gister; Low E  | Byte                    |                 |                 |                |              |              | XXXX XXXX               | uuuu uuuu           |

| 0Ch                | TMR0H                  | TMR0 Reg           | jister; High I | Byte                    |                 |                 |                |              |              | XXXX XXXX               | uuuu uuuu           |

| 0Dh                | TBLPTRL                | Low Byte of        | of Program     | Memory Tab              | le Pointer      |                 |                |              |              | 0000 0000               | 0000 0000           |

| 0Eh                | TBLPTRH                | High Byte          | of Program     | Memory Tab              | le Pointer      |                 |                |              |              | 0000 0000               | 0000 0000           |

| 0Fh                | BSR                    | Bank Sele          | ct Register    |                         |                 |                 |                |              |              | 0000 0000               | 0000 0000           |

| Bank 0             | •                      |                    |                |                         |                 |                 |                |              |              | •                       |                     |

| 10h                | PORTA <sup>(4,6)</sup> | RBPU               | —              | RA5/TX1/<br>CK1         | RA4/RX1/<br>DT1 | RA3/SDI/<br>SDA | RA2/SS/<br>SCL | RA1/T0CKI    | RA0/INT      | 0-xx 11xx               | 0-uu 11uu           |

| 11h                | DDRB                   | Data Direc         | tion Registe   | er for PORTE            | 3               |                 |                |              |              | 1111 1111               | 1111 1111           |

| 12h                | PORTB <sup>(4)</sup>   | RB7/               | RB6/           | RB5/                    | RB4/            | RB3/            | RB2/           | RB1/         | RB0/         | xxxx xxxx               | uuuu uuuu           |

| 13h                | RCSTA1                 | SDO<br>SPEN        | SCK<br>RX9     | TCLK3<br>SREN           | TCLK12<br>CREN  | PWM2            | PWM1<br>FERR   | CAP2<br>OERR | CAP1<br>RX9D | 0000 -00x               | 0000 -000           |

| 13h                | RCREG1                 | -                  | Receive Re     |                         | CREN            | _               | FERR           | OEKK         | KA9D         |                         |                     |

| 140<br>15h         | TXSTA1                 | CSRC               | TX9            | TXEN                    | SYNC            |                 |                | TRMT         | TX9D         | xxxx xxxx<br>00001x     | uuuu uuuu<br>00001u |

| 16h                | TXREG1                 |                    | -              | egister (for L          |                 | _               | _              |              | 1 Yan        | xxxx xxxx               | uuuu uuuu           |

| 17h                | SPBRG1                 |                    |                | Register (for           | ,               |                 |                |              |              | 0000 0000               | 0000 0000           |

| Bank 1             | SF BILGT               | Dauu Nale          | Generator      |                         | USARTI)         |                 |                |              |              | 0000 0000               | 0000 0000           |

|                    | DDRC <sup>(5)</sup>    | Data Direa         | tion Desists   |                         | <b>`</b>        |                 |                |              |              |                         |                     |

| 10h<br>11h         | PORTC <sup>(4,5)</sup> |                    | 0              | er for PORTC<br>RC5/AD5 | ,<br>RC4/AD4    | RC3/AD3         | RC2/AD2        | RC1/AD1      | RC0/AD0      | 1111 1111               | 1111 1111           |

|                    | DDRD <sup>(5)</sup>    |                    |                |                         |                 | RC3/AD3         | RUZ/ADZ        | RC1/AD1      | RCU/ADU      | XXXX XXXX               | uuuu uuuu           |

| 12h                |                        | Data Direc<br>RD7/ | RD6/           | er for PORTE<br>RD5/    | RD4/            | RD3/            | RD2/           | 1            | -            | 1111 1111               | 1111 1111           |

| 13h                | PORTD <sup>(4,5)</sup> | AD15               | AD14           | AD13                    | AD12            | AD11            | AD10           | RD1/AD9      | RD0/AD8      | xxxx xxxx               | սսսս սսսս           |

| 14h                | DDRE <sup>(5)</sup>    | Data Direc         | tion Registe   | er for PORTE            |                 |                 |                |              |              | 1111                    | 1112                |

| 15h                | PORTE <sup>(4,5)</sup> | -                  | —              | —                       | —               | RE3/<br>CAP4    | RE2/WR         | RE1/OE       | RE0/ALE      | xxxx                    | uuui                |

| 16h                | PIR1                   | RBIF               | TMR3IF         | TMR2IF                  | TMR1IF          | CA2IF           | CA1IF          | TX1IF        | RC1IF        | x000 0010               | u000 001            |

| 17h                | PIE1                   | RBIE               | TMR3IE         | TMR2IE                  | TMR1IE          | CA2IE           | CA1IE          | TX1IE        | RC1IE        | 0000 0000               | 0000 0000           |

#### TABLE 7-3: SPECIAL FUNCTION REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0', q = value depends on condition.

Shaded cells are unimplemented, read as '0'.

**Note** 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<15:8> whose contents are updated from, or transferred to, the upper byte of the program counter.

2: The TO and PD status bits in CPUSTA are not affected by a MCLR Reset.

3: Bank 8 and associated registers are only implemented on the PIC17C76X devices.

4: This is the value that will be in the port output latch.

5: When the device is configured for Microprocessor or Extended Microcontroller mode, the operation of this port does not rely on these registers.

6: On any device RESET, these pins are configured as inputs.

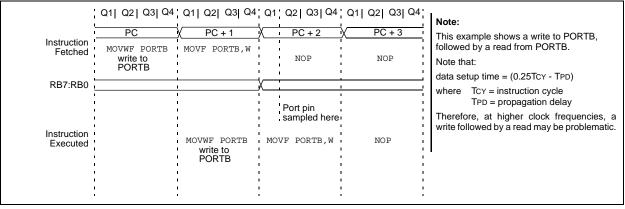

#### 10.10.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 10-20). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before executing the instruction that reads the values on that I/O port. Otherwise, the previous state of that pin may be read into the CPU, rather than the "new" state. When in doubt, it is better to separate these instructions with a NOP, or another instruction not accessing this I/O port.

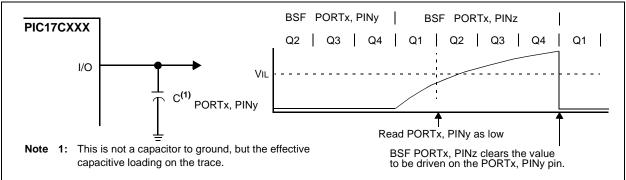

Figure 10-21 shows the I/O model which causes this situation. As the effective capacitance (C) becomes larger, the rise/fall time of the I/O pin increases. As the device frequency increases, or the effective capacitance increases, the possibility of this subsequent PORTx read-modify-write instruction issue increases. This effective capacitance includes the effects of the board traces.

The best way to address this is to add a series resistor at the I/O pin. This resistor allows the I/O pin to get to the desired level before the next instruction.

The use of NOP instructions between the subsequent PORTx read-modify-write instructions, is a lower cost solution, but has the issue that the number of NOP instructions is dependent on the effective capacitance C and the frequency of the device.

# FIGURE 10-20: SUCCESSIVE I/O OPERATION

#### FIGURE 10-21: I/O CONNECTION ISSUES

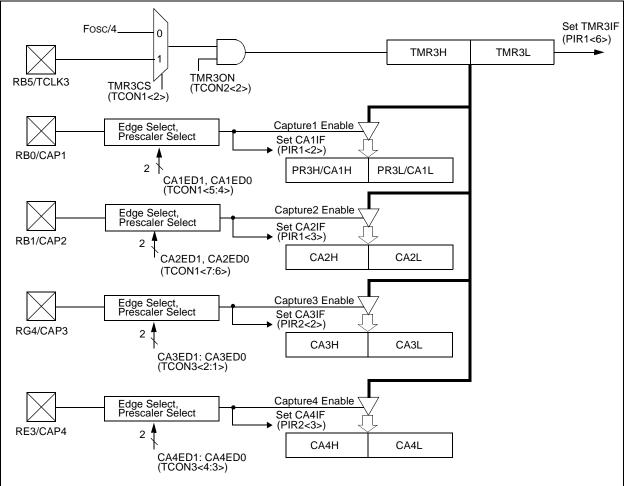

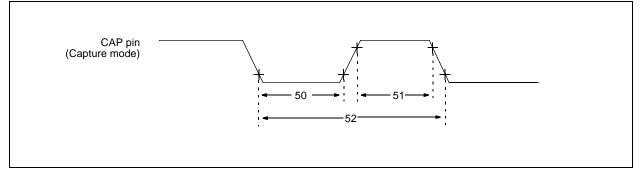

## 13.2.2 FOUR CAPTURE MODE

This mode is selected by setting bit CA1/PR3. A block diagram is shown in Figure 13-6. In this mode, TMR3 runs without a period register and increments from 0000h to FFFFh and rolls over to 0000h. The TMR3 interrupt Flag (TMR3IF) is set on this rollover. The TMR3IF bit must be cleared in software.

Registers PR3H/CA1H and PR3L/CA1L make a 16-bit capture register (Capture1). It captures events on pin RB0/CAP1. Capture mode is configured by the CA1ED1 and CA1ED0 bits. Capture1 Interrupt Flag bit (CA1IF) is set upon detection of the capture event. The corresponding interrupt mask bit is CA1IE. The Capture1 Overflow Status bit is CA1OVF.

All the captures operate in the same manner. Refer to Section 13.2.1 for the operation of capture.

#### FIGURE 13-6: TIMER3 WITH FOUR CAPTURES BLOCK DIAGRAM

#### 13.2.3 READING THE CAPTURE REGISTERS

The Capture overflow status flag bits are double buffered. The master bit is set if one captured word is already residing in the Capture register and another "event" has occurred on the CAPx pin. The new event will not transfer the TMR3 value to the capture register, protecting the previous unread capture value. When the user reads both the high and the low bytes (in any order) of the Capture register, the master overflow bit is transferred to the slave overflow bit (CAxOVF) and then the master bit is reset. The user can then read TCONx to determine the value of CAxOVF.

An example of an instruction sequence to read capture registers and capture overflow flag bits is shown in Example 13-1. Depending on the capture source, different registers will need to be read.

## EXAMPLE 13-1: SEQUENCE TO READ CAPTURE REGISTERS

; Select Bank 3

```

MOVLB 3

MOVPF CA2L, LO_BYTE

MOVPF CA2H, HI_BYTE

MOVPF TCON2, STAT_VAL

```

; Read Capture2 low byte, store in LO\_BYTE ; Read Capture2 high byte, store in HI\_BYTE

```

N2, STAT_VAL ; Read TCON2 into file STAT_VAL

```

| Address       | Name      | Bit 7     | Bit 6         | Bit 5         | Bit 4         | Bit 3        | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | MCLR, WDT |

|---------------|-----------|-----------|---------------|---------------|---------------|--------------|--------|--------|--------|-------------------------|-----------|

| 16h, Bank 3   | TCON1     | CA2ED1    | CA2ED0        | CA1ED1        | CA1ED0        | T16          | TMR3CS | TMR2CS | TMR1CS | 0000 0000               | 0000 0000 |

| 17h, Bank 3   | TCON2     | CA2OVF    | CA10VF        | PWM2ON        | PWM1ON        | CA1/PR3      | TMR3ON | TMR2ON | TMR1ON | 0000 0000               | 0000 0000 |

| 16h, Bank 7   | TCON3     | —         | CA4OVF        | CA3OVF        | CA4ED1        | CA4ED0       | CA3ED1 | CA3ED0 | PWM3ON | -000 0000               | -000 0000 |

| 12h, Bank 2   | TMR3L     | Holding R | egister for t | he Low Byte   | of the 16-bit | TMR3 Reg     | ister  |        |        | xxxx xxxx               | uuuu uuuu |

| 13h, Bank 2   | TMR3H     | Holding R | egister for t | he High Byte  | of the 16-bit | TMR3 Reg     | gister |        |        | XXXX XXXX               | uuuu uuuu |

| 16h, Bank 1   | PIR1      | RBIF      | TMR3IF        | TMR2IF        | TMR1IF        | CA2IF        | CA1IF  | TX1IF  | RC1IF  | x000 0010               | u000 0010 |

| 17h, Bank 1   | PIE1      | RBIE      | TMR3IE        | TMR2IE        | TMR1IE        | CA2IE        | CA1IE  | TX1IE  | RC1IE  | 0000 0000               | 0000 0000 |

| 10h, Bank 4   | PIR2      | SSPIF     | BCLIF         | ADIF          | —             | CA4IF        | CA3IF  | TX2IF  | RC2IF  | 000- 0010               | 000- 0010 |

| 11h, Bank 4   | PIE2      | SSPIE     | BCLIE         | ADIE          | _             | CA4IE        | CA3IE  | TX2IE  | RC2IE  | 000- 0000               | 000- 0000 |

| 07h, Unbanked | INTSTA    | PEIF      | T0CKIF        | T0IF          | INTF          | PEIE         | T0CKIE | T0IE   | INTE   | 0000 0000               | 0000 0000 |

| 06h, Unbanked | CPUSTA    | _         | _             | STKAV         | GLINTD        | TO           | PD     | POR    | BOR    | 11 11qq                 | 11 qquu   |

| 16h, Bank 2   | PR3L/CA1L | Timer3 Pe | riod Regist   | er, Low Byte/ | Capture1 Re   | gister, Low  | Byte   |        |        | xxxx xxxx               | uuuu uuuu |

| 17h, Bank 2   | PR3H/CA1H | Timer3 Pe | riod Regist   | er, High Byte | /Capture1 R   | egister, Hig | h Byte |        |        | xxxx xxxx               | uuuu uuuu |

| 14h, Bank 3   | CA2L      | Capture2  | Low Byte      |               |               |              |        |        |        | xxxx xxxx               | uuuu uuuu |

| 15h, Bank 3   | CA2H      | Capture2  | High Byte     |               |               |              |        |        |        | xxxx xxxx               | uuuu uuuu |

| 12h, Bank 7   | CA3L      | Capture3  | Low Byte      |               |               |              |        |        |        | xxxx xxxx               | uuuu uuuu |

| 13h, Bank 7   | CA3H      | Capture3  | High Byte     |               |               |              |        |        |        | xxxx xxxx               | uuuu uuuu |

| 14h, Bank 7   | CA4L      | Capture4  | Low Byte      |               |               |              |        |        |        | xxxx xxxx               | uuuu uuuu |

| 15h, Bank 7   | CA4H      | Capture4  | High Byte     |               |               |              |        |        |        | xxxx xxxx               | uuuu uuuu |

# TABLE 13-6: REGISTERS ASSOCIATED WITH CAPTURE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0', q = value depends on condition. Shaded cells are not used by Capture.

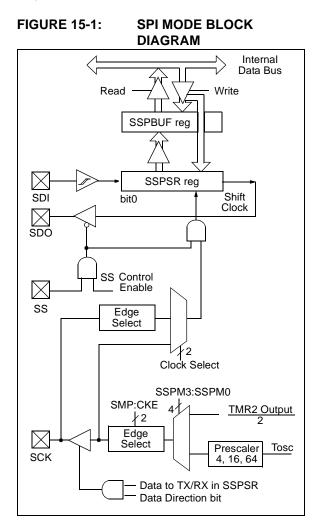

# 15.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit<sup>™</sup> (I<sup>2</sup>C)

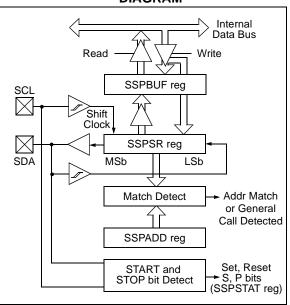

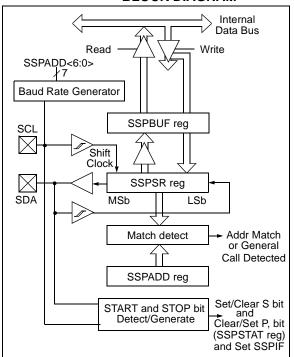

Figure 15-1 shows a block diagram for the SPI mode, while Figure 15-2 and Figure 15-3 show the block diagrams for the two different  $I^2C$  modes of operation.

# FIGURE 15-2:

#### I<sup>2</sup>C SLAVE MODE BLOCK DIAGRAM

#### I<sup>2</sup>C MASTER MODE BLOCK DIAGRAM

## 15.1.5 SLAVE MODE

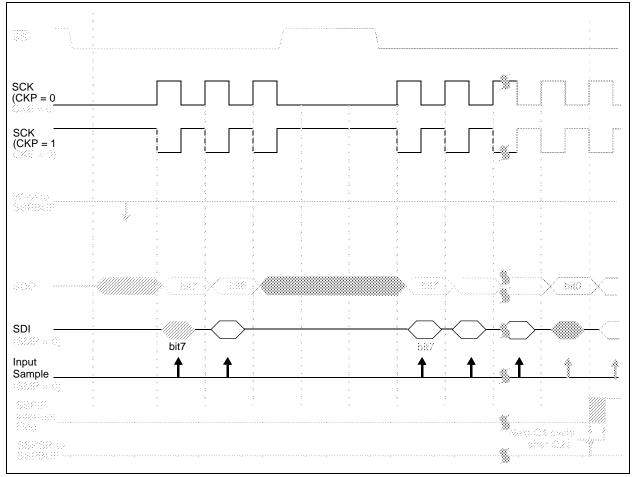

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the interrupt flag bit SSPIF (PIR2<7>) is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in SLEEP mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from SLEEP.

#### 15.1.6 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 04h). The pin must not be driven low for the  $\overline{SS}$  pin to function as an input. The RA2 Data Latch must be high. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and

the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable, depending on the application.

- Note 1: When the SPI is in Slave mode with  $\overline{SS}$ pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the  $\overline{SS}$ pin is set to VDD.

- 2: If the SPI is used in Slave mode with CKE = '1', then the SS pin control must be enabled.

When the SPI module resets, the bit counter is forced to 0. This can be done by either forcing the  $\overline{SS}$  pin to a high level, or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function), since it cannot create a bus conflict.

# FIGURE 15-7: SLAVE SYNCHRONIZATION WAVEFORM

# 16.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The analog-to-digital (A/D) converter module has twelve analog inputs for the PIC17C75X devices and sixteen for the PIC17C76X devices.

The analog input charges a sample and hold capacitor. The output of the sample and hold capacitor is the input into the converter. The converter then generates a digital result of this analog level via successive approximation. This A/D conversion of the analog input signal, results in a corresponding 10-bit digital number.

The analog reference voltages (positive and negative supply) are software selectable to either the device's supply voltages (AVDD, AVss), or the voltage level on the RG3/AN0/VREF+ and RG2/AN1/VREF- pins.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D clock must be derived from the A/D's internal RC oscillator.

The A/D module has four registers. These registers are:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register0 (ADCON0)

- A/D Control Register1 (ADCON1)

The ADCON0 register, shown in Register 16-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 16-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RG3 and RG2 can also be the voltage references), or as digital I/O.

|         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0        | R/W-0       | R/W-0       | U-0         | R/W-0                   | U-0           | R/W-0      |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|-------------|-------------|-------------------------|---------------|------------|--|--|--|

|         | CHS3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CHS2         | CHS1        | CHS0        | —           | GO/DONE                 | —             | ADON       |  |  |  |

|         | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |             |             |             | L                       |               | bit 0      |  |  |  |

| bit 7-4 | CHS3:CHS0: Analog Channel Select bits<br>0000 = channel 0, (AN0)<br>0001 = channel 1, (AN1)<br>0010 = channel 2, (AN2)<br>0011 = channel 3, (AN3)<br>0100 = channel 4, (AN4)<br>0101 = channel 5, (AN5)<br>0110 = channel 6, (AN6)<br>0111 = channel 7, (AN7)<br>1000 = channel 8, (AN8)<br>1001 = channel 9, (AN9)<br>1010 = channel 10, (AN10)<br>1011 = channel 11, (AN11)<br>1100 = channel 12, (AN12) (PIC17C76X only)<br>1101 = channel 13, (AN13) (PIC17C76X only)<br>1110 = channel 14, (AN14) (PIC17C76X only)<br>1111 = channel 15, (AN15) (PIC17C76X only)<br>1112 = channel 15, (AN15) (PIC17C75X only) |              |             |             |             |                         |               |            |  |  |  |

| bit 3   | Unimplem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ented: Read  | as '0'      |             |             |                         |               |            |  |  |  |

| bit 2   | GO/DONE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | : A/D Conver | sion Status | bit         |             |                         |               |            |  |  |  |

|         | cleared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              | when the A  | •           |             | ) conversion, v<br>ete) | which is auto | omatically |  |  |  |

| bit 1   | Unimplem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ented: Read  | as '0'      |             |             |                         |               |            |  |  |  |

| bit 0   | ADON: A/D On bit<br>1 = A/D converter module is operating<br>0 = A/D converter module is shut-off and consumes no operating current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |             |             |             |                         |               |            |  |  |  |

|         | Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |             |             |             |                         |               |            |  |  |  |

|         | R = Reada                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | able bit     | W = W       | ritable bit | U = Unim    | nplemented bi           | t, read as '0 | ,          |  |  |  |

|         | - n = Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | e at POR Res | et '1' = B  | it is set   | '0' = Bit i | s cleared               | x = Bit is un | known      |  |  |  |

### REGISTER 16-1: ADCON0 REGISTER (ADDRESS: 14h, BANK 5)

| INCF              | Incremen                                                        | Increment f                 |             |                       |  |  |  |  |

|-------------------|-----------------------------------------------------------------|-----------------------------|-------------|-----------------------|--|--|--|--|

| Syntax:           | [ label ]                                                       | INCF f                      | ,d          |                       |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \end{array}$ | 5                           |             |                       |  |  |  |  |

| Operation:        | (f) + 1 $\rightarrow$ (                                         | dest)                       |             |                       |  |  |  |  |

| Status Affected:  | OV, C, DC                                                       | ;, Z                        |             |                       |  |  |  |  |

| Encoding:         | 0001                                                            | 010d                        | ffff        | ffff                  |  |  |  |  |

| Description:      | The conten<br>mented. If '<br>WREG. If 'c<br>back in regi       | d' is 0, th<br>l' is 1, the | e result is | placed in             |  |  |  |  |

| Words:            | 1                                                               | 1                           |             |                       |  |  |  |  |

| Cycles:           | 1                                                               |                             |             |                       |  |  |  |  |

| Q Cycle Activity: |                                                                 |                             |             |                       |  |  |  |  |

| Q1                | Q2                                                              | Q3                          |             | Q4                    |  |  |  |  |

| Decode            | Read<br>register 'f'                                            | Proce<br>Dat                |             | Vrite to<br>stination |  |  |  |  |

| Example:          | INCF                                                            | CNT,                        | 1           |                       |  |  |  |  |

| Before Instr      |                                                                 |                             |             |                       |  |  |  |  |

| CNT<br>Z<br>C     | = 0xFF<br>= 0<br>= ?                                            |                             |             |                       |  |  |  |  |

| After Instruc     | tion                                                            |                             |             |                       |  |  |  |  |

| CNT<br>Z<br>C     | = 0x00<br>= 1<br>= 1                                            |                             |             |                       |  |  |  |  |

|                   |                                                                 |                             |             |                       |  |  |  |  |

| INC        | FSZ                                   | Incremen                                                                     | t f, skip if O                                                                                                                                                                                                                                                                             | )                    |  |  |  |

|------------|---------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| Synt       | ax:                                   | [ label ]                                                                    | INCFSZ f,o                                                                                                                                                                                                                                                                                 | d                    |  |  |  |

| Ope        | rands:                                | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \end{array}$              | 5                                                                                                                                                                                                                                                                                          |                      |  |  |  |

| Ope        | ration:                               | (f) + 1 $\rightarrow$ (skip if resu                                          |                                                                                                                                                                                                                                                                                            |                      |  |  |  |

| State      | us Affected:                          | None                                                                         |                                                                                                                                                                                                                                                                                            |                      |  |  |  |

| Enco       | oding:                                | 0001                                                                         | 111d ff                                                                                                                                                                                                                                                                                    | ff ffff              |  |  |  |

| Des        | cription:                             | mented. If '<br>WREG. If 'c<br>back in regi<br>If the result<br>which is alr | The contents of register 'f' are incre-<br>mented. If 'd' is 0, the result is placed in<br>WREG. If 'd' is 1, the result is placed<br>back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched is discarded<br>and a NOP is executed instead, making |                      |  |  |  |

| Wor        | ds:                                   | 1                                                                            |                                                                                                                                                                                                                                                                                            |                      |  |  |  |

| Cycl       | es:                                   | 1(2)                                                                         |                                                                                                                                                                                                                                                                                            |                      |  |  |  |

| QC         | ycle Activity:                        |                                                                              |                                                                                                                                                                                                                                                                                            |                      |  |  |  |

|            | Q1                                    | Q2                                                                           | Q3                                                                                                                                                                                                                                                                                         | Q4                   |  |  |  |

|            | Decode                                | Read<br>register 'f'                                                         | Process<br>Data                                                                                                                                                                                                                                                                            | Write to destination |  |  |  |

| lf sk      | ip:                                   |                                                                              |                                                                                                                                                                                                                                                                                            |                      |  |  |  |

|            | Q1                                    | Q2                                                                           | Q3                                                                                                                                                                                                                                                                                         | Q4                   |  |  |  |

|            | No                                    | No                                                                           | No                                                                                                                                                                                                                                                                                         | No                   |  |  |  |

|            | operation                             | operation                                                                    | operation                                                                                                                                                                                                                                                                                  | operation            |  |  |  |

| <u>Exa</u> | <u>mple</u> :                         | NZERO                                                                        | INCFSZ C<br>:<br>:                                                                                                                                                                                                                                                                         | NT, 1                |  |  |  |

|            | Before Instru<br>PC                   |                                                                              | G (HERE)                                                                                                                                                                                                                                                                                   |                      |  |  |  |

|            | After Instruct<br>CNT<br>If CNT<br>PC | = CNT +<br>= 0;                                                              | <b>1</b><br>S(ZERO)                                                                                                                                                                                                                                                                        |                      |  |  |  |

- If CNT  $\neq$  0;

- PC = Address (NZERO)

| MULLW                                                                             | Multiply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Literal with \           | WREG                                  | MULV         | VF                                                                                              | Multiply                                                                                                                                                                                                                                                                                                                                                                                                                       | WREG w                                                 | vith f |                                       |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------------|--------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------|---------------------------------------|

| Syntax:                                                                           | [ label ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MULLW k                  |                                       | Syntax       | C.                                                                                              | [ label ]                                                                                                                                                                                                                                                                                                                                                                                                                      | MULWF                                                  | f      |                                       |