Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 16MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 66                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 678 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 16x10b                                                                  |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c762t-16e-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Register Address     |     | Power-on Reset<br>Brown-out Reset | MCLR Reset<br>WDT Reset | Wake-up from SLEEP<br>through Interrupt |  |

|----------------------|-----|-----------------------------------|-------------------------|-----------------------------------------|--|

| Bank 7               |     |                                   |                         |                                         |  |

| PW3DCL               | 10h | xx0                               | uu0                     | uuu                                     |  |

| PW3DCH               | 11h | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |  |

| CA3L                 | 12h | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |  |

| САЗН                 | 13h | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |  |

| CA4L                 | 14h | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |  |

| CA4H                 | 15h | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |  |

| TCON3                | 16h | -000 0000                         | -000 0000               | -uuu uuuu                               |  |

| Unimplemented        | 17h |                                   |                         |                                         |  |

| Bank 8               |     |                                   |                         |                                         |  |

| DDRH                 | 10h | 1111 1111                         | 1111 1111               | uuuu uuuu                               |  |

| PORTH <sup>(4)</sup> | 11h | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |

| DDRJ                 | 12h | 1111 1111                         | 1111 1111               | uuuu uuuu                               |  |

| PORTJ <sup>(4)</sup> | 13h | xxxx xxxx                         | uuuu uuuu               | սսսս սսսս                               |  |

| Unbanked             |     |                                   |                         |                                         |  |

| PRODL                | 18h | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |  |

| PRODH                | 19h | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |

|                      |     |                                   |                         |                                         |  |

#### TABLE 5-4: INITIALIZATION CONDITIONS FOR SPECIAL FUNCTION REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented, read as '0', q = value depends on condition

Note 1: One or more bits in INTSTA, PIR1, PIR2 will be affected (to cause wake-up).

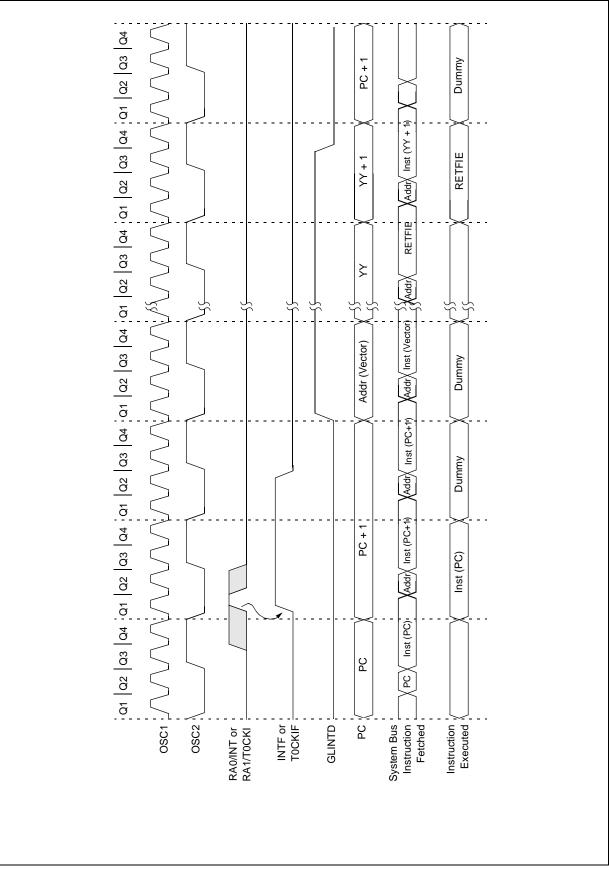

2: When the wake-up is due to an interrupt and the GLINTD bit is cleared, the PC is loaded with the interrupt vector.

3: See Table 5-3 for RESET value of specific condition.

4: This is the value that will be in the port output latch.

**5:** When the device is configured for Microprocessor or Extended Microcontroller mode, the operation of this port does not rely on these registers.

6: On any device RESET, these pins are configured as inputs.

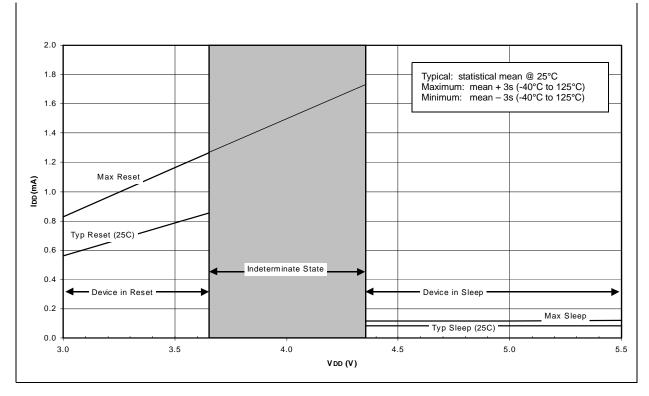

#### 5.1.5 BROWN-OUT RESET (BOR)

PIC17C7XX devices have on-chip Brown-out Reset circuitry. This circuitry places the device into a RESET when the device voltage falls below a trip point (BVDD). This ensures that the device does not continue program execution outside the valid operation range of the device. Brown-out Resets are typically used in AC line applications, or large battery applications, where large loads may be switched in (such as automotive).

| Note: | Before using the on-chip Brown-out for a |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|

|       | voltage supervisory function, please     |  |  |  |  |  |  |

|       | review the electrical specifications to  |  |  |  |  |  |  |

|       | ensure that they meet your requirements. |  |  |  |  |  |  |

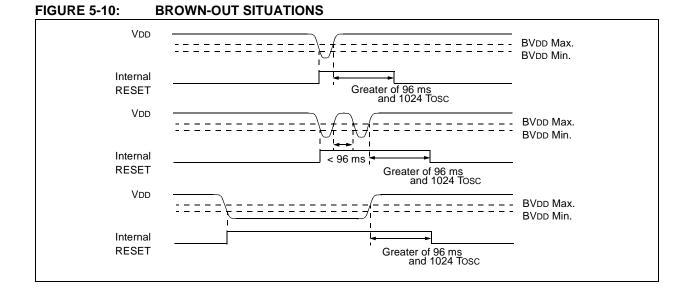

The BODEN configuration bit can disable (if clear/ programmed), or enable (if set) the Brown-out Reset circuitry. If VDD falls below BVDD (typically 4.0 V, paramter #D005 in electrical specification section), for greater than parameter #35, the Brown-out situation will reset the chip. A RESET is not guaranteed to occur if VDD falls below BVDD for less than paramter #35. The chip will remain in Brown-out Reset until VDD rises above BVDD. The Power-up Timer and Oscillator Startup Timer will then be invoked. This will keep the chip in RESET the greater of 96 ms and 1024 Tosc. If VDD drops below BVDD while the Power-up Timer/Oscillator Start-up Timer is running, the chip will go back into a Brown-out Reset. The Power-up Timer/Oscillator Startup Timer will be initialized. Once VDD rises above BVDD, the Power-up Timer/Oscillator Start-up Timer will start their time delays. Figure 5-10 shows typical Brown-out situations.

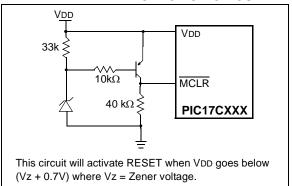

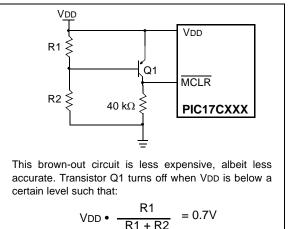

In some applications, the Brown-out Reset trip point of the device may not be at the desired level. Figure 5-8 and Figure 5-9 are two examples of external circuitry that may be implemented. Each needs to be evaluated to determine if they match the requirements of the application.

#### EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

FIGURE 5-9:

#### EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

© 1998-2013 Microchip Technology Inc.

NOTES:

## 8.0 TABLE READS AND TABLE WRITES

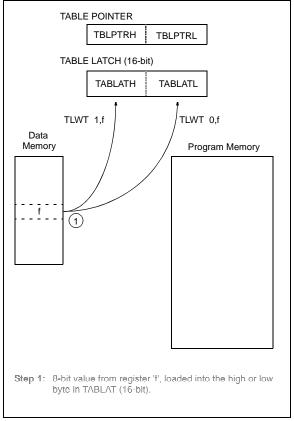

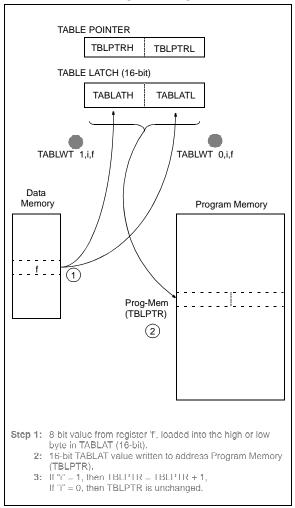

The PIC17C7XX has four instructions that allow the processor to move data from the data memory space to the program memory space, and vice versa. Since the program memory space is 16-bits wide and the data memory space is 8-bits wide, two operations are required to move 16-bit values to/from the data memory.

The TLWT t, f and TABLWT t, i, f instructions are used to write data from the data memory space to the program memory space. The TLRD t, f and TABLRD t, i, f instructions are used to write data from the program memory space to the data memory space.

The program memory can be internal or external. For the program memory access to be external, the device needs to be operating in Microprocessor or Extended Microcontroller mode.

Figure 8-1 through Figure 8-4 show the operation of these four instructions. The steps show the sequence of operation.

#### FIGURE 8-1: TLWT INSTRUCTION OPERATION

#### FIGURE 8-2: TABLWT INSTRUCTION OPERATION

|       | R-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R-0                                                                   | R/W-0                        | R/W-0          | R/W-0   | R/W-0                   | R/W-0         | R/W-0     |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------|----------------|---------|-------------------------|---------------|-----------|--|--|

|       | CA2OVF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CA10VF                                                                | PWM2ON                       | PWM10N         | CA1/PR3 | TMR3ON                  | TMR2ON        | TMR10N    |  |  |

|       | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                       |                              |                |         |                         |               | bit 0     |  |  |

| bit 7 | <b>CA2OVF</b> : Capture2 Overflow Status bit<br>This bit indicates that the capture value had not been read from the capture register pair<br>(CA2H:CA2L) before the next capture event occurred. The capture register retains the oldest<br>unread capture value (last capture before overflow). Subsequent capture events will not update<br>the capture register with the TMR3 value until the capture register has been read (both bytes).<br>1 = Overflow occurred on Capture2 register<br>0 = No overflow occurred on Capture2 register                                 |                                                                       |                              |                |         |                         |               |           |  |  |

| bit 6 | <ul> <li>CA10VF: Capture1 Overflow Status bit</li> <li>This bit indicates that the capture value had not been read from the capture register pair (PR3H/CA1H:PR3L/CA1L), before the next capture event occurred. The capture register retains the oldest unread capture value (last capture before overflow). Subsequent capture events will not update the capture register with the TMR3 value until the capture register has been read (both bytes).</li> <li>1 = Overflow occurred on Capture1 register</li> <li>0 = No overflow occurred on Capture1 register</li> </ul> |                                                                       |                              |                |         |                         |               |           |  |  |

| bit 5 | <b>PWM2ON</b> :<br>1 = PWM2<br>(The R<br>0 = PWM2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PWM2 On I<br>is enabled<br>B3/PWM2 pi<br>is disabled                  | bit<br>n ignores the         | e state of the |         | oit.)<br>for data direc | tion.)        |           |  |  |

| bit 4 | <b>PWM1ON</b> : PWM1 On bit<br>1 = PWM1 is enabled<br>(The RB2/PWM1 pin ignores the state of the DDRB<2> bit.)<br>0 = PWM1 is disabled<br>(The RB2/PWM1 pin uses the state of the DDRB<2> bit for data direction.)                                                                                                                                                                                                                                                                                                                                                            |                                                                       |                              |                |         |                         |               |           |  |  |

| bit 3 | 1 =Enable<br>(PR3H)<br>0 =Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | /CA1H:PR3L<br>s the Period                                            | /CA1L is the register        |                | -       | r3 runs witho<br>r3.)   | ut a period r | egister.) |  |  |

| bit 2 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Timer3 On b<br>Timer3                                                 |                              |                |         | ,                       |               |           |  |  |

| bit 1 | <ul> <li>TMR2ON: Timer2 On bit</li> <li>This bit controls the incrementing of the TMR2 register. When TMR2:TMR1 form the 16-bit timer (T16 is set), TMR2ON must be set. This allows the MSB of the timer to increment.</li> <li>1 = Starts Timer2 (must be enabled if the T16 bit (TCON1&lt;3&gt;) is set)</li> <li>0 = Stops Timer2</li> </ul>                                                                                                                                                                                                                               |                                                                       |                              |                |         |                         |               |           |  |  |

| bit 0 | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Timer1 On b                                                           | oit                          |                |         |                         |               |           |  |  |

|       | <u>When T16</u><br>1 = Starts 7<br>0 = Stops 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>is set (in 16</u><br>16-bit TMR2<br>16-bit TMR2:<br>is clear (in 8 | bit Timer mo<br>TMR1<br>TMR1 |                |         |                         |               |           |  |  |

## REGISTER 13-2: TCON2 REGISTER (ADDRESS: 17h, BANK 3)

#### 13.2.3 READING THE CAPTURE REGISTERS

The Capture overflow status flag bits are double buffered. The master bit is set if one captured word is already residing in the Capture register and another "event" has occurred on the CAPx pin. The new event will not transfer the TMR3 value to the capture register, protecting the previous unread capture value. When the user reads both the high and the low bytes (in any order) of the Capture register, the master overflow bit is transferred to the slave overflow bit (CAxOVF) and then the master bit is reset. The user can then read TCONx to determine the value of CAxOVF.

An example of an instruction sequence to read capture registers and capture overflow flag bits is shown in Example 13-1. Depending on the capture source, different registers will need to be read.

#### EXAMPLE 13-1: SEQUENCE TO READ CAPTURE REGISTERS

; Select Bank 3

```

MOVLB 3

MOVPF CA2L, LO_BYTE

MOVPF CA2H, HI_BYTE

MOVPF TCON2, STAT_VAL

```

; Read Capture2 low byte, store in LO\_BYTE ; Read Capture2 high byte, store in HI\_BYTE

```

N2, STAT_VAL ; Read TCON2 into file STAT_VAL

```

| Address       | Name      | Bit 7              | Bit 6              | Bit 5         | Bit 4         | Bit 3        | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | MCLR, WDT |

|---------------|-----------|--------------------|--------------------|---------------|---------------|--------------|--------|--------|--------|-------------------------|-----------|

| 16h, Bank 3   | TCON1     | CA2ED1             | CA2ED0             | CA1ED1        | CA1ED0        | T16          | TMR3CS | TMR2CS | TMR1CS | 0000 0000               | 0000 0000 |

| 17h, Bank 3   | TCON2     | CA2OVF             | CA10VF             | PWM2ON        | PWM1ON        | CA1/PR3      | TMR3ON | TMR2ON | TMR1ON | 0000 0000               | 0000 0000 |

| 16h, Bank 7   | TCON3     | —                  | CA4OVF             | CA3OVF        | CA4ED1        | CA4ED0       | CA3ED1 | CA3ED0 | PWM3ON | -000 0000               | -000 0000 |

| 12h, Bank 2   | TMR3L     | Holding R          | egister for t      | he Low Byte   | of the 16-bit | TMR3 Reg     | ister  |        |        | xxxx xxxx               | uuuu uuuu |

| 13h, Bank 2   | TMR3H     | Holding R          | egister for t      | he High Byte  | of the 16-bit | TMR3 Reg     | gister |        |        | XXXX XXXX               | uuuu uuuu |

| 16h, Bank 1   | PIR1      | RBIF               | TMR3IF             | TMR2IF        | TMR1IF        | CA2IF        | CA1IF  | TX1IF  | RC1IF  | x000 0010               | u000 0010 |

| 17h, Bank 1   | PIE1      | RBIE               | TMR3IE             | TMR2IE        | TMR1IE        | CA2IE        | CA1IE  | TX1IE  | RC1IE  | 0000 0000               | 0000 0000 |

| 10h, Bank 4   | PIR2      | SSPIF              | BCLIF              | ADIF          | —             | CA4IF        | CA3IF  | TX2IF  | RC2IF  | 000- 0010               | 000- 0010 |

| 11h, Bank 4   | PIE2      | SSPIE              | BCLIE              | ADIE          | _             | CA4IE        | CA3IE  | TX2IE  | RC2IE  | 000- 0000               | 000- 0000 |

| 07h, Unbanked | INTSTA    | PEIF               | T0CKIF             | T0IF          | INTF          | PEIE         | T0CKIE | T0IE   | INTE   | 0000 0000               | 0000 0000 |

| 06h, Unbanked | CPUSTA    | _                  | _                  | STKAV         | GLINTD        | TO           | PD     | POR    | BOR    | 11 11qq                 | 11 qquu   |

| 16h, Bank 2   | PR3L/CA1L | Timer3 Pe          | riod Regist        | er, Low Byte/ | Capture1 Re   | gister, Low  | v Byte |        |        | xxxx xxxx               | uuuu uuuu |

| 17h, Bank 2   | PR3H/CA1H | Timer3 Pe          | riod Regist        | er, High Byte | /Capture1 R   | egister, Hig | h Byte |        |        | xxxx xxxx               | uuuu uuuu |

| 14h, Bank 3   | CA2L      | Capture2           | Low Byte           |               |               |              |        |        |        | xxxx xxxx               | uuuu uuuu |

| 15h, Bank 3   | CA2H      | Capture2           | Capture2 High Byte |               |               |              |        |        |        |                         | uuuu uuuu |

| 12h, Bank 7   | CA3L      | Capture3 Low Byte  |                    |               |               |              |        |        |        | xxxx xxxx               | uuuu uuuu |

| 13h, Bank 7   | CA3H      | Capture3 High Byte |                    |               |               |              |        |        |        | xxxx xxxx               | uuuu uuuu |

| 14h, Bank 7   | CA4L      | Capture4           | Low Byte           |               |               |              |        |        |        | xxxx xxxx               | uuuu uuuu |

| 15h, Bank 7   | CA4H      | Capture4           | High Byte          |               |               |              |        |        |        | xxxx xxxx               | uuuu uuuu |

### TABLE 13-6: REGISTERS ASSOCIATED WITH CAPTURE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0', q = value depends on condition. Shaded cells are not used by Capture.

| Address     | Name   | Bit 7     | Bit 6    | Bit 5      | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | MCLR, WDT |

|-------------|--------|-----------|----------|------------|--------|-------|-------|-------|-------|-------------------------|-----------|

| 16h, Bank 1 | PIR1   | RBIF      | TMR3IF   | TMR2IF     | TMR1IF | CA2IF | CA1IF | TX1IF | RC1IF | x000 0010               | u000 0010 |

| 17h, Bank 1 | PIE1   | RBIE      | TMR3IE   | TMR2IE     | TMR1IE | CA2IE | CA1IE | TX1IE | RC1IE | 0000 0000               | 0000 0000 |

| 13h, Bank 0 | RCSTA1 | SPEN      | RX9      | SREN       | CREN   |       | FERR  | OERR  | RX9D  | 0000 - 00x              | 0000 -00u |

| 14h, Bank 0 | RCREG1 | RX7       | RX6      | RX5        | RX4    | RX3   | RX2   | RX1   | RX0   | xxxx xxxx               | uuuu uuuu |

| 15h, Bank 0 | TXSTA1 | CSRC      | TX9      | TXEN       | SYNC   | _     | _     | TRMT  | TX9D  | 00001x                  | 00001u    |

| 17h, Bank 0 | SPBRG1 | Baud Rate | Generato | r Register |        |       |       |       |       | 0000 0000               | 0000 0000 |

| 10h, Bank 4 | PIR2   | SSPIF     | BCLIF    | ADIF       | _      | CA4IF | CA3IF | TX2IF | RC2IF | 000- 0010               | 000- 0010 |

| 11h, Bank 4 | PIE2   | SSPIE     | BCLIE    | ADIE       | —      | CA4IE | CA3IE | TX2IE | RC2IE | 000- 0000               | 000- 0000 |

| 13h, Bank 4 | RCSTA2 | SPEN      | RX9      | SREN       | CREN   | _     | FERR  | OERR  | RX9D  | 0000 -00x               | 0000 -00u |

| 14h, Bank 4 | RCREG2 | RX7       | RX6      | RX5        | RX4    | RX3   | RX2   | RX1   | RX0   | xxxx xxxx               | uuuu uuuu |

| 15h, Bank 4 | TXSTA2 | CSRC      | TX9      | TXEN       | SYNC   | _     | —     | TRMT  | TX9D  | 00001x                  | 00001u    |

| 17h, Bank 4 | SPBRG2 | Baud Rate | Generato | r Register |        |       |       |       |       | 0000 0000               | 0000 0000 |

#### TABLE 14-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, u = unchanged, - = unimplemented, read as a '0'. Shaded cells are not used for synchronous master reception.

## 15.2.12 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the receive enable bit, RCEN (SSPCON2<3>).

| Note: | The SSP Module must be in an IDLE        |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|

|       | STATE before the RCEN bit is set, or the |  |  |  |  |  |  |

|       | RCEN bit will be disregarded.            |  |  |  |  |  |  |

The baud rate generator begins counting and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag is set, the SSPIF is set and the baud rate generator is suspended from counting, holding SCL low. The SSP is now in IDLE state, awaiting the next command. When the buffer is read by the CPU, the BF flag is automatically cleared. The user can then send an acknowledge bit at the end of reception, by setting the acknowledge sequence enable bit, ACKEN (SSPCON2<4>).

#### 15.2.12.1 BF Status Flag

In receive operation, BF is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when SSPBUF is read.

#### 15.2.12.2 SSPOV Status Flag

In receive operation, SSPOV is set when 8 bits are received into the SSPSR, and the BF flag is already set from a previous reception.

#### 15.2.12.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

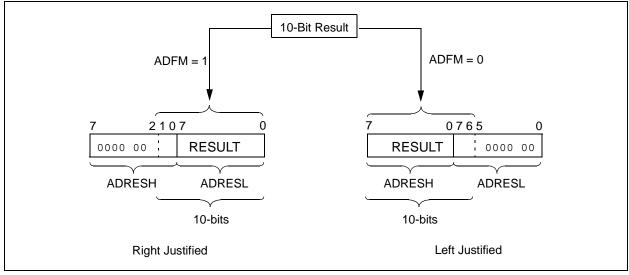

#### 16.4.1 A/D RESULT REGISTERS

The ADRESH:ADRESL register pair is the location where the 10-bit A/D result is loaded at the completion of the A/D conversion. This register pair is 16-bits wide. The A/D module gives the flexibility to left or right justify the 10-bit result in the 16-bit result register. The A/D Format Select bit (ADFM) controls this justification. Figure 16-6 shows the operation of the A/D result justification. The extra bits are loaded with '0's'. When an A/ D result will not overwrite these locations (A/D disable), these registers may be used as two general purpose 8bit registers.

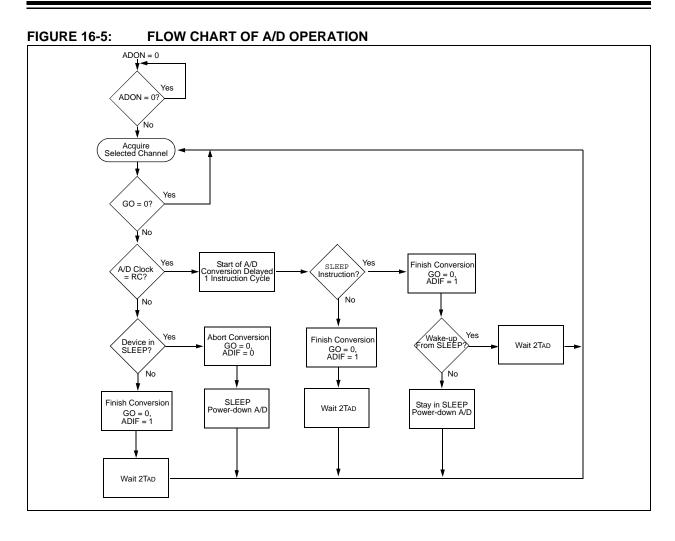

## 16.5 A/D Operation During SLEEP

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared, and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from

#### FIGURE 16-6: A/D RESULT JUSTIFICATION

SLEEP. If the A/D interrupt is not enabled, the A/D module will then be turned off, although the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

Note: For the A/D module to operate in SLEEP, the A/D clock source must be set to RC (ADCS1:ADCS0 = 11). To allow the conversion to occur during SLEEP, ensure the SLEEP instruction immediately follows the instruction that sets the GO/DONE bit.

### 16.6 Effects of a RESET

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off, and any conversion is aborted.

The value that is in the ADRESH:ADRESL registers is not modified for a Power-on Reset. The ADRESH:ADRESL registers will contain unknown data after a Power-on Reset.

Table 18-2 lists the instructions recognized by the MPASM assembler.

**Note 1:** Any unused opcode is Reserved. Use of any reserved opcode may cause unexpected operation.

All instruction examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

To represent a binary number:

0000 0100b

where b signifies a binary string.

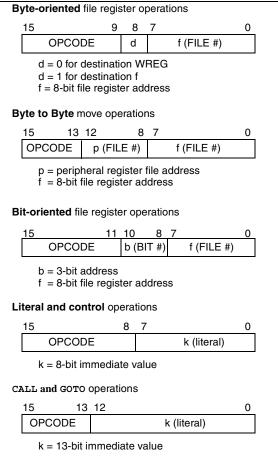

## FIGURE 18-1: GENERAL FORMAT FOR INSTRUCTIONS

## 18.1 Special Function Registers as Source/Destination

The PIC17C7XX's orthogonal instruction set allows read and write of all file registers, including special function registers. There are some special situations the user should be aware of:

#### 18.1.1 ALUSTA AS DESTINATION

If an instruction writes to ALUSTA, the Z, C, DC and OV bits may be set or cleared as a result of the instruction and overwrite the original data bits written. For example, executing CLRF ALUSTA will clear register ALUSTA and then set the Z bit leaving 0000 0100b in the register.

#### 18.1.2 PCL AS SOURCE OR DESTINATION

Read, write or read-modify-write on PCL may have the following results:

| Read PC:           | $PCH \to PCLATH;  PCL \to dest$                                                              |

|--------------------|----------------------------------------------------------------------------------------------|

| Write PCL:         | PCLATH $\rightarrow$ PCH;<br>8-bit destination value $\rightarrow$ PCL                       |

| Read-Modify-Write: | PCL $\rightarrow$ ALU operand<br>PCLATH $\rightarrow$ PCH;<br>8-bit result $\rightarrow$ PCL |

Where PCH = program counter high byte (not an addressable register), PCLATH = Program counter high holding latch, dest = destination, WREG or f.

#### 18.1.3 BIT MANIPULATION

All bit manipulation instructions are done by first reading the entire register, operating on the selected bit and writing the result back (read-modify-write (R-M-W)). The user should keep this in mind when operating on some special function registers, such as ports.

| Note: | Status bits that are manipulated by the        |

|-------|------------------------------------------------|

|       | device (including the interrupt flag bits) are |

|       | set or cleared in the Q1 cycle. So, there is   |

|       | no issue on doing R-M-W instructions on        |

|       | registers which contain these bits             |

| SWA        | APF                                                    | Swap f                                                                    |                         |                             |                       |

|------------|--------------------------------------------------------|---------------------------------------------------------------------------|-------------------------|-----------------------------|-----------------------|

| Synt       | tax:                                                   | [label]                                                                   | SWAPF                   | f,d                         |                       |

| Ope        | rands:                                                 | $\begin{array}{l} 0 \leq f \leq 25 \\ d \in \left[0,1\right] \end{array}$ | 5                       |                             |                       |

| Ope        | ration:                                                | $f<3:0> \rightarrow f<7:4> \rightarrow$                                   |                         | ,                           |                       |

| State      | us Affected:                                           | None                                                                      |                         |                             |                       |

| Enc        | oding:                                                 | 0001                                                                      | 110d                    | ffff                        | ffff                  |

| Des        | cription:                                              | The upper<br>'f' are exch<br>placed in V<br>placed in re                  | anged. If<br>VREG. If ' | 'd' is 0, th<br>d' is 1, th | e result is           |

| Wor        | ds:                                                    | 1                                                                         |                         |                             |                       |

| Cycl       | les:                                                   | 1                                                                         |                         |                             |                       |

| QC         | ycle Activity:                                         |                                                                           |                         |                             |                       |

|            | Q1                                                     | Q2                                                                        | Q3                      | 3                           | Q4                    |

|            | Decode                                                 | Read<br>register 'f'                                                      | Proce<br>Dat            |                             | Vrite to<br>stination |

| <u>Exa</u> | mple:<br>Before Instru<br>REG<br>After Instruct<br>REG | iction<br>= 0x53                                                          | REG,                    | 0                           |                       |

| ТАВ                                                  | LRD          | Tab                 | le Rea                                                                                                                                                                                  | ad                       |                                                          |                    |  |  |

|------------------------------------------------------|--------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------|--------------------|--|--|

| Synt                                                 | ax:          | [ <i>la</i>         | bel]                                                                                                                                                                                    | TABLRD                   | t,i,f                                                    |                    |  |  |

| Ope                                                  | rands:       | i∈                  | f ≤ 258<br>[0,1]<br>[0,1]                                                                                                                                                               | 5                        |                                                          |                    |  |  |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$ |              |                     |                                                                                                                                                                                         |                          |                                                          | BLAT;              |  |  |

| Statu                                                | us Affected  | : No                | None                                                                                                                                                                                    |                          |                                                          |                    |  |  |

| Enco                                                 | oding:       | 1                   | 010                                                                                                                                                                                     | 10ti                     | ffff                                                     | ffff               |  |  |

| Deso                                                 | cription:    | 1.                  | is mov<br>If t = 1                                                                                                                                                                      | ved to reg<br>: the high | ble latch (<br>ister file 'f'<br>byte is m<br>byte is mo | oved;              |  |  |

|                                                      |              | 2.                  | <ol> <li>Then, the contents of the pro-<br/>gram memory location pointed to<br/>by the 16-bit Table Pointer<br/>(TBLPTR) are loaded into the<br/>16-bit Table Latch (TBLAT).</li> </ol> |                          |                                                          |                    |  |  |

|                                                      |              | 3.                  | <ol> <li>If i = 1: TBLPTR is incremented;<br/>If i = 0: TBLPTR is not<br/>incremented.</li> </ol>                                                                                       |                          |                                                          |                    |  |  |

| Wor                                                  | ds:          | 1                   | 1                                                                                                                                                                                       |                          |                                                          |                    |  |  |

| Cycl                                                 | es:          | 2 (3                | 2 (3-cycle if f = PCL)                                                                                                                                                                  |                          |                                                          |                    |  |  |

| QC                                                   | cle Activity | /:                  |                                                                                                                                                                                         |                          |                                                          |                    |  |  |

|                                                      | Q1           | Q                   | 2                                                                                                                                                                                       | Q3                       | (                                                        | Q4                 |  |  |

|                                                      | Decode       | Re<br>regi:<br>TBLA | ster                                                                                                                                                                                    | Proces<br>Data           | -                                                        | /rite<br>ister 'f' |  |  |

| Decode    | Read           | Process   | Write         |

|-----------|----------------|-----------|---------------|

|           | register       | Data      | register 'f'  |

|           | TBLATH or      |           |               |

|           | TBLATL         |           |               |

| No        | No             | No        | No            |

| operation | operation      | operation | operation     |

|           | (Table Pointer |           | (OE goes low) |

|           | on Address     |           |               |

|           | bus)           |           |               |

### 19.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC16F87X and can be used to develop for this and other PIC microcontrollers from the PIC16CXXX family. The MPLAB ICD utilizes the in-circuit debugging capability built into the PIC16F87X. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

### 19.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC MCU devices. It can also set code protection in this mode.

### 19.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

#### 19.11 PICDEM 1 Low Cost PIC MCU Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A). PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

#### 19.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the I<sup>2</sup>C<sup>™</sup> bus and separate headers for connection to an LCD module and a keypad.

NOTES:

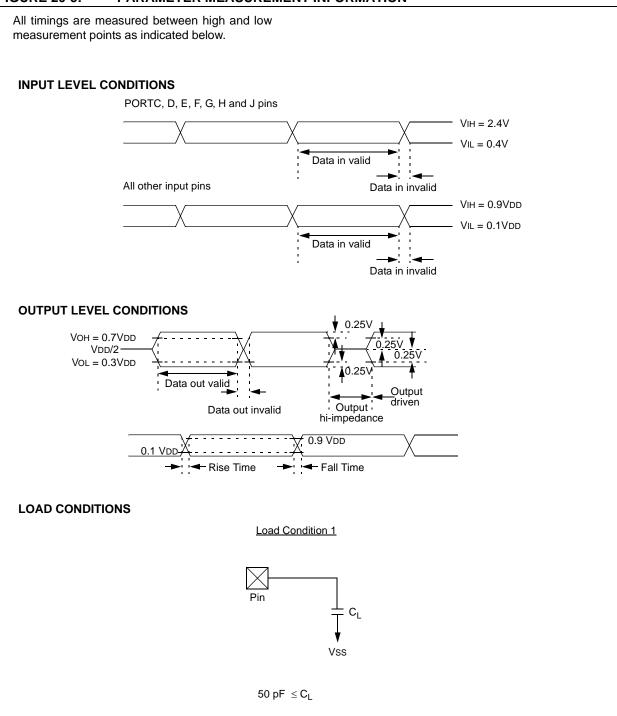

#### FIGURE 20-5: PARAMETER MEASUREMENT INFORMATION

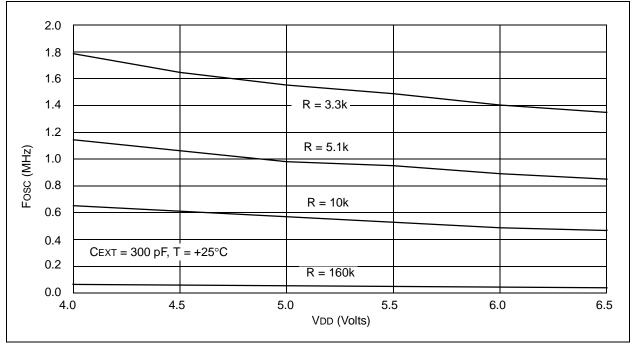

### TABLE 21-2: RC OSCILLATOR FREQUENCIES

| Сехт   | Rext |          | rage<br>5V, +25°C |

|--------|------|----------|-------------------|

| 22 pF  | 10k  | 3.33 MHz | ± 12%             |

|        | 100k | 353 kHz  | ± 13%             |

| 100 pF | 3.3k | 3.54 MHz | ± 10%             |

|        | 5.1k | 2.43 MHz | ± 14%             |

|        | 10k  | 1.30 MHz | ± 17%             |

|        | 100k | 129 kHz  | ± 10%             |

| 300 pF | 3.3k | 1.54 MHz | ± 14%             |

|        | 5.1k | 980 kHz  | ± 12%             |

|        | 10k  | 564 kHz  | ± 16%             |

|        | 160k | 35 kHz   | ± 18%             |

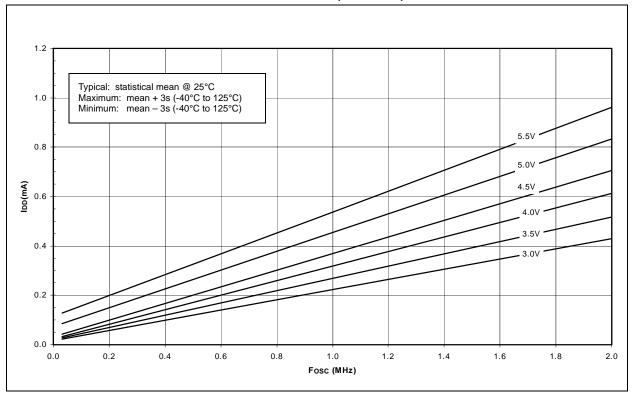

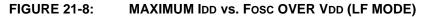

FIGURE 21-7: TYPICAL IDD vs. Fosc OVER VDD (LF MODE)

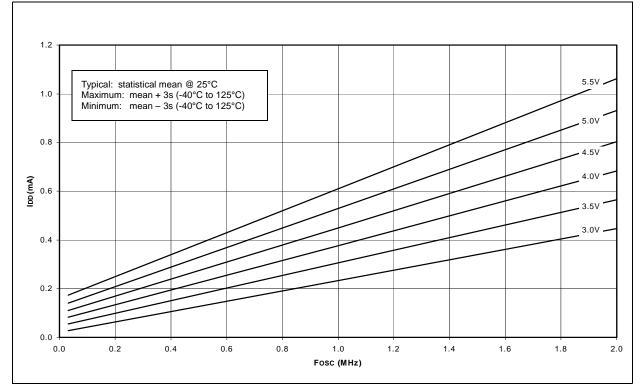

FIGURE 21-11: TYPICAL AND MAXIMUM IPD vs. VDD (SLEEP MODE, ALL PERIPHERALS DISABLED, -40°C to +125°C)

FIGURE 21-12: TYPICAL AND MAXIMUM IPD vs. VDD (SLEEP MODE, BOR ENABLED, -40°C to +125°C)

#### INDEX

| Α                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A/D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Accuracy/Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADCON0 Register179                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ADCON1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ADIF bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Analog Input Model Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Analog-to-Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Configuring Analog Port Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Configuring the Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Configuring the Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Connection Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Conversion Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Converter Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Delays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Effects of a RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Equations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Flow Chart of A/D Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GO/DONE bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Internal Sampling Switch (Rss) Impedence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Operation During SLEEP 188                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Sampling Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Sampling Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Source Impedence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Time Delays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Transfer Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A/D Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A/D Interrupt Flag bit, ADIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A/D Module Interrupt Enable, ADIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |