Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 33MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 66                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 678 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                |

| Data Converters            | A/D 16x10b                                                                 |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 84-LCC (J-Lead)                                                            |

| Supplier Device Package    | 84-PLCC (29.31x29.31)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c762t-33e-l |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 OVERVIEW

This data sheet covers the PIC17C7XX group of the PIC17CXXX family of microcontrollers. The following devices are discussed in this data sheet:

- PIC17C752

- PIC17C756A

- PIC17C762

- PIC17C766

The PIC17C7XX devices are 68/84-pin, EPROM based members of the versatile PIC17CXXX family of low cost, high performance, CMOS, fully static, 8-bit microcontrollers.

All PIC<sup>®</sup> microcontrollers employ an advanced RISC architecture. The PIC17CXXX has enhanced core features, 16-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 16-bit wide instruction word with a separate 8-bit wide data path. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 58 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance. For mathematical intensive applications, all devices have a single cycle 8 x 8 Hardware Multiplier.

PIC17CXXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

PIC17C7XX devices have up to 902 bytes of RAM and 66 I/O pins. In addition, the PIC17C7XX adds several peripheral features, useful in many high performance applications, including:

- Four timer/counters

- Four capture inputs

- Three PWM outputs

- Two independent Universal Synchronous Asynchronous Receiver Transmitters (USARTs)

- An A/D converter (multi-channel, 10-bit resolution)

- A Synchronous Serial Port (SPI and I<sup>2</sup>C w/ Master mode)

These special features reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption.

There are four oscillator options, of which the single pin RC oscillator provides a low cost solution, the LF oscillator is for low frequency crystals and minimizes power consumption, XT is a standard crystal and the EC is for external clock input.

The SLEEP (power-down) mode offers additional power saving. Wake-up from SLEEP can occur through several external and internal interrupts and device RESETS.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software malfunction.

There are four configuration options for the device operational mode:

- Microprocessor

- Microcontroller

- Extended microcontroller

- Protected microcontroller

The microprocessor and extended microcontroller modes allow up to 64K-words of external program memory.

The device also has Brown-out Reset circuitry. This allows a device RESET to occur if the device VDD falls below the Brown-out voltage trip point (BVDD). The chip will remain in Brown-out Reset until VDD rises above BVDD.

A UV erasable, CERQUAD packaged version (compatible with PLCC), is ideal for code development, while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC17C7XX fits perfectly in applications that require extremely fast execution of complex software programs. These include applications ranging from precise motor control and industrial process control to automotive, instrumentation, and telecom applications.

The EPROM technology makes customization of application programs (with unique security codes, combinations, model numbers, parameter storage, etc.) fast and convenient. Small footprint package options (including die sales) make the PIC17C7XX ideal for applications with space limitations that require high performance.

High speed execution, powerful peripheral features, flexible I/O, and low power consumption all at low cost make the PIC17C7XX ideal for a wide range of embedded control applications.

## 1.1 Family and Upward Compatibility

The PIC17CXXX family of microcontrollers have architectural enhancements over the PIC16C5X and PIC16CXX families. These enhancements allow the device to be more efficient in software and hardware requirements. Refer to Appendix A for a detailed list of enhancements and modifications. Code written for PIC16C5X or PIC16CXX can be easily ported to PIC17CXXX devices (Appendix B).

## 1.2 Development Support

The PIC17CXXX family is supported by a full featured macro assembler, a software simulator, an in-circuit emulator, a universal programmer, a "C" compiler and fuzzy logic support tools. For additional information, see Section 19.0.

© 1998-2013 Microchip Technology Inc.

NOTES:

| TABLE 3-1: | PINC       | DUT DE      | SCRIP       | TIONS       | (CON       | TINUE         | D)             |                                                                                                                                                                               |

|------------|------------|-------------|-------------|-------------|------------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | F          | PIC17C7     | 5X          | PIC17C76X   |            |               |                |                                                                                                                                                                               |

| Name       | DIP<br>No. | PLCC<br>No. | TQFP<br>No. | PLCC<br>No. | QFP<br>No. | I/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                   |

|            |            |             |             |             |            |               |                | PORTC is a bi-directional I/O Port.                                                                                                                                           |

| RC0/AD0    | 2          | 3           | 58          | 3           | 72         | I/O           | TTL            | This is also the least significant byte (LSB) of                                                                                                                              |

| RC1/AD1    | 63         | 67          | 55          | 83          | 69         | I/O           | TTL            | the 16-bit wide system bus in Microprocessor                                                                                                                                  |

| RC2/AD2    | 62         | 66          | 54          | 82          | 68         | I/O           | TTL            | mode or Extended Microcontroller mode. In                                                                                                                                     |

| RC3/AD3    | 61         | 65          | 53          | 81          | 67         | I/O           | TTL            | multiplexed system bus configuration, these<br>pins are address output as well as data input of                                                                               |

| RC4/AD4    | 60         | 64          | 52          | 80          | 66         | I/O           | TTL            | output.                                                                                                                                                                       |

| RC5/AD5    | 58         | 63          | 51          | 79          | 65         | I/O           | TTL            |                                                                                                                                                                               |

| RC6/AD6    | 58         | 62          | 50          | 78          | 64         | I/O           | TTL            |                                                                                                                                                                               |

| RC7/AD7    | 57         | 61          | 49          | 77          | 63         | I/O           | TTL            |                                                                                                                                                                               |

|            |            |             |             |             |            |               |                | PORTD is a bi-directional I/O Port.                                                                                                                                           |

| RD0/AD8    | 10         | 11          | 2           | 15          | 4          | I/O           | TTL            | This is also the most significant byte (MSB) of                                                                                                                               |

| RD1/AD9    | 9          | 10          | 1           | 14          | 3          | I/O           | TTL            | the 16-bit system bus in Microprocessor mode                                                                                                                                  |

| RD2/AD10   | 8          | 9           | 64          | 9           | 78         | I/O           | TTL            | or Extended Microcontroller mode. In multi-                                                                                                                                   |

| RD3/AD11   | 7          | 8           | 63          | 8           | 77         | I/O           | TTL            | plexed system bus configuration, these pins an<br>address output as well as data input or output.                                                                             |

| RD4/AD12   | 6          | 7           | 62          | 7           | 76         | I/O           | TTL            |                                                                                                                                                                               |

| RD5/AD13   | 5          | 6           | 61          | 6           | 75         | I/O           | TTL            |                                                                                                                                                                               |

| RD6/AD14   | 4          | 5           | 60          | 5           | 74         | I/O           | TTL            |                                                                                                                                                                               |

| RD7/AD15   | 3          | 4           | 59          | 4           | 73         | I/O           | TTL            |                                                                                                                                                                               |

|            |            |             |             |             |            |               |                | PORTE is a bi-directional I/O Port.                                                                                                                                           |

| RE0/ALE    | 11         | 12          | 3           | 16          | 5          | I/O           | TTL            | In Microprocessor mode or Extended Microcor<br>troller mode, RE0 is the Address Latch Enable<br>(ALE) output. Address should be latched on the<br>falling edge of ALE output. |

| RE1/OE     | 12         | 13          | 4           | 17          | 6          | I/O           | TTL            | In Microprocessor or Extended Microcontroller mode, RE1 is the Output Enable (OE) control output (active low).                                                                |

| RE2/WR     | 13         | 14          | 5           | 18          | 7          | I/O           | TTL            | In Microprocessor or Extended Microcontroller mode, RE2 is the Write Enable (WR) control output (active low).                                                                 |

| RE3/CAP4   | 14         | 15          | 6           | 19          | 8          | I/O           | ST             | RE3 can also be the Capture4 input pin.                                                                                                                                       |

|            |            |             |             |             |            |               |                | PORTF is a bi-directional I/O Port.                                                                                                                                           |

| RF0/AN4    | 26         | 28          | 18          | 36          | 24         | I/O           | ST             | RF0 can also be analog input 4.                                                                                                                                               |

| RF1/AN5    | 25         | 27          | 17          | 35          | 23         | I/O           | ST             | RF1 can also be analog input 5.                                                                                                                                               |

| RF2/AN6    | 24         | 26          | 16          | 30          | 18         | I/O           | ST             | RF2 can also be analog input 6.                                                                                                                                               |

| RF3/AN7    | 23         | 25          | 15          | 29          | 17         | I/O           | ST             | RF3 can also be analog input 7.                                                                                                                                               |

| RF4/AN8    | 22         | 24          | 14          | 28          | 16         | I/O           | ST             | RF4 can also be analog input 8.                                                                                                                                               |

| RF5/AN9    | 21         | 23          | 13          | 27          | 15         | I/O           | ST             | RF5 can also be analog input 9.                                                                                                                                               |

| RF6/AN10   | 20         | 22          | 12          | 26          | 14         | I/O           | ST             | RF6 can also be analog input 10.                                                                                                                                              |

| RF7/AN11   | 19         | 21          | 11          | 25          | 13         | I/O           | ST             | RF7 can also be analog input 11.                                                                                                                                              |

TABLE 3-1: PINOUT DESCRIPTIONS (CONTINUED)

Legend: I = Input only; O = Output only; I/O = Inp P = Power; — = Not Used; TTL = T

I/O = Input/Output; TTL = TTL input;

ST = Schmitt Trigger input

Note 1: The output is only available by the peripheral operation.2: Open drain input/output pin. Pin forced to input upon any device RESET.

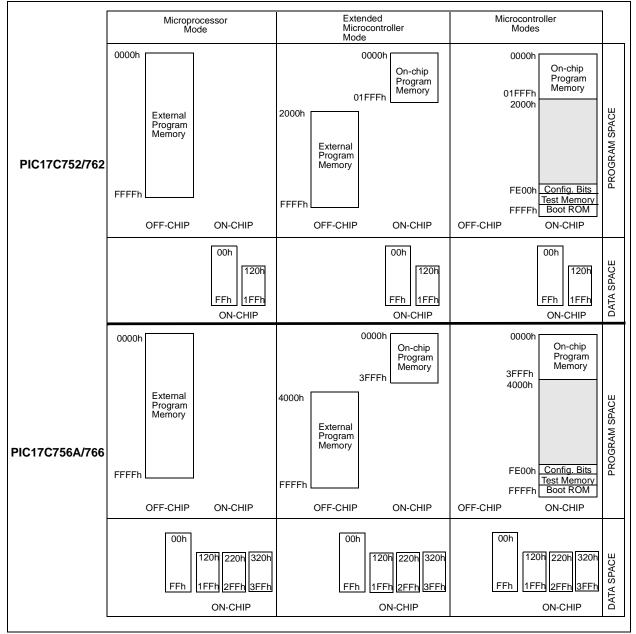

## TABLE 7-1: MODE MEMORY ACCESS

| Operating<br>Mode            | Internal<br>Program<br>Memory | Configuration Bits,<br>Test Memory,<br>Boot ROM |  |  |

|------------------------------|-------------------------------|-------------------------------------------------|--|--|

| Microprocessor               | No Access                     | No Access                                       |  |  |

| Microcontroller              | Access                        | Access                                          |  |  |

| Extended<br>Microcontroller  | Access                        | No Access                                       |  |  |

| Protected<br>Microcontroller | Access                        | Access                                          |  |  |

The PIC17C7XX can operate in modes where the program memory is off-chip. They are the Microprocessor and Extended Microcontroller modes. The Microprocessor mode is the default for an unprogrammed device.

Regardless of the processor mode, data memory is always on-chip.

## FIGURE 7-2: MEMORY MAP IN DIFFERENT MODES

## 7.3 Stack Operation

PIC17C7XX devices have a 16 x 16-bit hardware stack (Figure 7-1). The stack is not part of either the program or data memory space, and the stack pointer is neither readable nor writable. The PC (Program Counter) is "PUSH'd" onto the stack when a CALL or LCALL instruction is executed, or an interrupt is acknowledged. The stack is "POP'd" in the event of a RETURN, RETLW, or a RETFIE instruction execution. PCLATH is not affected by a "PUSH" or a "POP" operation.

The stack operates as a circular buffer, with the stack pointer initialized to '0' after all RESETS. There is a stack available bit (STKAV) to allow software to ensure that the stack will not overflow. The STKAV bit is set after a device RESET. When the stack pointer equals Fh, STKAV is cleared. When the stack pointer rolls over from Fh to 0h, the STKAV bit will be held clear until a device RESET.

- **Note 1:** There is not a status bit for stack underflow. The STKAV bit can be used to detect the underflow which results in the stack pointer being at the Top-of-Stack.

- 2: There are no instruction mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt vector.

- 3: After a RESET, if a "POP" operation occurs before a "PUSH" operation, the STKAV bit will be cleared. This will appear as if the stack is full (underflow has occurred). If a "PUSH" operation occurs next (before another "POP"), the STKAV bit will be locked clear. Only a device RESET will cause this bit to set.

After the device is "PUSH'd" sixteen times (without a "POP"), the seventeenth push overwrites the value from the first push. The eighteenth push overwrites the second push (and so on).

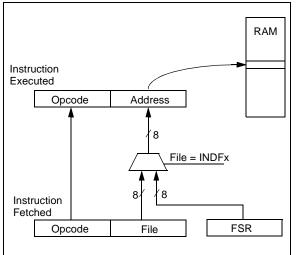

## 7.4 Indirect Addressing

Indirect addressing is a mode of addressing data memory where the data memory address in the instruction is not fixed. That is, the register that is to be read or written can be modified by the program. This can be useful for data tables in the data memory. Figure 7-6 shows the operation of indirect addressing. This depicts the moving of the value to the data memory address specified by the value of the FSR register.

Example 7-1 shows the use of indirect addressing to clear RAM in a minimum number of instructions. A similar concept could be used to move a defined number of bytes (block) of data to the USART transmit register (TXREG). The starting address of the block of data to be transmitted could easily be modified by the program.

#### FIGURE 7-6: INDIRECT ADDRESSING

## 7.4.1 INDIRECT ADDRESSING REGISTERS

The PIC17C7XX has four registers for indirect addressing. These registers are:

- INDF0 and FSR0

- INDF1 and FSR1

Registers INDF0 and INDF1 are not physically implemented. Reading or writing to these registers activates indirect addressing, with the value in the corresponding FSR register being the address of the data. The FSR is an 8-bit register and allows addressing anywhere in the 256-byte data memory address range. For banked memory, the bank of memory accessed is specified by the value in the BSR.

If file INDF0 (or INDF1) itself is read indirectly via an FSR, all '0's are read (Zero bit is set). Similarly, if INDF0 (or INDF1) is written to indirectly, the operation will be equivalent to a NOP, and the status bits are not affected.

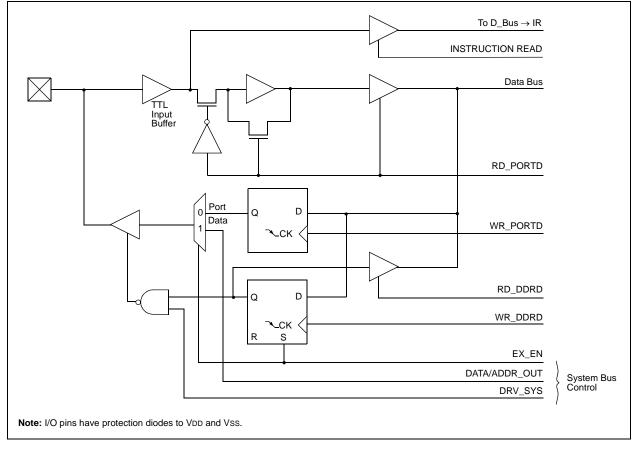

## 10.4 PORTD and DDRD Registers

PORTD is an 8-bit bi-directional port. The corresponding data direction register is DDRD. A '1' in DDRD configures the corresponding port pin as an input. A '0' in the DDRD register configures the corresponding port pin as an output. Reading PORTD reads the status of the pins, whereas writing to PORTD will write to the port latch. PORTD is multiplexed with the system bus. When operating as the system bus, PORTD is the high order byte of the address/data bus (AD15:AD8). The timing for the system bus is shown in the Electrical Specifications section.

**Note:** This port is configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, this port is a general purpose I/O. Example 10-4 shows an instruction sequence to initialize PORTD. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized. The following example uses the MOVLB instruction to load the BSR register for bank selection.

#### EXAMPLE 10-4: INITIALIZING PORTD

| MOVLB | 1      |   | ; | Select Bank 1            |

|-------|--------|---|---|--------------------------|

| CLRF  | PORTD, | F | ; | Initialize PORTD data    |

|       |        |   | ; | latches before setting   |

|       |        |   | ; | the data direction reg   |

| MOVLW | 0xCF   |   | ; | Value used to initialize |

|       |        |   | ; | data direction           |

| MOVWF | DDRD   |   | ; | Set RD<3:0> as inputs    |

|       |        |   | ; | RD<5:4> as outputs       |

|       |        |   | ; | RD<7:6> as inputs        |

|       |        |   |   |                          |

#### FIGURE 10-10: BLOCK DIAGRAM OF RD7:RD0 PORT PINS (IN I/O PORT MODE)

## TABLE 10-11: PORTF FUNCTIONS

| Name     | Bit  | Buffer Type | Function                         |

|----------|------|-------------|----------------------------------|

| RF0/AN4  | bit0 | ST          | Input/output or analog input 4.  |

| RF1/AN5  | bit1 | ST          | Input/output or analog input 5.  |

| RF2/AN6  | bit2 | ST          | Input/output or analog input 6.  |

| RF3/AN7  | bit3 | ST          | Input/output or analog input 7.  |

| RF4/AN8  | bit4 | ST          | Input/output or analog input 8.  |

| RF5/AN9  | bit5 | ST          | Input/output or analog input 9.  |

| RF6/AN10 | bit6 | ST          | Input/output or analog input 10. |

| RF7/AN11 | bit7 | ST          | Input/output or analog input 11. |

Legend: ST = Schmitt Trigger input

## TABLE 10-12: REGISTERS/BITS ASSOCIATED WITH PORTF

| Address     | Name   | Bit 7        | Bit 6        | Bit 5        | Bit 4       | Bit 3       | Bit 2       | Bit 1       | Bit 0       | Value on<br>POR,<br>BOR | MCLR,<br>WDT |

|-------------|--------|--------------|--------------|--------------|-------------|-------------|-------------|-------------|-------------|-------------------------|--------------|

| 10h, Bank 5 | DDRF   | Data Dire    | ection Reg   | gister for P | ORTF        |             |             |             |             | 1111 1111               | 1111 1111    |

| 11h, Bank 5 | PORTF  | RF7/<br>AN11 | RF6/<br>AN10 | RF5/<br>AN9  | RF4/<br>AN8 | RF3/<br>AN7 | RF2/<br>AN6 | RF1/<br>AN5 | RF0/<br>AN4 | 0000 0000               | 0000 0000    |

| 15h, Bank 5 | ADCON1 | ADCS1        | ADCS0        | ADFM         | —           | PCFG3       | PCFG2       | PCFG1       | PCFG0       | 000- 0000               | 000- 0000    |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTF.

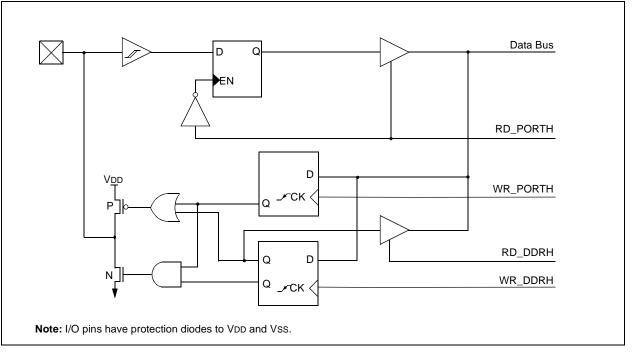

## FIGURE 10-18: RH3:RH0 BLOCK DIAGRAM

## TABLE 10-15: PORTH FUNCTIONS

| Name     | Bit  | Buffer Type | Function                         |

|----------|------|-------------|----------------------------------|

| RH0      | bit0 | ST          | Input/output.                    |

| RH1      | bit1 | ST          | Input/output.                    |

| RH2      | bit2 | ST          | Input/output.                    |

| RH3      | bit3 | ST          | Input/output.                    |

| RH4/AN12 | bit4 | ST          | Input/output or analog input 12. |

| RH5/AN13 | bit5 | ST          | Input/output or analog input 13. |

| RH6/AN14 | bit6 | ST          | Input/output or analog input 14. |

| RH7/AN15 | bit7 | ST          | Input/output or analog input 15. |

Legend: ST = Schmitt Trigger input

## TABLE 10-16: REGISTERS/BITS ASSOCIATED WITH PORTH

| Address     | Name   | Bit 7        | Bit 6        | Bit 5        | Bit 4        | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | MCLR, WDT |

|-------------|--------|--------------|--------------|--------------|--------------|-------|-------|-------|-------|-------------------------|-----------|

| 10h, Bank 8 | DDRH   | Data Dire    | ction Regis  | ter for PORT | Ή            |       |       |       |       | 1111 1111               | 1111 1111 |

| 11h, Bank 8 | PORTH  | RH7/<br>AN15 | RH6/<br>AN14 | RH5/<br>AN13 | RH4/<br>AN12 | RH3   | RH2   | RH1   | RH0   | 0000 xxxx               | 0000 uuuu |

| 15h, Bank 5 | ADCON1 | ADCS1        | ADCS0        | ADFM         | _            | PCFG3 | PCFG2 | PCFG1 | PCFG0 | 000- 0000               | 000- 0000 |

Legend: x = unknown, u = unchanged

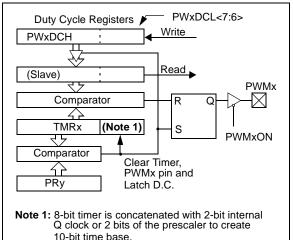

## 13.1.3 USING PULSE WIDTH MODULATION (PWM) OUTPUTS WITH TIMER1 AND TIMER2

Three high speed pulse width modulation (PWM) outputs are provided. The PWM1 output uses Timer1 as its time base, while PWM2 and PWM3 may independently be software configured to use either Timer1 or Timer2 as the time base. The PWM outputs are on the RB2/PWM1, RB3/PWM2 and RG5/PWM3 pins.

Each PWM output has a maximum resolution of 10bits. At 10-bit resolution, the PWM output frequency is 32.2 kHz (@ 32 MHz clock) and at 8-bit resolution the PWM output frequency is 128.9 kHz. The duty cycle of the output can vary from 0% to 100%.

Figure 13-3 shows a simplified block diagram of a PWM module.

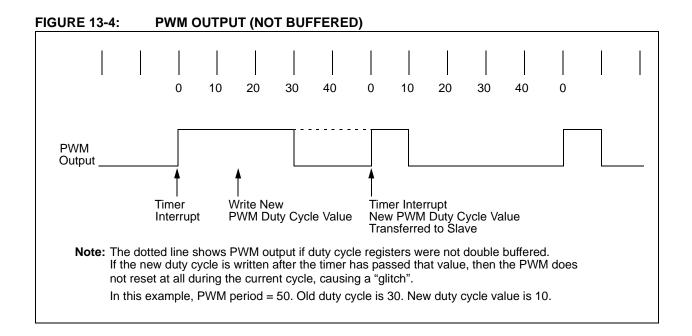

The duty cycle registers are double buffered for glitch free operation. Figure 13-4 shows how a glitch could occur if the duty cycle registers were not double buffered.

The user needs to set the PWM1ON bit (TCON2<4>) to enable the PWM1 output. When the PWM1ON bit is set, the RB2/PWM1 pin is configured as PWM1 output and forced as an output, irrespective of the data direction bit (DDRB<2>). When the PWM1ON bit is clear, the pin behaves as a port pin and its direction is controlled by its data direction bit (DDRB<2>). Similarly, the PWM2ON (TCON2<5>) bit controls the configuration of the RB3/PWM2 pin and the PWM3ON (TCON3<0>) bit controls the configuration of the RG5/PWM3 pin.

#### FIGURE 13-3: SIMPLIFIED PWM BLOCK DIAGRAM

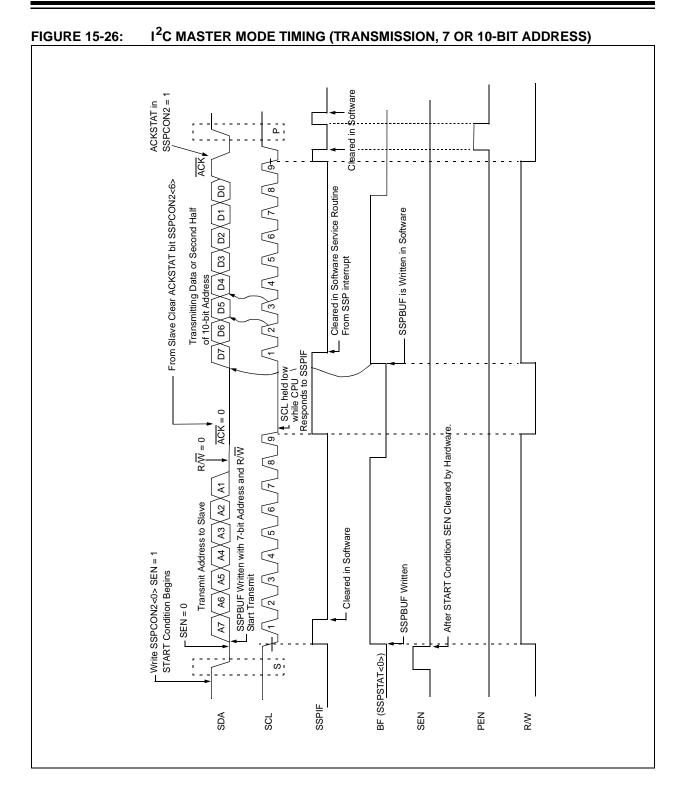

### 15.2.1.1 Addressing

Once the MSSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register on the falling edge of the 8th SCL pulse.

- b) The buffer full bit, BF, is set on the falling edge of the 8th SCL pulse.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR2<7>), is set (interrupt is generated if enabled) - on the falling edge of the 9th SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for a 10-bit address is as follows, with steps 7- 9 for slave-transmitter:

- 1. Receive first (high) byte of Address (bits SSPIF, BF and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of Address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of Address. This will clear bit UA and release the SCL line.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

**Note:** Following the Repeated Start condition (step 7) in 10-bit mode, the user only needs to match the first 7-bit address. The user does not update the SSPADD for the second half of the address.

## 15.2.1.2 Slave Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON1<6>) is set.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR2<7>) must be cleared in software. The SSPSTAT register is used to determine the status of the received byte.

Note: The SSPBUF will be loaded if the SSPOV bit is set and the BF flag is cleared. If a read of the SSPBUF was performed, but the user did not clear the state of the SSPOV bit before the next receive occurred, the ACK is not sent and the SSP-BUF is updated.

|    | ts as Data<br>s Received | SSPSR $ ightarrow$ SSPBUF | Generate ACK<br>Pulse | Set bit SSPIF<br>(SSP Interrupt occurs |

|----|--------------------------|---------------------------|-----------------------|----------------------------------------|

| BF | SSPOV                    |                           | Fuise                 | if enabled)                            |

| 0  | 0                        | Yes                       | Yes                   | Yes                                    |

| 1  | 0                        | No                        | No                    | Yes                                    |

| 1  | 1                        | No                        | No                    | Yes                                    |

| 0  | 1                        | Yes                       | No                    | Yes                                    |

## TABLE 15-2: DATA TRANSFER RECEIVED BYTE ACTIONS

Note 1: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

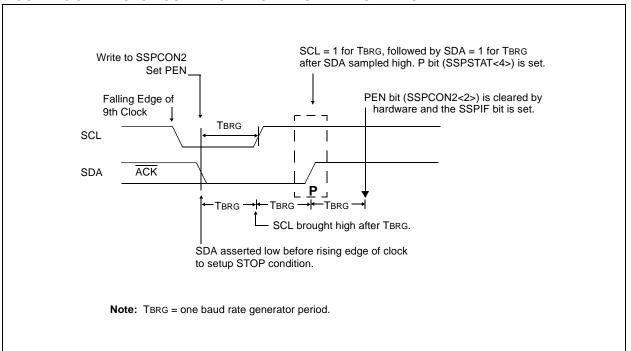

## 15.2.14 STOP CONDITION TIMING

A STOP bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit PEN (SSPCON2<2>). At the end of a receive/ transmit the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the baud rate generator is reloaded and counts down to '0'. When the baud rate generator times out, the SCL pin will be brought high and one TBRG (baud rate generator rollover count) later, the SDA pin will be de-asserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 15-31).

Whenever the firmware decides to take control of the bus, it will first determine if the bus is busy by checking the S and P bits in the SSPSTAT register. If the bus is busy, then the CPU can be interrupted (notified) when a STOP bit is detected (i.e., bus is free).

## 15.2.14.1 WCOL Status Flag

If the user writes the SSPBUF when a STOP sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 15-31: STOP CONDITION RECEIVE OR TRANSMIT MODE

#### EXAMPLE 15-2: INTERFACING TO A 24LC01B SERIAL EEPROM (USING MPLAB C17)

```

// Writes the byte data to 24LC01B at the specified address

void ByteWrite(static unsigned char address, static unsigned char data)

{

StartI2C();

// Send start bit

// Wait for idle condition

IdleI2C();

WriteI2C(CONTROL);

// Send control byte

IdleI2C();

// Wait for idle condition

if (!SSPCON2bits.ACKSTAT)

// If 24LC01B ACKs

{

WriteI2C(address);

// Send control byte

IdleI2C();

// Wait for idle condition

// If 24LC01B ACKs

if (!SSPCON2bits.ACKSTAT)

WriteI2C(data);

// Send data

}

IdleI2C();

// Wait for idle condition

StopI2C();

// Send stop bit

// Wait for idle condition

IdleI2C();

return;

// Reads a byte of data from 24LC01B at the specified address

unsigned char ByteRead(static unsigned char address)

// Send start bit

StartI2C();

IdleI2C();

// Wait for idle condition

WriteI2C(CONTROL);

// Send control byte

IdleI2C();

// Wait for idle condition

if (!SSPCON2bits.ACKSTAT)

// If the 24LC01B ACKs

{

// Send address

WriteI2C(address);

// Wait for idle condition

IdleI2C();

if (!SSPCON2bits.ACKSTAT) // If the 24LC01B ACKs

{

RestartI2C();

// Send restart

IdleI2C();

// Wait for idle condition

// Send control byte with R/W set

WriteI2C(CONTROL+1);

IdleI2C();

// Wait for idle condition

// If the 24LC01B ACKs

if (!SSPCON2bits.ACKSTAT)

{

// Read a byte of data from 24LC01B

getcI2C();

// Wait for idle condition

IdleI2C();

NotAckI2C();

// Send a NACK to 24LC01B

IdleI2C();

// Wait for idle condition

// Send stop bit

StopI2C();

IdleI2C();

// Wait for idle condition

}

}

}

return(SSPBUF);

```

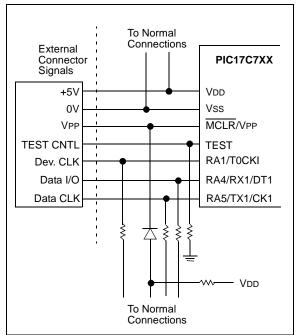

## 17.6 In-Circuit Serial Programming

The PIC17C7XX group of the high-end family (PIC17CXXX) has an added feature that allows serial programming while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware to be programmed.

Devices may be serialized to make the product unique; "special" variants of the product may be offered and code updates are possible. This allows for increased design flexibility.

To place the device into the Serial Programming Test mode, two pins will need to be placed at VIHH. These are the TEST pin and the MCLR/VPP pin. Also, a sequence of events must occur as follows:

- 1. The TEST pin is placed at VIHH.

- 2. The MCLR/VPP pin is placed at VIHH.

There is a setup time between step 1 and step 2 that must be met.

After this sequence, the Program Counter is pointing to program memory address 0xFF60. This location is in the Boot ROM. The code initializes the USART/SCI so that it can receive commands. For this, the device must be clocked. The device clock source in this mode is the RA1/T0CKI pin. After delaying to allow the USART/SCI to initialize, commands can be received. The flow is shown in these 3 steps:

- 1. The device clock source starts.

- 2. Wait 80 device clocks for Boot ROM code to configure the USART/SCI.

- 3. Commands may now be sent.

|             |          | During Programming |                                                   |  |  |  |  |  |

|-------------|----------|--------------------|---------------------------------------------------|--|--|--|--|--|

| Name        | Function | Туре               | Description                                       |  |  |  |  |  |

| RA4/RX1/DT1 | DT       | I/O                | Serial Data                                       |  |  |  |  |  |

| RA5/TX1/CK1 | СК       | I                  | Serial Clock                                      |  |  |  |  |  |

| RA1/T0CKI   | OSCI     | I                  | Device Clock Source                               |  |  |  |  |  |

| TEST        | TEST     | I                  | Test mode selection control input, force to VIHH  |  |  |  |  |  |

| MCLR/VPP    | MCLR/VPP | Р                  | Master Clear Reset and Device Programming Voltage |  |  |  |  |  |

| Vdd         | Vdd      | Р                  | Positive supply for logic and I/O pins            |  |  |  |  |  |

| Vss         | Vss      | Р                  | Ground reference for logic and I/O pins           |  |  |  |  |  |

#### TABLE 17-3: ICSP INTERFACE PINS

For complete details of serial programming, please refer to the PIC17C7XX Programming Specification. (Contact your local Microchip Technology Sales Office for availability.)

FIGURE 17-3:

#### TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| XORLW                     | th                                   |                 |                   |                  |  |  |  |  |  |

|---------------------------|--------------------------------------|-----------------|-------------------|------------------|--|--|--|--|--|

| Syntax:                   | [ label ] ]                          | [label] XORLW k |                   |                  |  |  |  |  |  |

| Operands:                 | $0 \le k \le 2$                      | 55              |                   |                  |  |  |  |  |  |

| Operation:                | (WREG)                               | .XOR. k         | $\rightarrow$ (WR | EG)              |  |  |  |  |  |

| Status Affected:          | Z                                    |                 |                   |                  |  |  |  |  |  |

| Encoding:                 | 1011                                 | 0100            | kkkk              | kkkk             |  |  |  |  |  |

| Description:              | The conte<br>with the 8<br>placed in | -bit literal    |                   |                  |  |  |  |  |  |

| Words:                    | 1                                    |                 |                   |                  |  |  |  |  |  |

| Cycles:                   | 1                                    | 1               |                   |                  |  |  |  |  |  |

| Q Cycle Activity:         |                                      |                 |                   |                  |  |  |  |  |  |

| Q1                        | Q2                                   | Q3              |                   | Q4               |  |  |  |  |  |

| Decode                    | Read<br>literal 'k'                  | Proce:<br>Data  |                   | Write to<br>WREG |  |  |  |  |  |

| Example:<br>Before Instru |                                      | 0xAF            |                   |                  |  |  |  |  |  |

| WREG                      | = 0xB5                               |                 |                   |                  |  |  |  |  |  |

| After Instruc<br>WREG     |                                      |                 |                   |                  |  |  |  |  |  |

| XOR         | WF                           | Exclusive                                                 | e OR WI                      | REG wit                  | h f                      |

|-------------|------------------------------|-----------------------------------------------------------|------------------------------|--------------------------|--------------------------|

| Synt        | ax:                          | [label]                                                   | XORWF                        | f,d                      |                          |

| Ope         | rands:                       | $0 \le f \le 255$<br>$d \in [0,1]$                        | 5                            |                          |                          |

| Ope         | ration:                      | (WREG) .                                                  | XOR. (f                      | $\rightarrow$ (des       | st)                      |

| Statu       | us Affected:                 | Z                                                         |                              |                          |                          |

| Enco        | oding:                       | 0000                                                      | 110d                         | ffff                     | ffff                     |

| Deso        | cription:                    | Exclusive C<br>with registe<br>stored in W<br>stored bacl | er 'f'. If 'd'<br>/REG. If ' | is 0, the<br>d' is 1, th | result is<br>e result is |

| Wor         | ds:                          | 1                                                         |                              |                          |                          |

| Cycl        | es:                          | 1                                                         |                              |                          |                          |

| QC          | cle Activity:                |                                                           |                              |                          |                          |

|             | Q1                           | Q2                                                        | Q3                           | }                        | Q4                       |

|             | Decode                       | Read<br>register 'f'                                      | Proce<br>Dat                 |                          | Write to<br>estination   |

| <u>Exar</u> | nple:                        | XORWF                                                     | REG, 1                       |                          |                          |

|             | Before Instru<br>REG<br>WREG | iction<br>= 0xAF<br>= 0xB5                                | 1010<br>1011                 |                          |                          |

| WINEO         | -    | 0,00 | 1011 0101 |

|---------------|------|------|-----------|

| After Instruc | tion |      |           |

| REG           | =    | 0x1A | 0001 1010 |

| WREG          | =    | 0xB5 |           |

NOTES:

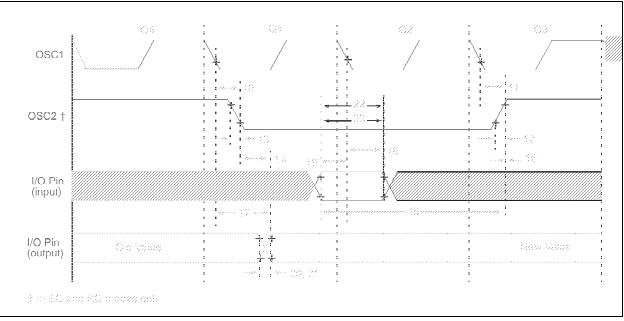

| TABLE 20-2: | CLKOUT AND I/O TIMING REQUIREMENTS |

|-------------|------------------------------------|

|-------------|------------------------------------|

| Param<br>No. | Sym      | Characteristic                                                  | Min          | Тур† | Max         | Units | Conditions |

|--------------|----------|-----------------------------------------------------------------|--------------|------|-------------|-------|------------|

| 10           | TosL2ckL | OSC1↓ to CLKOUT↓                                                | —            | 15   | 30          | ns    | (Note 1)   |

| 11           | TosL2ckH | OSC1↓ to CLKOUT↑                                                | —            | 15   | 30          | ns    | (Note 1)   |

| 12           | TckR     | CLKOUT rise time                                                | —            | 5    | 15          | ns    | (Note 1)   |

| 13           | TckF     | CLKOUT fall time                                                | —            | 5    | 15          | ns    | (Note 1)   |

| 14           | TckH2ioV | CLKOUT ↑ to Port out valid                                      | —            | —    | 0.5Tcy + 20 | ns    | (Note 1)   |

| 15           | TioV2ckH | Port in valid before CLKOUT <sup>↑</sup>                        | 0.25Tcy + 25 | —    | _           | ns    | (Note 1)   |

| 16           | TckH2iol | Port in hold after CLKOUT <sup>↑</sup>                          | 0            | —    | _           | ns    | (Note 1)   |

| 17           | TosL2ioV | OSC1↓ (Q1 cycle) to Port out valid                              | —            | —    | 100         | ns    |            |

| 18           | TosL2iol | OSC1↓ (Q2 cycle) to Port input<br>invalid<br>(I/O in hold time) | 0            | —    | _           | ns    |            |

| 19           | TioV2osL | Port input valid to OSC1↓<br>(I/O in setup time)                | 30           | —    | _           | ns    |            |

| 20           | TioR     | Port output rise time                                           | —            | 10   | 35          | ns    |            |

| 21           | TioF     | Port output fall time                                           | —            | 10   | 35          | ns    |            |

| 22           | TinHL    | INT pin high or low time                                        | 25           |      | —           | ns    |            |

| 23           | TrbHL    | RB7:RB0 change INT high or low time                             | 25           | —    | _           | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note** 1: Measurements are taken in EC mode, where CLKOUT output is 4 x Tosc.

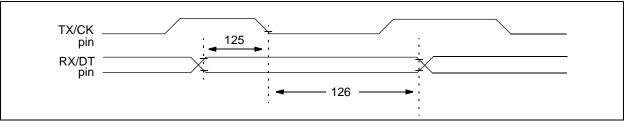

## FIGURE 20-20: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 20-15: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                                                                | Min | Тур† | Max | Unit<br>s | Conditions |

|--------------|----------|-------------------------------------------------------------------------------|-----|------|-----|-----------|------------|

| 125          | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data setup before $CK\downarrow$ (DT setup time) | 15  | _    | _   | ns        |            |

| 126          | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                | 15  | _    |     | ns        |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated.

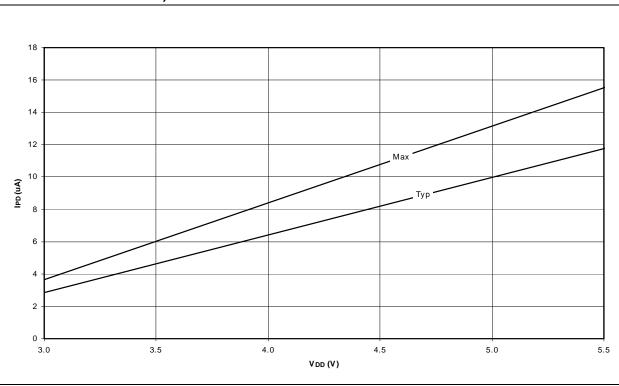

## FIGURE 21-13: TYPICAL AND MAXIMUM △IPD vs. VDD (SLEEP MODE, WDT ENABLED, -40°C to +125°C)

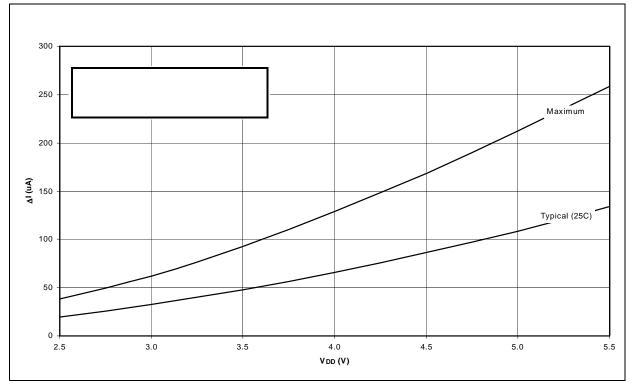

FIGURE 21-14: TYPICAL AND MAXIMUM △IRBPU vs. VDD (MEASURED PER INPUT PIN, -40°C TO +125°C)