Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

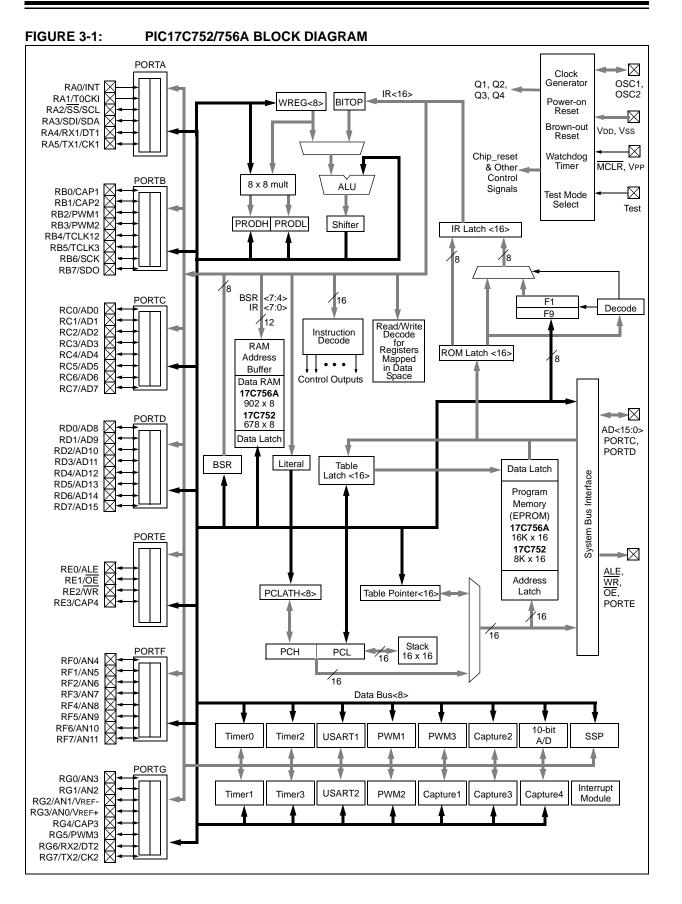

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 33MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 66                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 902 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                |

| Data Converters            | A/D 16x10b                                                                 |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c766-33e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 6.2 Peripheral Interrupt Enable Register1 (PIE1) and Register2 (PIE2)

These registers contains the individual enable bits for the peripheral interrupts.

## REGISTER 6-2: PIE1 REGISTER (ADDRESS: 17h, BANK 1)

|       |             | •                               |            | ,            | ,            |              |                 |       |

|-------|-------------|---------------------------------|------------|--------------|--------------|--------------|-----------------|-------|

|       | R/W-0       | R/W-0                           | R/W-0      | R/W-0        | R/W-0        | R/W-0        | R/W-0           | R/W-0 |

|       | RBIE        | TMR3IE                          | TMR2IE     | TMR1IE       | CA2IE        | CA1IE        | TX1IE           | RC1IE |

|       | bit 7       |                                 |            |              |              |              |                 | bit 0 |

|       |             |                                 |            |              |              |              |                 |       |

| bit 7 |             | RTB Interrupt                   | •          |              |              |              |                 |       |

|       |             | e PORTB inte<br>e PORTB inte    |            |              |              |              |                 |       |

| bit 6 |             | MR3 Interrup                    | •          | •            |              |              |                 |       |

| bit 0 |             | • TMR3 interr                   |            |              |              |              |                 |       |

|       | 0 = Disable | e TMR3 inter                    | rupt       |              |              |              |                 |       |

| bit 5 |             | MR2 Interrup                    |            |              |              |              |                 |       |

|       |             | e TMR2 interr<br>e TMR2 inter   | •          |              |              |              |                 |       |

| bit 4 |             | MR1 Interrup                    | •          |              |              |              |                 |       |

| DIL 4 |             | • TMR1 interr                   |            |              |              |              |                 |       |

|       |             | e TMR1 inter                    | •          |              |              |              |                 |       |

| bit 3 |             | pture2 Interr                   |            | oit          |              |              |                 |       |

|       |             | e Capture2 in<br>e Capture2 ir  |            |              |              |              |                 |       |

| bit 2 |             | e Capture2 in<br>apture1 Interr | •          | vit          |              |              |                 |       |

|       |             | e Capture1 in                   |            | ni -         |              |              |                 |       |

|       |             | e Capture1 ir                   |            |              |              |              |                 |       |

| bit 1 |             | ART1 Transr                     |            |              |              |              |                 |       |

|       |             | e USART1 Tra<br>e USART1 Tr     |            |              |              |              |                 |       |

| bit 0 |             | SART1 Recei                     |            |              | ταρι         |              |                 |       |

| DILO  |             | USART1 Re                       |            |              |              |              |                 |       |

|       |             | e USART1 R                      |            |              |              |              |                 |       |

|       |             |                                 |            |              |              |              |                 |       |

|       | Legend:     |                                 |            |              |              |              |                 |       |

|       | R = Reada   | ble bit                         | W = W      | /ritable bit | U = Unim     | plemented bi | it, read as '0' |       |

|       | - n = Value | at POR Res                      | et '1' = B | it is set    | '0' = Bit is | s cleared    | x = Bit is un   | known |

|       |             |                                 |            |              |              |              |                 |       |

#### EXAMPLE 6-1: SAVING STATUS AND WREG IN RAM (SIMPLE)

; The addresses that are used to store the CPUSTA and WREG values must be in the data memory ; address range of 1Ah - 1Fh. Up to 6 locations can be saved and restored using the MOVFP ; instruction. This instruction neither affects the status bits, nor corrupts the WREG register. UNBANK1 ; Address for 1st location to save EQU 0x01A UNBANK2 EQU 0x01B ; Address for 2nd location to save UNBANK3 EQU 0x01C ; Address for 3rd location to save UNBANK4 0x01D EOU ; Address for 4th location to save UNBANK5 EQU 0x01E ; Address for 5th location to save (Label Not used in program) ; UNBANK6 EQU 0x01F ; Address for 6th location to save (Label Not used in program) ; ; ; At Interrupt Vector Address • ALUSTA, UNBANK1 PUSH MOVFP ; Push ALUSTA value MOVFP BSR, UNBANK2 ; Push BSR value MOVFP WREG, UNBANK3 ; Push WREG value MOVFP PCLATH, UNBANK4 ; Push PCLATH value ; ; Interrupt Service Routine (ISR) code : ; UNBANK4, PCLATH ; Restore PCLATH value POP MOVFP UNBANK3, WREG ; Restore WREG value MOVFP MOVFP UNBANK2, BSR ; Restore BSR value MOVFP UNBANK1, ALUSTA ; Restore ALUSTA value ; RETFIE ; Return from interrupt (enable interrupts)

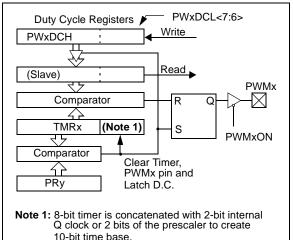

## 13.1.3 USING PULSE WIDTH MODULATION (PWM) OUTPUTS WITH TIMER1 AND TIMER2

Three high speed pulse width modulation (PWM) outputs are provided. The PWM1 output uses Timer1 as its time base, while PWM2 and PWM3 may independently be software configured to use either Timer1 or Timer2 as the time base. The PWM outputs are on the RB2/PWM1, RB3/PWM2 and RG5/PWM3 pins.

Each PWM output has a maximum resolution of 10bits. At 10-bit resolution, the PWM output frequency is 32.2 kHz (@ 32 MHz clock) and at 8-bit resolution the PWM output frequency is 128.9 kHz. The duty cycle of the output can vary from 0% to 100%.

Figure 13-3 shows a simplified block diagram of a PWM module.

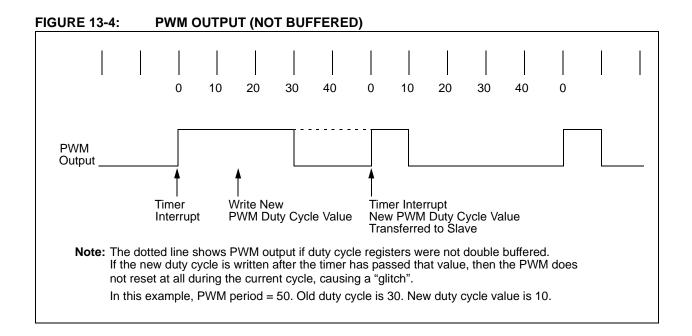

The duty cycle registers are double buffered for glitch free operation. Figure 13-4 shows how a glitch could occur if the duty cycle registers were not double buffered.

The user needs to set the PWM1ON bit (TCON2<4>) to enable the PWM1 output. When the PWM1ON bit is set, the RB2/PWM1 pin is configured as PWM1 output and forced as an output, irrespective of the data direction bit (DDRB<2>). When the PWM1ON bit is clear, the pin behaves as a port pin and its direction is controlled by its data direction bit (DDRB<2>). Similarly, the PWM2ON (TCON2<5>) bit controls the configuration of the RB3/PWM2 pin and the PWM3ON (TCON3<0>) bit controls the configuration of the RG5/PWM3 pin.

#### FIGURE 13-3: SIMPLIFIED PWM BLOCK DIAGRAM

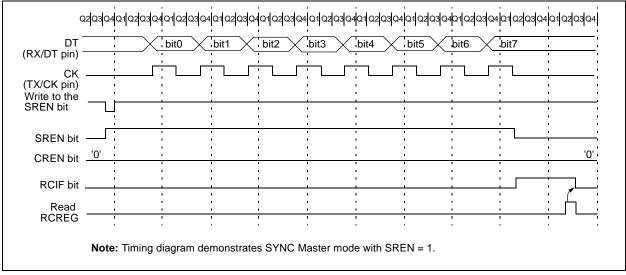

## 14.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either the SREN (RCSTA<5>) bit or the CREN (RCSTA<4>) bit. Data is sampled on the RX/ DT pin on the falling edge of the clock. If SREN is set, then only a single word is received. If CREN is set, the reception is continuous until CREN is reset. If both bits are set, then CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to RCREG (if it is empty). If the transfer is complete, the interrupt bit RCIF is set. The actual interrupt can be enabled/disabled by setting/clearing the RCIE bit. RCIF is a read only bit which is reset by the hardware. In this case, it is reset when RCREG has been read and is empty. RCREG is a double buffered register; i.e., it is a two deep FIFO. It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR. On the clocking of the last bit of the third byte, if RCREG is still full, then the overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. RCREG can be read twice to retrieve the two bytes in the FIFO. The OERR bit has to be cleared in software. This is done by clearing the CREN bit. If OERR is set, transfers from RSR to RCREG are inhibited, so it is essential to clear the OERR bit if it is set. The 9th receive bit is buffered the same way as the receive data. Reading the RCREG register will allow the RX9D and FERR bits to be loaded with values for the next received data; therefore, it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old FERR and RX9D information.

Steps to follow when setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. See Section 14.1 for details.

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, then set the RCIE bit.

- 4. If 9-bit reception is desired, then set the RX9 bit.

- 5. If a single reception is required, set bit SREN. For continuous reception set bit CREN.

- 6. The RCIF bit will be set when reception is complete and an interrupt will be generated if the RCIE bit was set.

- 7. Read RCSTA to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading RCREG.

- 9. If any error occurred, clear the error by clearing CREN.

Note: To terminate a reception, either clear the SREN and CREN bits, or the SPEN bit. This will reset the receive logic so that it will be in the proper state when receive is re-enabled.

## FIGURE 14-10: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

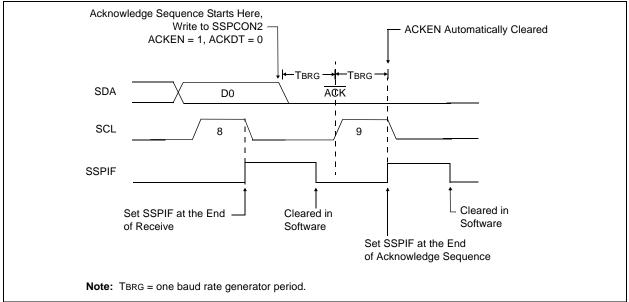

#### 15.2.13 ACKNOWLEDGE SEQUENCE TIMING

An acknowledge sequence is enabled by setting the acknowledge sequence enable bit, ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the acknowledge data bit is presented on the SDA pin. If the user wishes to generate an acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an acknowledge sequence. The baud rate generator then counts for one rollover period (TBRG), and the SCL pin is de-asserted (pulled high). When the SCL pin is sampled high (clock arbitration), the baud rate generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the baud rate generator is turned off and the SSP module then goes into IDLE mode (Figure 15-29).

### 15.2.13.1 WCOL Status Flag

If the user writes the SSPBUF when an acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

## FIGURE 15-29: ACKNOWLEDGE SEQUENCE WAVEFORM

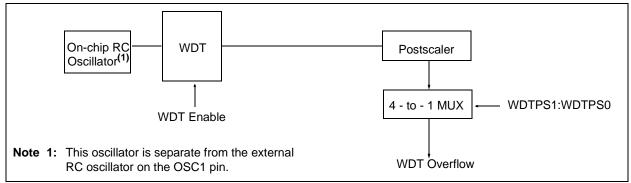

## 17.3 Watchdog Timer (WDT)

The Watchdog Timer's function is to recover from software malfunction, or to reset the device while in SLEEP mode. The WDT uses an internal free running on-chip RC oscillator for its clock source. This does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device RESET. The WDT can be permanently disabled by programming the configuration bits WDTPS1:WDTPS0 as '00' (Section 17.1).

Under normal operation, the WDT must be cleared on a regular interval. This time must be less than the minimum WDT overflow time. Not clearing the WDT in this time frame will cause the WDT to overflow and reset the device.

### 17.3.1 WDT PERIOD

The WDT has a nominal time-out period of 12 ms (with postscaler = 1). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, configuration bits should be used to enable the WDT with a greater prescale. Thus, typical time-out periods up to 3.0 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and its postscale setting and prevent it from timing out, thus generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the CPUSTA register will be cleared upon a WDT time-out.

## FIGURE 17-1: WATCHDOG TIMER BLOCK DIAGRAM

## TABLE 17-2: REGISTERS/BITS ASSOCIATED WITH THE WATCHDOG TIMER

|                                                                           | POR, BOR | MCLR, WDT |

|---------------------------------------------------------------------------|----------|-----------|

| Config See Figure 17-1 for location of WDTPSx bits in Configuration Word. | (Note 1) | (Note 1)  |

| 06h, Unbanked CPUSTA – – STKAV GLINTD TO PD POR BOR                       | 11 11qq  | 11 qquu   |

**Note** 1: This value will be as the device was programmed, or if unprogrammed, will read as all '1's.

The WDT and postscaler are cleared when:

- The device is in the RESET state

- A SLEEP instruction is executed

- A CLRWDT instruction is executed

- Wake-up from SLEEP by an interrupt

The WDT counter/postscaler will start counting on the first edge after the device exits the RESET state.

## 17.3.3 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., Max. WDT postscaler), it may take several seconds before a WDT time-out occurs.

The WDT and postscaler become the Power-up Timer whenever the PWRT is invoked.

## 17.3.4 WDT AS NORMAL TIMER

When the WDT is selected as a normal timer, the clock source is the device clock. Neither the WDT nor the postscaler are directly readable or writable. The overflow time is 65536 Tosc cycles. On overflow, the TO bit is cleared (device is not RESET). The CLRWDT instruction can be used to set the TO bit. This allows the WDT to be a simple overflow timer. The simple timer does not increment when in SLEEP.

## 17.4.2 MINIMIZING CURRENT CONSUMPTION

To minimize current consumption, all I/O pins should be either at VDD, or VSS, with no external circuitry drawing current from the I/O pin. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should be at VDD or VSS. The contributions from on-chip pull-ups on PORTB should also be considered and disabled, when possible.

## 17.5 Code Protection

The code in the program memory can be protected by selecting the microcontroller in Code Protected mode (PM2:PM0 = '000').

In this mode, instructions that are in the on-chip program memory space, can continue to read or write the program memory. An instruction that is executed outside of the internal program memory range will be inhibited from writing to, or reading from, program memory.

**Note:** Microchip does not recommend code protecting windowed devices.

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

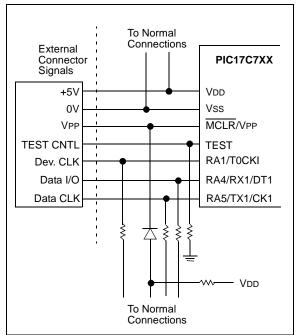

## 17.6 In-Circuit Serial Programming

The PIC17C7XX group of the high-end family (PIC17CXXX) has an added feature that allows serial programming while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware to be programmed.

Devices may be serialized to make the product unique; "special" variants of the product may be offered and code updates are possible. This allows for increased design flexibility.

To place the device into the Serial Programming Test mode, two pins will need to be placed at VIHH. These are the TEST pin and the MCLR/VPP pin. Also, a sequence of events must occur as follows:

- 1. The TEST pin is placed at VIHH.

- 2. The MCLR/VPP pin is placed at VIHH.

There is a setup time between step 1 and step 2 that must be met.

After this sequence, the Program Counter is pointing to program memory address 0xFF60. This location is in the Boot ROM. The code initializes the USART/SCI so that it can receive commands. For this, the device must be clocked. The device clock source in this mode is the RA1/T0CKI pin. After delaying to allow the USART/SCI to initialize, commands can be received. The flow is shown in these 3 steps:

- 1. The device clock source starts.

- 2. Wait 80 device clocks for Boot ROM code to configure the USART/SCI.

- 3. Commands may now be sent.

|             | During Programming |      |                                                   |  |  |  |

|-------------|--------------------|------|---------------------------------------------------|--|--|--|

| Name        | Function           | Туре | Description                                       |  |  |  |

| RA4/RX1/DT1 | DT                 | I/O  | Serial Data                                       |  |  |  |

| RA5/TX1/CK1 | СК                 | I    | Serial Clock                                      |  |  |  |

| RA1/T0CKI   | OSCI               | I    | Device Clock Source                               |  |  |  |

| TEST        | TEST               | I    | Test mode selection control input, force to VIHH  |  |  |  |

| MCLR/VPP    | MCLR/VPP           | Р    | Master Clear Reset and Device Programming Voltage |  |  |  |

| Vdd         | Vdd                | Р    | Positive supply for logic and I/O pins            |  |  |  |

| Vss         | Vss                | Р    | Ground reference for logic and I/O pins           |  |  |  |

#### TABLE 17-3: ICSP INTERFACE PINS

For complete details of serial programming, please refer to the PIC17C7XX Programming Specification. (Contact your local Microchip Technology Sales Office for availability.)

FIGURE 17-3:

#### TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

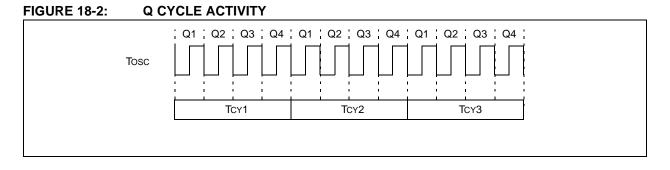

## 18.2 Q Cycle Activity

Each instruction cycle (TcY) is comprised of four Q cycles (Q1-Q4). The Q cycle is the same as the device oscillator cycle (Tosc). The Q cycles provide the timing/ designation for the Decode, Read, Process Data, Write, etc., of each instruction cycle. The following diagram shows the relationship of the Q cycles to the instruction cycle.

The four Q cycles that make up an instruction cycle (TCY) can be generalized as:

- Q1: Instruction Decode Cycle or forced No operation

- Q2: Instruction Read Cycle or No operation

- Q3: Process the Data

- Q4: Instruction Write Cycle or No operation

Each instruction will show the detailed Q cycle operation for the instruction.

| моч   | VLR                            | Move Lite<br>BSR                                                                                                                                                                                                                                                                   | eral to hi     | igh nibb | le in                           |  |  |

|-------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------|---------------------------------|--|--|

| Synt  | ax:                            | [ label ]                                                                                                                                                                                                                                                                          | MOVLR          | k        |                                 |  |  |

| Ope   | rands:                         | $0 \le k \le 15$                                                                                                                                                                                                                                                                   |                |          |                                 |  |  |

| Ope   | ration:                        | $k \rightarrow (BSR < 7:4>)$                                                                                                                                                                                                                                                       |                |          |                                 |  |  |

| Statu | us Affected:                   | None                                                                                                                                                                                                                                                                               |                |          |                                 |  |  |

| Enc   | oding:                         | 1011                                                                                                                                                                                                                                                                               | 101x           | kkkk     | uuuu                            |  |  |

| Des   | cription:                      | otion: The 4-bit literal 'k' is loaded into the<br>most significant 4-bits of the Bank<br>Select Register (BSR). Only the high<br>4-bits of the Bank Select Register<br>are affected. The lower half of the<br>BSR is unchanged. The assembler<br>will encode the "u" fields as 0. |                |          |                                 |  |  |

| Wor   | ds:                            | 1                                                                                                                                                                                                                                                                                  |                |          |                                 |  |  |

| Cyc   | les:                           | 1                                                                                                                                                                                                                                                                                  |                |          |                                 |  |  |

| QC    | ycle Activity:                 |                                                                                                                                                                                                                                                                                    |                |          |                                 |  |  |

|       | Q1                             | Q2                                                                                                                                                                                                                                                                                 | Q3             |          | Q4                              |  |  |

|       | Decode                         | Read literal<br>'k'                                                                                                                                                                                                                                                                | Proce:<br>Data | a lite   | Write<br>eral 'k' to<br>SR<7:4> |  |  |

|       | <u>mple</u> :<br>Before Instru | MOVLR 5                                                                                                                                                                                                                                                                            | i              | ·        |                                 |  |  |

|       | BSR regi                       | ster = 0x                                                                                                                                                                                                                                                                          | 22             |          |                                 |  |  |

|       | After Instruct<br>BSR regi     |                                                                                                                                                                                                                                                                                    | 52             |          |                                 |  |  |

| MO\                                                      | /LW           | Move Lit               | eral to V    | VREG   | 6 |                  |  |

|----------------------------------------------------------|---------------|------------------------|--------------|--------|---|------------------|--|

| Synt                                                     | ax:           | [ label ]              | MOVLW        | / k    |   |                  |  |

| Ope                                                      | rands:        | $0 \le k \le 255$      |              |        |   |                  |  |

| Ope                                                      | ration:       | $k \rightarrow (WREG)$ |              |        |   |                  |  |

| Statu                                                    | us Affected:  | None                   |              |        |   |                  |  |

| Enco                                                     | oding:        | 1011                   | 0000         | kkk    | k | kkkk             |  |

| Description: The eight-bit literal 'k' is loaded i WREG. |               |                        |              | d into |   |                  |  |

| Wor                                                      | ds:           | 1                      |              |        |   |                  |  |

| Cycl                                                     | es:           | 1                      |              |        |   |                  |  |

| QC                                                       | cle Activity: |                        |              |        |   |                  |  |

|                                                          | Q1            | Q2                     | Q            | 3      |   | Q4               |  |

|                                                          | Decode        | Read<br>literal 'k'    | Proce<br>Dat |        | - | Vrite to<br>VREG |  |

|                                                          |               |                        |              |        |   |                  |  |

| <u>Exar</u>                                              | <u>mple</u> : | MOVLW                  | 0x5A         |        |   |                  |  |

After Instruction WREG = 0x5A

© 1998-2013 Microchip Technology Inc.

| SLEEP                                                                                           | Enter SL                                                                                                                          | EEP mode                                                                                             |                                |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------|

| Syntax:                                                                                         | [label] S                                                                                                                         | SLEEP                                                                                                |                                |

| Operands:                                                                                       | None                                                                                                                              |                                                                                                      |                                |

| Operation:                                                                                      | $\begin{array}{l} 00h \rightarrow W\\ 0 \rightarrow WDT\\ 1 \rightarrow \overline{TO};\\ 0 \rightarrow \overline{PD} \end{array}$ | DT;<br>「postscaler;                                                                                  |                                |

| Status Affected:                                                                                | TO, PD                                                                                                                            |                                                                                                      |                                |

| Encoding:                                                                                       | 0000                                                                                                                              | 0000 000                                                                                             | 00 0011                        |

| Description:                                                                                    | cleared. Th<br>set. Watch<br>scaler are<br>The proces                                                                             | -down status I<br>ne time-out sta<br>dog Timer and<br>cleared.<br>ssor is put into<br>the oscillator | tus bit (TO) is<br>d its post- |

| Words:                                                                                          | 1                                                                                                                                 |                                                                                                      |                                |

| Cycles:                                                                                         | 1                                                                                                                                 |                                                                                                      |                                |

| Q Cycle Activity:                                                                               |                                                                                                                                   |                                                                                                      |                                |

| Q1                                                                                              | Q2                                                                                                                                | Q3                                                                                                   | Q4                             |

| Decode                                                                                          | No<br>operation                                                                                                                   | Process<br>Data                                                                                      | Go to<br>sleep                 |

| Example:<br>Before Instru<br>TO =<br>PD =<br>After Instructi<br>TO =<br>PD =<br>† If WDT causes | ?<br>?<br>ion<br>1 †<br>0                                                                                                         | nis bit is clea                                                                                      | red                            |

| SUBLW                   | S         | Subtr           | act   | WREG                  | fron    | n Lit | teral               |

|-------------------------|-----------|-----------------|-------|-----------------------|---------|-------|---------------------|

| Syntax:                 | [         | label           | ] 5   | SUBLW                 | k       |       |                     |

| Operands:               | 0         | ) ≤ k ≤         | ≤ 25  | 5                     |         |       |                     |

| Operation:              | k         | . – (N          | /RE   | $(G) \rightarrow (N)$ | NRE     | G)    |                     |

| Status Affected:        | C         | DV, C           | , D0  | C, Z                  |         |       |                     |

| Encoding:               | Γ         | 1011            | 1     | 0010                  | kk}     | ck    | kkkk                |

| Description:            | li        |                 | k'. T | ubtracte<br>he result |         |       | e eight-bit<br>I in |

| Words:                  | 1         |                 |       |                       |         |       |                     |

| Cycles:                 | 1         |                 |       |                       |         |       |                     |

| Q Cycle Activity:       |           |                 |       |                       |         |       |                     |

| Q1                      |           | Q2              |       | Q3                    |         |       | Q4                  |

| Decode                  |           | Read<br>eral 'k | ς'    | Proce<br>Data         |         |       | Write to<br>WREG    |

| Example 1:              | S         | UBLW            | 0     | x02                   |         |       |                     |

| Before Instru           | uctio     | n               |       |                       |         |       |                     |

| WREG<br>C               | =<br>=    | 1<br>?          |       |                       |         |       |                     |

| After Instruc           |           |                 |       |                       |         |       |                     |

| WREG<br>C               | =<br>=    | 1<br>1          |       | sult is po            | ocitivo |       |                     |

| Z                       | =         | 0               | , re  | suit is pt            | JSILIVE | •     |                     |

| Example 2:              |           |                 |       |                       |         |       |                     |

| Before Instru           | uctio     | n               |       |                       |         |       |                     |

| WREG<br>C               | =         | 2<br>?          |       |                       |         |       |                     |

| After Instruc           | -<br>tion | ·               |       |                       |         |       |                     |

| WREG                    | =         | 0               |       |                       |         |       |                     |

| С                       | =         | 1               | ; re  | sult is ze            | ero     |       |                     |

| Z<br><u>Example 3</u> : | =         | 1               |       |                       |         |       |                     |

| Before Instru           |           |                 |       |                       |         |       |                     |

| WREG<br>C               | =         | 3<br>?          |       |                       |         |       |                     |

| After Instruc           | _         | :               |       |                       |         |       |                     |

| WREG                    | =         | FF              | ; (2  | 's comple             | emen    | t)    |                     |

| С                       | =         | 0               |       | sult is ne            |         | ,     |                     |

| Z                       | =         | 0               |       |                       |         |       |                     |

## 19.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC16F87X and can be used to develop for this and other PIC microcontrollers from the PIC16CXXX family. The MPLAB ICD utilizes the in-circuit debugging capability built into the PIC16F87X. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

## 19.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC MCU devices. It can also set code protection in this mode.

## 19.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

## 19.11 PICDEM 1 Low Cost PIC MCU Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A). PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

## 19.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the I<sup>2</sup>C<sup>™</sup> bus and separate headers for connection to an LCD module and a keypad.

# PIC17C7XX

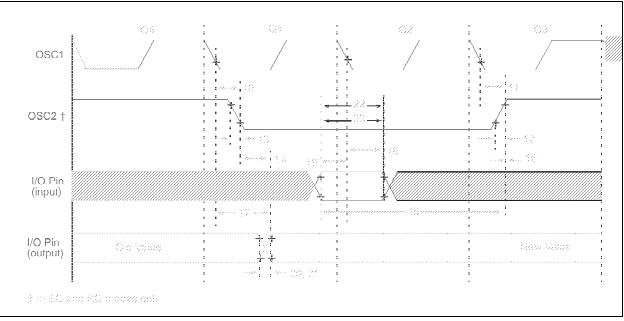

| TABLE 20-2: | CLKOUT AND I/O TIMING REQUIREMENTS |

|-------------|------------------------------------|

|-------------|------------------------------------|

| Param<br>No. | Sym      | Characteristic                                                  | Min          | Тур† | Max         | Units | Conditions |

|--------------|----------|-----------------------------------------------------------------|--------------|------|-------------|-------|------------|

| 10           | TosL2ckL | OSC1↓ to CLKOUT↓                                                |              | 15   | 30          | ns    | (Note 1)   |

| 11           | TosL2ckH | OSC1↓ to CLKOUT↑                                                | —            | 15   | 30          | ns    | (Note 1)   |

| 12           | TckR     | CLKOUT rise time                                                | —            | 5    | 15          | ns    | (Note 1)   |

| 13           | TckF     | CLKOUT fall time                                                | —            | 5    | 15          | ns    | (Note 1)   |

| 14           | TckH2ioV | CLKOUT ↑ to Port out valid                                      | —            | —    | 0.5Tcy + 20 | ns    | (Note 1)   |

| 15           | TioV2ckH | Port in valid before CLKOUT <sup>↑</sup>                        | 0.25Tcy + 25 | —    | —           | ns    | (Note 1)   |

| 16           | TckH2iol | Port in hold after CLKOUT <sup>↑</sup>                          | 0            | —    | —           | ns    | (Note 1)   |

| 17           | TosL2ioV | OSC1↓ (Q1 cycle) to Port out valid                              | —            | —    | 100         | ns    |            |

| 18           | TosL2iol | OSC1↓ (Q2 cycle) to Port input<br>invalid<br>(I/O in hold time) | 0            | —    | _           | ns    |            |

| 19           | TioV2osL | Port input valid to OSC1↓<br>(I/O in setup time)                | 30           | —    | _           | ns    |            |

| 20           | TioR     | Port output rise time                                           | —            | 10   | 35          | ns    |            |

| 21           | TioF     | Port output fall time                                           | —            | 10   | 35          | ns    |            |

| 22           | TinHL    | INT pin high or low time                                        | 25           | —    | —           | ns    |            |

| 23           | TrbHL    | RB7:RB0 change INT high or low time                             | 25           | —    | _           | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note** 1: Measurements are taken in EC mode, where CLKOUT output is 4 x Tosc.

| Param.<br>No. | Sym   | Charac                              | teristic           | Min            | Тур†                      | Max            | Units | Conditions                                                                              |

|---------------|-------|-------------------------------------|--------------------|----------------|---------------------------|----------------|-------|-----------------------------------------------------------------------------------------|

| A01           | NR    | Resolution                          |                    | _              | _                         | 10             | bit   | $\label{eq:VREF+} \begin{array}{l} VDD = 5.12V,\\ VSS \leq VAIN \leq VREF+ \end{array}$ |

|               |       |                                     |                    | _              | _                         | 10             | bit   | $(VREF+ - VREF-) \ge 3.0V,$<br>$VREF- \le VAIN \le VREF+$                               |

| A02           | Eabs  | Absolute error                      |                    | _              | _                         | < ±1           | LSb   | $\begin{array}{l} VREF+ = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF+ \end{array}$          |

|               |       |                                     |                    | —              | —                         | < ±1           | LSb   | $(VREF+ - VREF-) \ge 3.0V,$<br>$VREF- \le VAIN \le VREF+$                               |

| A03           | EIL   | Integral linearity                  | error              |                | -                         | < ±1           | LSb   | VREF+ = VDD = 5.12V,<br>$VSS \le VAIN \le VREF+$                                        |

|               |       |                                     |                    | _              | -                         | < ±1           | LSb   | $(VREF+ - VREF-) \ge 3.0V,$<br>$VREF- \le VAIN \le VREF+$                               |

| A04           | Edl   | Differential linear                 | ity error          |                |                           | < ±1           | LSb   | VREF+ = VDD = 5.12V,<br>$VSS \le VAIN \le VREF+$                                        |

|               |       |                                     |                    | _              | _                         | < ±1           | LSb   | $(VREF+ - VREF-) \ge 3.0V,$<br>$VREF- \le VAIN \le VREF+$                               |

| A05           | Efs   | Full scale error                    |                    | _              | _                         | < ±1           | LSb   | $\label{eq:VREF+} \begin{array}{l} VDD = 5.12V,\\ VSS \leq VAIN \leq VREF+ \end{array}$ |

|               |       |                                     |                    | _              | _                         | < ±1           | LSb   | $(VREF+ - VREF-) \ge 3.0V,$<br>$VREF- \le VAIN \le VREF+$                               |

| A06           | EOFF  | Offset error                        |                    | _              | _                         | < ±1           | LSb   | $\label{eq:VREF+} \begin{array}{l} VBF F F F VDD F F S S S S S S S S$                   |

|               |       |                                     |                    | _              | _                         | < ±1           | LSb   | $(VREF+ - VREF-) \ge 3.0V,$<br>$VREF- \le VAIN \le VREF+$                               |

| A10           | —     | Monotonicity                        |                    | —              | guaranteed <sup>(3)</sup> | _              | —     | $VSS \leq VAIN \leq VREF$                                                               |

| A20           | Vref  | Reference voltage<br>(VREF+ — VREF- | ,                  | 0V             |                           | _              | V     | VREF delta when changing voltage levels on VREF inputs                                  |

| A20A          |       |                                     |                    | 3V             | _                         | _              | V     | Absolute minimum electrical spec.<br>to ensure 10-bit accuracy                          |

| A21           | VREF+ | Reference voltag                    | ge high            | Avss<br>+ 3.0V | —                         | AVDD +<br>0.3V | V     |                                                                                         |

| A22           | VREF- | Reference voltag                    | ge low             | Avss -<br>0.3V | _                         | Avdd -<br>3.0V | V     |                                                                                         |

| A25           | Vain  | Analog input volt                   | age                | Avss-<br>0.3V  | _                         | Vref +<br>0.3V | V     |                                                                                         |

| A30           | Zain  | Recommended i analog voltage s      |                    | _              | _                         | 10.0           | kΩ    |                                                                                         |

| A40           | IAD   | A/D conversion                      | PIC17CXXX          | —              | 180                       |                | μΑ    | Average current consumption when                                                        |

|               |       | current (VDD)                       | PIC17LCXXX         | _              | 90                        | _              | μΑ    | A/D is on <b>(Note 1)</b>                                                               |

| A50           | IREF  | VREF input curre                    | nt <b>(Note 2)</b> | 10             | —                         | 1000           | μA    | During VAIN acquisition.<br>Based on differential of VHOLD to<br>VAIN                   |

|               |       |                                     |                    | _              | _                         | 10             | μΑ    | During A/D conversion cycle                                                             |

| TABLE 20-18: A/D C | ONVERTER | CHARACTERISTICS |

|--------------------|----------|-----------------|

|--------------------|----------|-----------------|

† Data in "Typ" column is at 5V, 25°C unless otherwise stated.

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RG0 and RG1 pins or AVDD and AVSS pins, whichever is selected as reference input.

3: The A/D conversion result never decreases with an increase in the Input Voltage and has no missing codes.

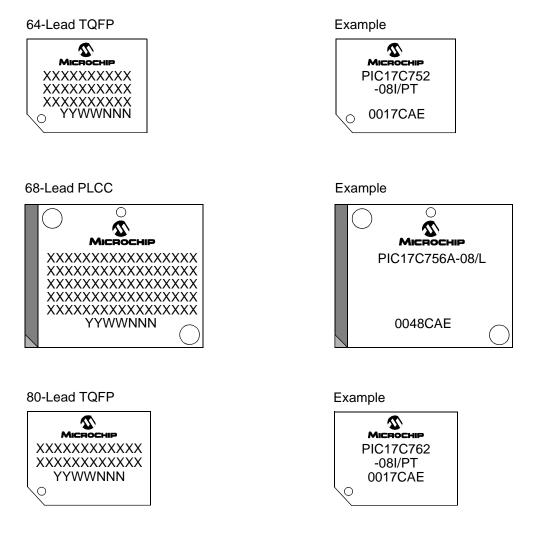

# 22.0 PACKAGING INFORMATION

## 22.1 Package Marking Information

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                      | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Note:  | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                              |  |

# PIC17C7XX

#### F

| PIC17C75X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FERR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Flowcharts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Acknowledge166                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Master Receiver163                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Master Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RESTART Condition157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Start Condition 155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| STOP Condition 168                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FOSC0 191                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| FOSC1 191                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| FS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FS3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FSR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| FSR154<br>G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| General Call Address Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| General Call Address Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| General Format for Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| General Purpose RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| General Purpose RAM Bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |