Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 16MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 66                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 902 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 16x10b                                                                  |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c766t-16i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

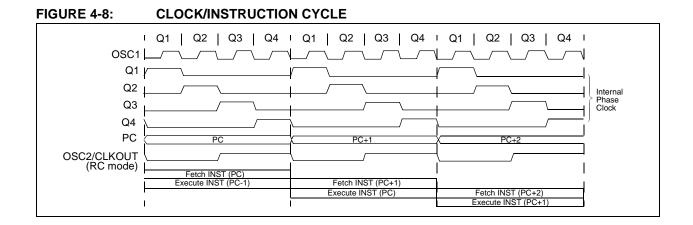

### 4.2 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1 and the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 4-8.

## 4.3 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO), then two cycles are required to complete the instruction (Example 4-1).

A fetch cycle begins with the program counter incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### EXAMPLE 4-1: INSTRUCTION PIPELINE FLOW

|                         | TCY0        | TCY1      | TCY2      | TCY3      | TCY4        | TCY5          |

|-------------------------|-------------|-----------|-----------|-----------|-------------|---------------|

| 1. MOVLW 55h            | Fetch 1     | Execute 1 |           |           |             |               |

| 2. MOVWF PORTB          |             | Fetch 2   | Execute 2 |           | _           |               |

| 3. CALL SUB_1           |             |           | Fetch 3   | Execute 3 |             |               |

| 4. BSF PORTA, BIT3 (F   | Forced NOP) |           |           | Fetch 4   | Flush       |               |

| 5. Instruction @ addres | s SUB_1     |           |           |           | Fetch SUB_1 | Execute SUB_1 |

|                         |             |           |           |           |             |               |

All instructions are single cycle, except for any program branches. These take two cycles since the fetched instruction is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

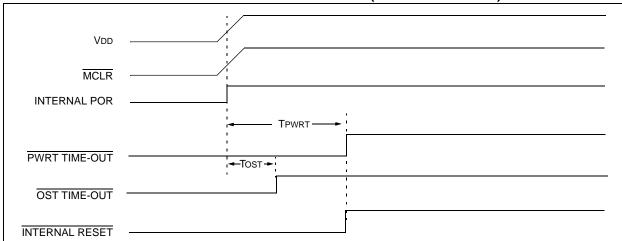

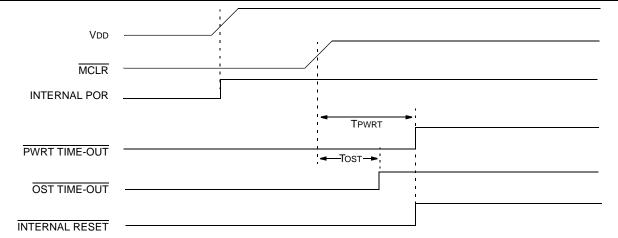

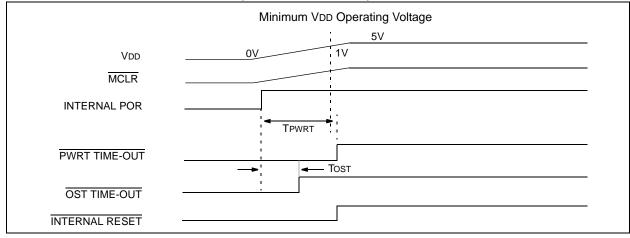

In Figure 5-5, Figure 5-6 and Figure 5-7, the TPWRT timer time-out is greater then the TOST timer time-out, as would be the case in higher frequency crystals. For lower frequency crystals (i.e., 32 kHz), TOST may be greater.

### FIGURE 5-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

| TABLE 5-4: INITIALIZATION CONDITIONS FOR SPECIAL FUNCTION REGISTERS (CONTI |         |                                   |                         |                                         |  |  |

|----------------------------------------------------------------------------|---------|-----------------------------------|-------------------------|-----------------------------------------|--|--|

| Register                                                                   | Address | Power-on Reset<br>Brown-out Reset | MCLR Reset<br>WDT Reset | Wake-up from SLEEP<br>through Interrupt |  |  |

| Bank 1                                                                     |         |                                   |                         |                                         |  |  |

| DDRC <sup>(5)</sup>                                                        | 10h     | 1111 1111                         | 1111 1111               | սսսս սսսս                               |  |  |

| PORTC <sup>(4,5)</sup>                                                     | 11h     | xxxx xxxx                         | uuuu uuuu               | นนนน นนนน                               |  |  |

| DDRD <sup>(5)</sup>                                                        | 12h     | 1111 1111                         | 1111 1111               | นนนน นนนน                               |  |  |

| PORTD <sup>(4,5)</sup>                                                     | 13h     | xxxx xxxx                         | uuuu uuuu               | นนนน นนนน                               |  |  |

| DDRE <sup>(5)</sup>                                                        | 14h     | 1111                              | 1111                    | uuuu                                    |  |  |

| PORTE <sup>(4,5)</sup>                                                     | 15h     | xxxx                              | uuuu                    | uuuu                                    |  |  |

| PIR1                                                                       | 16h     | x000 0010                         | u000 0010               | սսսս սսսս(1)                            |  |  |

| PIE1                                                                       | 17h     | 0000 0000                         | 0000 0000               | uuuu uuuu                               |  |  |

| Bank 2                                                                     |         |                                   |                         |                                         |  |  |

| TMR1                                                                       | 10h     | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |

| TMR2                                                                       | 11h     | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |

| TMR3L                                                                      | 12h     | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |

| TMR3H                                                                      | 13h     | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |  |  |

| PR1                                                                        | 14h     | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |

| PR2                                                                        | 15h     | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |

| PR3/CA1L                                                                   | 16h     | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |

| PR3/CA1H                                                                   | 17h     | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |  |  |

| Bank 3                                                                     |         |                                   |                         |                                         |  |  |

| PW1DCL                                                                     | 10h     | xx                                | uu                      | uu                                      |  |  |

| PW2DCL                                                                     | 11h     | xx0                               | uu0                     | uuu                                     |  |  |

| PW1DCH                                                                     | 12h     | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |

| PW2DCH                                                                     | 13h     | xxxx xxxx                         | uuuu uuuu               | นนนน นนนน                               |  |  |

| CA2L                                                                       | 14h     | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |

| CA2H                                                                       | 15h     | xxxx xxxx                         | uuuu uuuu               | uuuu uuuu                               |  |  |

| TCON1                                                                      | 16h     | 0000 0000                         | 0000 0000               | uuuu uuuu                               |  |  |

| TCON2                                                                      | 17h     | 0000 0000                         | 0000 0000               | uuuu uuuu                               |  |  |

### TABLE 5-4: INITIALIZATION CONDITIONS FOR SPECIAL FUNCTION REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented, read as '0', q = value depends on condition

Note 1: One or more bits in INTSTA, PIR1, PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GLINTD bit is cleared, the PC is loaded with the interrupt vector.

3: See Table 5-3 for RESET value of specific condition.

4: This is the value that will be in the port output latch.

**5:** When the device is configured for Microprocessor or Extended Microcontroller mode, the operation of this port does not rely on these registers.

6: On any device RESET, these pins are configured as inputs.

### 5.1.5 BROWN-OUT RESET (BOR)

PIC17C7XX devices have on-chip Brown-out Reset circuitry. This circuitry places the device into a RESET when the device voltage falls below a trip point (BVDD). This ensures that the device does not continue program execution outside the valid operation range of the device. Brown-out Resets are typically used in AC line applications, or large battery applications, where large loads may be switched in (such as automotive).

| Note: | Before using the on-chip Brown-out for a |

|-------|------------------------------------------|

|       | voltage supervisory function, please     |

|       | review the electrical specifications to  |

|       | ensure that they meet your requirements. |

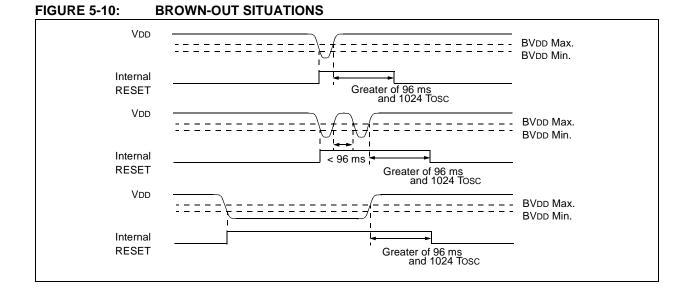

The BODEN configuration bit can disable (if clear/ programmed), or enable (if set) the Brown-out Reset circuitry. If VDD falls below BVDD (typically 4.0 V, paramter #D005 in electrical specification section), for greater than parameter #35, the Brown-out situation will reset the chip. A RESET is not guaranteed to occur if VDD falls below BVDD for less than paramter #35. The chip will remain in Brown-out Reset until VDD rises above BVDD. The Power-up Timer and Oscillator Startup Timer will then be invoked. This will keep the chip in RESET the greater of 96 ms and 1024 Tosc. If VDD drops below BVDD while the Power-up Timer/Oscillator Start-up Timer is running, the chip will go back into a Brown-out Reset. The Power-up Timer/Oscillator Startup Timer will be initialized. Once VDD rises above BVDD, the Power-up Timer/Oscillator Start-up Timer will start their time delays. Figure 5-10 shows typical Brown-out situations.

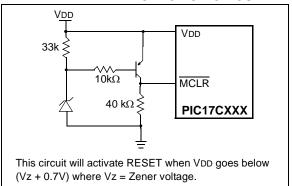

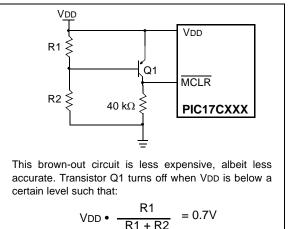

In some applications, the Brown-out Reset trip point of the device may not be at the desired level. Figure 5-8 and Figure 5-9 are two examples of external circuitry that may be implemented. Each needs to be evaluated to determine if they match the requirements of the application.

### EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

FIGURE 5-9:

### EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

© 1998-2013 Microchip Technology Inc.

NOTES:

### 6.1 Interrupt Status Register (INTSTA)

The Interrupt Status/Control register (INTSTA) contains the flag and enable bits for non-peripheral interrupts.

The PEIF bit is a read only, bit wise OR of all the peripheral flag bits in the PIR registers (Figure 6-4 and Figure 6-5).

| Note: | All interrupt flag bits get set by their speci- |

|-------|-------------------------------------------------|

|       | fied condition, even if the corresponding       |

|       | interrupt enable bit is clear (interrupt dis-   |

|       | abled), or the GLINTD bit is set (all inter-    |

|       | rupts disabled).                                |

Care should be taken when clearing any of the INTSTA register enable bits when interrupts are enabled (GLINTD is clear). If any of the INTSTA flag bits (T0IF, INTF, T0CKIF, or PEIF) are set in the same instruction cycle as the corresponding interrupt enable bit is cleared, the device will vector to the RESET address (0x00).

Prior to disabling any of the INTSTA enable bits, the GLINTD bit should be set (disabled).

### REGISTER 6-1: INTSTA REGISTER (ADDRESS: 07h, UNBANKED)

|       | R-0                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                            | R/W-0                                        | R/W-0                          | R/W-0        | R/W-0                              | R/W-0         | R/W-0      |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------|--------------------------------|--------------|------------------------------------|---------------|------------|--|--|

|       | PEIF                                                                                                                                                                                                                                                                                                                                                | T0CKIF                                           | T0IF                                         | INTF                           | PEIE         | <b>T0CKIE</b>                      | T0IE          | INTE       |  |  |

|       | bit 7                                                                                                                                                                                                                                                                                                                                               |                                                  |                                              |                                |              |                                    |               | bit 0      |  |  |

| bit 7 | This bit is t<br>The interro<br>pending.<br>1 = A perip                                                                                                                                                                                                                                                                                             |                                                  | peripheral in<br>es program<br>pt is pending | execution to                   |              | vith their corres<br>20h) when a p |               |            |  |  |

| bit 6 | <b>TOCKIF</b> : External Interrupt on TOCKI Pin Flag bit<br>This bit is cleared by hardware, when the interrupt logic forces program execution to address (18h).<br>1 = The software specified edge occurred on the RA1/T0CKI pin<br>0 = The software specified edge did not occur on the RA1/T0CKI pin                                             |                                                  |                                              |                                |              |                                    |               |            |  |  |

| bit 5 | <ul> <li>TOIF: TMR0 Overflow Interrupt Flag bit</li> <li>This bit is cleared by hardware, when the interrupt logic forces program execution to address (10h).</li> <li>1 = TMR0 overflowed</li> <li>0 = TMR0 did not overflow</li> </ul>                                                                                                            |                                                  |                                              |                                |              |                                    |               |            |  |  |

| bit 4 | This bit is o<br>1 = The so                                                                                                                                                                                                                                                                                                                         | oftware specif                                   | dware, when                                  | the interrupt<br>curred on the | e RA0/INT pi |                                    | tion to addre | ess (08h). |  |  |

| bit 3 | <ul> <li>0 = The software specified edge did not occur on the RA0/INT pin</li> <li>PEIE: Peripheral Interrupt Enable bit</li> <li>This bit acts as a global enable bit for the peripheral interrupts that have their corresponding enable bits set.</li> <li>1 = Enable peripheral interrupts</li> <li>0 = Disable peripheral interrupts</li> </ul> |                                                  |                                              |                                |              |                                    |               |            |  |  |

| bit 2 | 1 = Enable                                                                                                                                                                                                                                                                                                                                          | xternal Interr<br>software sp<br>e interrupt on  | ecified edge                                 | interrupt on                   |              | CKI pin                            |               |            |  |  |

| bit 1 | 1 = Enable                                                                                                                                                                                                                                                                                                                                          | 80 Overflow I<br>e TMR0 overf<br>e TMR0 over     | low interrupt                                |                                |              |                                    |               |            |  |  |

| bit 0 | 1 = Enable                                                                                                                                                                                                                                                                                                                                          | ernal Interrup<br>e software sp<br>e software sp | ecified edge                                 | interrupt on                   | the RA0/INT  |                                    |               |            |  |  |

|       | Legend:                                                                                                                                                                                                                                                                                                                                             |                                                  |                                              |                                |              |                                    |               |            |  |  |

|       | R = Reada                                                                                                                                                                                                                                                                                                                                           | ble bit                                          | W = W                                        | ritable bit                    | U = Unim     | plemented bit                      | , read as '0  | ,          |  |  |

'1' = Bit is set

- n = Value at POR Reset

x = Bit is unknown

'0' = Bit is cleared

### 7.2.2.2 CPU Status Register (CPUSTA)

The CPUSTA register contains the status and control bits for the CPU. This register has a bit that is used to globally enable/disable interrupts. If only a specific interrupt is desired to be enabled/disabled, please refer to the Interrupt Status (INTSTA) register and the Peripheral Interrupt Enable (PIE) registers. The CPUSTA register also indicates if the stack is available and contains the Power-down (PD) and Time-out (TO) bits. The TO, PD, and STKAV bits are not writable. These bits are set and cleared according to device

logic. Therefore, the result of an instruction with the CPUSTA register as destination may be different than intended.

The  $\overrightarrow{\text{POR}}$  bit allows the differentiation between a Power-on Reset, external  $\overrightarrow{\text{MCLR}}$  Reset, or a WDT Reset. The BOR bit indicates if a Brown-out Reset occurred.

**Note 1:** The BOR status bit is a don't care and is not necessarily predictable if the Brown-out circuit is disabled (when the BODEN bit in the Configuration word is programmed).

### REGISTER 7-2: CPUSTA REGISTER (ADDRESS: 06h, UNBANKED)

| _ | U-0   | U-0 | R-1   | R/W-1  | R-1 | R-1 | R/W-0 | R/W-1 |

|---|-------|-----|-------|--------|-----|-----|-------|-------|

|   | _     |     | STKAV | GLINTD | TO  | PD  | POR   | BOR   |

|   | bit 7 |     |       |        |     |     |       | bit 0 |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | <ul> <li>STKAV: Stack Available bit</li> <li>This bit indicates that the 4-bit stack pointer value is Fh, or has rolled over from Fh → 0h (stack overflow).</li> <li>1 = Stack is available</li> <li>0 = Stack is full, or a stack overflow may have occurred (once this bit has been cleared by a stack overflow, only a device RESET will set this bit)</li> </ul> |

| bit 4   | <ul> <li>GLINTD: Global Interrupt Disable bit</li> <li>This bit disables all interrupts. When enabling interrupts, only the sources with their enable bits set can cause an interrupt.</li> <li>1 = Disable all interrupts</li> <li>0 = Enables all unmasked interrupts</li> </ul>                                                                                   |

| bit 3   | TO: WDT Time-out Status bit<br>1 = After power-up, by a CLRWDT instruction, or by a SLEEP instruction<br>0 = A Watchdog Timer time-out occurred                                                                                                                                                                                                                      |

| bit 2   | <b>PD</b> : Power-down Status bit<br>1 = After power-up or by the CLRWDT instruction<br>0 = By execution of the SLEEP instruction                                                                                                                                                                                                                                    |

| bit 1   | <b>POR</b> : Power-on Reset Status bit<br>1 = No Power-on Reset occurred<br>0 = A Power-on Reset occurred (must be set by software)                                                                                                                                                                                                                                  |

| bit 0   | BOR: Brown-out Reset Status bit                                                                                                                                                                                                                                                                                                                                      |

|         | When BODEN Configuration bit is set (enabled):<br>1 = No Brown-out Reset occurred<br>0 = A Brown-out Reset occurred (must be set by software)                                                                                                                                                                                                                        |

|         | When BODEN Configuration bit is clear (disabled):<br>Don't care                                                                                                                                                                                                                                                                                                      |

|         |                                                                                                                                                                                                                                                                                                                                                                      |

|         | Legend:                                                                                                                                                                                                                                                                                                                                                              |

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR Reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

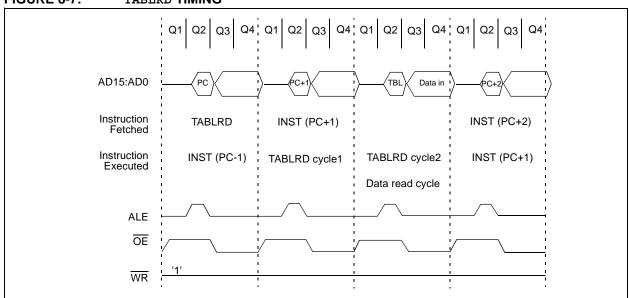

### 8.3 Table Reads

The table read allows the program memory to be read. This allows constants to be stored in the program memory space and retrieved into data memory when needed. Example 8-2 reads the 16-bit value at program memory address TBLPTR. After the dummy byte has been read from the TABLATH, the TABLATH is loaded with the 16-bit data from program memory address TBLPTR and then increments the TBLPTR value. The first read loads the data into the latch and can be considered a dummy read (unknown data loaded into 'f'). INDF0 should be configured for either auto-increment or auto-decrement.

### EXAMPLE 8-2: TABLE READ

| MOVLW  | HIGH (TBL_ADDR) ; Load the Table |

|--------|----------------------------------|

| MOVWF  | TBLPTRH ; address                |

| MOVLW  | LOW (TBL_ADDR) ;                 |

| MOVWF  | TBLPTRL ;                        |

| TABLRD | 0, 1, DUMMY ; Dummy read,        |

|        | ; Updates TABLATH                |

|        | ; Increments TBLPTR              |

| TLRD   | 1, INDF0 ; Read HI byte          |

|        | ; of TABLATH                     |

| TABLRD | 0, 1, INDF0 ; Read LO byte       |

|        | ; of TABLATL and                 |

|        | ; Update TABLATH                 |

|        | ; Increment TBLPTR               |

|        |                                  |

### FIGURE 8-8: TABLED TIMING (CONSECUTIVE TABLED INSTRUCTIONS)

|                         | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4    | Q1 Q2 Q3 Q4     | Q1 Q2 Q3 Q4    | Q1 Q2 Q3 Q4     | Q1 Q2 Q3 Q4 |

|-------------------------|-------------|----------------|-----------------|----------------|-----------------|-------------|

| AD15:AD0                | PC          | PC+1           | TBL1 Data in 1  | PC+2           | TBL2 Data in 2  |             |

| Instruction<br>Fetched  | TABLRD1     | TABLRD2        |                 | INST (PC+2)    |                 | INST (PC+3) |

| Instruction<br>Executed | INST (PC-1) | TABLRD1 cycle1 | TABLRD1 cycle2  | TABLRD2 cycle1 | TABLRD2 cycle2  | INST (PC+2) |

|                         |             |                | Data read cycle | 1<br>1         | Data read cycle |             |

| ALE                     |             |                |                 |                |                 |             |

| OE                      |             |                |                 |                |                 |             |

| WR                      | '1'         |                |                 |                |                 |             |

|                         | I           |                | I               | I              | •               |             |

FIGURE 8-7: TABLRD TIMING

|       | R-0                                                                            | R-0                                                                   | R/W-0                                                                            | R/W-0                                                                       | R/W-0                        | R/W-0                                                            | R/W-0                         | R/W-0                       |

|-------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------|-------------------------------|-----------------------------|

|       | CA2OVF                                                                         | CA10VF                                                                | PWM2ON                                                                           | PWM10N                                                                      | CA1/PR3                      | TMR3ON                                                           | TMR2ON                        | TMR10N                      |

|       | bit 7                                                                          |                                                                       |                                                                                  |                                                                             |                              |                                                                  |                               | bit 0                       |

| bit 7 | This bit in<br>(CA2H:CA<br>unread cap<br>the capture<br>1 = Overflo            | 2L) before th<br>oture value (l                                       | the capture<br>ne next capt<br>ast capture<br>h the TMR3<br>on Capture2          | e value had<br>ure event oc<br>before overfle<br>value until th<br>register | curred. The ow). Subseq      | ead from the<br>capture regi<br>uent capture<br>gister has be    | ster retains<br>events will r | the oldest<br>not update    |

| bit 6 | This bit ind<br>CA1H:PR3<br>est unread<br>update the<br>bytes).<br>1 = Overflo | BL/CA1L), be<br>I capture va                                          | ne capture va<br>fore the next<br>lue (last cap<br>ister with the<br>on Capture1 | alue had not l<br>capture even<br>oture before<br>TMR3 value<br>register    | nt occurred.<br>overflow). S | om the captur<br>The capture r<br>subsequent c<br>apture registe | egister retai<br>apture even  | ns the old-<br>its will not |

| bit 5 | <b>PWM2ON</b> :<br>1 = PWM2<br>(The R<br>0 = PWM2                              | PWM2 On I<br>is enabled<br>B3/PWM2 pi<br>is disabled                  | bit<br>n ignores the                                                             | e state of the                                                              |                              | oit.)<br>for data direc                                          | tion.)                        |                             |

| bit 4 | 1 = PWM1<br>(The R<br>0 = PWM1                                                 | B2/PWM1 pi<br>is disabled                                             | n ignores the                                                                    | e state of the<br>tate of the DI                                            |                              | oit.)<br>for data direc                                          | tion.)                        |                             |

| bit 3 | 1 =Enable<br>(PR3H)<br>0 =Enable                                               | /CA1H:PR3L<br>s the Period                                            | /CA1L is the register                                                            |                                                                             | -                            | r3 runs witho<br>r3.)                                            | ut a period r                 | egister.)                   |

| bit 2 | -                                                                              | Timer3 On b<br>Timer3                                                 |                                                                                  |                                                                             |                              | ,                                                                |                               |                             |

| bit 1 | TMR2ON:<br>This bit cor<br>(T16 is set                                         | Timer2 On b<br>ntrols the inc<br>), TMR2ON<br>Timer2 (mus             | rementing of<br>must be set.                                                     |                                                                             | he MSB of t                  | n TMR2:TMR<br>he timer to in<br>>) is set)                       |                               | 6-bit timer                 |

| bit 0 | •                                                                              | Timer1 On b                                                           | oit                                                                              |                                                                             |                              |                                                                  |                               |                             |

|       | <u>When T16</u><br>1 = Starts 7<br>0 = Stops 7                                 | <u>is set (in 16</u><br>16-bit TMR2<br>16-bit TMR2:<br>is clear (in 8 | bit Timer mo<br>TMR1<br>TMR1                                                     |                                                                             |                              |                                                                  |                               |                             |

## REGISTER 13-2: TCON2 REGISTER (ADDRESS: 17h, BANK 3)

#### 15.1.4 MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 15-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "Line Activity Monitor" mode.

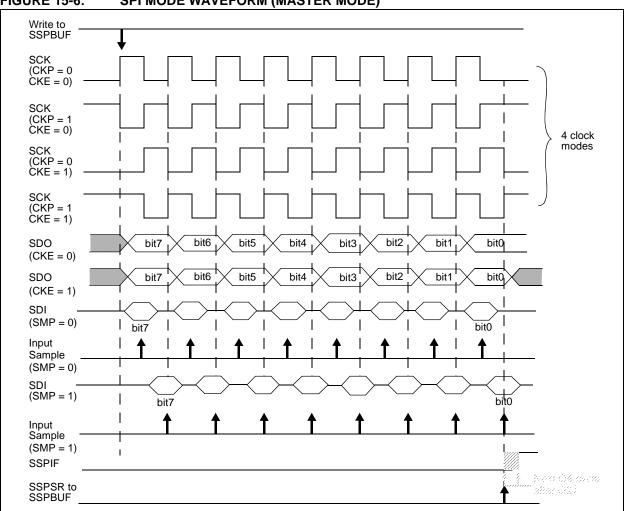

The clock polarity is selected by appropriately programming bit CKP (SSPCON1<4>). This then, would give waveforms for SPI communication as shown in

Figure 15-6, Figure 15-8 and Figure 15-9, where the MSb is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum bit clock frequency (at 33 MHz) of 8.25 MHz.

Figure 15-6 shows the waveforms for Master mode. When CKE = 1, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

#### **FIGURE 15-6:** SPI MODE WAVEFORM (MASTER MODE)

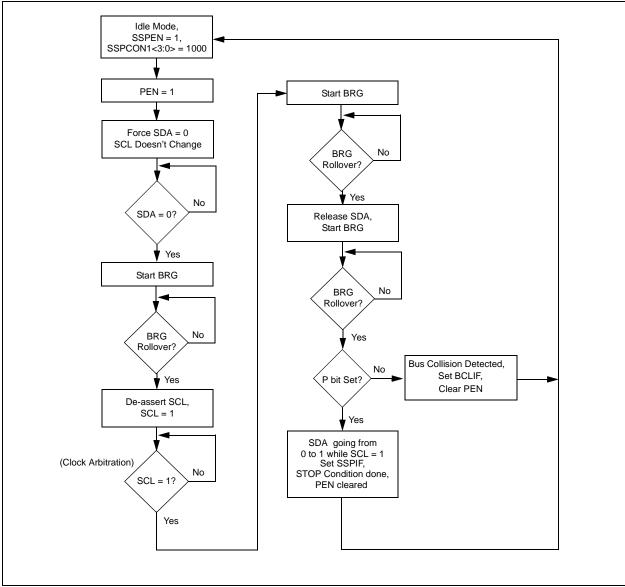

### FIGURE 15-32: STOP CONDITION FLOW CHART

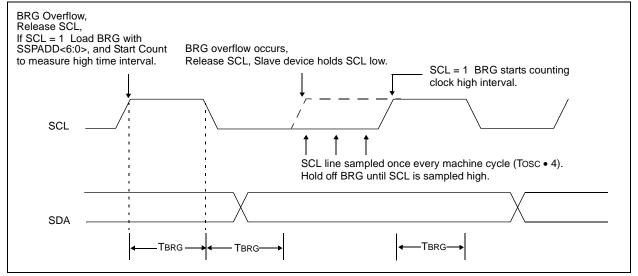

### 15.2.15 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit, or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the baud rate generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count, in the event that the clock is held low by an external device (Figure 15-33).

### 15.2.16 SLEEP OPERATION

While in SLEEP mode, the I<sup>2</sup>C module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from SLEEP (if the SSP interrupt is enabled).

### 15.2.17 EFFECTS OF A RESET

A RESET disables the SSP module and terminates the current transfer.

### FIGURE 15-33: CLOCK ARBITRATION TIMING IN MASTER TRANSMIT MODE

### 17.4.2 MINIMIZING CURRENT CONSUMPTION

To minimize current consumption, all I/O pins should be either at VDD, or VSS, with no external circuitry drawing current from the I/O pin. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should be at VDD or VSS. The contributions from on-chip pull-ups on PORTB should also be considered and disabled, when possible.

## 17.5 Code Protection

The code in the program memory can be protected by selecting the microcontroller in Code Protected mode (PM2:PM0 = '000').

In this mode, instructions that are in the on-chip program memory space, can continue to read or write the program memory. An instruction that is executed outside of the internal program memory range will be inhibited from writing to, or reading from, program memory.

**Note:** Microchip does not recommend code protecting windowed devices.

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| MO\   | /PF            | Move p to f                                                                                                                         |                                                                                                                                                                                                                                   |      |                      |  |  |  |

|-------|----------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|--|--|--|

| Synt  | ax:            | [ <i>label</i> ] N                                                                                                                  | <i>I</i> OVPF                                                                                                                                                                                                                     | p,f  |                      |  |  |  |

| Ope   | rands:         | $0 \le f \le 25$<br>$0 \le p \le 31$                                                                                                | -                                                                                                                                                                                                                                 |      |                      |  |  |  |

| Ope   | ration:        | $(p) \to (f)$                                                                                                                       |                                                                                                                                                                                                                                   |      |                      |  |  |  |

| Statu | us Affected:   | Z                                                                                                                                   |                                                                                                                                                                                                                                   |      |                      |  |  |  |

| Enco  | oding:         | 010p                                                                                                                                | pppp                                                                                                                                                                                                                              | ffff | ffff                 |  |  |  |

| Des   | cription:      | 'p' to data u<br>'f' can be a<br>space (00h<br>to 1Fh.<br>Either 'p' o<br>special situ<br>MOVPF is p<br>ring a perip<br>or an I/O p | Either 'p' or 'f' can be WREG (a useful, special situation).<br>MOVPF is particularly useful for transferring a peripheral register (e.g. the timer or an I/O port) to a data memory location. Both 'f' and 'p' can be indirectly |      |                      |  |  |  |

| Wor   | ds:            | 1                                                                                                                                   |                                                                                                                                                                                                                                   |      |                      |  |  |  |

| Cycl  | es:            | 1                                                                                                                                   | 1                                                                                                                                                                                                                                 |      |                      |  |  |  |

| QC    | ycle Activity: |                                                                                                                                     |                                                                                                                                                                                                                                   |      |                      |  |  |  |

|       | Q1             | Q2                                                                                                                                  | Q3                                                                                                                                                                                                                                | 3    | Q4                   |  |  |  |

|       | Decode         | Read<br>register 'p'                                                                                                                | Proce<br>Dat                                                                                                                                                                                                                      |      | Write<br>egister 'f' |  |  |  |

|       |                |                                                                                                                                     |                                                                                                                                                                                                                                   |      |                      |  |  |  |

| Example:          | MOVPF | REG1, | REG2 |

|-------------------|-------|-------|------|

| Before Instruc    | tion  |       |      |

| REG1              | =     | 0x11  |      |

| REG2              | =     | 0x33  |      |

| After Instruction | on    |       |      |

=

=

0x11

0x11

REG1

REG2

| MOVWF             | Move WR                                  | EG to f                  |      |                     |  |  |  |  |

|-------------------|------------------------------------------|--------------------------|------|---------------------|--|--|--|--|

| Syntax:           | [ label ]                                | MOVWF                    | f    |                     |  |  |  |  |

| Operands:         | $0 \le f \le 255$                        | $0 \leq f \leq 255$      |      |                     |  |  |  |  |

| Operation:        | (WREG) -                                 | $(WREG) \rightarrow (f)$ |      |                     |  |  |  |  |

| Status Affected:  | None                                     |                          |      |                     |  |  |  |  |

| Encoding:         | 0000                                     | 0001                     | ffff | ffff                |  |  |  |  |

| Description:      | Move data<br>Location 'f'<br>byte data s | can be an                | 0    |                     |  |  |  |  |

| Words:            | 1                                        |                          |      |                     |  |  |  |  |

| Cycles:           | 1                                        |                          |      |                     |  |  |  |  |

| Q Cycle Activity: |                                          |                          |      |                     |  |  |  |  |

| Q1                | Q2                                       | Q3                       |      | Q4                  |  |  |  |  |

| Decode            | Read<br>register 'f'                     | Proces<br>Data           |      | Write<br>gister 'f' |  |  |  |  |

| Example:          | MOVWF                                    | REG                      | ·    |                     |  |  |  |  |

| Before Instr  | uctio | n    |

|---------------|-------|------|

| WREG          | =     | 0x4F |

| REG           | =     | 0xFF |

| After Instruc | tion  |      |

|      | lion |      |

|------|------|------|

| WREG | =    | 0x4F |

| REG  | =    | 0x4F |

### 19.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can also link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian is a librarian for precompiled code to be used with the MPLINK object linker. When a routine from a library is called from another source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. The MPLIB object librarian manages the creation and modification of library files.

The MPLINK object linker features include:

- Integration with MPASM assembler and MPLAB C17 and MPLAB C18 C compilers.

- Allows all memory areas to be defined as sections to provide link-time flexibility.

The MPLIB object librarian features include:

- Easier linking because single libraries can be included instead of many smaller files.

- Helps keep code maintainable by grouping related modules together.

- Allows libraries to be created and modules to be added, listed, replaced, deleted or extracted.

## 19.5 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC-hosted environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user-defined key press, to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and the MPLAB C18 C compilers and the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent multiproject software development tool.

## 19.6 MPLAB ICE High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB ICE universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers (MCUs). Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE in-circuit emulator system has been designed as a real-time emulation system, with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows environment were chosen to best make these features available to you, the end user.

## 19.7 ICEPIC In-Circuit Emulator

The ICEPIC low cost, in-circuit emulator is a solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X and PIC16CXXX families of 8-bit One-Time-Programmable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules, or daughter boards. The emulator is capable of emulating without target application circuitry being present.

|               |        |                                                       | Standard Operating Conditions (unless otherwise stated) Operating temperature                                                                                                                                                                                                                                                                               |      |       |       |                                                                                                           |  |

|---------------|--------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|-----------------------------------------------------------------------------------------------------------|--|

| DC CHAF       | RACTER | ISTICS                                                | $\begin{array}{rcl} -40^{\circ}\text{C} &\leq \text{Ta} \leq +125^{\circ}\text{C} \text{ for extended} \\ -40^{\circ}\text{C} &\leq \text{Ta} \leq +85^{\circ}\text{C} \text{ for industrial} \\ 0^{\circ}\text{C} &\leq \text{Ta} \leq +70^{\circ}\text{C} \text{ for commercial} \\ \end{array}$ Operating voltage VDD range as described in Section 20.1 |      |       |       |                                                                                                           |  |

| Param.<br>No. | Sym    | Characteristic                                        | Min                                                                                                                                                                                                                                                                                                                                                         | Тур† | Max   | Units | Conditions                                                                                                |  |

| D150          | Vod    | Open Drain High Voltage                               | -                                                                                                                                                                                                                                                                                                                                                           | -    | 8.5   | V     | RA2 and RA3 pins only<br>pulled up to externally<br>applied voltage                                       |  |

| _             | _      | Capacitive Loading Specs on<br>Output Pins            |                                                                                                                                                                                                                                                                                                                                                             |      |       | _     |                                                                                                           |  |

| D100          | Cosc2  | OSC2/CLKOUT pin                                       | _                                                                                                                                                                                                                                                                                                                                                           | -    | 25    | pF    | In EC or RC osc modes,<br>when OSC2 pin is outputting<br>CLKOUT. External clock is<br>used to drive OSC1. |  |

| D101          | Сю     | All I/O pins and OSC2<br>(in RC mode)                 | -                                                                                                                                                                                                                                                                                                                                                           | -    | 50    | pF    |                                                                                                           |  |

| D102          | CAD    | System Interface Bus (PORTC, PORTD and PORTE)         | _                                                                                                                                                                                                                                                                                                                                                           | _    | 50    | pF    | In Microprocessor or<br>Extended Microcontroller<br>mode                                                  |  |

|               |        | Internal Program Memory<br>Programming Specs (Note 4) |                                                                                                                                                                                                                                                                                                                                                             |      |       |       |                                                                                                           |  |

| D110          | Vpp    | Voltage on MCLR/VPP pin                               | 12.75                                                                                                                                                                                                                                                                                                                                                       | -    | 13.25 | V     | (Note 5)                                                                                                  |  |

| D111          | VDDP   | Supply voltage during programming                     | 4.75                                                                                                                                                                                                                                                                                                                                                        | 5.0  | 5.25  | V     |                                                                                                           |  |

| D112          | IPP    | Current into MCLR/VPP pin                             | _                                                                                                                                                                                                                                                                                                                                                           | 25   | 50    | mA    |                                                                                                           |  |

| D113          | IDDP   | Supply current during<br>programming                  | -                                                                                                                                                                                                                                                                                                                                                           | -    | 30    | mA    |                                                                                                           |  |

| D114          | Tprog  | Programming pulse width                               | 100                                                                                                                                                                                                                                                                                                                                                         | _    | 1000  | ms    | Terminated via internal/<br>external interrupt or a<br>RESET                                              |  |

Standard Operating Conditions (unloss otherwise stated)

Data in "Typ" column is at 5V, 25°C unless otherwise stated.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC17CXXX devices be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

**4:** These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17C7XX Programming Specifications (Literature number DS TBD).

5: The MCLR/VPP pin may be kept in this range at times other than programming, but is not recommended.

6: For TTL buffers, the better of the two specifications may be used.

Note 1: When using the Table Write for internal programming, the device temperature must be less than 40°C.

2: For In-Circuit Serial Programming (ICSP<sup>™</sup>), refer to the device programming specification.

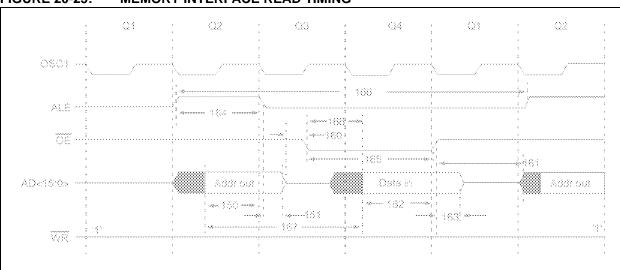

### FIGURE 20-25: MEMORY INTERFACE READ TIMING

### TABLE 20-21: MEMORY INTERFACE READ REQUIREMENTS

| Param.<br>No. | Sym      | Characteristic                                  | ;                   | Min          | Тур†    | Max          | Unit<br>s | Conditions |

|---------------|----------|-------------------------------------------------|---------------------|--------------|---------|--------------|-----------|------------|

| 150           | TadV2alL | AD15:AD0 (address) valid to                     | PIC17 <b>C</b> XXX  | 0.25Tcy - 10 | _       | —            | ns        |            |

|               |          | ALE $\downarrow$ (address setup time)           | PIC17 <b>LC</b> XXX | 0.25Tcy - 10 | —       | _            |           |            |

| 151           | TalL2adl | ALE $\downarrow$ to address out invalid         | PIC17 <b>C</b> XXX  | 5            | —       | _            | ns        |            |

|               |          | (address hold time)                             | PIC17LCXXX          | 5            | —       | _            |           |            |

| 160           | TadZ2oeL | AD15:AD0 hi-impedance to                        | PIC17 <b>C</b> XXX  | 0            | —       | _            | ns        |            |

|               |          | OE↓                                             | PIC17LCXXX          | 0            | —       | _            |           |            |

| 161           | ToeH2ad  | OE <sup>↑</sup> to AD15:AD0 driven              | PIC17 <b>C</b> XXX  | 0.25Tcy - 15 | _       | _            | ns        |            |

|               | D        |                                                 | PIC17 <b>LC</b> XXX | 0.25Tcy - 15 | —       | —            |           |            |

| 162           | TadV2oeH | Data in valid before $\overline{OE}^{\uparrow}$ | PIC17 <b>C</b> XXX  | 35           | _       | _            | ns        |            |

|               |          | (data setup time)                               | PIC17LCXXX          | 45           |         |              |           |            |

| 163           | ToeH2adl | OE <sup>↑</sup> to data in invalid              | PIC17 <b>C</b> XXX  | 0            | _       |              | ns        |            |

|               |          | (data hold time)                                | PIC17LCXXX          | 0            | _       |              |           |            |

| 164           | TalH     | ALE pulse width                                 | PIC17 <b>C</b> XXX  | —            | 0.25TCY | —            | ns        |            |

|               |          |                                                 | PIC17LCXXX          | —            | 0.25TCY | —            |           |            |

| 165           | ToeL     | OE pulse width                                  | PIC17 <b>C</b> XXX  | 0.5TCY - 35  | —       | —            | ns        |            |

|               |          |                                                 | PIC17LCXXX          | 0.5Tcy - 35  | —       | _            |           |            |

| 166           | TalH2alH | ALE↑ to ALE↑(cycle time)                        | PIC17 <b>C</b> XXX  | _            | Тсү     | _            | ns        |            |

|               |          |                                                 | PIC17LCXXX          | —            | Тсү     | —            |           |            |

| 167           | Tacc     | Address access time                             | PIC17 <b>C</b> XXX  | —            | —       | 0.75Tcy - 30 | ns        |            |

|               |          |                                                 | PIC17LCXXX          | _            | _       | 0.75Tcy - 45 |           |            |

| 168           | Toe      | Output enable access time                       | PIC17 <b>C</b> XXX  | _            | _       | 0.5Tcy - 45  | ns        |            |

|               |          | (OE low to data valid)                          | PIC17LCXXX          | _            | _       | 0.5Tcy - 75  |           |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated.

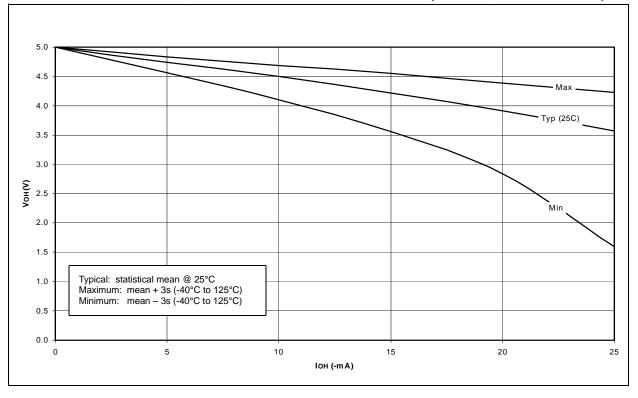

FIGURE 21-17: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 5V, -40°C TO +125°C)

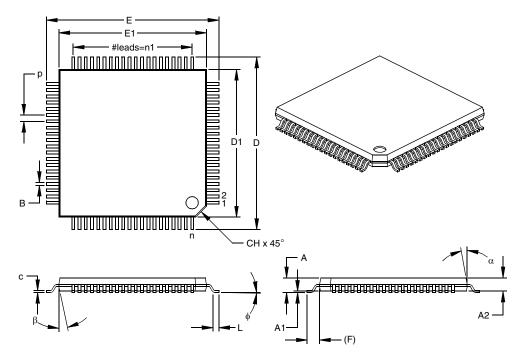

### 80-Lead Plastic Thin Quad Flatpack (PT) 12x12x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                          | Units    |      | INCHES |      | М     | ILLIMETERS | *     |

|--------------------------|----------|------|--------|------|-------|------------|-------|

| Dimensio                 | n Limits | MIN  | NOM    | MAX  | MIN   | NOM        | MAX   |

| Number of Pins           | n        |      | 80     |      |       | 80         |       |

| Pitch                    | р        |      | .020   |      |       | 0.50       |       |

| Pins per Side            | n1       |      | 20     |      |       | 20         |       |

| Overall Height           | Α        | .039 | .043   | .047 | 1.00  | 1.10       | 1.20  |

| Molded Package Thickness | A2       | .037 | .039   | .041 | 0.95  | 1.00       | 1.05  |

| Standoff §               | A1       | .002 | .004   | .006 | 0.05  | 0.10       | 0.15  |

| Foot Length              | L        | .018 | .024   | .030 | 0.45  | 0.60       | 0.75  |

| Footprint (Reference)    | (F)      |      | .039   |      |       | 1.00       |       |

| Foot Angle               | ф        | 0    | 3.5    | 7    | 0     | 3.5        | 7     |

| Overall Width            | Е        | .541 | .551   | .561 | 13.75 | 14.00      | 14.25 |

| Overall Length           | D        | .541 | .551   | .561 | 13.75 | 14.00      | 14.25 |

| Molded Package Width     | E1       | .463 | .472   | .482 | 11.75 | 12.00      | 12.25 |

| Molded Package Length    | D1       | .463 | .472   | .482 | 11.75 | 12.00      | 12.25 |

| Lead Thickness           | С        | .004 | .006   | .008 | 0.09  | 0.15       | 0.20  |

| Lead Width               | В        | .007 | .009   | .011 | 0.17  | 0.22       | 0.27  |

| Pin 1 Corner Chamfer     | CH       | .025 | .035   | .045 | 0.64  | 0.89       | 1.14  |

| Mold Draft Angle Top     | α        | 5    | 10     | 15   | 5     | 10         | 15    |

| Mold Draft Angle Bottom  | β        | 5    | 10     | 15   | 5     | 10         | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-026 Drawing No. C04-092

| Timer0                                                                             | 97                               |

|------------------------------------------------------------------------------------|----------------------------------|

| Timer1                                                                             |                                  |

| 16-bit Mode 10                                                                     | )5                               |

| Clock Source Select10                                                              | )1                               |

| On bit                                                                             | )3                               |

| Section                                                                            | )4                               |

| Timer2                                                                             |                                  |

| 16-bit Mode                                                                        | )5                               |

| Clock Source Select10                                                              |                                  |

| On bit                                                                             |                                  |

| Section                                                                            |                                  |

| Timer3                                                                             |                                  |

| Clock Source Select                                                                | 11                               |

| On bit                                                                             |                                  |

| Section                                                                            |                                  |

| Timers                                                                             | U                                |

|                                                                                    | 5                                |

| TCON3                                                                              | 13                               |

| Timing Diagrams                                                                    |                                  |

| A/D Conversion                                                                     |                                  |

| Acknowledge Sequence Timing16                                                      |                                  |

| Asynchronous Master Transmission 12                                                |                                  |

| Asynchronous Reception12                                                           |                                  |

| Back to Back Asynchronous Master Transmission 12                                   |                                  |

| Baud Rate Generator with Clock Arbitration 15                                      | 53                               |

| BRG Reset Due to SDA Collision17                                                   | '2                               |

| Bus Collision                                                                      |                                  |

| START Condition Timing17                                                           | ′1                               |

| Bus Collision During a RESTART Condition                                           |                                  |

| (Case 1)                                                                           | <b>'</b> 3                       |

| Bus Collision During a RESTART Condition                                           | -                                |

| (Case 2)                                                                           | 73                               |

| Bus Collision During a START Condition                                             | Ů                                |

| (SCL = 0)                                                                          | 20                               |

| Bus Collision During a                                                             | 2                                |

| STOP Condition17                                                                   | 7 /                              |

| Bus Collision for Transmit and Acknowledge                                         |                                  |

|                                                                                    |                                  |

| External Parallel Resonant Crystal Oscillator Circuit 1                            |                                  |

| External Program Memory Access4                                                    |                                  |

| I <sup>2</sup> C Bus Data                                                          |                                  |

| I <sup>2</sup> C Bus START/STOP bits                                               |                                  |

| I <sup>2</sup> C Master Mode First START bit Timing                                |                                  |

| I <sup>2</sup> C Master Mode Reception Timing16                                    |                                  |

| I <sup>2</sup> C Master Mode Transmission Timing16                                 |                                  |

| Interrupt (INT, TMR0 Pins)4                                                        |                                  |

| Master Mode Transmit Clock Arbitration                                             | 60                               |

| Oscillator Start-up Time2                                                          | 24                               |

| PIC17C752/756 Capture Timing25                                                     | 53                               |

| PIC17C752/756 CLKOUT and I/O25                                                     |                                  |

| PIC17C752/756 External Clock24                                                     | 9                                |

| PIC17C752/756 Memory Interface Read26                                              | 6                                |

| PIC17C752/756 Memory Interface Write                                               | 55                               |