Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 33MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 66                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 902 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 16x10b                                                                  |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c766t-33e-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| Register             | Address | Power-on Reset<br>Brown-out Reset | MCLR Reset<br>WDT Reset | Wake-up from SLEEP<br>through Interrupt |

|----------------------|---------|-----------------------------------|-------------------------|-----------------------------------------|

| Bank 4               |         | ·                                 |                         | ·                                       |

| PIR2                 | 10h     | 000- 0010                         | 000- 0010               | uuu- uuuu <b>(1)</b>                    |

| PIE2                 | 11h     | 000- 0000                         | 000- 0000               | uuu- uuuu                               |

| Unimplemented        | 12h     |                                   |                         |                                         |

| RCSTA2               | 13h     | x00-0000                          | 0000 -00u               | uuuu -uuu                               |

| RCREG2               | 14h     | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |

| TXSTA2               | 15h     | 00001x                            | 00001u                  | uuuuuu                                  |

| TXREG2               | 16h     | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |

| SPBRG2               | 17h     | 0000 0000                         | 0000 0000               | นนนน นนนน                               |

| Bank 5               |         |                                   |                         |                                         |

| DDRF                 | 10h     | 1111 1111                         | 1111 1111               | uuuu uuuu                               |

| PORTF <sup>(4)</sup> | 11h     | 0000 0000                         | 0000 0000               | uuuu uuuu                               |

| DDRG                 | 12h     | 1111 1111                         | 1111 1111               | uuuu uuuu                               |

| PORTG <sup>(4)</sup> | 13h     | xxxx 0000                         | uuuu 0000               | uuuu uuuu                               |

| ADCON0               | 14h     | 0000 -0-0                         | 0000 -0-0               | uuuu uuuu                               |

| ADCON1               | 15h     | 000- 0000                         | 000- 0000               | uuuu uuuu                               |

| ADRESL               | 16h     | XXXX XXXX                         | uuuu uuuu               | uuuu uuuu                               |

| ADRESH               | 17h     | xxxx xxxx                         | uuuu uuuu               | นนนน นนนน                               |

| Bank 6               |         |                                   |                         |                                         |

| SSPADD               | 10h     | 0000 0000                         | 0000 0000               | uuuu uuuu                               |

| SSPCON1              | 11h     | 0000 0000                         | 0000 0000               | uuuu uuuu                               |

| SSPCON2              | 12h     | 0000 0000                         | 0000 0000               | uuuu uuuu                               |

| SSPSTAT              | 13h     | 0000 0000                         | 0000 0000               | uuuu uuuu                               |

| SSPBUF               | 14h     | XXXX XXXX                         | uuuu uuuu               | นนนน นนนน                               |

| Unimplemented        | 15h     |                                   |                         |                                         |

| Unimplemented        | 16h     |                                   |                         |                                         |

| Unimplemented        | 17h     |                                   |                         |                                         |

| TABLE 5-4: | INITIALIZATION CONDITIONS FOR SPECIAL FUNCTION REGISTERS ( | (CONTINUED) |  |

|------------|------------------------------------------------------------|-------------|--|

|            |                                                            |             |  |

Legend: u = unchanged, x = unknown, - = unimplemented, read as '0', q = value depends on condition

Note 1: One or more bits in INTSTA, PIR1, PIR2 will be affected (to cause wake-up).

**2:** When the wake-up is due to an interrupt and the GLINTD bit is cleared, the PC is loaded with the interrupt vector.

**3:** See Table 5-3 for RESET value of specific condition.

4: This is the value that will be in the port output latch.

**5:** When the device is configured for Microprocessor or Extended Microcontroller mode, the operation of this port does not rely on these registers.

6: On any device RESET, these pins are configured as inputs.

### 6.4 Interrupt Operation

Global Interrupt Disable bit, GLINTD (CPUSTA<4>), enables all unmasked interrupts (if clear), or disables all interrupts (if set). Individual interrupts can be disabled through their corresponding enable bits in the INTSTA register. Peripheral interrupts need either the global peripheral enable PEIE bit disabled, or the specific peripheral enable bit disabled. Disabling the peripherals via the global peripheral enable bit, disables all peripheral interrupts. GLINTD is set on RESET (interrupts disabled).

The RETFIE instruction clears the GLINTD bit while forcing the Program Counter (PC) to the value loaded at the Top-of-Stack.

When an interrupt is responded to, the GLINTD bit is automatically set to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with the interrupt vector. There are four interrupt vectors which help reduce interrupt latency.

The peripheral interrupt vector has multiple interrupt sources. Once in the peripheral Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The peripheral interrupt flag bit(s) must be cleared in software before reenabling interrupts to avoid continuous interrupts.

The PIC17C7XX devices have four interrupt vectors. These vectors and their hardware priority are shown in Table 6-1. If two enabled interrupts occur "at the same time", the interrupt of the highest priority will be serviced first. This means that the vector address of that interrupt will be loaded into the program counter (PC).

#### TABLE 6-1: INTERRUPT VECTORS/ PRIORITIES

| Address | Vector                                       | Priority    |

|---------|----------------------------------------------|-------------|

| 0008h   | External Interrupt on RA0/<br>INT pin (INTF) | 1 (Highest) |

| 0010h   | TMR0 Overflow Interrupt<br>(T0IF)            | 2           |

| 0018h   | External Interrupt on T0CKI<br>(T0CKIF)      | 3           |

| 0020h   | Peripherals (PEIF)                           | 4 (Lowest)  |

- Note 1: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GLINTD bit.

- 2: Before disabling any of the INTSTA enable bits, the GLINTD bit should be set (disabled).

#### 6.5 RA0/INT Interrupt

The external interrupt on the RA0/INT pin is edge triggered. Either the rising edge if the INTEDG bit (T0STA<7>) is set, or the falling edge if the INTEDG bit is clear. When a valid edge appears on the RA0/INT pin, the INTF bit (INTSTA<4>) is set. This interrupt can be disabled by clearing the INTE control bit (INTSTA<0>). The INT interrupt can wake the processor from SLEEP. See Section 17.4 for details on SLEEP operation.

### 6.6 T0CKI Interrupt

The external interrupt on the RA1/T0CKI pin is edge triggered. Either the rising edge if the T0SE bit (T0STA<6>) is set, or the falling edge if the T0SE bit is clear. When a valid edge appears on the RA1/T0CKI pin, the T0CKIF bit (INTSTA<6>) is set. This interrupt can be disabled by clearing the T0CKIE control bit (INTSTA<2>). The T0CKI interrupt can wake up the processor from SLEEP. See Section 17.4 for details on SLEEP operation.

## 6.7 Peripheral Interrupt

The peripheral interrupt flag indicates that at least one of the peripheral interrupts occurred (PEIF is set). The PEIF bit is a read only bit and is a bit wise OR of all the flag bits in the PIR registers AND'd with the corresponding enable bits in the PIE registers. Some of the peripheral interrupts can wake the processor from SLEEP. See Section 17.4 for details on SLEEP operation.

## 6.8 Context Saving During Interrupts

During an interrupt, only the returned PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt; e.g. WREG, ALUSTA and the BSR registers. This requires implementation in software.

Example 6-2 shows the saving and restoring of information for an Interrupt Service Routine. This is for a simple interrupt scheme, where only one interrupt may occur at a time (no interrupt nesting). The SFRs are stored in the non-banked GPR area.

Example 6-2 shows the saving and restoring of information for a more complex Interrupt Service Routine. This is useful where nesting of interrupts is required. A maximum of 6 levels can be done by this example. The BSR is stored in the non-banked GPR area, while the other registers would be stored in a particular bank. Therefore, 6 saves may be done with this routine (since there are 6 non-banked GPR registers). These routines require a dedicated indirect addressing register, FSR0, to be selected for this.

The PUSH and POP code segments could either be in each Interrupt Service Routine, or could be subroutines that were called. Depending on the application, other registers may also need to be saved.

#### EXAMPLE 6-1: SAVING STATUS AND WREG IN RAM (SIMPLE)

; The addresses that are used to store the CPUSTA and WREG values must be in the data memory ; address range of 1Ah - 1Fh. Up to 6 locations can be saved and restored using the MOVFP ; instruction. This instruction neither affects the status bits, nor corrupts the WREG register. UNBANK1 ; Address for 1st location to save EQU 0x01A UNBANK2 EQU 0x01B ; Address for 2nd location to save UNBANK3 EQU 0x01C ; Address for 3rd location to save UNBANK4 0x01D EOU ; Address for 4th location to save UNBANK5 EQU 0x01E ; Address for 5th location to save (Label Not used in program) ; UNBANK6 EQU 0x01F ; Address for 6th location to save (Label Not used in program) ; ; ; At Interrupt Vector Address ٠ ALUSTA, UNBANK1 PUSH MOVFP ; Push ALUSTA value MOVFP BSR, UNBANK2 ; Push BSR value MOVFP WREG, UNBANK3 ; Push WREG value MOVFP PCLATH, UNBANK4 ; Push PCLATH value ; ; Interrupt Service Routine (ISR) code : ; UNBANK4, PCLATH ; Restore PCLATH value POP MOVFP UNBANK3, WREG ; Restore WREG value MOVFP MOVFP UNBANK2, BSR ; Restore BSR value MOVFP UNBANK1, ALUSTA ; Restore ALUSTA value ; RETFIE ; Return from interrupt (enable interrupts)

| Address | Name                 | Bit 7        | Bit 6           | Bit 5          | Bit 4        | Bit 3        | Bit 2       | Bit 1       | Bit 0       | Value on<br>POR,<br>BOR | MCLR,<br>WDT |

|---------|----------------------|--------------|-----------------|----------------|--------------|--------------|-------------|-------------|-------------|-------------------------|--------------|

| Bank 2  |                      |              |                 |                |              |              |             |             |             |                         | •            |

| 10h     | TMR1                 | Timer1's R   | ner1's Register |                |              |              |             |             |             | XXXX XXXX               | uuuu uuuu    |

| 11h     | TMR2                 | Timer2's R   | legister        |                |              |              |             |             |             | xxxx xxxx               | uuuu uuuu    |

| 12h     | TMR3L                | Timer3's R   | egister; Lov    | v Byte         |              |              |             |             |             | XXXX XXXX               | uuuu uuuu    |

| 13h     | TMR3H                |              | egister; Hig    | -              |              |              |             |             |             | XXXX XXXX               | uuuu uuuu    |

| 14h     | PR1                  |              | eriod Regis     |                |              |              |             |             |             | XXXX XXXX               | uuuu uuuu    |

| 15h     | PR2                  |              | eriod Regis     |                |              |              |             |             |             | XXXX XXXX               | uuuu uuuu    |

| 16h     | PR3L/CA1L            |              | -               |                | e/Capture1 F | -            | -           |             |             | XXXX XXXX               | uuuu uuuu    |

| 17h     | PR3H/CA1H            | Timer3's P   | eriod Regis     | ter - High By  | te/Capture1  | Register; Hi | gh Byte     |             |             | XXXX XXXX               | uuuu uuuu    |

| Bank 3  |                      |              |                 |                |              |              |             |             |             |                         |              |

| 10h     | PW1DCL               | DC1          | DC0             |                |              |              | —           |             | —           | xx                      | uu           |

| 11h     | PW2DCL               | DC1          | DC0             | TM2PW2         | _            |              | —           | —           | —           | xx0                     | uu0          |

| 12h     | PW1DCH               | DC9          | DC8             | DC7            | DC6          | DC5          | DC4         | DC3         | DC2         | XXXX XXXX               | uuuu uuuu    |

| 13h     | PW2DCH               | DC9          | DC8             | DC7            | DC6          | DC5          | DC4         | DC3         | DC2         | XXXX XXXX               | uuuu uuuu    |

| 14h     | CA2L                 | Capture2 L   | ,               |                |              |              |             |             |             | XXXX XXXX               | uuuu uuuu    |

| 15h     | CA2H                 | Capture2 H   | ° ,             | 01/55/         | 01/550       | 710          |             |             |             | XXXX XXXX               | uuuu uuuu    |

| 16h     | TCON1                | CA2ED1       | CA2ED0          | CA1ED1         | CA1ED0       | T16          | TMR3CS      | TMR2CS      | TMR1CS      | 0000 0000               | 0000 0000    |

| 17h     | TCON2                | CA2OVF       | CA10VF          | PWM2ON         | PWM10N       | CA1/PR3      | TMR3ON      | TMR2ON      | TMR10N      | 0000 0000               | 0000 0000    |

| Bank 4  |                      |              |                 |                |              |              |             |             |             |                         |              |

| 10h     | PIR2                 | SSPIF        | BCLIF           | ADIF           | —            | CA4IF        | CA3IF       | TX2IF       | RC2IF       | 000- 0010               | 000- 0010    |

| 11h     | PIE2                 | SSPIE        | BCLIE           | ADIE           |              | CA4IE        | CA3IE       | TX2IE       | RC2IE       | 000- 0000               | 000- 0000    |

| 12h     | Unimplemented        |              | _               | _              |              | _            | _           | _           | _           |                         |              |

| 13h     | RCSTA2               | SPEN         | RX9             | SREN           | CREN         | _            | FERR        | OERR        | RX9D        | 0000 -00x               | 0000 -00u    |

| 14h     | RCREG2               | Serial Port  | Receive Re      | egister for US | SART2        |              |             |             |             | xxxx xxxx               | uuuu uuuu    |

| 15h     | TXSTA2               | CSRC         | TX9             | TXEN           | SYNC         | _            | _           | TRMT        | TX9D        | 00001x                  | 00001u       |

| 16h     | TXREG2               | Serial Port  | Transmit R      | egister for U  | SART2        |              |             |             |             | xxxx xxxx               | uuuu uuuu    |

| 17h     | SPBRG2               | Baud Rate    | Generator       | for USART2     |              |              |             |             |             | 0000 0000               | 0000 0000    |

| Bank 5: |                      |              |                 |                |              |              |             |             |             |                         |              |

| 10h     | DDRF                 | Data Direc   | tion Registe    | er for PORTF   |              |              |             |             |             | 1111 1111               | 1111 1111    |

| 11h     | PORTF <sup>(4)</sup> | RF7/<br>AN11 | RF6/<br>AN10    | RF5/<br>AN9    | RF4/<br>AN8  | RF3/<br>AN7  | RF2/<br>AN6 | RF1/<br>AN5 | RF0/<br>AN4 | 0000 0000               | 0000 0000    |

| 12h     | DDRG                 |              |                 | er for PORTO   |              | ,            | 7           | ,           | ,           | 1111 1111               | 1111 1111    |

|         | PORTG <sup>(4)</sup> | RG7/         | RG6/            | RG5/           | RG4/         | RG3/         | RG2/        | RG1/        | RG0/        |                         |              |

| 13h     | PORIG                | TX2/CK2      | RX2/DT2         | PWM3           | CAP3         | AN0          | AN1         | AN2         | AN3         | xxxx 0000               | uuuu 0000    |

| 14h     | ADCON0               | CHS3         | CHS2            | CHS1           | CHS0         | —            | GO/DONE     | _           | ADON        | 0000 -0-0               | 0000 -0-0    |

| 15h     | ADCON1               | ADCS1        | ADCS0           | ADFM           | —            | PCFG3        | PCFG2       | PCFG1       | PCFG0       | 000- 0000               | 000- 0000    |

| 16h     | ADRESL               | A/D Result   | t Register Lo   | ow Byte        |              | -            |             |             | •           | xxxx xxxx               | uuuu uuuu    |

| 17h     | ADRESH               | A/D Result   | t Register H    | igh Byte       |              |              |             |             |             | xxxx xxxx               | uuuu uuuu    |

| TABLE 7-3: | SPECIAL FUNCTION REGISTERS | (CONTINUED) | ) |

|------------|----------------------------|-------------|---|

|            |                            |             |   |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0', q = value depends on condition.

Shaded cells are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<15:8> whose contents are updated from, or transferred to, the upper byte of the program counter.

2: The TO and PD status bits in CPUSTA are not affected by a MCLR Reset.

3: Bank 8 and associated registers are only implemented on the PIC17C76X devices.

4: This is the value that will be in the port output latch.

5: When the device is configured for Microprocessor or Extended Microcontroller mode, the operation of this port does not rely on these registers.

6: On any device RESET, these pins are configured as inputs.

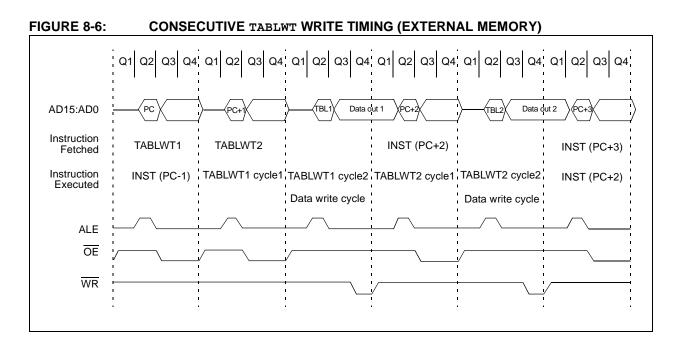

### 8.1 Table Writes to Internal Memory

A table write operation to internal memory causes a long write operation. The long write is necessary for programming the internal EPROM. Instruction execution is halted while in a long write cycle. The long write will be terminated by any enabled interrupt. To ensure that the EPROM location has been well programmed, a minimum programming time is required (see specification #D114). Having only one interrupt enabled to terminate the long write ensures that no unintentional interrupts will prematurely terminate the long write.

The sequence of events for programming an internal program memory location should be:

- 1. Disable all interrupt sources, except the source to terminate EPROM program write.

- 2. Raise MCLR/VPP pin to the programming voltage.

- 3. Clear the WDT.

- 4. Do the table write. The interrupt will terminate the long write.

- 5. Verify the memory location (table read).

- Note 1: Programming requirements must be met. See timing specification in electrical specifications for the desired device. Violating these specifications (including temperature) may result in EPROM locations that are not fully programmed and may lose their state over time.

- 2: If the VPP requirement is not met, the table write is a 2-cycle write and the program memory is unchanged.

### 8.1.1 TERMINATING LONG WRITES

An interrupt source or RESET are the only events that terminate a long write operation. Terminating the long write from an interrupt source requires that the interrupt enable and flag bits are set. The GLINTD bit only enables the vectoring to the interrupt address.

If the TOCKI, RA0/INT, or TMR0 interrupt source is used to terminate the long write, the interrupt flag of the highest priority enabled interrupt, will terminate the long write and automatically be cleared.

- **Note 1:** If an interrupt is pending, the TABLWT is aborted (a NOP is executed). The highest priority pending interrupt, from the TOCKI, RA0/INT, or TMR0 sources that is enabled, has its flag cleared.

- 2: If the interrupt is not being used for the program write timing, the interrupt should be disabled. This will ensure that the interrupt is not lost, nor will it terminate the long write prematurely.

If a peripheral interrupt source is used to terminate the long write, the interrupt enable and flag bits must be set. The interrupt flag will not be automatically cleared upon the vectoring to the interrupt vector address.

The GLINTD bit determines whether the program will branch to the interrupt vector when the long write is terminated. If GLINTD is clear, the program will vector, if GLINTD is set, the program will not vector to the interrupt address.

| Interrupt<br>Source | GLINTD | Enable<br>Bit | Flag<br>Bit | Action                                                                                         |

|---------------------|--------|---------------|-------------|------------------------------------------------------------------------------------------------|

| RA0/INT,            | 0      | 1             | 1           | Terminate long table write (to internal program memory),                                       |

| TMR0,               |        |               |             | branch to interrupt vector (branch clears flag bit).                                           |

| TOCKI               | 0      | 1             | 0           | None.                                                                                          |

|                     | 1      | 0             | x           | None.                                                                                          |

|                     | 1      | 1             | 1           | Terminate long table write, do not branch to interrupt vector (flag is automatically cleared). |

| Peripheral          | 0      | 1             | 1           | Terminate long table write, branch to interrupt vector.                                        |

|                     | 0      | 1             | 0           | None.                                                                                          |

|                     | 1      | 0             | x           | None.                                                                                          |

|                     | 1      | 1             | 1           | Terminate long table write, do not branch to interrupt vector (flag remains set).              |

#### TABLE 8-1: INTERRUPT - TABLE WRITE INTERACTION

Example 9-4 shows the sequence to do a 16 x 16 signed multiply. Equation 9-2 shows the algorithm used. The 32-bit result is stored in four registers, RES3:RES0. To account for the sign bits of the arguments, each argument pairs most significant bit (MSb) is tested and the appropriate subtractions are done.

#### EQUATION 9-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:RES0                                                     |   |

|---------------------------------------------------------------|---|

| $= ARG1H:ARG1L \bullet ARG2H:ARG2L$                           |   |

| $= (ARG1H \bullet ARG2H \bullet 2^{16})$                      | + |

| $(ARG1H \bullet ARG2L \bullet 2^8)$                           | + |

| $(ARG1L \bullet ARG2H \bullet 2^8)$                           | + |

| $(ARG1L \bullet ARG2L)$                                       | + |

| $(-1 \bullet ARG2H < 7 > \bullet ARG1H:ARG1L \bullet 2^{16})$ | + |

| $(-1 \bullet ARG1H < 7 > \bullet ARG2H:ARG2L \bullet 2^{16})$ |   |

|                                                               |   |

#### EXAMPLE 9-4: 16 x 16 SIGNED MULTIPLY ROUTINE

|    | MOVFP    | ARG1L, WREG            |   |                  |

|----|----------|------------------------|---|------------------|

|    | MULWF    |                        | ; | ARG1L * ARG2L -> |

|    |          |                        |   | PRODH: PRODL     |

|    | MOVPF    | PRODH, RES1            |   |                  |

|    |          | PRODL, RESO            |   |                  |

| ;  |          |                        | ' |                  |

| '  | MOVFP    | ARG1H, WREG            |   |                  |

|    | MULWF    | ARG2H                  |   | ARG1H * ARG2H -> |

|    |          |                        |   | PRODH: PRODL     |

|    | MOVPF    | PRODH, RES3            |   | 1110211111022    |

|    |          | PRODL, RES2            |   |                  |

| ;  |          | 111022, 11202          | ' |                  |

| '  | MOVFP    | ARG1L, WREG            |   |                  |

|    | MULWF    |                        |   | ARG1L * ARG2H -> |

|    |          |                        | ; |                  |

|    | MOVFP    | PRODL, WREG            |   | I KODII I KODII  |

|    | ADDWF    |                        |   | Add cross        |

|    | MOVFP    | PRODH, WREG            |   |                  |

|    |          |                        |   | products         |

|    | CLRF     |                        | ; |                  |

|    |          | WREG, F<br>RES3, F     |   |                  |

|    | ADDWFC   | RESS, F                | ; |                  |

| ;  | MOVFP    | ADCIN MDEC             |   |                  |

|    |          | ARG1H, WREG            |   |                  |

|    | MULWF    | ARG2L                  |   | ARG1H * ARG2L -> |

|    | MOUTED   |                        |   | PRODH: PRODL     |

|    | MOVFP    | PRODL, WREG<br>RES1, F |   |                  |

|    |          |                        |   |                  |

|    | MOVFP    |                        |   | products         |

|    | ADDWFC   | RES2, F                | ; |                  |

|    | CLRF     | WREG, F                | ; |                  |

|    | ADDWFC   | RES3, F                | ; |                  |

| ;  | DEFIC    |                        |   |                  |

|    |          | AKGZA, /               | ; | ARG2H:ARG2L neg? |

|    | GOTO     |                        |   | no, check ARG1   |

|    | MOVFP    | ARG1L, WREG            | ; |                  |

|    | SUBWF    | RES2                   | ; |                  |

|    | MOVFP    | ARG1H, WREG            | ; |                  |

|    | SUBWFB   | RES3                   |   |                  |

| ;  | CNI ADC1 |                        |   |                  |

| SI | GN_ARG1  |                        |   | ADCILLADCIL DC-2 |

|    | BTFSS    | CONT_CODE              |   | ARG1H:ARG1L neg? |

|    | GOTO     |                        |   | no, done         |

|    | MOVFP    | ARG2L, WREG            | ; |                  |

|    | SUBWF    | RES2                   | ; |                  |

|    | MOVFP    | ARG2H, WREG            | ; |                  |

|    | SUBWFB   | KES3                   |   |                  |

| ;  |          |                        |   |                  |

| CO | NT_CODE  |                        |   |                  |

|    | :        |                        |   |                  |

| 1  |          |                        |   |                  |

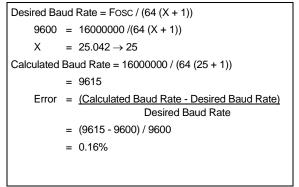

### 14.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. Table 14-2 shows the formula for computation of the baud rate for different USART modes. These only apply when the USART is in Synchronous Master mode (internal clock) and Asynchronous mode.

Given the desired baud rate and Fosc, the nearest integer value between 0 and 255 can be calculated using the formula below. The error in baud rate can then be determined.

### TABLE 14-2: BAUD RATE FORMULA

| SYNC | Mode         | Baud Rate      |

|------|--------------|----------------|

| 0    | Asynchronous | Fosc/(64(X+1)) |

| 1    | Synchronous  | Fosc/(4(X+1))  |

X = value in SPBRG (0 to 255)

Example 14-1 shows the calculation of the baud rate error for the following conditions:

Fosc = 16 MHz Desired Baud Rate = 9600 SYNC = 0

#### EXAMPLE 14-1: CALCULATING BAUD RATE ERROR

Writing a new value to the SPBRG, causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

#### Effects of Reset

After any device RESET, the SPBRG register is cleared. The SPBRG register will need to be loaded with the desired value after each RESET.

|        | Address     | Name   | Bit 7    | Bit 6                        | Bit 5       | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | MCLR, WDT |

|--------|-------------|--------|----------|------------------------------|-------------|-------|-------|-------|-------|-------|-------------------------|-----------|

|        | 13h, Bank 0 | RCSTA1 | SPEN     | RX9                          | SREN        | CREN  | —     | FERR  | OERR  | RX9D  | 0000 -00x               | 0000 -00u |

| USART  | 15h, Bank 0 | TXSTA1 | CSRC     | TX9                          | TXEN        | SYNC  | —     | _     | TRMT  | TX9D  | 00001x                  | 00001u    |

| ns     | 17h, Bank 0 | SPBRG1 | Baud Rat | Baud Rate Generator Register |             |       |       |       |       |       | 0000 0000               | 0000 0000 |

| 2      | 13h, Bank 4 | RCSTA2 | SPEN     | RX9                          | SREN        | CREN  | _     | FERR  | OERR  | RX9D  | 0000 -00x               | 0000 -00u |

| USART2 | 15h, Bank 4 | TXSTA2 | CSRC     | TX9                          | TXEN        | SYNC  | _     |       | TRMT  | TX9D  | 00001x                  | 00001u    |

| N      | 17h, Bank 4 | SPBRG2 | Baud Rat | e Genera                     | tor Registe | r     |       |       |       |       | 0000 0000               | 0000 0000 |

## TABLE 14-3: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Baud Rate Generator.

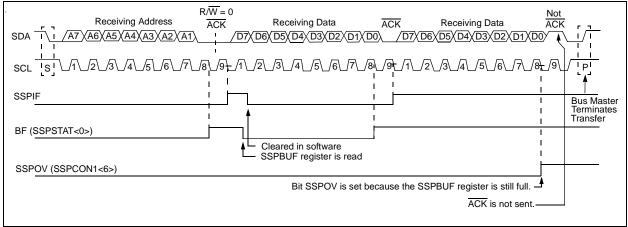

#### REGISTER 15-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS: 13h, BANK 6) R/W-0 R/W-0 R-0 R-0 R-0 R-0 R-0 R-0 SMP CKE D/A Р S R/W UA BF bit 7 bit 0 bit 7 SMP: Sample bit SPI Master mode: 1 = Input data sampled at end of data output time 0 = Input data sampled at middle of data output time SPI Slave mode: SMP must be cleared when SPI is used in Slave mode In I<sup>2</sup>C Master or Slave mode: 1 = Slew rate control disabled for Standard Speed mode (100 kHz and 1 MHz) 0 = Slew rate control enabled for High Speed mode (400 kHz) bit 6 CKE: SPI Clock Edge Select (Figure 15-6, Figure 15-8 and Figure 15-9) CKP = 0: 1 = Data transmitted on rising edge of SCK 0 = Data transmitted on falling edge of SCK CKP = 1: 1 = Data transmitted on falling edge of SCK 0 = Data transmitted on rising edge of SCK bit 5 D/A: Data/Address bit (I<sup>2</sup>C mode only) 1 = Indicates that the last byte received or transmitted was data 0 = Indicates that the last byte received or transmitted was address P: STOP bit bit 4 $(l^2C \text{ mode only})$ . This bit is cleared when the MSSP module is disabled, SSPEN is cleared.) 1 = Indicates that a STOP bit has been detected last (this bit is '0' on RESET) 0 = STOP bit was not detected last bit 3 S: START bit (I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.) 1 = Indicates that a START bit has been detected last (this bit is '0' on RESET) 0 = START bit was not detected last **R/W**: Read/Write bit Information (I<sup>2</sup>C mode only) bit 2 This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to the next START bit, STOP bit, or not ACK bit. In I<sup>2</sup>C Slave mode: 1 = Read 0 = WriteIn I<sup>2</sup>C Master mode: 1 = Transmit is in progress 0 = Transmit is not in progress Or'ing this bit with SEN, RSEN, PEN, RCEN, or ACKEN will indicate if the MSSP is in IDLE mode. bit 1 **UA**: Update Address (10-bit I<sup>2</sup>C mode only) 1 = Indicates that the user needs to update the address in the SSPADD register 0 = Address does not need to be updated bit 0 BF: Buffer Full Status bit Receive (SPI and I<sup>2</sup>C modes) 1 = Receive complete, SSPBUF is full 0 = Receive not complete, SSPBUF is empty Transmit (I<sup>2</sup>C mode only) 1 = Data transmit in progress (does not include the ACK and STOP bits), SSPBUF is full 0 = Data transmit complete (does not include the $\overline{ACK}$ and STOP bits), SSPBUF is empty Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

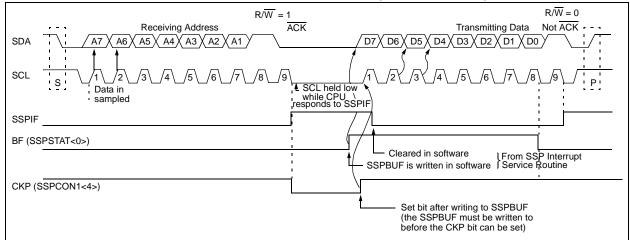

#### 15.2.1.3 Slave Transmission

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The  $\overline{ACK}$  pulse will be sent on the ninth bit, and the SCL pin is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then SCL pin should be enabled by setting bit CKP (SSPCON1<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 15-13). An SSP interrupt is generated for each data transfer byte. The SSPIF flag bit must be cleared in software, and the SSPSTAT register is used to determine the status of the byte transfer. The SSPIF flag bit is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the ACK pulse from the masterreceiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not ACK), then the data transfer is complete. When the not ACK is latched by the slave, the slave logic is reset and the slave then monitors for another occurrence of the START bit. If the SDA line was low (ACK), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, the SCL pin should be enabled by setting the CKP bit.

#### FIGURE 15-12: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

### FIGURE 15-13: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

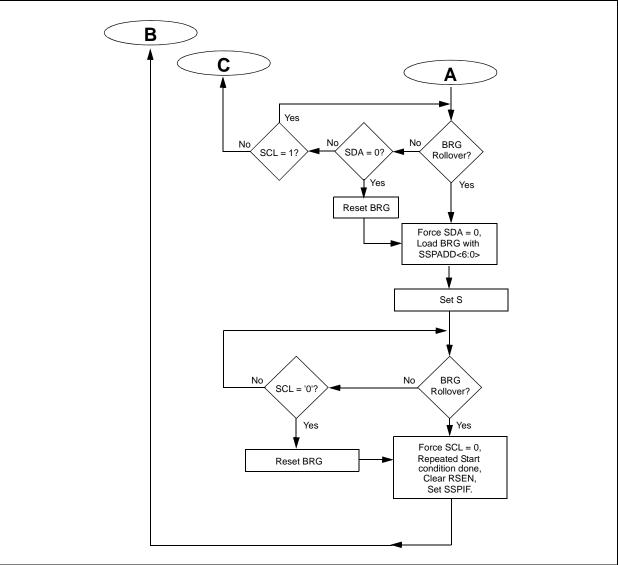

Table 18-2 lists the instructions recognized by the MPASM assembler.

**Note 1:** Any unused opcode is Reserved. Use of any reserved opcode may cause unexpected operation.

All instruction examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

To represent a binary number:

0000 0100b

where b signifies a binary string.

## FIGURE 18-1: GENERAL FORMAT FOR INSTRUCTIONS

## 18.1 Special Function Registers as Source/Destination

The PIC17C7XX's orthogonal instruction set allows read and write of all file registers, including special function registers. There are some special situations the user should be aware of:

### 18.1.1 ALUSTA AS DESTINATION

If an instruction writes to ALUSTA, the Z, C, DC and OV bits may be set or cleared as a result of the instruction and overwrite the original data bits written. For example, executing CLRF ALUSTA will clear register ALUSTA and then set the Z bit leaving 0000 0100b in the register.

#### 18.1.2 PCL AS SOURCE OR DESTINATION

Read, write or read-modify-write on PCL may have the following results:

| Read PC:           | $PCH \to PCLATH;  PCL \to dest$                                                              |

|--------------------|----------------------------------------------------------------------------------------------|

| Write PCL:         | PCLATH $\rightarrow$ PCH;<br>8-bit destination value $\rightarrow$ PCL                       |

| Read-Modify-Write: | PCL $\rightarrow$ ALU operand<br>PCLATH $\rightarrow$ PCH;<br>8-bit result $\rightarrow$ PCL |

Where PCH = program counter high byte (not an addressable register), PCLATH = Program counter high holding latch, dest = destination, WREG or f.

#### 18.1.3 BIT MANIPULATION

All bit manipulation instructions are done by first reading the entire register, operating on the selected bit and writing the result back (read-modify-write (R-M-W)). The user should keep this in mind when operating on some special function registers, such as ports.

| Note: | Status bits that are manipulated by the        |

|-------|------------------------------------------------|

|       | device (including the interrupt flag bits) are |

|       | set or cleared in the Q1 cycle. So, there is   |

|       | no issue on doing R-M-W instructions on        |

|       | registers which contain these bits             |

| Mnemonio | C,      | Description                                   | Quality |      | 16-bit ( | Opcode | •    | Status    | Nate  |

|----------|---------|-----------------------------------------------|---------|------|----------|--------|------|-----------|-------|

| Operands |         | Description                                   | Cycles  | MSb  | MSb      |        | LSb  | Affected  | Notes |

| TSTFSZ   | f       | Test f, skip if 0                             | 1 (2)   | 0011 | 0011     | ffff   | ffff | None      | 6,8   |

| XORWF    | f,d     | Exclusive OR WREG with f                      | 1       | 0000 | 110d     | ffff   | ffff | Z         |       |

| BIT-ORIE | NTED FI | LE REGISTER OPERATIONS                        | 1       |      |          |        |      |           | 1     |

| BCF      | f,b     | Bit Clear f                                   | 1       | 1000 | 1bbb     | ffff   | ffff | None      |       |

| BSF      | f,b     | Bit Set f                                     | 1       | 1000 | 0bbb     | ffff   | ffff | None      |       |

| BTFSC    | f,b     | Bit test, skip if clear                       | 1 (2)   | 1001 | 1bbb     | ffff   | ffff | None      | 6,8   |

| BTFSS    | f,b     | Bit test, skip if set                         | 1 (2)   | 1001 | 0bbb     | ffff   | ffff | None      | 6,8   |

| BTG      | f,b     | Bit Toggle f                                  | 1       | 0011 | 1bbb     | ffff   | ffff | None      |       |

| LITERAL  | AND CO  | NTROL OPERATIONS                              | 1       |      |          |        |      |           | 1     |

| ADDLW    | k       | ADD literal to WREG                           | 1       | 1011 | 0001     | kkkk   | kkkk | OV,C,DC,Z |       |

| ANDLW    | k       | AND literal with WREG                         | 1       | 1011 | 0101     | kkkk   | kkkk | Z         |       |

| CALL     | k       | Subroutine Call                               | 2       | 111k | kkkk     | kkkk   | kkkk | None      | 7     |

| CLRWDT   | _       | Clear Watchdog Timer                          | 1       | 0000 | 0000     | 0000   | 0100 | TO, PD    |       |

| GOTO     | k       | Unconditional Branch                          | 2       | 110k | kkkk     | kkkk   | kkkk | None      | 7     |

| IORLW    | k       | Inclusive OR literal with WREG                | 1       | 1011 | 0011     | kkkk   | kkkk | Z         |       |

| LCALL    | k       | Long Call                                     | 2       | 1011 | 0111     | kkkk   | kkkk | None      | 4,7   |

| MOVLB    | k       | Move literal to low nibble in BSR             | 1       | 1011 | 1000     | uuuu   | kkkk | None      |       |

| MOVLR    | k       | Move literal to high nibble in BSR            | 1       | 1011 | 101x     | kkkk   | uuuu | None      |       |

| MOVLW    | k       | Move literal to WREG                          | 1       | 1011 | 0000     | kkkk   | kkkk | None      |       |

| MULLW    | k       | Multiply literal with WREG                    | 1       | 1011 | 1100     | kkkk   | kkkk | None      |       |

| RETFIE   | _       | Return from interrupt (and enable interrupts) | 2       | 0000 | 0000     | 0000   | 0101 | GLINTD    | 7     |

| RETLW    | k       | Return literal to WREG                        | 2       | 1011 | 0110     | kkkk   | kkkk | None      | 7     |

| RETURN   | _       | Return from subroutine                        | 2       | 0000 | 0000     | 0000   | 0010 | None      | 7     |

| SLEEP    | _       | Enter SLEEP mode                              | 1       | 0000 | 0000     | 0000   | 0011 | TO, PD    |       |

| SUBLW    | k       | Subtract WREG from literal                    | 1       | 1011 | 0010     | kkkk   | kkkk | OV,C,DC,Z |       |

| XORLW    | k       | Exclusive OR literal with WREG                | 1       | 1011 | 0100     | kkkk   | kkkk | Z         |       |

#### TABLE 18-2: PIC17CXXX INSTRUCTION SET (CONTINUED)

Legend: Refer to Table 18-1 for opcode field descriptions.

**Note 1:** 2's Complement method.

2: Unsigned arithmetic.

**3:** If s = '1', only the file is affected: If s = '0', both the WREG register and the file are affected; If only the Working register (WREG) is required to be affected, then f = WREG must be specified.

4: During an LCALL, the contents of PCLATH are loaded into the MSB of the PC and kkkk kkkk is loaded into the LSB of the PC (PCL).

5: Multiple cycle instruction for EPROM programming when table pointer selects internal EPROM. The instruction is terminated by an interrupt event. When writing to external program memory, it is a two-cycle instruction.

6: Two-cycle instruction when condition is true, else single cycle instruction.

7: Two-cycle instruction except for TABLRD to PCL (program counter low byte), in which case it takes 3 cycles.

8: A "skip" means that instruction fetched during execution of current instruction is not executed, instead a NOP is executed.

| BTF                                                                                                                                                                                                                         | SS            | Bit Test, skip if Set             |              |                      |                                |                         |                                 |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------|--------------|----------------------|--------------------------------|-------------------------|---------------------------------|--|--|

| Synt                                                                                                                                                                                                                        | ax:           | [ label ]                         | ΒT           | FSS f,t              | )                              |                         |                                 |  |  |

| Ope                                                                                                                                                                                                                         | rands:        | $0 \le f \le 12$<br>$0 \le b < 7$ |              |                      |                                |                         |                                 |  |  |

| Ope                                                                                                                                                                                                                         | ration:       | skip if (f<                       | <b></b>      | -) = 1               |                                |                         |                                 |  |  |

| Statu                                                                                                                                                                                                                       | us Affected:  | None                              |              |                      |                                |                         |                                 |  |  |

| Enco                                                                                                                                                                                                                        | oding:        | 1001                              |              | 0bbb                 | fff                            | f                       | ffff                            |  |  |

| Description:<br>If bit 'b' in register 'f' is 1, th<br>instruction is skipped.<br>If bit 'b' is 1, then the next<br>fetched during the current<br>cution is discarded and a M<br>instead, making this a two<br>instruction. |               |                                   |              |                      | next ir<br>rrent ir<br>id a NC | nstru<br>nstru<br>DP is | ction<br>ction exe-<br>executed |  |  |

| Word                                                                                                                                                                                                                        | ds:           | 1                                 |              |                      |                                |                         |                                 |  |  |

| Cycl                                                                                                                                                                                                                        | es:           | 1(2)                              |              |                      |                                |                         |                                 |  |  |

| QC                                                                                                                                                                                                                          | cle Activity: | . ,                               |              |                      |                                |                         |                                 |  |  |

|                                                                                                                                                                                                                             | Q1            | Q2                                |              | Q3                   | 3                              |                         | Q4                              |  |  |

|                                                                                                                                                                                                                             | Decode        | Read<br>register 'f               | e,           | Proce<br>Data        |                                |                         | No<br>peration                  |  |  |

| lf ski                                                                                                                                                                                                                      | p:            |                                   |              |                      |                                |                         |                                 |  |  |

|                                                                                                                                                                                                                             | Q1            | Q2                                |              | Q3                   |                                |                         | Q4                              |  |  |

|                                                                                                                                                                                                                             | No            | No                                |              | No                   |                                |                         | No                              |  |  |

|                                                                                                                                                                                                                             | operation     | operation                         | 1            | operat               | tion                           | op                      | peration                        |  |  |

| <u>Exar</u>                                                                                                                                                                                                                 | <u>nple</u> : | HERE<br>FALSE<br>TRUE             | B1<br>:<br>: | FSS                  | FLAG                           | ,1                      |                                 |  |  |

| Before Instruction<br>PC = add                                                                                                                                                                                              |               |                                   |              | ress (HE             | RE)                            |                         |                                 |  |  |

| After Instruction<br>If FLAG<1><br>PC<br>If FLAG<1><br>PC                                                                                                                                                                   |               | 1> = 0<br>= a<br>1> = 1           | ;            | ress (FA<br>ress (TR |                                |                         |                                 |  |  |

| BTG                    | Bit roggi                            | Bit Toggle f      |      |          |                   |  |  |  |

|------------------------|--------------------------------------|-------------------|------|----------|-------------------|--|--|--|

| Syntax:                | [ <i>label</i> ] B                   | TG f,b            |      |          |                   |  |  |  |

| Operands:              | $0 \le f \le 255$<br>$0 \le b < 7$   |                   |      |          |                   |  |  |  |

| Operation:             | $(\overline{f} < b >) \rightarrow ($ | (f <b>)</b>       |      |          |                   |  |  |  |

| Status Affected:       | None                                 |                   |      |          |                   |  |  |  |

| Encoding:              | 0011                                 | 1bbb              | ff   | ff       | ffff              |  |  |  |

| Description:           | Bit 'b' in da<br>inverted.           | ta memory         | loca | ition 'f | ' is              |  |  |  |

| Words:                 | 1                                    |                   |      |          |                   |  |  |  |

| Cycles:                | 1                                    |                   |      |          |                   |  |  |  |

| Q Cycle Activity:      |                                      |                   |      |          |                   |  |  |  |

| Q1                     | Q2                                   | Q3                |      | (        | ຊ4                |  |  |  |

| Decode                 | Read<br>register 'f'                 | Proces<br>Data    | S    |          | /rite<br>ster 'f' |  |  |  |

| Evenale                |                                      |                   |      |          |                   |  |  |  |

| Example:               | BTG I                                | PORTC,            | 4    |          |                   |  |  |  |

| Before Instru<br>PORTC |                                      | 0101 <b>[0x75</b> | 5]   |          |                   |  |  |  |

| After Instruction:     |                                      |                   |      |          |                   |  |  |  |

After Instruction: PORTC = 0110 0101 [0x65]

| NEG         | W                     | Negate W                                                                |                                    |                             |                                                        |  |  |  |

|-------------|-----------------------|-------------------------------------------------------------------------|------------------------------------|-----------------------------|--------------------------------------------------------|--|--|--|

| Synt        | ax:                   | [ <i>label</i> ] N                                                      | EGW                                | f,s                         |                                                        |  |  |  |

| Ope         | rands:                | $0 \le f \le 255$<br>s $\in [0,1]$                                      | 5                                  |                             |                                                        |  |  |  |

| Ope         | ration:               | WREG + 2<br>WREG + 2                                                    |                                    |                             |                                                        |  |  |  |

| Statu       | us Affected:          | OV, C, DC                                                               | ;, Z                               |                             |                                                        |  |  |  |

| Enco        | oding:                | 0010                                                                    | 110s                               | ffff                        | ffff                                                   |  |  |  |

| Des         | cription:             | WREG is ne<br>ment. If 's' i<br>WREG and<br>'s' is 1, the<br>memory loc | s 0, the r<br>data me<br>result is | result is pla<br>emory loca | aced in<br>tion 'f'. If                                |  |  |  |

| Wor         | ds:                   | 1                                                                       | 1                                  |                             |                                                        |  |  |  |

| Cycl        | es:                   | 1                                                                       |                                    |                             |                                                        |  |  |  |

| QC          | vcle Activity:        |                                                                         |                                    |                             |                                                        |  |  |  |

|             | Q1                    | Q2                                                                      | Q3                                 | 3                           | Q4                                                     |  |  |  |

|             | Decode                | Read<br>register 'f'                                                    | Proce<br>Dat                       | a re<br>ar                  | Write<br>gister 'f'<br>nd other<br>pecified<br>egister |  |  |  |

|             |                       |                                                                         | •                                  | •                           |                                                        |  |  |  |

| <u>Exar</u> | <u>mple</u> :         | NEGW R                                                                  | EG,0                               |                             |                                                        |  |  |  |

|             | Before Instru<br>WREG | = 0011 1                                                                | .010 <b>[0x</b> :                  |                             |                                                        |  |  |  |

| NOF                   | )              | No Operation    |                 |      |    |                |  |  |

|-----------------------|----------------|-----------------|-----------------|------|----|----------------|--|--|

| Synt                  | ax:            | [ label ]       | NOP             |      |    |                |  |  |

| Ope                   | rands:         | None            |                 |      |    |                |  |  |

| Ope                   | ration:        | No operation    |                 |      |    |                |  |  |

| Status Affected: None |                |                 |                 |      |    |                |  |  |

| Encoding:             |                | 0000            | 0000            | 0000 |    | 0000           |  |  |

| Des                   | cription:      | No operati      | on.             |      |    |                |  |  |

| Wor                   | ds:            | 1               |                 |      |    |                |  |  |

| Cycl                  | es:            | 1               |                 |      |    |                |  |  |

| QC                    | vcle Activity: |                 |                 |      |    |                |  |  |

|                       | Q1             | Q2              | Q               | 3    |    | Q4             |  |  |

|                       | Decode         | No<br>operation | No<br>operation |      | ор | No<br>peration |  |  |

#### Example:

None.

| WREG           | =    | 0011 | 1010 <b>[0x3A]</b> , |

|----------------|------|------|----------------------|

| REG            | =    | 1010 | 1011 <b>[0xAB]</b>   |

| After Instruct | tion |      |                      |

| WREG           | =    | 1100 | 0110 <b>[0xC6]</b>   |

| REG            | =    | 1100 | 0110 <b>[0xC6]</b>   |

| SWA        | APF                                                    | Swap f                                                                    |                                                                                                                                                                   |      |                       |  |  |  |  |

|------------|--------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|--|--|--|--|

| Synt       | tax:                                                   | [label]                                                                   | SWAPF                                                                                                                                                             | f,d  |                       |  |  |  |  |

| Ope        | rands:                                                 | $\begin{array}{l} 0 \leq f \leq 25 \\ d \in \left[0,1\right] \end{array}$ | 5                                                                                                                                                                 |      |                       |  |  |  |  |

| Ope        | ration:                                                | $f<3:0> \rightarrow f<7:4> \rightarrow$                                   |                                                                                                                                                                   | ,    |                       |  |  |  |  |

| State      | us Affected:                                           | None                                                                      |                                                                                                                                                                   |      |                       |  |  |  |  |

| Enc        | oding:                                                 | 0001                                                                      | 110d                                                                                                                                                              | ffff | ffff                  |  |  |  |  |

| Des        | cription:                                              | 'f' are exch<br>placed in V                                               | The upper and lower nibbles of register<br>'f' are exchanged. If 'd' is 0, the result is<br>placed in WREG. If 'd' is 1, the result is<br>placed in register 'f'. |      |                       |  |  |  |  |

| Wor        | ds:                                                    | 1                                                                         | 1                                                                                                                                                                 |      |                       |  |  |  |  |

| Cycl       | les:                                                   | 1                                                                         | 1                                                                                                                                                                 |      |                       |  |  |  |  |

| QC         | ycle Activity:                                         |                                                                           |                                                                                                                                                                   |      |                       |  |  |  |  |

|            | Q1                                                     | Q2                                                                        | Q3                                                                                                                                                                | 3    | Q4                    |  |  |  |  |

|            | Decode                                                 | Read<br>register 'f'                                                      | Proce<br>Dat                                                                                                                                                      |      | Vrite to<br>stination |  |  |  |  |

| <u>Exa</u> | mple:<br>Before Instru<br>REG<br>After Instruct<br>REG | iction<br>= 0x53                                                          | REG,                                                                                                                                                              | 0    |                       |  |  |  |  |

| ТАВ   | LRD          | Tab                                       | Table Read                                                                                                                                                                                                 |                                    |                                                           |                               |  |  |  |  |

|-------|--------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------|-------------------------------|--|--|--|--|

| Synt  | ax:          | [ <i>la</i>                               | [ label ] TABLRD t,i,f                                                                                                                                                                                     |                                    |                                                           |                               |  |  |  |  |

| Ope   | rands:       | i∈                                        | 0 ≤ f ≤ 255<br>i ∈ [0,1]<br>t ∈ [0,1]                                                                                                                                                                      |                                    |                                                           |                               |  |  |  |  |

| Ope   | ration:      | TBI<br>If t<br>TBI<br>If i<br>TBI<br>If i | If t = 1,<br>TBLATH $\rightarrow$ f;<br>If t = 0,<br>TBLATL $\rightarrow$ f;<br>Prog Mem (TBLPTR) $\rightarrow$ TBLAT;<br>If i = 1,<br>TBLPTR + 1 $\rightarrow$ TBLPTR<br>If i = 0,<br>TBLPTR is unchanged |                                    |                                                           |                               |  |  |  |  |

| Statu | us Affected  | : No                                      | None                                                                                                                                                                                                       |                                    |                                                           |                               |  |  |  |  |

| Enco  | oding:       | 1                                         | 1010 10ti ffff ffff                                                                                                                                                                                        |                                    |                                                           |                               |  |  |  |  |

| Deso  | cription:    | 1.                                        | <ol> <li>A byte of the table latch (TBLAT)<br/>is moved to register file 'f'.<br/>If t = 1: the high byte is moved;<br/>If t = 0: the low byte is moved.</li> </ol>                                        |                                    |                                                           |                               |  |  |  |  |

|       |              | 2.                                        | gram<br>by th<br>(TBLF                                                                                                                                                                                     | memory lo<br>ne 16-bit<br>PTR) are | tents of t<br>ocation po<br>Table<br>loaded i<br>ch (TBLA | nted to<br>Pointer<br>nto the |  |  |  |  |

|       |              | 3.                                        | <ol> <li>If i = 1: TBLPTR is incremented;<br/>If i = 0: TBLPTR is not<br/>incremented.</li> </ol>                                                                                                          |                                    |                                                           |                               |  |  |  |  |

| Wor   | ds:          | 1                                         | 1                                                                                                                                                                                                          |                                    |                                                           |                               |  |  |  |  |

| Cycl  | es:          | 2 (3                                      | 2 (3-cycle if f = PCL)                                                                                                                                                                                     |                                    |                                                           |                               |  |  |  |  |

| QC    | cle Activity | /:                                        |                                                                                                                                                                                                            |                                    |                                                           |                               |  |  |  |  |

|       | Q1           | Q                                         | 2                                                                                                                                                                                                          | Q3                                 | (                                                         | Q4                            |  |  |  |  |

|       | Decode       | Re<br>regi:<br>TBLA                       | ster                                                                                                                                                                                                       | Proces<br>Data                     | -                                                         | /rite<br>ister 'f'            |  |  |  |  |

| Decode    | Read           | Process   | Write         |

|-----------|----------------|-----------|---------------|

|           | register       | Data      | register 'f'  |

|           | TBLATH or      |           |               |

|           | TBLATL         |           |               |

| No        | No             | No        | No            |

| operation | operation      | operation | operation     |

|           | (Table Pointer |           | (OE goes low) |

|           | on Address     |           |               |

|           | bus)           |           |               |

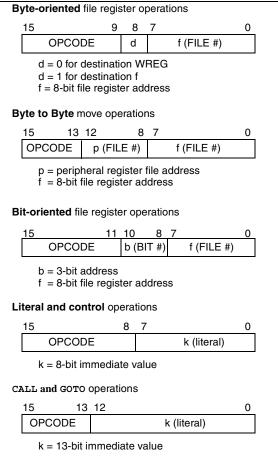

## 20.4 Timing Diagrams and Specifications

### TABLE 20-1: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic         | Min   | Тур†   | Max   | Units | Conditions                                      |

|--------------|-------|------------------------|-------|--------|-------|-------|-------------------------------------------------|

|              | Fosc  | External CLKIN         | DC    |        | 8     | MHz   | EC osc mode - 08 devices (8 MHz devices)        |

|              |       | Frequency (Note 1)     | DC    | —      | 16    | MHz   | - 16 devices (16 MHz devices)                   |

|              |       |                        | DC    | —      | 33    | MHz   | - 33 devices (33 MHz devices)                   |

|              |       | Oscillator Frequency   | DC    | _      | 4     | MHz   | RC osc mode                                     |

|              |       | (Note 1)               | 2     | —      | 8     | MHz   | XT osc mode - 08 devices (8 MHz devices)        |

|              |       |                        | 2     | —      | 16    | MHz   | - 16 devices (16 MHz devices)                   |

|              |       |                        | 2     | —      | 33    | MHz   | - 33 devices (33 MHz devices)                   |

|              |       |                        | DC    | —      | 2     | MHz   | LF osc mode                                     |

| 1            | Tosc  | External CLKIN Period  | 125   | Ι      |       | ns    | EC osc mode - 08 devices (8 MHz devices)        |

|              |       | (Note 1)               | 62.5  | —      | —     | ns    | - 16 devices (16 MHz devices)                   |

|              |       |                        | 30.3  | _      | —     | ns    | - 33 devices (33 MHz devices)                   |

|              |       | Oscillator Period      | 250   |        |       | ns    | RC osc mode                                     |

|              |       | (Note 1)               | 125   | —      | 1,000 | ns    | XT osc mode - 08 devices (8 MHz devices)        |

|              |       |                        | 62.5  | —      | 1,000 | ns    | <ul> <li>16 devices (16 MHz devices)</li> </ul> |

|              |       |                        | 30.3  | —      | 1,000 | ns    | - 33 devices (33 MHz devices)                   |

|              |       |                        | 500   | —      | —     | ns    | LF osc mode                                     |

| 2            | Тсү   | Instruction Cycle Time | 121.2 | 4/Fosc | DC    | ns    |                                                 |

|              |       | (Note 1)               |       |        |       |       |                                                 |