Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 8MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 50                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 678 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17lc752-08i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-1: PIC17CXXX FAMILY OF DEVICES

| Features                                |            | PIC17C42A                                               | PIC17C43                                                   | PIC17C44                                                   | PIC17C752                  | PIC17C756A                 | PIC17C762                  | PIC17C766                  |

|-----------------------------------------|------------|---------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------|----------------------------|----------------------------|----------------------------|----------------------------|

| Maximum Frequer<br>of Operation         | ю          | 33 MHz                                                  | 33 MHz                                                     | 33 MHz                                                     | 33 MHz                     | 33 MHz                     | 33 MHz                     | 33 MHz                     |

| <b>Operating Voltage</b>                | Range      | 2.5 - 6.0V                                              | 2.5 - 6.0V                                                 | 2.5 - 6.0V                                                 | 3.0 - 5.5V                 | 3.0 - 5.5V                 | 3.0 - 5.5V                 | 3.0 - 5.5V                 |

| Program                                 | (EPROM)    | 2 K                                                     | 4 K                                                        | 8 K                                                        | 8 K                        | 16 K                       | 8 K                        | 16 K                       |

| Memory (x16)                            | (ROM)      | _                                                       | —                                                          | _                                                          | _                          | —                          | —                          | _                          |

| Data Memory (byte                       | es)        | 232                                                     | 454                                                        | 454                                                        | 678                        | 902                        | 678                        | 902                        |

| Hardware Multiplie                      | er (8 x 8) | Yes                                                     | Yes                                                        | Yes                                                        | Yes                        | Yes                        | Yes                        | Yes                        |

| Timer0<br>(16-bit + 8-bit post          | scaler)    | Yes                                                     | Yes                                                        | Yes                                                        | Yes                        | Yes                        | Yes                        | Yes                        |

| Timer1 (8-bit)                          |            | Yes                                                     | Yes                                                        | Yes                                                        | Yes                        | Yes                        | Yes                        | Yes                        |

| Timer2 (8-bit)                          |            | Yes                                                     | Yes                                                        | Yes                                                        | Yes                        | Yes                        | Yes                        | Yes                        |

| Timer3 (16-bit)                         |            | Yes                                                     | Yes                                                        | Yes                                                        | Yes                        | Yes                        | Yes                        | Yes                        |

| Capture inputs (16                      | -bit)      | 2                                                       | 2                                                          | 2                                                          | 4                          | 4                          | 4                          | 4                          |

| PWM outputs (up t                       | o 10-bit)  | 2                                                       | 2                                                          | 2                                                          | 3                          | 3 3                        |                            | 3                          |

| USART/SCI                               |            | 1                                                       | 1                                                          | 1                                                          | 2                          | 2                          | 2 2                        |                            |

| A/D channels (10-bit)                   |            | _                                                       | —                                                          | _                                                          | 12                         | 12                         | 16                         | 16                         |

| SSP (SPI/I <sup>2</sup> C w/Ma<br>mode) | aster      | —                                                       | —                                                          | —                                                          | Yes                        | Yes Yes                    |                            | Yes                        |

| Power-on Reset                          |            | Yes                                                     | Yes                                                        | Yes                                                        | Yes                        | Yes                        | Yes                        | Yes                        |

| Watchdog Timer                          |            | Yes                                                     | Yes                                                        | Yes                                                        | Yes                        | Yes                        | Yes                        | Yes                        |

| External Interrupts                     |            | Yes                                                     | Yes                                                        | Yes                                                        | Yes                        | Yes                        | Yes                        | Yes                        |

| Interrupt Sources                       |            | 11                                                      | 11                                                         | 11                                                         | 18                         | 18 18                      |                            | 18                         |

| Code Protect                            |            | Yes                                                     | Yes                                                        | Yes                                                        | Yes                        | Yes                        | Yes                        | Yes                        |

| Brown-out Reset                         |            |                                                         | —                                                          |                                                            | Yes                        | Yes                        | Yes                        | Yes                        |

| In-Circuit Serial<br>Programming        |            |                                                         | —                                                          |                                                            | Yes                        | Yes                        | Yes                        | Yes                        |

| I/O Pins                                |            | 33                                                      | 33                                                         | 33                                                         | 50                         | 50                         | 66                         | 66                         |

| I/O High                                | Source     | 25 mA                                                   | 25 mA                                                      | 25 mA                                                      | 25 mA                      | 25 mA                      | 25 mA                      | 25 mA                      |

| Current Capability                      | Sink       | 25 mA <sup>(1)</sup>                                    | 25 mA <sup>(1)</sup>                                       | 25 mA <sup>(1)</sup>                                       | 25 mA <sup>(1)</sup>       | 25 mA <sup>(1)</sup>       | 25 mA <sup>(1)</sup>       | 25 mA <sup>(1)</sup>       |

| Package Types                           |            | 40-pin DIP<br>44-pin PLCC<br>44-pin MQFP<br>44-pin TQFP | 40-pin DIP<br>44-pin PLCC<br>44-pin<br>MQFP<br>44-pin TQFP | 40-pin DIP<br>44-pin PLCC<br>44-pin<br>MQFP<br>44-pin TQFP | 64-pin TQFP<br>68-pin PLCC | 64-pin TQFP<br>68-pin PLCC | 80-pin TQFP<br>84-pin PLCC | 80-pin TQFP<br>84-pin PLCC |

**Note 1:** Pins RA2 and RA3 can sink up to 60 mA.

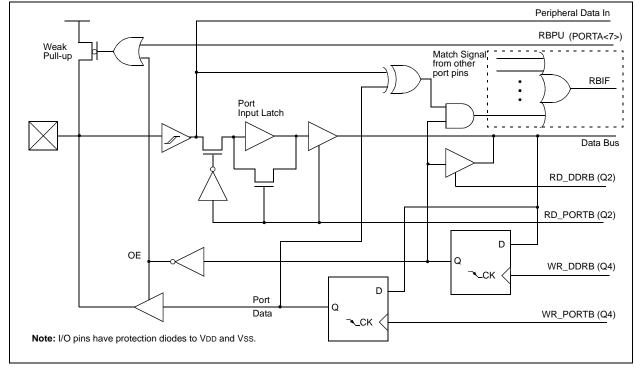

#### **10.2 PORTB and DDRB Registers**

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is DDRB. A '1' in DDRB configures the corresponding port pin as an input. A '0' in the DDRB register configures the corresponding port pin as an output. Reading PORTB reads the status of the pins, whereas writing to PORTB will write to the port latch.

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (PORTA<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are enabled on any RESET.

PORTB also has an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB0 pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB7:RB0) are compared with the value in the PORTB data latch. The "mismatch" outputs of RB7:RB0 are OR'd together to set the PORTB Interrupt Flag bit, RBIF (PIR1<7>). This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt by:

- a) Read-Write PORTB (such as: MOVPF PORTB, PORTB). This will end the mismatch condition.

- b) Then, clear the RBIF bit.

A mismatch condition will continue to set the RBIF bit. Reading, then writing PORTB, will end the mismatch condition and allow the RBIF bit to be cleared.

This interrupt-on-mismatch feature, together with software configurable pull-ups on this port, allows easy interface to a keypad and makes it possible for wakeup on key depression. For an example, refer to Application Note AN552, "Implementing Wake-up on Keystroke."

The interrupt-on-change feature is recommended for wake-up on operations, where PORTB is only used for the interrupt-on-change feature and key depression operations.

**Note:** On a device RESET, the RBIF bit is indeterminate, since the value in the latch may be different than the pin.

#### FIGURE 10-5: BLOCK DIAGRAM OF RB5:RB4 AND RB1:RB0 PORT PINS

## PIC17C7XX

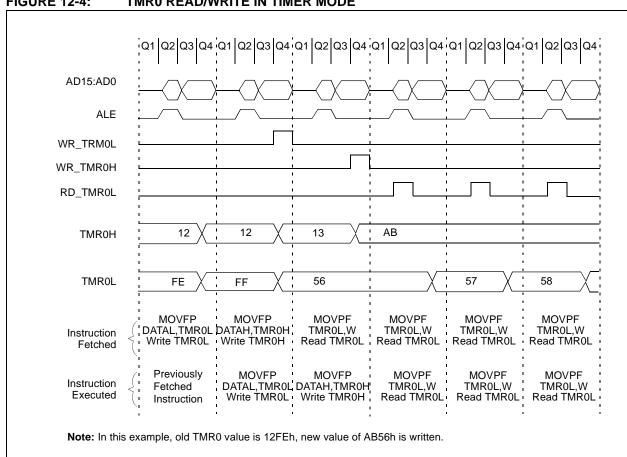

#### FIGURE 12-4: **TMR0 READ/WRITE IN TIMER MODE**

#### **TABLE 12-1: REGISTERS/BITS ASSOCIATED WITH TIMER0**

| Address       | Name   | Bit 7    | Bit 6                   | Bit 5 | Bit 4  | Bit 3 | Bit 2         | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | MCLR, WDT |

|---------------|--------|----------|-------------------------|-------|--------|-------|---------------|-------|-------|-------------------------|-----------|

| 05h, Unbanked | TOSTA  | INTEDG   | TOSE                    | T0CS  | T0PS3  | T0PS2 | T0PS1         | T0PS0 | —     | 0000 000-               | 0000 000- |

| 06h, Unbanked | CPUSTA | -        | -                       | STKAV | GLINTD | TO    | PD            | POR   | BOR   | 11 11qq                 | 11 qquu   |

| 07h, Unbanked | INTSTA | PEIF     | TOCKIF                  | T0IF  | INTF   | PEIE  | <b>T0CKIE</b> | TOIE  | INTE  | 0000 0000               | 0000 0000 |

| 0Bh, Unbanked | TMR0L  | TMR0 Reg | TMR0 Register; Low Byte |       |        |       |               |       |       |                         | uuuu uuuu |

| 0Ch, Unbanked | TMR0H  | TMR0 Reg | MR0 Register; High Byte |       |        |       |               |       |       |                         | uuuu uuuu |

Legend: x = unknown, u = unchanged, - = unimplemented, read as a '0', q = value depends on condition. Shaded cells are not used by Timer0.

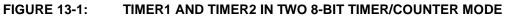

#### 13.1 Timer1 and Timer2

#### 13.1.1 TIMER1, TIMER2 IN 8-BIT MODE

Both Timer1 and Timer2 will operate in 8-bit mode when the T16 bit is clear. These two timers can be independently configured to increment from the internal instruction cycle clock (TcY), or from an external clock source on the RB4/TCLK12 pin. The timer clock source is configured by the TMRxCS bit (x = 1 for Timer1, or = 2 for Timer2). When TMRxCS is clear, the clock source is internal and increments once every instruction cycle (Fosc/4). When TMRxCS is set, the clock source is the RB4/TCLK12 pin and the counters will increment on every falling edge of the RB4/TCLK12 pin.

The timer increments from 00h until it equals the Period register (PRx). It then resets to 00h at the next increment cycle. The timer interrupt flag is set when the timer is reset. TMR1 and TMR2 have individual interrupt flag bits. The TMR1 interrupt flag bit is latched into TMR1IF and the TMR2 interrupt flag bit is latched into TMR2IF.

Each timer also has a corresponding interrupt enable bit (TMRxIE). The timer interrupt can be enabled/ disabled by setting/clearing this bit. For peripheral interrupts to be enabled, the Peripheral Interrupt Enable bit must be set (PEIE = '1') and global interrupt must be enabled (GLINTD = '0').

The timers can be turned on and off under software control. When the timer on control bit (TMRxON) is set, the timer increments from the clock source. When TMRxON is cleared, the timer is turned off and cannot cause the timer interrupt flag to be set.

### 13.1.1.1 External Clock Input for Timer1 and Timer2

When TMRxCS is set, the clock source is the RB4/ TCLK12 pin, and the counter will increment on every falling edge on the RB4/TCLK12 pin. The TCLK12 input is synchronized with internal phase clocks. This causes a delay from the time a falling edge appears on TCLK12 to the time TMR1 or TMR2 is actually incremented. For the external clock input timing requirements, see the Electrical Specification section.

#### 13.1.3 USING PULSE WIDTH MODULATION (PWM) OUTPUTS WITH TIMER1 AND TIMER2

Three high speed pulse width modulation (PWM) outputs are provided. The PWM1 output uses Timer1 as its time base, while PWM2 and PWM3 may independently be software configured to use either Timer1 or Timer2 as the time base. The PWM outputs are on the RB2/PWM1, RB3/PWM2 and RG5/PWM3 pins.

Each PWM output has a maximum resolution of 10bits. At 10-bit resolution, the PWM output frequency is 32.2 kHz (@ 32 MHz clock) and at 8-bit resolution the PWM output frequency is 128.9 kHz. The duty cycle of the output can vary from 0% to 100%.

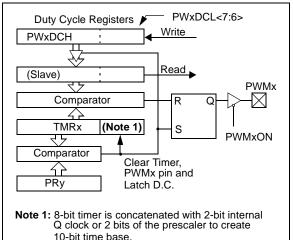

Figure 13-3 shows a simplified block diagram of a PWM module.

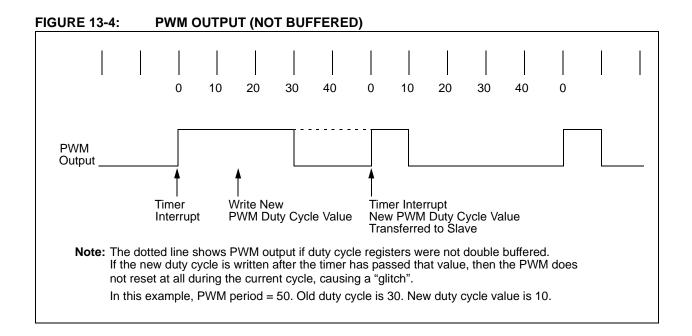

The duty cycle registers are double buffered for glitch free operation. Figure 13-4 shows how a glitch could occur if the duty cycle registers were not double buffered.

The user needs to set the PWM1ON bit (TCON2<4>) to enable the PWM1 output. When the PWM1ON bit is set, the RB2/PWM1 pin is configured as PWM1 output and forced as an output, irrespective of the data direction bit (DDRB<2>). When the PWM1ON bit is clear, the pin behaves as a port pin and its direction is controlled by its data direction bit (DDRB<2>). Similarly, the PWM2ON (TCON2<5>) bit controls the configuration of the RB3/PWM2 pin and the PWM3ON (TCON3<0>) bit controls the configuration of the RG5/PWM3 pin.

#### FIGURE 13-3: SIMPLIFIED PWM BLOCK DIAGRAM

| TABLE 14-5: BAUD R | ATES FOR ASYNCHRONOUS MODE |

|--------------------|----------------------------|

|--------------------|----------------------------|

| BAUD        | Fosc = | = 33 MHz                                                                                    | SPBRG              | FOSC = 25      | MHz    | SPBRG              | FOSC = 2 | FOSC = 20 MHz  |                    | SPBRG FOSC = 16 MHz |        | SPBRG              |

|-------------|--------|---------------------------------------------------------------------------------------------|--------------------|----------------|--------|--------------------|----------|----------------|--------------------|---------------------|--------|--------------------|

| RATE<br>(K) | KBAU   | D %ERROR                                                                                    | VALUE<br>(DECIMAL) | KBAUD          | %ERROR | VALUE<br>(DECIMAL) | KBAUD    | %ERROR         | VALUE<br>(DECIMAL) | KBAUD               | %ERROR | VALUE<br>(DECIMAL) |

| 0.3         | NA     |                                                                                             |                    | NA             | _      |                    | NA       | _              |                    | NA                  | _      |                    |

| 1.2         | NA     | _                                                                                           | _                  | NA             | _      | _                  | 1.221    | +1.73          | 255                | 1.202               | +0.16  | 207                |

| 2.4         | 2.398  | -0.07                                                                                       | 214                | 2.396          | 0.14   | 162                | 2.404    | +0.16          | 129                | 2.404               | +0.16  | 103                |

| 9.6         | 9.548  |                                                                                             | 53                 | 9.53           | -0.76  | 40                 | 9.469    | -1.36          | 32                 | 9.615               | +0.16  | 25                 |

| 19.2        | 19.09  |                                                                                             | 26                 | 19.53          | +1.73  | 19                 | 19.53    | +1.73          | 15                 | 19.23               | +0.16  | 12                 |

| 76.8        | 73.66  | 6 -4.09                                                                                     | 6                  | 78.13          | +1.73  | 4                  | 78.13    | +1.73          | 3                  | 83.33               | +8.51  | 2                  |

| 96          | 103.1  | 2 +7.42                                                                                     | 4                  | 97.65          | +1.73  | 3                  | 104.2    | +8.51          | 2                  | NA                  | _      | _                  |

| 300         | 257.8  | 1 -14.06                                                                                    | 1                  | 390.63         | +30.21 | 0                  | 312.5    | +4.17          | 0                  | NA                  | _      | _                  |

| 500         | 515.6  | 2 +3.13                                                                                     | 0                  | NA             | _      | _                  | NA       | _              | _                  | NA                  | _      | _                  |

| HIGH        | 515.6  | 2 —                                                                                         | 0                  | _              | _      | 0                  | 312.5    | _              | 0                  | 250                 | _      | 0                  |

| LOW         | 2.014  | 4 <u> </u>                                                                                  | 255                | 1.53           | _      | 255                | 1.221    | _              | 255                | 0.977               | _      | 255                |

| I           | F      | Fosc = 10 MHz                                                                               |                    |                | Fosc   | = 7.159 MH         | 7        |                | FOSC = 5           | .068 MHz            |        |                    |

| BAU<br>RAT  | ID     |                                                                                             |                    | SPBRG<br>VALUE |        | - 1.100 1011       |          | SPBRG<br>VALUE | 1 000 - 0          |                     |        | SPBRG<br>VALUE     |

| (K)         | )      | KBAUD                                                                                       | %ERROR             | (DECIMA        | L) KE  | BAUD %             | ERROR    | (DECIMAL       | ) KBAU             | D %I                | ERROR  | (DECIMAL)          |

| 0.3         | 3      | NA                                                                                          | —                  | _              |        | NA                 | _        | —              | 0.31               |                     | +3.13  | 255                |

| 1.2         | 2      | 1.202                                                                                       | +0.16              | 129            | 1      | .203               | _0.23    | 92             | 1.2                |                     | 0      | 65                 |

| 2.4         | Ļ      | 2.404                                                                                       | +0.16              | 64             | 2      | .380               | -0.83    | 46             | 2.4                |                     | 0      | 32                 |

| 9.6         | 6      | 9.766                                                                                       | +1.73              | 15             | 9      | .322               | -2.90    | -2.90 11       |                    |                     | -3.13  | 7                  |

| 19.3        | 2      | 19.53                                                                                       | +1.73              | 7              | 1      | 8.64               | -2.90    | 2.90 5         |                    |                     | +3.13  | 3                  |

| 76.         | 8      | 78.13                                                                                       | +1.73              | 1              |        | NA                 | —        |                | 79.2               |                     | +3.13  | 0                  |

| 96          | ;      | NA                                                                                          | —                  | —              |        | NA                 | —        |                | NA                 |                     | —      | —                  |

| 300         | C      | NA                                                                                          | —                  | _              |        | NA                 | _        | — NA           |                    |                     |        | -                  |

| 500         |        | NA                                                                                          | —                  | _              |        | NA                 | _        | —              | NA                 |                     |        | -                  |

| HIG         |        | 156.3                                                                                       | —                  | 0              |        | 11.9               | _        | 0              | 0 79.2             |                     | _      | 0                  |

| LO          | N      | 0.610                                                                                       | —                  | 255            | 0      | .437               | —        | 255            | 0.309              | 0.309               |        | 2 <b>55</b>        |

|             | F      | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | Hz                 | Fosc =         |        | SC = 1 MHz         |          | Fosc = 3       |                    | C = 32.768 kHz      |        |                    |

| BAU<br>RAT  | ID     |                                                                                             |                    | SPBRG<br>VALUE | i      |                    |          | SPBRG<br>VALUE |                    |                     |        | SPBRG<br>VALUE     |

| (K)         |        | KBAUD                                                                                       | %ERROR             | (DECIMA        | L) KE  | AUD %              | ERROR    | (DECIMAL       | ) KBAU             | D %I                | ERROR  | (DECIMAL)          |

| 0.3         | 3      | 0.301                                                                                       | +0.23              | 185            | 0      | .300               | +0.16    | 51             | 0.256              | ; -                 | 14.67  | 1                  |

| 1.2         | 2      | 1.190                                                                                       | -0.83              | 46             | 1      | .202               | +0.16    | 12             | NA                 |                     | _      | _                  |

| 2.4         | Ļ      | 2.432                                                                                       | +1.32              | 22             | 2      | .232               | -6.99    | 6              | NA                 |                     | _      | _                  |

| 9.6         | 6      | 9.322                                                                                       | -2.90              | 5              |        | NA                 | _        | _              | NA                 |                     | _      | _                  |

| 19.:        | 2      | 18.64                                                                                       | -2.90              | 2              |        | NA                 | _        | _              | NA                 |                     | _      | _                  |

| 76.         | 8      | NA                                                                                          | _                  | _              |        | NA                 | _        | _              | NA                 |                     | _      | _                  |

| 96          | ;      | NA                                                                                          | _                  | _              |        | NA                 | _        | _              | NA                 |                     | _      | _                  |

| 300         | C      | NA                                                                                          | _                  | _              |        | NA                 | _        | _              | NA                 |                     | _      | _                  |

| 500         | D      | NA                                                                                          | _                  | _              |        | NA                 | _        | _              | NA                 |                     | _      | _                  |

| HIG         | н      | 55.93                                                                                       | _                  | 0              | 1      | 5.63               | _        | 0              | 0.512              | 2                   | _      | 0                  |

| LOV         | N      | 0.218                                                                                       | _                  | 255            | 0      | .061               | _        | 255            | 0.002              | 2                   | _      | 255                |

#### REGISTER 15-2: SSPCON1: SYNC SERIAL PORT CONTROL REGISTER1 (ADDRESS 11h, BANK 6)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WCOL  | SSPOV | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7 WCOL: Write Collision Detect bit

Master mode:

1 = A write to the SSPBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started

0 = No collision

<u>Slave mode:</u>

1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)

0 = No collision

bit 6

SSPOV: Receive Overflow Indicator bit

In SPI mode:

- 1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in Slave mode. In Slave mode, the user must read the SSPBUF, even if only transmitting data, to avoid setting overflow. In Master mode, the overflow bit is not set, since each new reception (and transmission) is initiated by writing to the SSPBUF register. (Must be cleared in software.)

- 0 = No overflow

- In I<sup>2</sup>C mode:

- 1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit mode. (Must be cleared in software.)

- 0 = No overflow

bit 5 SSPEN: Synchronous Serial Port Enable bit

In both modes, when enabled, these pins must be properly configured as input or output.

In SPI mode:

1 = Enables serial port and configures SCK, SDO, SDI and  $\overline{SS}$  as the source of the serial port pins 0 = Disables serial port and configures these pins as I/O port pins

In I<sup>2</sup>C mode:

- 1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins 0 = Disables serial port and configures these pins as I/O port pins

- **Note:** In SPI mode, these pins must be properly configured as input or output.

bit 4 **CKP**: Clock Polarity Select bit

In SPI mode: 1 = Idle state for clock is a high level 0 = Idle state for clock is a low level

- In I<sup>2</sup>C Slave mode: SCK release control

- 1 = Enable clock

0 = Holds clock low (clock stretch). (Used to ensure data setup time.)

In I<sup>2</sup>C Master mode:

Unused in this mode

bit 3-0 SSPM3:SSPM0: Synchronous Serial Port Mode Select bits

- 0000 = SPI Master mode, clock = Fosc/4

- 0001 = SPI Master mode, clock = FOSC/16

- 0010 = SPI Master mode, clock = FOSC/64

- 0011 = SPI Master mode, clock = TMR2 output/2

- 0100 = SPI Slave mode, clock = SCK pin,  $\overline{SS}$  pin control enabled

- 0101 =SPI Slave mode, clock = SCK pin,  $\overline{SS}$  pin control disabled,  $\overline{SS}$  can be used as I/O pin

- $0110 = I^2C$  Slave mode, 7-bit address

- $0111 = I^2C$  Slave mode, 10-bit address

- $1000 = I^2C$  Master mode, clock = Fosc / (4 \* (SSPADD+1))

- 1xx1 = Reserved

- 1x1x = Reserved

| Legend:                  |                  |                                    |                    |  |  |  |

|--------------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit         | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| - n = Value at POR Reset | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

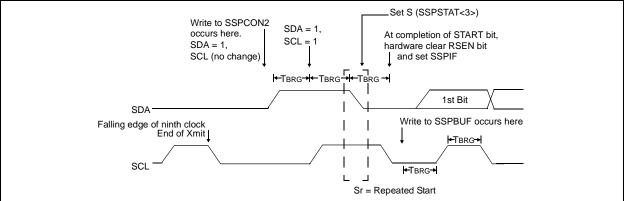

#### 15.2.10 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C module is in the idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the baud rate generator is loaded with the contents of SSPADD<6:0> and begins counting. The SDA pin is released (brought high) for one baud rate generator count (TBRG). When the baud rate generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA is low) for one TBRG while SCL is high. Following this, the RSEN bit in the SSPCON2 register will be automatically cleared and the baud rate generator is not reloaded, leaving the SDA pin held low. As soon as a START condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the baud rate generator has timed out.

- Note 1: If the RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low to high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode), or eight bits of data (7-bit mode).

#### 15.2.10.1 WCOL status flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

**Note:** Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

#### FIGURE 15-22: REPEAT START CONDITION WAVEFORM

Figure 16-2 shows the conversion sequence and the terms that are used. Acquisition time is the time that the A/D module's holding capacitor is connected to the external voltage level. Then, there is the conversion time of 12 TAD, which is started when the GO bit is set. The sum of these two times is the sampling time. There is a minimum acquisition time to ensure that the holding capacitor is charged to a level that will give the desired accuracy for the A/D conversion.

#### FIGURE 16-2: A/D CONVERSION SEQUENCE

| Acquisition Time                                | A/D Conversion Time                                                                                                                                       |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                 | A/D conversion complete, result is loaded in ADRES register.<br>Holding capacitor begins acquiring voltage level on selected<br>channel, ADIF bit is set. |

|                                                 | /hen A/D conversion is started setting the GO bit).                                                                                                       |

| When A/D holding cap<br>After A/D conversion, c | acitor starts to charge.<br>r when new A/D channel is selected.                                                                                           |

#### 16.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 16-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), Figure 16-3. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (changed) this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 16-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

Example 16-1 shows the calculation of the minimum required acquisition time (TACQ). This is based on the following application system assumptions.

| CHOLD            | =      | 120 pF                             |

|------------------|--------|------------------------------------|

| Rs               | =      | 10 kΩ                              |

| Conversion Error | $\leq$ | 1/2 LSb                            |

| Vdd              | =      | $5V \rightarrow Rss = 7 \ k\Omega$ |

|                  |        | (see graph in Figure 16-3)         |

| Temperature      | =      | 50°C (system max.)                 |

| VHOLD            | =      | 0V @ time = 0                      |

|                  |        |                                    |

#### EQUATION 16-1: ACQUISITION TIME

| TACQ = | Amplifier Settling Time +<br>Holding Capacitor Charging Time +<br>Temperature Coefficient |

|--------|-------------------------------------------------------------------------------------------|

| =      | TAMP + TC + TCOFF                                                                         |

#### EQUATION 16-2: A/D MINIMUM CHARGING TIME

VHOLD =  $(V_{REF} - (V_{REF}/2048)) \cdot (1 - e^{(-T_c/C_{HOLD}(R_{IC} + R_{SS} + R_S))})$ or TC =  $-(120 \text{ pF})(1 \text{ k}\Omega + \text{Rss} + \text{Rs}) \ln(1/2047)$

#### EXAMPLE 16-1: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME

| TACQ =   | TAMP + TC + TCOFF                                                                                                                                                                                         |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Temperat | ture coefficient is only required for temperatures > $25^{\circ}$ C.                                                                                                                                      |

| TACQ =   | $2 \ \mu s + Tc + [(Temp - 25^{\circ}C)(0.05 \ \mu s/^{\circ}C)]$                                                                                                                                         |

| Tc =     | -CHOLD (RIC + RSS + RS) $\ln(1/2047)$<br>-120 pF (1 k $\Omega$ + 7 k $\Omega$ + 10 k $\Omega$ ) $\ln(0.0004885)$<br>-120 pF (18 k $\Omega$ ) $\ln(0.0004885)$<br>-2.16 $\mu$ s (-7.6241)<br>16.47 $\mu$ s |

| TACQ =   | 2 μs + 16.47 μs + [(50×C - 25°C)(0.05 μs/°C)]<br>18.447 μs + 1.25 μs<br>19.72 μs                                                                                                                          |

Note 1: The reference voltage (VREF) has no effect on the equation since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

- **4:** After a conversion has completed, a 2.0 TAD delay must complete before acquisition can begin again. During this time, the holding capacitor is not connected to the selected A/D input channel.

© 1998-2013 Microchip Technology Inc.

### 17.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of realtime applications. The PIC17CXXX family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection (Section 4.0)

- RESET (Section 5.0)

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts (Section 6.0)

- Watchdog Timer (WDT)

- SLEEP mode

- Code protection

The PIC17CXXX has a Watchdog Timer which can be shut-off only through EPROM bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on POR and BOR. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 96 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake from SLEEP through external RESET, Watchdog Timer Reset, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LF crystal option saves power. Configuration bits are used to select various options. This configuration word has the format shown in Figure 17-1.

| High (H) Table Read Addr. | U-x                        | R/P-1              | R/P-1         | U-x       | U-x       | U-x    | U-x    | U-x   | U-x   |

|---------------------------|----------------------------|--------------------|---------------|-----------|-----------|--------|--------|-------|-------|

| FE0Fh - FE08h             | —                          | PM2                | BODEN         | _         | —         | —      | —      | —     | —     |

|                           | bit 15 bit 8               | bit 7              |               |           |           |        |        |       | bit 0 |

| Low (L) Table Read Addr.  | U-x                        | U-x                | R/P-1         | U-x       | R/P-1     | R/P-1  | R/P-1  | R/P-1 | R/P-1 |

| FE07h - FE00h             |                            | —                  | PM1           |           | PM0       | WDTPS1 | WDTPS0 | FOSC1 | FOSC0 |

|                           | bit 15 bit 8               | bit 7              |               |           |           |        |        |       | bit 0 |

| bits 7H, 6L, 4L           | PM2, PM1, I                | <b>&gt;M∩</b> ∙ Pr | ocessor M     | nde Sel   | ect hits  |        |        |       |       |

| 513 71, 02, 42            | 111 = Micro                |                    |               |           |           |        |        |       |       |

|                           | 110 <b>= Micro</b>         |                    |               |           |           |        |        |       |       |

|                           | 101 = Exten                |                    |               |           | mode      |        |        |       |       |

| bit 6H                    | BODEN: Bro                 |                    |               |           | moue      |        |        |       |       |

|                           | 1 = Brown-o                |                    |               |           | ed        |        |        |       |       |

|                           | 0 = Brown-o                | ut Detec           | t circuitry i | s disabl  | ed        |        |        |       |       |

| bits 3L:2L                | WDTPS1:W                   |                    |               |           | Select bi | ts     |        |       |       |

|                           | 11 = WDT e<br>10 = WDT e   |                    |               |           |           |        |        |       |       |

|                           | 01 = WDT e                 |                    |               |           |           |        |        |       |       |

|                           | 00 = WDT d                 | isabled,           | 16-bit over   | rflow tim | ner       |        |        |       |       |

| bits 1L:0L                | FOSC1:FOS                  |                    | cillator Sele | ect bits  |           |        |        |       |       |

|                           | 11 = EC osc<br>10 = XT osc |                    |               |           |           |        |        |       |       |

|                           | 01 = RC osc                |                    |               |           |           |        |        |       |       |

|                           | 00 = LF osc                | llator             |               |           |           |        |        |       |       |

| Shaded bits (—)           | Reserved                   |                    |               |           |           |        |        |       |       |

#### **REGISTER 17-1: CONFIGURATION WORDS**

#### TABLE 18-2: PIC17CXXX INSTRUCTION SET

| Mnemonic | ,     | Description                           | Cycles | 16-bit Opcode |        |      |          | Status    | Notes |

|----------|-------|---------------------------------------|--------|---------------|--------|------|----------|-----------|-------|

| Operands |       | Description                           | Cycles | MSb           | Sb LSb |      | Affected | Notes     |       |

| BYTE-ORI | ENTED | FILE REGISTER OPERATIONS              |        |               |        |      |          | 1         |       |

| ADDWF    | f,d   | ADD WREG to f                         | 1      | 0000          | 111d   | ffff | ffff     | OV,C,DC,Z |       |

| ADDWFC   | f,d   | ADD WREG and Carry bit to f           | 1      | 0001          | 000d   | ffff | ffff     | OV,C,DC,Z |       |

| ANDWF    | f,d   | AND WREG with f                       | 1      | 0000          | 101d   | ffff | ffff     | Z         |       |

| CLRF     | f,s   | Clear f, or Clear f and Clear WREG    | 1      | 0010          | 100s   | ffff | ffff     | None      | 3     |

| COMF     | f,d   | Complement f                          | 1      | 0001          | 001d   | ffff | ffff     | Z         |       |

| CPFSEQ   | f     | Compare f with WREG, skip if f = WREG | 1 (2)  | 0011          | 0001   | ffff | ffff     | None      | 6,8   |

| CPFSGT   | f     | Compare f with WREG, skip if f > WREG | 1 (2)  | 0011          | 0010   | ffff | ffff     | None      | 2,6,8 |

| CPFSLT   | f     | Compare f with WREG, skip if f < WREG | 1 (2)  | 0011          | 0000   | ffff | ffff     | None      | 2,6,8 |

| DAW      | f,s   | Decimal Adjust WREG Register          | 1      | 0010          | 111s   | ffff | ffff     | С         | 3     |

| DECF     | f,d   | Decrement f                           | 1      | 0000          | 011d   | ffff | ffff     | OV,C,DC,Z |       |

| DECFSZ   | f,d   | Decrement f, skip if 0                | 1 (2)  | 0001          | 011d   | ffff | ffff     | None      | 6,8   |

| DCFSNZ   | f,d   | Decrement f, skip if not 0            | 1 (2)  | 0010          | 011d   | ffff | ffff     | None      | 6,8   |

| INCF     | f,d   | Increment f                           | 1      | 0001          | 010d   | ffff | ffff     | OV,C,DC,Z |       |

| INCFSZ   | f,d   | Increment f, skip if 0                | 1 (2)  | 0001          | 111d   | ffff | ffff     | None      | 6,8   |

| INFSNZ   | f,d   | Increment f, skip if not 0            | 1 (2)  | 0010          | 010d   | ffff | ffff     | None      | 6,8   |

| IORWF    | f,d   | Inclusive OR WREG with f              | 1      | 0000          | 100d   | ffff | ffff     | Z         |       |

| MOVFP    | f,p   | Move f to p                           | 1      | 011p          | pppp   | ffff | ffff     | None      |       |

| MOVPF    | p,f   | Move p to f                           | 1      | 010p          | pppp   | ffff | ffff     | Z         |       |

| MOVWF    | f     | Move WREG to f                        | 1      | 0000          | 0001   | ffff | ffff     | None      |       |

| MULWF    | f     | Multiply WREG with f                  | 1      | 0011          | 0100   | ffff | ffff     | None      |       |

| NEGW     | f,s   | Negate WREG                           | 1      | 0010          | 110s   | ffff | ffff     | OV,C,DC,Z | 1,3   |

| NOP      | _     | No Operation                          | 1      | 0000          | 0000   | 0000 | 0000     | None      |       |

| RLCF     | f,d   | Rotate left f through Carry           | 1      | 0001          | 101d   | ffff | ffff     | С         |       |

| RLNCF    | f,d   | Rotate left f (no carry)              | 1      | 0010          | 001d   | ffff | ffff     | None      |       |

| RRCF     | f,d   | Rotate right f through Carry          | 1      | 0001          | 100d   | ffff | ffff     | С         |       |

| RRNCF    | f,d   | Rotate right f (no carry)             | 1      | 0010          | 000d   | ffff | ffff     | None      |       |

| SETF     | f,s   | Set f                                 | 1      | 0010          | 101s   | ffff | ffff     | None      | 3     |

| SUBWF    | f,d   | Subtract WREG from f                  | 1      | 0000          | 010d   | ffff | ffff     | OV,C,DC,Z | 1     |

| SUBWFB   | f,d   | Subtract WREG from f with Borrow      | 1      | 0000          | 001d   | ffff | ffff     | OV,C,DC,Z | 1     |

| SWAPF    | f,d   | Swap f                                | 1      | 0001          | 110d   | ffff | ffff     | None      |       |

| TABLRD   | t,i,f | Table Read                            | 2 (3)  | 1010          | 10ti   | ffff | ffff     | None      | 7     |

| TABLWT   | t,i,f | Table Write                           | 2      | 1010          | 11ti   | ffff | ffff     | None      | 5     |

| TLRD     | t,f   | Table Latch Read                      | 1      | 1010          | 00tx   | ffff | ffff     | None      |       |

| TLWT     | t,f   | Table Latch Write                     | 1      | 1010          | 01tx   | ffff | ffff     | None      |       |

Legend: Refer to Table 18-1 for opcode field descriptions.

Note 1: 2's Complement method.

**2:** Unsigned arithmetic.

**3:** If s = '1', only the file is affected: If s = '0', both the WREG register and the file are affected; If only the Working register (WREG) is required to be affected, then f = WREG must be specified.

4: During an LCALL, the contents of PCLATH are loaded into the MSB of the PC and kkkk kkkk is loaded into the LSB of the PC (PCL).

**5:** Multiple cycle instruction for EPROM programming when table pointer selects internal EPROM. The instruction is terminated by an interrupt event. When writing to external program memory, it is a two-cycle instruction.

**6:** Two-cycle instruction when condition is true, else single cycle instruction.

7: Two-cycle instruction except for TABLRD to PCL (program counter low byte), in which case it takes 3 cycles.

8: A "skip" means that instruction fetched during execution of current instruction is not executed, instead a NOP is executed.

| ADD        | OWFC                                      | ADD WR                                                         | ADD WREG and Carry bit to f                                     |                             |                          |  |  |  |  |  |

|------------|-------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------|--------------------------|--|--|--|--|--|

| Syn        | tax:                                      | [ label ] A                                                    | DDWFC                                                           | f,d                         |                          |  |  |  |  |  |

| Ope        | rands:                                    | $\begin{array}{l} 0 \leq f \leq 25 \\ d \in [0,1] \end{array}$ | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \end{array}$ |                             |                          |  |  |  |  |  |

| Ope        | ration:                                   | (WREG) ·                                                       | + (f) + C –                                                     | → (dest)                    |                          |  |  |  |  |  |

| Stat       | us Affected:                              | OV, C, D0                                                      | OV, C, DC, Z                                                    |                             |                          |  |  |  |  |  |

| Enc        | oding:                                    | 0001                                                           | 000d                                                            | ffff                        | ffff                     |  |  |  |  |  |

| Des        | cription:                                 | Add WREC<br>memory lo<br>placed in V<br>placed in d            | cation 'f'. If<br>VREG. If 'd                                   | 'd' is 0, th<br>' is 1, the | e result is<br>result is |  |  |  |  |  |

| Wor        | ds:                                       | 1                                                              |                                                                 |                             |                          |  |  |  |  |  |

| Сус        | les:                                      | 1                                                              | 1                                                               |                             |                          |  |  |  |  |  |

| QC         | ycle Activity:                            |                                                                |                                                                 |                             |                          |  |  |  |  |  |

|            | Q1                                        | Q2                                                             | Q3                                                              |                             | Q4                       |  |  |  |  |  |

|            | Decode                                    | Read<br>register 'f'                                           | Proces<br>Data                                                  | -                           | rite to<br>tination      |  |  |  |  |  |

| <u>Exa</u> | mple:                                     | ADDWFC                                                         | REG (                                                           | D                           |                          |  |  |  |  |  |

|            | Before Instru<br>Carry bit<br>REG<br>WREG | = 1<br>= 0x02                                                  |                                                                 |                             |                          |  |  |  |  |  |

|            | After Instruct<br>Carry bit<br>REG        |                                                                |                                                                 |                             |                          |  |  |  |  |  |

| AND                | DLW            | And Lite                              | And Literal with WREG    |                     |    |                  |  |  |  |

|--------------------|----------------|---------------------------------------|--------------------------|---------------------|----|------------------|--|--|--|

| Synt               | ax:            | [label] A                             | [ <i>label</i> ] ANDLW k |                     |    |                  |  |  |  |

| Ope                | rands:         | $0 \le k \le 25$                      | 55                       |                     |    |                  |  |  |  |

| Ope                | ration:        | (WREG)                                | AND. (k                  | $() \rightarrow ()$ | WR | EG)              |  |  |  |

| Statu              | us Affected:   | Z                                     |                          |                     |    |                  |  |  |  |

| Enco               | oding:         | 1011                                  | 0101                     | kkk                 | k  | kkkk             |  |  |  |

| Des                | cription:      | The conter<br>the 8-bit lite<br>WREG. |                          |                     |    |                  |  |  |  |

| Wor                | ds:            | 1                                     | 1                        |                     |    |                  |  |  |  |

| Cycl               | es:            | 1                                     |                          |                     |    |                  |  |  |  |

| QC                 | vcle Activity: |                                       |                          |                     |    |                  |  |  |  |

|                    | Q1             | Q2                                    | Q                        | 3                   |    | Q4               |  |  |  |

|                    | Decode         | Read literal<br>'k'                   | Proce<br>Dat             |                     | -  | Vrite to<br>VREG |  |  |  |

|                    |                |                                       |                          |                     |    |                  |  |  |  |

| Example:           |                | ANDLW                                 | 0x5F                     |                     |    |                  |  |  |  |

| Before Instruction |                |                                       |                          |                     |    |                  |  |  |  |

WREG = 0xA3 After Instruction WREG = 0x03

| Carry bit | = | 0    |

|-----------|---|------|

| REG       | = | 0x02 |

| WREG      | = | 0x50 |

| MULLW                                                                             | Multiply                                                                                                                          | Literal with \                                                                                                                                                                           | WREG                                                                                        | MULV   | VF                                                                                              | Multiply                                | WREG w                                                                                                                                                                                                                                                                                                                                                                                                                        | vith f |                                                                                         |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------|

| Syntax:                                                                           | [ label ]                                                                                                                         | MULLW k                                                                                                                                                                                  |                                                                                             | Syntax | C.                                                                                              | [ label ]                               | MULWF                                                                                                                                                                                                                                                                                                                                                                                                                         | f      |                                                                                         |

| Operands:                                                                         | $0 \le k \le 25$                                                                                                                  | 5                                                                                                                                                                                        |                                                                                             | Opera  | nds:                                                                                            | $0 \le f \le 2$                         | 55                                                                                                                                                                                                                                                                                                                                                                                                                            |        |                                                                                         |

| Operation:                                                                        | (k x WRE                                                                                                                          | $G) \rightarrow PROD$                                                                                                                                                                    | H:PRODL                                                                                     | Opera  | tion:                                                                                           | (WREG                                   | $x f) \rightarrow PR$                                                                                                                                                                                                                                                                                                                                                                                                         | ODH:   | PRODL                                                                                   |

| Status Affected:                                                                  | None                                                                                                                              |                                                                                                                                                                                          |                                                                                             | Status | Affected:                                                                                       | None                                    |                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                                                                                         |

| Encoding:                                                                         | 1011                                                                                                                              | 1100 kk                                                                                                                                                                                  | kk kkkk                                                                                     | Encod  | ding:                                                                                           | 0011                                    | 0100                                                                                                                                                                                                                                                                                                                                                                                                                          | ffff   | ffff                                                                                    |

| Description:                                                                      | out betwee<br>and the 8-t<br>result is pla<br>register pa<br>high byte.<br>WREG is u<br>None of the<br>Note that n<br>is possible | ed multiplicatio<br>in the contents<br>bit literal 'k'. Th<br>aced in PRODH<br>ir. PRODH con<br>unchanged.<br>e status flags a<br>either overflow<br>in this operatio<br>ssible, but not | of WREG<br>e 16-bit<br>H:PRODL<br>atains the<br>are affected.<br>v, nor carry<br>on. A zero | Descr  | Description:                                                                                    |                                         | An unsigned multiplication is carried<br>out between the contents of WREG<br>and the register file location 'f'. The<br>16-bit result is stored in the<br>PRODH:PRODL register pair.<br>PRODH contains the high byte.<br>Both WREG and 'f' are unchanged.<br>None of the status flags are affected<br>Note that neither overflow, nor carry<br>is possible in this operation. A zero<br>result is possible, but not detected. |        | f WREG<br>a'r'. The<br>air.<br>byte.<br>hanged.<br>e affected.<br>nor carry<br>. A zero |

| Words:                                                                            | 1                                                                                                                                 |                                                                                                                                                                                          |                                                                                             | Words  | 3:                                                                                              | 1                                       |                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                                                                                         |

| Cycles:                                                                           | 1                                                                                                                                 |                                                                                                                                                                                          |                                                                                             | Cycle  | s:                                                                                              | 1                                       |                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                                                                                         |

| Q Cycle Activity:                                                                 |                                                                                                                                   |                                                                                                                                                                                          |                                                                                             | Q Cyc  | le Activity:                                                                                    |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                                                                                         |

| Q1                                                                                | Q2                                                                                                                                | Q3                                                                                                                                                                                       | Q4                                                                                          |        | Q1                                                                                              | Q2                                      | Q3                                                                                                                                                                                                                                                                                                                                                                                                                            |        | Q4                                                                                      |

| Decode                                                                            | Read<br>literal 'k'                                                                                                               | Process<br>Data                                                                                                                                                                          | Write<br>registers<br>PRODH:<br>PRODL                                                       |        | Decode                                                                                          | Read<br>register 'f'                    | Proce<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                 |        | Write<br>registers<br>PRODH:<br>PRODL                                                   |