Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

|                            |                                                                            |

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 8MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 66                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 902 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | A/D 16x10b                                                                 |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 84-LCC (J-Lead)                                                            |

| Supplier Device Package    | 84-PLCC (29.31x29.31)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17lc766t-08-l |

#### **Table of Contents**

| 1.0        | Overview                                                                | 7   |

|------------|-------------------------------------------------------------------------|-----|

| 2.0        | Device Varieties                                                        |     |

| 3.0        | Architectural Overview                                                  | 11  |

| 4.0        | On-chip Oscillator Circuit                                              | 17  |

| 5.0        | Reset                                                                   | 23  |

| 6.0        | Interrupts                                                              | 33  |

| 7.0        | Memory Organization                                                     | 43  |

| 8.0        | Table Reads and Table Writes                                            | 59  |

| 9.0        | Hardware Multiplier                                                     | 67  |

| 10.0       | I/O Ports                                                               |     |

| 11.0       | Overview of Timer Resources                                             | 95  |

| 12.0       | Timer0                                                                  | 97  |

| 13.0       | Timer1, Timer2, Timer3, PWMs and Captures                               |     |

| 14.0       | Universal Synchronous Asynchronous Receiver Transmitter (USART) Modules | 117 |

| 15.0       | Master Synchronous Serial Port (MSSP) Module                            | 133 |

| 16.0       | Analog-to-Digital Converter (A/D) Module                                | 179 |

| 17.0       | Special Features of the CPU                                             | 191 |

| 18.0       | Instruction Set Summary                                                 | 197 |

| 19.0       | Development Support                                                     | 233 |

| 20.0       | PIC17C7XX Electrical Characteristics                                    | 239 |

| 21.0       | PIC17C7XX DC and AC Characteristics                                     | 267 |

| 22.0       | Packaging Information                                                   | 281 |

| Appendix . | A: Modifications                                                        | 287 |

| Appendix   | B: Compatibility                                                        | 287 |

| Appendix   | C: What's New                                                           | 288 |

| Appendix   | D: What's Changed                                                       | 288 |

|            |                                                                         |     |

| On-Line S  | upport                                                                  | 299 |

| Reader Re  | esponse                                                                 | 300 |

| Droduct Id | antification System                                                     | 201 |

#### REGISTER 6-3: PIE2 REGISTER (ADDRESS: 11h, BANK 4)

| R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----|-------|-------|-------|-------|

| SSPIE | BCLIE | ADIE  | -   | CA4IE | CA3IE | TX2IE | RC2IE |

|       |       |       |     |       |       |       |       |

bit 7 bit 0

bit 7 SSPIE: Synchronous Serial Port Interrupt Enable bit

1 = Enable SSP interrupt

0 = Disable SSP interrupt

bit 6 BCLIE: Bus Collision Interrupt Enable bit

1 = Enable bus collision interrupt

0 = Disable bus collision interrupt

bit 5 ADIE: A/D Module Interrupt Enable bit

1 = Enable A/D module interrupt

0 = Disable A/D module interrupt

bit 4 Unimplemented: Read as '0'

bit 3 CA4IE: Capture4 Interrupt Enable bit

1 = Enable Capture4 interrupt

0 = Disable Capture4 interrupt

bit 2 CA3IE: Capture3 Interrupt Enable bit

1 = Enable Capture3 interrupt

0 = Disable Capture3 interrupt

bit 1 TX2IE: USART2 Transmit Interrupt Enable bit

1 = Enable USART2 Transmit buffer empty interrupt

0 = Disable USART2 Transmit buffer empty interrupt

bit 0 RC2IE: USART2 Receive Interrupt Enable bit

1 = Enable USART2 Receive buffer full interrupt

0 = Disable USART2 Receive buffer full interrupt

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR Reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### 7.3 Stack Operation

PIC17C7XX devices have a 16 x 16-bit hardware stack (Figure 7-1). The stack is not part of either the program or data memory space, and the stack pointer is neither readable nor writable. The PC (Program Counter) is "PUSH'd" onto the stack when a CALL or LCALL instruction is executed, or an interrupt is acknowledged. The stack is "POP'd" in the event of a RETURN, RETLW, or a RETFIE instruction execution. PCLATH is not affected by a "PUSH" or a "POP" operation.

The stack operates as a circular buffer, with the stack pointer initialized to '0' after all RESETS. There is a stack available bit (STKAV) to allow software to ensure that the stack will not overflow. The STKAV bit is set after a device RESET. When the stack pointer equals Fh, STKAV is cleared. When the stack pointer rolls over from Fh to 0h, the STKAV bit will be held clear until a device RESET.

- Note 1: There is not a status bit for stack underflow. The STKAV bit can be used to detect the underflow which results in the stack pointer being at the Top-of-Stack.

- 2: There are no instruction mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt vector.

- 3: After a RESET, if a "POP" operation occurs before a "PUSH" operation, the STKAV bit will be cleared. This will appear as if the stack is full (underflow has occurred). If a "PUSH" operation occurs next (before another "POP"), the STKAV bit will be locked clear. Only a device RESET will cause this bit to set.

After the device is "PUSH'd" sixteen times (without a "POP"), the seventeenth push overwrites the value from the first push. The eighteenth push overwrites the second push (and so on).

#### 7.4 Indirect Addressing

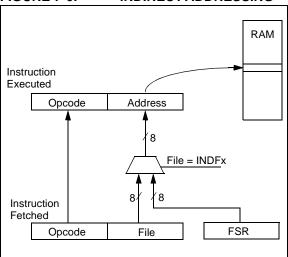

Indirect addressing is a mode of addressing data memory where the data memory address in the instruction is not fixed. That is, the register that is to be read or written can be modified by the program. This can be useful for data tables in the data memory. Figure 7-6 shows the operation of indirect addressing. This depicts the moving of the value to the data memory address specified by the value of the FSR register.

Example 7-1 shows the use of indirect addressing to clear RAM in a minimum number of instructions. A similar concept could be used to move a defined number of bytes (block) of data to the USART transmit register (TXREG). The starting address of the block of data to be transmitted could easily be modified by the program.

FIGURE 7-6: INDIRECT ADDRESSING

### 7.4.1 INDIRECT ADDRESSING REGISTERS

The PIC17C7XX has four registers for indirect addressing. These registers are:

- INDF0 and FSR0

- INDF1 and FSR1

Registers INDF0 and INDF1 are not physically implemented. Reading or writing to these registers activates indirect addressing, with the value in the corresponding FSR register being the address of the data. The FSR is an 8-bit register and allows addressing anywhere in the 256-byte data memory address range. For banked memory, the bank of memory accessed is specified by the value in the BSR.

If file INDF0 (or INDF1) itself is read indirectly via an FSR, all '0's are read (Zero bit is set). Similarly, if INDF0 (or INDF1) is written to indirectly, the operation will be equivalent to a NOP, and the status bits are not affected.

Example 9-4 shows the sequence to do a 16 x 16 signed multiply. Equation 9-2 shows the algorithm used. The 32-bit result is stored in four registers, RES3:RES0. To account for the sign bits of the arguments, each argument pairs most significant bit (MSb) is tested and the appropriate subtractions are done.

# EQUATION 9-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

```

RES3:RES0

= ARG1H:ARG1L \bullet ARG2H:ARG2L

= (ARG1H \bullet ARG2H \bullet 2^{16}) + (ARG1H \bullet ARG2L \bullet 2^{8}) + (ARG1L \bullet ARG2H \bullet 2^{8}) + (ARG1L \bullet ARG2L) + (-1 \bullet ARG2H < 7 > \bullet ARG1H:ARG1L \bullet 2^{16}) + (-1 \bullet ARG1H < 7 > \bullet ARG2H:ARG2L \bullet 2^{16})

```

### EXAMPLE 9-4: 16 x 16 SIGNED MULTIPLY ROUTINE

```

MOVFP

ARG1L, WREG

MULWF

ARG2L ; ARG1L * ARG2L ->

; PRODH:PRODL

MOVPF

PRODH, RES1 ;

MOVPF

PRODL, RESO ;

MOVFP

ARG1H, WREG

ARG2H ; ARG1H * ARG2H ->

MULWF

; PRODH:PRODL

PRODH, RES3 ;

MOVPF

MOVPF

PRODL, RES2 ;

MOVFP

ARG1L, WREG

ARG2H ; ARG1L * ARG2H -> PRODH.PRODI.

MULWF

; PRODH: PRODL

MOVED

PRODL, WREG ;

RES1, F ; Add cross

ADDWF

MOVFP

PRODH, WREG ; products

RES2, F ;

ADDWFC

WREG, F

CLRF

ADDWFC

RES3, F

MOVFP

ARG1H, WREG ;

ARG2L ; ARG1H * ARG2L ->

MULWF

; PRODH:PRODL

PRODL, WREG ;

MOVFP

ADDWF

RES1, F ; Add cross

MOVFP

PRODH, WREG; products

ADDWFC RES2, F ;

CLRF

WREG, F

ADDWFC

RES3, F

BTFSS

ARG2H, 7 ; ARG2H:ARG2L neg? SIGN_ARG1 ; no, check ARG1

GOTO

ARG1L, WREG ;

MOVFP

SUBWF

RES2

MOVFP

ARG1H, WREG ;

SUBWFB

RES3

SIGN ARG1

ARG1H, 7 ; ARG1H:ARG1L neg? CONT_CODE ; no, done

BTFSS

GOTO

MOVFP

ARG2L, WREG ;

SUBWF

RES2

MOVFP

ARG2H, WREG ;

SUBWFB

RES3

CONT_CODE

:

```

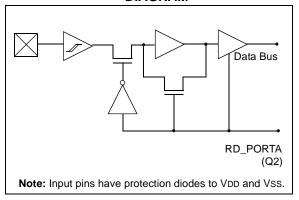

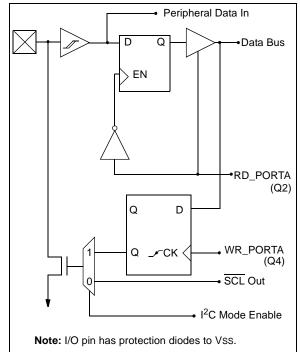

#### 10.1 PORTA Register

PORTA is a 6-bit wide latch. PORTA does not have a corresponding Data Direction Register (DDR). Upon a device RESET, the PORTA pins are forced to be himpedance inputs. For the RA4 and RA5 pins, the peripheral module controls the output. When a device RESET occurs, the peripheral module is disabled, so these pins are forced to be hi-impedance inputs.

Reading PORTA reads the status of the pins.

The RA0 pin is multiplexed with the external interrupt, INT. The RA1 pin is multiplexed with TMR0 clock input, RA2 and RA3 are multiplexed with the SSP functions, and RA4 and RA5 are multiplexed with the USART1 functions. The control of RA2, RA3, RA4 and RA5 as outputs, is automatically configured by their multiplexed peripheral module when the module is enabled.

#### 10.1.1 USING RA2, RA3 AS OUTPUTS

The RA2 and RA3 pins are open drain outputs. To use the RA2 and/or the RA3 pin(s) as output(s), simply write to the PORTA register the desired value. A '0' will cause the pin to drive low, while a '1' will cause the pin to float (hi-impedance). An external pull-up resistor should be used to pull the pin high. Writes to the RA2 and RA3 pins will not affect the other PORTA pins.

#### Note

When using the RA2 or RA3 pin(s) as output(s), read-modify-write instructions (such as BCF, BSF, BTG) on PORTA are not recommended.

Such operations read the port pins, do the desired operation, and then write this value to the data latch. This may inadvertently cause the RA2 or RA3 pins to switch from input to output (or vice-versa).

To avoid this possibility, use a shadow register for PORTA. Do the bit operations on this shadow register and then move it to PORTA.

Example 10-1 shows an instruction sequence to initialize PORTA. The Bank Select Register (BSR) must be selected to Bank 0 for the port to be initialized. The following example uses the MOVLB instruction to load the BSR register for bank selection.

#### **EXAMPLE 10-1: INITIALIZING PORTA**

MOVLB 0 ; Select Bank 0

MOVLW 0xF3 ;

MOVWF PORTA ; Initialize PORTA ; RA<3:2> are output low ; RA<5:4> and RA<1:0> ; are inputs ; (outputs floating)

### FIGURE 10-1: RA0 AND RA1 BLOCK DIAGRAM

#### FIGURE 10-2: RA2 BLOCK DIAGRAM

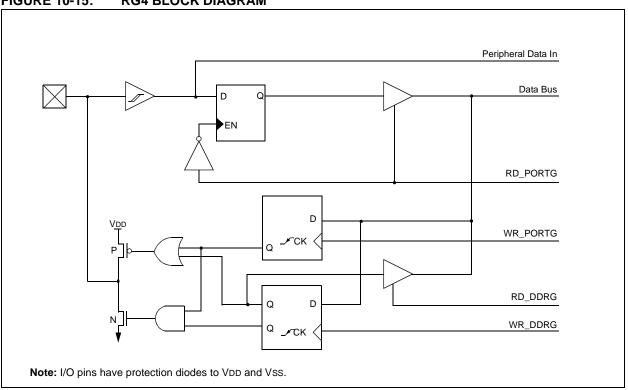

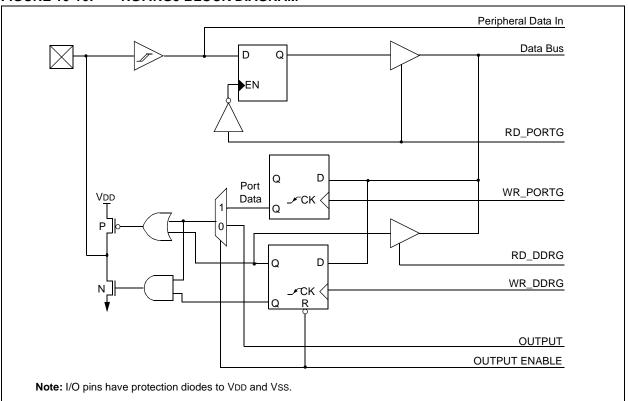

FIGURE 10-15: RG4 BLOCK DIAGRAM

FIGURE 10-16: RG7:RG5 BLOCK DIAGRAM

#### 13.1.3.1 PWM Periods

The period of the PWM1 output is determined by Timer1 and its period register (PR1). The period of the PWM2 and PWM3 outputs can be individually software configured to use either Timer1 or Timer2 as the time-base. For PWM2, when TM2PW2 bit (PW2DCL<5>) is clear, the time base is determined by TMR1 and PR1 and when TM2PW2 is set, the time base is determined by Timer2 and PR2. For PWM3, when TM2PW3 bit (PW3DCL<5>) is clear, the time base is determined by TMR1 and PR1, and when TM2PW3 is set, the time base is determined by Timer2 and PR2.

Running two different PWM outputs on two different timers allows different PWM periods. Running all PWMs from Timer1 allows the best use of resources by freeing Timer2 to operate as an 8-bit timer. Timer1 and Timer2 cannot be used as a 16-bit timer if any PWM is being used.

The PWM periods can be calculated as follows:

period of PWM1 =

$$[(PR1) + 1] \times 4Tosc$$

period of PWM2 =  $[(PR1) + 1] \times 4Tosc$  or  $[(PR2) + 1] \times 4Tosc$

period of PWM3 =  $[(PR1) + 1] \times 4Tosc$  or  $[(PR2) + 1] \times 4Tosc$

The duty cycle of PWMx is determined by the 10-bit value DCx<9:0>. The upper 8-bits are from register PWxDCH and the lower 2-bits are from PWxDCL<7:6> (PWxDCH:PWxDCL<7:6>). Table 13-4 shows the maximum PWM frequency (FPWM), given the value in the period register.

The number of bits of resolution that the PWM can achieve depends on the operation frequency of the device as well as the PWM frequency (FPWM).

Maximum PWM resolution (bits) for a given PWM frequency:

$$= \frac{\log\left(\frac{Fosc}{Fpwm}\right)}{\log(2)} \quad bits$$

where: FPWM = 1 / period of PWM

The PWMx duty cycle is as follows:

PWMx Duty Cycle =

$$(DCx) x TOSC$$

where DCx represents the 10-bit value from PWxDCH:PWxDCL.

If DCx = 0, then the duty cycle is zero. If PRx = PWxDCH, then the PWM output will be low for one to four Q-clocks (depending on the state of the PWxDCL<7:6> bits). For a duty cycle to be 100%, the PWxDCH value must be greater then the PRx value.

The duty cycle registers for both PWM outputs are double buffered. When the user writes to these registers, they are stored in master latches. When TMR1 (or TMR2) overflows and a new PWM period begins, the master latch values are transferred to the slave latches and the PWMx pin is forced high.

| Note: | For PW1DCH, PW1DCL, PW2DCH,                   |

|-------|-----------------------------------------------|

|       | PW2DCL, PW3DCH and PW3DCL regis-              |

|       | ters, a write operation writes to the "master |

|       | latches", while a read operation reads the    |

|       | "slave latches". As a result, the user may    |

|       | not read back what was just written to the    |

|       | duty cycle registers (until transferred to    |

|       | slave latch).                                 |

The user should also avoid any "read-modify-write" operations on the duty cycle registers, such as: ADDWF PW1DCH. This may cause duty cycle outputs that are unpredictable.

TABLE 13-4: PWM FREQUENCY vs. RESOLUTION AT 33 MHz

| PWM                    |        | Fre   | equency | (kHz) |       |

|------------------------|--------|-------|---------|-------|-------|

| Frequency              | 32.2   | 64.5  | 90.66   | 128.9 | 515.6 |

| PRx Value              | 0xFF   | 0x7F  | 0x5A    | 0x3F  | 0x0F  |

| High<br>Resolution     | 10-bit | 9-bit | 8.5-bit | 8-bit | 6-bit |

| Standard<br>Resolution | 8-bit  | 7-bit | 6.5-bit | 6-bit | 4-bit |

#### 13.1.3.2 PWM INTERRUPTS

The PWM modules make use of the TMR1 and/or TMR2 interrupts. A timer interrupt is generated when TMR1 or TMR2 equals its period register and on the following increment is cleared to zero. This interrupt also marks the beginning of a PWM cycle. The user can write new duty cycle values before the timer rollover. The TMR1 interrupt is latched into the TMR1IF bit and the TMR2 interrupt is latched into the TMR2IF bit. These flags must be cleared in software.

### 13.2.3 READING THE CAPTURE REGISTERS

The Capture overflow status flag bits are double buffered. The master bit is set if one captured word is already residing in the Capture register and another "event" has occurred on the CAPx pin. The new event will not transfer the TMR3 value to the capture register, protecting the previous unread capture value. When the user reads both the high and the low bytes (in any

order) of the Capture register, the master overflow bit is transferred to the slave overflow bit (CAxOVF) and then the master bit is reset. The user can then read TCONx to determine the value of CAxOVF.

An example of an instruction sequence to read capture registers and capture overflow flag bits is shown in Example 13-1. Depending on the capture source, different registers will need to be read.

#### **EXAMPLE 13-1: SEQUENCE TO READ CAPTURE REGISTERS**

```

MOVLB 3 ; Select Bank 3

MOVPF CA2L, LO_BYTE ; Read Capture2 low byte, store in LO_BYTE

MOVPF CA2H, HI_BYTE ; Read Capture2 high byte, store in HI_BYTE

MOVPF TCON2, STAT_VAL ; Read TCON2 into file STAT_VAL

```

#### TABLE 13-6: REGISTERS ASSOCIATED WITH CAPTURE

| Address       | Name      | Bit 7     | Bit 6                        | Bit 5         | Bit 4         | Bit 3        | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR,<br>BOR | MCLR, WDT |

|---------------|-----------|-----------|------------------------------|---------------|---------------|--------------|--------|--------|-----------|-------------------------|-----------|

| 16h, Bank 3   | TCON1     | CA2ED1    | CA2ED0                       | CA1ED1        | CA1ED0        | T16          | TMR3CS | TMR2CS | TMR1CS    | 0000 0000               | 0000 0000 |

| 17h, Bank 3   | TCON2     | CA2OVF    | CA10VF                       | PWM2ON        | PWM1ON        | CA1/PR3      | TMR3ON | TMR2ON | TMR10N    | 0000 0000               | 0000 0000 |

| 16h, Bank 7   | TCON3     | _         | CA4OVF                       | CA3OVF        | CA4ED1        | CA4ED0       | CA3ED1 | CA3ED0 | PWM3ON    | -000 0000               | -000 0000 |

| 12h, Bank 2   | TMR3L     | Holding R | egister for t                | he Low Byte   | of the 16-bit | TMR3 Reg     | ister  |        |           | xxxx xxxx               | uuuu uuuu |

| 13h, Bank 2   | TMR3H     | Holding R | egister for t                | he High Byte  | of the 16-bit | TMR3 Reg     | gister |        |           | xxxx xxxx               | uuuu uuuu |

| 16h, Bank 1   | PIR1      | RBIF      | TMR3IF                       | TMR2IF        | TMR1IF        | CA2IF        | CA1IF  | TX1IF  | RC1IF     | x000 0010               | u000 0010 |

| 17h, Bank 1   | PIE1      | RBIE      | TMR3IE                       | TMR2IE        | TMR1IE        | CA2IE        | CA1IE  | TX1IE  | RC1IE     | 0000 0000               | 0000 0000 |

| 10h, Bank 4   | PIR2      | SSPIF     | BCLIF                        | ADIF          | _             | CA4IF        | CA3IF  | TX2IF  | RC2IF     | 000- 0010               | 000- 0010 |

| 11h, Bank 4   | PIE2      | SSPIE     | BCLIE                        | ADIE          | _             | CA4IE        | CA3IE  | TX2IE  | RC2IE     | 000- 0000               | 000- 0000 |

| 07h, Unbanked | INTSTA    | PEIF      | T0CKIF                       | T0IF          | INTF          | PEIE         | T0CKIE | TOIE   | INTE      | 0000 0000               | 0000 0000 |

| 06h, Unbanked | CPUSTA    | _         |                              | STKAV         | GLINTD        | TO           | PD     | POR    | BOR       | 11 11qq                 | 11 qquu   |

| 16h, Bank 2   | PR3L/CA1L | Timer3 Pe | riod Regist                  | er, Low Byte/ | Capture1 Re   | gister, Low  | Byte   |        |           | xxxx xxxx               | uuuu uuuu |

| 17h, Bank 2   | PR3H/CA1H | Timer3 Pe | riod Regist                  | er, High Byte | /Capture1 Re  | egister, Hig | h Byte |        |           | xxxx xxxx               | uuuu uuuu |

| 14h, Bank 3   | CA2L      | Capture2  | Low Byte                     |               |               |              |        |        |           | xxxx xxxx               | uuuu uuuu |

| 15h, Bank 3   | CA2H      | Capture2  | High Byte                    |               |               |              |        |        |           | xxxx xxxx               | uuuu uuuu |

| 12h, Bank 7   | CA3L      | Capture3  | Capture3 Low Byte xxx        |               |               |              |        |        | xxxx xxxx | uuuu uuuu               |           |

| 13h, Bank 7   | CA3H      | Capture3  | Capture3 High Byte xxxx xxxx |               |               |              |        |        | xxxx xxxx | uuuu uuuu               |           |

| 14h, Bank 7   | CA4L      | Capture4  | Low Byte                     |               |               |              |        |        |           | xxxx xxxx               | uuuu uuuu |

| 15h, Bank 7   | CA4H      | Capture4  | High Byte                    |               |               |              |        |        |           | xxxx xxxx               | uuuu uuuu |

Legend:  $x = unknown, \ u = unchanged, - = unimplemented, read as '0', \ q = value depends on condition. Shaded cells are not used by Capture.$

#### 14.2 USART Asynchronous Mode

In this mode, the USART uses standard nonreturn-to-zero (NRZ) format (one START bit, eight or nine data bits, and one STOP bit). The most common data format is 8-bits. An on-chip dedicated 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART's transmitter and receiver are functionally independent but use the same data format and baud rate. The baud rate generator produces a clock x64 of the bit shift rate. Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

The Asynchronous mode is selected by clearing the SYNC bit (TXSTA<4>).

The USART Asynchronous module consists of the following components:

- · Baud Rate Generator

- · Sampling Circuit

- · Asynchronous Transmitter

- · Asynchronous Receiver

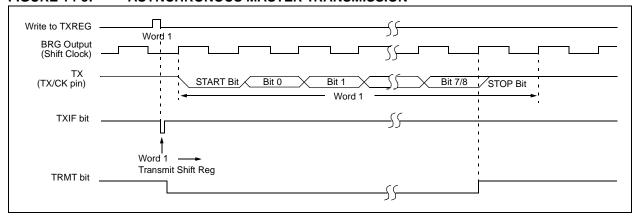

### 14.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 14-1. The heart of the transmitter is the transmit shift register (TSR). The shift register obtains its data from the read/write transmit buffer (TXREG). TXREG is loaded with data in software. The TSR is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once TXREG transfers the data to the TSR (occurs in one Tcy at the end of the current BRG cycle), the TXREG is empty and an interrupt bit, TXIF, is set. This interrupt can be enabled/disabled by setting/clearing the TXIE bit. TXIF will be set, regardless of TXIE and cannot be reset in software. It will reset only when new data is loaded into TXREG. While TXIF indicates the status of the TXREG, the TRMT (TXSTA<1>) bit shows the status of the TSR.

TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR is empty.

**Note:** The TSR is not mapped in data memory, so it is not available to the user.

Transmission enabled bv settina TXEN (TXSTA<5>) bit. The actual transmission will not occur until TXREG has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 14-3). The transmission can also be started by first loading TXREG and then setting TXEN. Normally, when transmission is first started, the TSR is empty, so a transfer to TXREG will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 14-4). Clearing TXEN during a transmission will cause the transmission to be aborted. This will reset the transmitter and the TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit value should be written to TX9D (TXSTA<0>). The ninth bit value must be written before writing the 8-bit data to the TXREG. This is because a data write to TXREG can result in an immediate transfer of the data to the TSR (if the TSR is empty).

Steps to follow when setting up an Asynchronous Transmission:

- Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the TXIE bit.

- 4. If 9-bit transmission is desired, then set the TX9 bit.

- 5. If 9-bit transmission is selected, the ninth bit should be loaded in TX9D.

- 6. Load data to the TXREG register.

- 7. Enable the transmission by setting TXEN (starts transmission).

#### 15.4 Example Program

Example 15-2 shows MPLAB® C17 'C' code for using the I<sup>2</sup>C module in Master mode to communicate with a 24LC01B serial EEPROM. This example uses the PIC® MCU 'C' libraries included with MPLAB C17.

#### EXAMPLE 15-2: INTERFACING TO A 24LC01B SERIAL EEPROM (USING MPLAB C17)

```

// Include necessary header files

#include <p17c756.h>

// Processor header file

// Delay routines header file

// Standard Library header file

#include <delays.h>

#include <stdlib.h>

// Stanuaru Bleen.

// I2C routines header file

#include <i2c16.h>

#define CONTROL 0xa0

// Control byte definition for 24LC01B

// Function declarations

void main(void);

void WritePORTD(static unsigned char data);

void ByteWrite(static unsigned char address, static unsigned char data);

unsigned char ByteRead(static unsigned char address);

void ACKPoll(void);

// Main program

void main(void)

static unsigned char address; // I2C address of 24LC01B

static unsigned char datao; \hspace{0.2in} // Data written to 24LC01B

static unsigned char datai;

// Data read from 24LC01B

// Preset address to 0

address = 0;

OpenI2C(MASTER,SLEW_ON);

\ensuremath{//} Configure I2C Module Master mode, Slew rate control on

SSPADD = 39;

// Configure clock for 100KHz

while(address<128)

// Loop 128 times, 24LC01B is 128x8

datao = PORTB:

do

ByteWrite(address, datao); // Write data to EEPROM

ACKPoll();

// Poll the 24LC01B for state

datai = ByteRead(address); // Read data from EEPROM into SSPBUF

} while(datai != datao);

// Loop as long as data not correctly

written to 24LC01B

address++:

// Increment address

}

while(1)

// Done writing 128 bytes to 24LC01B, Loop forever

{

Nop();

}

```

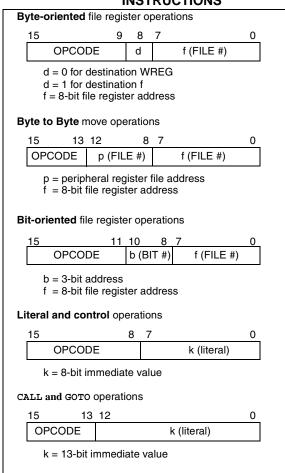

Table 18-2 lists the instructions recognized by the MPASM assembler.

**Note 1:** Any unused opcode is Reserved. Use of any reserved opcode may cause unexpected operation.

All instruction examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

To represent a binary number:

0000 0100b

where b signifies a binary string.

### FIGURE 18-1: GENERAL FORMAT FOR INSTRUCTIONS

### 18.1 Special Function Registers as Source/Destination

The PIC17C7XX's orthogonal instruction set allows read and write of all file registers, including special function registers. There are some special situations the user should be aware of:

#### 18.1.1 ALUSTA AS DESTINATION

If an instruction writes to ALUSTA, the Z, C, DC and OV bits may be set or cleared as a result of the instruction and overwrite the original data bits written. For example, executing CLRF ALUSTA will clear register ALUSTA and then set the Z bit leaving 0000 0100b in the register.

#### 18.1.2 PCL AS SOURCE OR DESTINATION

Read, write or read-modify-write on PCL may have the following results:

Read PC:  $PCH \rightarrow PCLATH$ ;  $PCL \rightarrow dest$

Write PCL: PCLATH  $\rightarrow$  PCH;

8-bit destination value → PCL

Read-Modify-Write: PCL→ ALU operand

PCLATH → PCH; 8-bit result → PCL

Where PCH = program counter high byte (not an addressable register), PCLATH = Program counter high holding latch, dest = destination, WREG or f.

#### 18.1.3 BIT MANIPULATION

All bit manipulation instructions are done by first reading the entire register, operating on the selected bit and writing the result back (read-modify-write (R-M-W)). The user should keep this in mind when operating on some special function registers, such as ports.

Note: Status bits that are manipulated by the device (including the interrupt flag bits) are set or cleared in the Q1 cycle. So, there is no issue on doing R-M-W instructions on registers which contain these bits

**DECF** Decrement f Syntax: [label] DECF f,d Operands:  $0 \leq f \leq 255$  $d \in [0,1]$ Operation:  $(f) - 1 \rightarrow (dest)$ Status Affected: OV, C, DC, Z Encoding: 0000 011d ffff ffff Description: Decrement register 'f'. If 'd' is 0, the result is stored in WREG. If 'd' is 1, the result is stored back in register 'f'.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2                   | Q3              | Q4                   |

|--------|----------------------|-----------------|----------------------|

| Decode | Read<br>register 'f' | Process<br>Data | Write to destination |

Example: DECF CNT, 1

Before Instruction

$\begin{array}{rcl} \mathsf{CNT} & = & \mathsf{0x01} \\ \mathsf{Z} & = & \mathsf{0} \end{array}$

After Instruction

$\begin{array}{ccc} CNT & = & 0x00 \\ Z & = & 1 \end{array}$

| DECFSZ           | Decreme                                                                                                                    | ent f, ski | ip if 0 |           |

|------------------|----------------------------------------------------------------------------------------------------------------------------|------------|---------|-----------|

| Syntax:          | [ label ]                                                                                                                  | DECFS      | Z f,d   |           |

| Operands:        | $0 \le f \le 25$ $d \in [0,1]$                                                                                             | 55         |         |           |

| Operation:       | (f) $-1 \rightarrow (dest)$ ;<br>skip if result = 0                                                                        |            |         |           |

| Status Affected: | None                                                                                                                       |            |         |           |

| Encoding:        | 0001                                                                                                                       | 011d       | ffff    | ffff      |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in WREG. If 'd' is 1, the result is placed |            |         | placed in |

back in register 'f'. If the result is 0, the next instruction, which is already fetched is discarded and a  $\mathtt{NOP}$  is executed instead, making

it a two-cycle instruction.

Words: 1 Cycles: 1(2)

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4          |

|--------|--------------|---------|-------------|

| Decode | Read         | Process | Write to    |

|        | register 'f' | Data    | destination |

If skip:

| Q1        | Q2        | Q3        | Q4        |

|-----------|-----------|-----------|-----------|

| No        | No        | No        | No        |

| operation | operation | operation | operation |

Example: HERE DECFSZ CNT, 1

GOTO HERE

NZERO ZERO

Before Instruction

PC = Address (HERE)

After Instruction

CNT = CNT - 1If CNT = 0;

PC = Address (HERE)

If CNT  $\neq$  0;

PC = Address (NZERO)

Move Literal to high nibble in **BSR**

Syntax: [label] MOVLR k

Operation:  $k \rightarrow (BSR < 7:4>)$

Status Affected: None

**MOVLR**

Operands:

Encoding: 1011 101x kkkk uuuu

$0 \le k \le 15$

Description: The 4-bit literal 'k' is loaded into the most significant 4-bits of the Bank Select Register (BSR). Only the high 4-bits of the Bank Select Register are affected. The lower half of the

BSR is unchanged. The assembler will encode the "u" fields as 0.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4             |

|--------|--------------|---------|----------------|

| Decode | Read literal | Process | Write          |

|        | 'k'          | Data    | literal 'k' to |

|        |              |         | BSR<7:4>       |

Example: MOVLR

**Before Instruction**

BSR register = 0x22

After Instruction

BSR register = 0x52

| MOVEW Move Literal to WREG | MOVLW | Move Literal to WREG |

|----------------------------|-------|----------------------|

|----------------------------|-------|----------------------|

Syntax: [label] MOVLW k

Operands:  $0 \le k \le 255$ Operation:  $k \rightarrow (WREG)$

Status Affected: None

Encoding: 1011 0000 kkkk kkkk

Description: The eight-bit literal 'k' is loaded into

WREG.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2          | Q3      | Q4       |

|--------|-------------|---------|----------|

| Decode | Read        | Process | Write to |

|        | literal 'k' | Data    | WREG     |

Example: MOVLW 0x5A

After Instruction

WREG 0x5A

#### 19.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- · Integrated Development Environment

- MPLAB® IDE Software

- · Assemblers/Compilers/Linkers

- MPASM<sup>TM</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK™ Object Linker/ MPLIB™ Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC™ In-Circuit Emulator

- · In-Circuit Debugger

- MPLAB ICD for PIC16F87X

- · Device Programmers

- PRO MATE® II Universal Device Programmer

- PICSTART® Plus Entry-Level Development Programmer

- · Low Cost Demonstration Boards

- PICDEM™ 1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ® Demonstration Board

### 19.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows®-based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- · A full-featured editor

- · A project manager

- Customizable toolbar and key mapping

- · A status bar

- · On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- · Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the cost-effective simulator to a full-featured emulator with minimal retraining.

#### 19.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCU's.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- · Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process.

### 19.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

20.2 DC Characteristics: PIC17C7XX-16 (Commercial, Industrial, Extended)

PIC17C7XX-33 (Commercial, Industrial, Extended)

PIC17LC7XX-08 (Commercial, Industrial)

Standard Operating Conditions (unless otherwise stated)

Operating temperature

DC CHARACTERISTICS -40°C ≤ TA ≤ +125°C for extended

-40°C  $\leq$  TA  $\leq$  +85°C for industrial 0°C  $\leq$  TA  $\leq$  +70°C for commercial

Operating voltage VDD range as described in Section 20.1

| Param.<br>No. | Sym  | Characteristic              | Min      | Typ†   | Max    | Units | Conditions                     |

|---------------|------|-----------------------------|----------|--------|--------|-------|--------------------------------|

|               |      | Input Low Voltage           |          |        |        |       |                                |

|               | VIL  | I/O ports                   |          |        |        |       |                                |

| D030          |      | with TTL buffer (Note 6)    | Vss      | _      | 0.8    | V     | $4.5V \le VDD \le 5.5V$        |

|               |      | ,                           | Vss      | _      | 0.2Vdd | V     | $3.0 V \leq V_{DD} \leq 4.5 V$ |

| D031          |      | with Schmitt Trigger buffer |          |        |        |       |                                |

|               |      | RA2, RA3                    | Vss      | _      | 0.3Vdd | V     | I <sup>2</sup> C compliant     |

|               |      | All others                  | Vss      | -      | 0.2Vdd | V     |                                |

| D032          |      | MCLR, OSC1 (in EC and RC    | Vss      | _      | 0.2Vdd | V     | (Note 1)                       |

|               |      | mode)                       |          |        |        |       |                                |

| D033          |      | OSC1 (in XT, and LF mode)   | _        | 0.5VDD | _      | V     |                                |

|               |      | Input High Voltage          |          |        |        |       |                                |

|               | VIH  | I/O ports                   |          |        |        |       |                                |

| D040          |      | with TTL buffer (Note 6)    | 2.0      | _      | VDD    | V     | $4.5V \le VDD \le 5.5V$        |

|               |      |                             | 1+0.2VDD | _      | Vdd    | V     | $3.0V \le VDD \le 4.5V$        |

| D041          |      | with Schmitt Trigger buffer |          |        |        |       |                                |

|               |      | RA2, RA3                    | 0.7Vdd   | _      | Vdd    | V     | I <sup>2</sup> C compliant     |

|               |      | All others                  | 0.8VDD   | -      | Vdd    | V     |                                |

| D042          |      | MCLR                        | 0.8VDD   | _      | VDD    | V     | (Note 1)                       |

| D043          |      | OSC1 (XT, and LF mode)      | _        | 0.5VDD | -      | V     |                                |

| D050          | VHYS | Hysteresis of               | 0.15VDD  | _      | -      | V     |                                |

|               |      | Schmitt Trigger Inputs      |          |        |        |       |                                |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated.

- **Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC17CXXX devices be driven with external clock in RC mode.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- **4:** These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17C7XX Programming Specifications (Literature number DS TBD).

- 5: The MCLR/VPP pin may be kept in this range at times other than programming, but is not recommended.

- 6: For TTL buffers, the better of the two specifications may be used.

#### 20.4 Timing Diagrams and Specifications

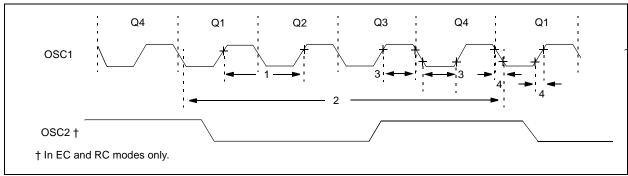

FIGURE 20-6: EXTERNAL CLOCK TIMING

TABLE 20-1: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic         | Min   | Тур†   | Max   | Units | Conditions                               |

|--------------|-------|------------------------|-------|--------|-------|-------|------------------------------------------|

|              | Fosc  | External CLKIN         | DC    | _      | 8     | MHz   | EC osc mode - 08 devices (8 MHz devices) |

|              |       | Frequency (Note 1)     | DC    | _      | 16    | MHz   | - 16 devices (16 MHz devices)            |

|              |       |                        | DC    | _      | 33    | MHz   | - 33 devices (33 MHz devices)            |

|              |       | Oscillator Frequency   | DC    | _      | 4     | MHz   | RC osc mode                              |

|              |       | (Note 1)               | 2     |        | 8     | MHz   | XT osc mode - 08 devices (8 MHz devices) |

|              |       |                        | 2     | _      | 16    | MHz   | - 16 devices (16 MHz devices)            |

|              |       |                        | 2     | _      | 33    | MHz   | - 33 devices (33 MHz devices)            |

|              |       |                        | DC    | —      | 2     | MHz   | LF osc mode                              |

| 1            | Tosc  | External CLKIN Period  | 125   |        | _     | ns    | EC osc mode - 08 devices (8 MHz devices) |

|              |       | (Note 1)               | 62.5  | _      | _     | ns    | - 16 devices (16 MHz devices)            |

|              |       |                        | 30.3  | _      | _     | ns    | - 33 devices (33 MHz devices)            |

|              |       | Oscillator Period      | 250   | 1      | _     | ns    | RC osc mode                              |

|              |       | (Note 1)               | 125   | _      | 1,000 | ns    | XT osc mode - 08 devices (8 MHz devices) |

|              |       |                        | 62.5  | _      | 1,000 | ns    | - 16 devices (16 MHz devices)            |

|              |       |                        | 30.3  | _      | 1,000 | ns    | - 33 devices (33 MHz devices)            |

|              |       |                        | 500   | _      | _     | ns    | LF osc mode                              |

| 2            | TCY   | Instruction Cycle Time | 121.2 | 4/Fosc | DC    | ns    |                                          |

|              |       | (Note 1)               |       |        |       |       |                                          |

| 3            | TosL, | Clock in (OSC1)        | 10    |        | _     | ns    | EC oscillator                            |

|              | TosH  | High or Low Time       |       |        |       |       |                                          |

| 4            | TosR, | Clock in (OSC1)        | _     | _      | 5     | ns    | EC oscillator                            |

|              | TosF  | Rise or Fall Time      |       |        |       |       |                                          |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

| Bus Collision During a RESTART Condition | 173    | Configuration                              |                                         |

|------------------------------------------|--------|--------------------------------------------|-----------------------------------------|

| Bus Collision During a START Condition   | 171    | Bits                                       | 192                                     |

| Bus Collision During a STOP Condition    | 174    | Locations                                  | 192                                     |

| Bus Collision Interrupt Enable, BCLIE    | 36     | Oscillator                                 | 17, 192                                 |

| Bus Collision Interrupt Flag bit, BCLIF  | 38     | Word                                       | 191                                     |

| C                                        |        | CPFSEQ                                     | 209                                     |

| C                                        | 11, 51 | CPFSGT                                     | 209                                     |

| CA1/PR3                                  | 102    | CPFSLT                                     | 210                                     |

| CA1ED0                                   | 101    | CPUSTA                                     | 52, 194                                 |

| CA1ED1                                   | 101    | Crystal Operation, Overtone Crystals       | 18                                      |

| CA1IE                                    | 35     | Crystal or Ceramic Resonator Operation     | 18                                      |

| CA1IF                                    | 37     | Crystal Oscillator                         | 17                                      |

| CA1OVF                                   | 102    | D                                          |                                         |

| CA2ED0                                   | 101    | D/Ā                                        | 134                                     |

| CA2ED1                                   | 101    | Data Memory                                |                                         |

| CA2H                                     |        | GPR                                        | 43, 46                                  |

| CA2IE                                    | *      | Indirect Addressing                        | ,                                       |

| CA2IF                                    | ,      | Organization                               |                                         |

| CA2L                                     | ,      | SFR                                        |                                         |

| CA2OVF                                   | ,      | Data Memory Banking                        |                                         |

| CA3H                                     |        | Data/Address bit, D/A                      |                                         |

| CA3IE                                    |        | DAW                                        |                                         |

| CA3IF                                    |        | DC                                         |                                         |

| CA3L                                     |        | DDRB                                       | ,                                       |

| CA4H                                     |        | DDRC                                       | , -,                                    |

| CA4IE                                    |        | DDRD                                       |                                         |

| CA4IF                                    |        | DDRE                                       | -, -, -                                 |

| Calculating Baud Rate Error              |        | DDRF                                       | , ,                                     |

| CALL                                     |        | DDRG                                       |                                         |

| Capacitor Selection                      |        | DECF                                       | • • • • • • • • • • • • • • • • • • • • |

| Ceramic Resonators                       | 18     | DECFSNZ                                    |                                         |

| Crystal Oscillator                       |        | DECFSZ                                     |                                         |

| Capture                                  |        | Delay From External Clock Edge             |                                         |

| Capture Sequence to Read Example         |        | Digit Borrow                               |                                         |

| Capture1                                 | 110    | Digit Carry (DC)                           |                                         |

| Mode                                     | 101    | Duty Cycle                                 |                                         |

| Overflow                                 |        | F                                          | 107                                     |

| Capture1 Interrupt                       | ,      | Electrical Characteristics                 |                                         |

| Capture2                                 |        | PIC17C752/756                              |                                         |

| Mode                                     | 101    | Absolute Maximum Ratings                   | 230                                     |

| Overflow                                 |        | Capture Timing                             |                                         |

| Capture2 Interrupt                       | - ,    | CLKOUT and I/O Timing                      |                                         |

| Capture3 Interrupt Enable, CA3IE         |        | DC Characteristics                         |                                         |

| Capture3 Interrupt Flag bit, CA3IF       |        | External Clock Timing                      |                                         |

| Capture4 Interrupt Enable, CA4IE         |        | Memory Interface Read Timing               |                                         |

| Capture4 Interrupt Flag bit, CA4IF       |        | Memory Interface Write Timing              |                                         |

| Carry (C)                                |        | Parameter Measurement Information          |                                         |

| Ceramic Resonators                       |        | Reset, Watchdog Timer, Oscillator Start-up |                                         |

| Circular Buffer                          |        | Timer and Power-up Timer Timing            |                                         |

| CKE                                      |        | Timer Clock Timing                         |                                         |

| CKP                                      | _      | Timer1, Timer2 and Timer3 Clock Timing     |                                         |

| Clearing the Prescaler                   |        | Timing Parameter Symbology                 |                                         |

| Clock Polarity Select bit, CKP           |        | USART Module Synchronous Receive Tim       |                                         |

| Clock/Instruction Cycle (Figure)         |        | USART Module Synchronous Transmission      | •                                       |

| Clocking Scheme/Instruction Cycle        |        | Timing                                     |                                         |

| CLRF                                     |        | EPROM Memory Access Time Order Suffix      |                                         |

| CLRWDT                                   |        | Errata                                     |                                         |

| Code Examples                            | 200    | Extended Microcontroller                   |                                         |

| Indirect Addressing                      | 55     | Extended Microcontroller Mode              |                                         |

| Loading the SSPBUF register              |        | External Memory Interface                  |                                         |

| •                                        |        | External Program Memory Waveforms          |                                         |

| Saving Status and WREG in RAM Table Read |        | External Frogram Memory Wavelonis          | 40                                      |

| Table Write                              |        |                                            |                                         |

| Code Protection                          |        |                                            |                                         |

| COME                                     | 195    |                                            |                                         |

| F                                               |     | Bus Collision                                    | 170       |

|-------------------------------------------------|-----|--------------------------------------------------|-----------|

| Family of Devices                               |     | Acknowledge                                      | 170       |

| PIC17C75X                                       | 8   | RESTART Condition                                | 173       |

| FERR                                            | 125 | RESTART Condition Timing (Case1)                 | 173       |

| Flowcharts                                      |     | RESTART Condition Timing (Case2)                 | 173       |

| Acknowledge                                     | 166 | START Condition                                  | 171       |

| Master Receiver                                 | 163 | START Condition Timing                           | 171, 172  |

| Master Transmit                                 | 160 | STOP Condition                                   | 174       |

| RESTART Condition                               |     | STOP Condition Timing (Case1)                    | 174       |

| Start Condition                                 |     | STOP Condition Timing (Case2)                    |           |

| STOP Condition                                  |     | Transmit Timing                                  |           |

| FOSC0                                           |     | Bus Collision Timing                             |           |

| FOSC1                                           |     | Clock Arbitration                                |           |

| FS0                                             |     | Clock Arbitration Timing (Master Transmit)       |           |

| FS1                                             |     | Conditions to not give ACK Pulse                 |           |

| FS2                                             |     | General Call Address Support                     |           |

|                                                 |     | Master Mode                                      |           |

| FS3                                             |     | Master Mode 7-bit Reception timing               |           |

| FSR0                                            |     | Master Mode Operation                            |           |

| FSR1                                            | 54  | Master Mode Start Condition                      |           |

| G                                               |     | Master Mode Start Condition                      |           |

| GCE                                             |     |                                                  |           |

| General Call Address Sequence                   | 149 | Master Mode Transmit Sequence                    |           |

| General Call Address Support                    | 149 | Master Transmit Flowchart                        |           |

| General Call Enable bit, GCE                    | 136 | Multi-Master Communication                       |           |

| General Format for Instructions                 | 198 | Multi-master Mode                                |           |

| General Purpose RAM                             |     | Operation                                        |           |

| General Purpose RAM Bank                        |     | Repeat Start Condition timing                    |           |

| General Purpose Register (GPR)                  |     | RESTART Condition Flowchart                      | 157       |

| GLINTD39, 52,                                   |     | Slave Mode                                       | 144       |

| Global Interrupt Disable bit, GLINTD            |     | Slave Reception                                  | 145       |

| GOTO                                            |     | Slave Transmission                               | 146       |

|                                                 |     | SSPBUF                                           | 144       |

| GPR (General Purpose Register)                  |     | Start Condition Flowchart                        | 155       |

| GPR Banks                                       | 57  | Stop Condition Flowchart                         | 168       |

| Graphs                                          | _,  | Stop Condition Receive or Transmit timing        |           |

| RC Oscillator Frequency vs. VDD (CEXT = 100 p   |     | Stop Condition timing                            |           |

| RC Oscillator Frequency vs. VDD (CEXT = 22 pF   | •   | Waveforms for 7-bit Reception                    |           |

| RC Oscillator Frequency vs. VDD (CEXT = 300 p   |     | Waveforms for 7-bit Transmission                 |           |

| Transconductance of LF Oscillator vs.VDD        |     | I <sup>2</sup> C Module Address Register, SSPADD |           |

| Transconductance of XT Oscillator vs. VDD       | 270 | I <sup>2</sup> C Slave Mode                      |           |

| Typical RC Oscillator vs. Temperature           | 267 | INCF                                             |           |

| H                                               |     | INCFSNZ                                          |           |

| Hardware Multiplier                             | 67  |                                                  |           |

| 1                                               |     | INCFSZ                                           |           |

| I/O Ports                                       |     | In-Circuit Serial Programming                    |           |

| Bi-directional                                  | 93  | INDF0                                            |           |

| I/O Ports                                       | 71  | INDF1                                            | 54        |

| Programming Considerations                      |     | Indirect Addressing                              |           |

| Read-Modify-Write Instructions                  |     | Indirect Addressing                              |           |

| Successive Operations                           |     | Operation                                        |           |

| 1 <sup>2</sup> C                                | 142 | Registers                                        | 54        |

|                                                 |     | Initializing PORTB                               |           |

| I2C Input                                       |     | Initializing PORTC                               | 78        |

| <sup>12</sup> C Master Mode Receiver Flow Chart |     | Initializing PORTD                               | 80        |

| <sup>12</sup> C Master Mode Reception           |     | Initializing PORTE82                             | 2, 84, 86 |

| <sup>12</sup> C Master Mode RESTART Condition   |     | INSTA                                            | 48        |

| I <sup>2</sup> C Mode Selection                 | 143 | Instruction Flow/Pipelining                      |           |

| I <sup>2</sup> C Module                         |     | Instruction Set                                  |           |

| Acknowledge Flow Chart                          | 166 | ADDLW                                            | 202       |

| Acknowledge Sequence Timing                     | 165 | ADDWF                                            |           |

| Addressing                                      | 145 | ADDWF                                            |           |

| Baud Rate Generator                             | 153 | ANDLW                                            |           |

| Block Diagram                                   | 151 | ANDWF                                            |           |

| BRG Block Diagram                               |     |                                                  |           |

| BRG Reset due to SDA Collision                  |     | BCF                                              |           |

| BRG Timing                                      |     | BSF                                              |           |

| Bus Arbitration                                 |     | BTFSC                                            |           |

|                                                 | •   | BTFSS                                            | 206       |

| SEEVAL Evaluation and Programming System | 236          | SSPIE                                        | 36            |

|------------------------------------------|--------------|----------------------------------------------|---------------|

| Serial Clock, SCK                        |              | SSPIF                                        | 38, 145       |

| Serial Clock, SCL                        | 144          | SSPM3:SSPM0                                  | 135           |

| Serial Data Address, SDA                 | 144          | SSPOV                                        | 135, 144, 162 |

| Serial Data In, SDI                      | 137          | SSPSTAT                                      | 50, 134, 144  |

| Serial Data Out, SDO                     | 137          | ST Input                                     | 278           |

| SETF                                     | 224          | Stack                                        |               |

| SFR                                      | 198          | Operation                                    | 54            |

| SFR (Special Function Registers)         | 43           | Pointer                                      | 54            |

| SFR As Source/Destination                |              | Stack                                        | 43            |

| Signed Math                              | 11           | START bit (S)                                | 134           |

| Slave Select Synchronization             | 140          | START Condition Enabled bit, SAE             | 136           |

| Slave Select, SS                         | 137          | STKAV                                        | 52, 54        |

| SLEEP                                    | 194, 225     | STOP bit (P)                                 | 134           |

| SLEEP Mode, All Peripherals Disabled     | 273          | STOP Condition Enable bit                    | 136           |

| SLEEP Mode, BOR Enabled                  | 273          | SUBLW                                        | 225           |

| SMP                                      |              | SUBWF                                        | 226           |

| Software Simulator (MPLAB SIM)           | 234          | SUBWFB                                       | 226           |

| SPBRG 1                                  | 26, 130, 132 | SWAPF                                        |               |

| SPBRG1                                   | 27, 48       | Synchronous Master Mode                      |               |

| SPBRG2                                   |              | Synchronous Master Reception                 |               |

| SPE                                      |              | Synchronous Master Transmission              |               |

| Special Features of the CPU              |              | Synchronous Serial Port                      |               |

| Special Function Registers               | 43, 198      | Synchronous Serial Port Enable bit, SSPEN    |               |

| Summary                                  |              | Synchronous Serial Port Interrupt            |               |

| Special Function Registers, File Map     | 47           | Synchronous Serial Port Interrupt Enable, SS | PIE 36        |

| SPI                                      |              | Synchronous Serial Port Mode Select bits,    |               |

| Master Mode                              |              | SSPM3:SSPM0                                  |               |

| Serial Clock                             |              | Synchronous Slave Mode                       | 131           |

| Serial Data In                           |              | Т                                            |               |

| Serial Data Out                          |              | T0CKI                                        |               |

| Serial Peripheral Interface (SPI)        |              | T0CKI Pin                                    |               |

| Slave Select                             |              | T0CKIE                                       |               |

| SPI clock                                |              | T0CKIF                                       |               |

| SPI Mode                                 |              | T0CS                                         |               |

| SPI Clock Edge Select, CKE               |              | T0IE                                         |               |

| SPI Data Input Sample Phase Select, SMP  |              | TOIF                                         | _             |

| SPI Master/Slave Connection              | 138          | T0SE                                         |               |

| SPI Module  Master/Slave Connection      | 100          | TOSTA                                        |               |

| Slave Mode                               |              | T16                                          |               |

| Slave Select Synchronization             |              | Table Latch                                  |               |

| Slave Synch Timing                       |              | Table Pointer                                | 55            |

| SS                                       |              | Table Read                                   | 0.4           |

| SSP                                      |              | Example                                      |               |

| Block Diagram (SPI Mode)                 |              | . 45.5                                       |               |

| SPI Mode                                 |              | TLRD<br>Table Write                          | 64            |

| SSPADD                                   |              | Code                                         | 60            |

| SSPBUF                                   |              |                                              |               |

| SSPCON1                                  | •            | Timing To External Memory                    |               |

| SSPCON2                                  |              | TABLRD                                       |               |

| SSPSR                                    |              | TABLWT                                       | ,             |

| SSPSTAT                                  | •            | TAD                                          |               |

| SSP I <sup>2</sup> C                     | ,            | TBLATH                                       |               |

| SSP I <sup>2</sup> C Operation           | 143          | TBLATL                                       |               |

| SSP Module                               |              | TBLPTRH                                      |               |

| SPI Master Mode                          | 139          | TBLPTRL                                      |               |

| SPI Master/Slave Connection              |              | TCLK12                                       |               |

| SPI Slave Mode                           | 140          | TCLK3                                        |               |

| SSPCON1 Register                         | 143          | TCON1                                        |               |

| SSP Overflow Detect bit, SSPOV           |              | TCON2                                        | ,             |

| SSPADD                                   | 50           | TCON2,TCON3                                  |               |

| SSPBUF                                   | 50, 144      | TCON3                                        |               |

| SSPCON1                                  |              | Time-Out Sequence                            | ,             |

| SSPCON2                                  |              | Timer Resources                              |               |

| SSPEN                                    | 135          |                                              |               |

#### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO. Device   | X /XX XXX<br>Temperature Package Pattern<br>Range                                                     | Examples:  a) PIC17C756 - 16L Commercial Temp., PLCC package, 16 MHz, normal VDD limits                                                    |

|-------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Device            | PIC17C756: Standard VDD range<br>PIC17C756T: (Tape and Reel)<br>PIC17LC756: Extended VDD range        | b) PIC17LC756-08/PT Commercial Temp., TQFP package, 8MHz, extended VDD limits  c) PIC17C756-33I/PT Industrial Temp., TQFP package, 33 MHz, |

| Temperature Range | - = 0°C to +70°C<br>I = -40°C to +85°C                                                                | normal VDD limits                                                                                                                          |

| Package           | CL = Windowed LCC PT = TQFP L = PLCC                                                                  |                                                                                                                                            |

| Pattern           | QTP, SQTP, ROM Code (factory specified) or Special Requirements . Blamk for OTP and Windowed devices. |                                                                                                                                            |

<sup>\*</sup> JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type.

#### **Sales and Support**

#### **Data Sheets**

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Corporate Literature Center U.S. FAX: (480) 792-7277

- 3. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### **New Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.