Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                              |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 100MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                 |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                       |

| Number of I/O              | 29                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 1K x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                        |

| Data Converters            | A/D 21x10b; D/A 1x10b                                            |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 32-LQFP                                                          |

| Supplier Device Package    | 32-LQFP (7x7)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f361-c-gq |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C8051F360/1/2/3/4/5/6/7/8/9

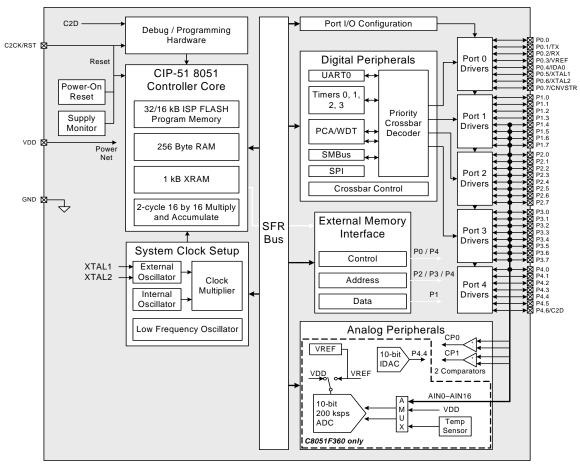

Figure 1.1. C8051F360/3 Block Diagram

#### 1.1.3. Additional Features

The C8051F36x SoC family includes several key enhancements to the CIP-51 core and peripherals to improve performance and ease of use in end applications.

The extended interrupt handler provides 16 interrupt sources into the CIP-51 (as opposed to 7 for the standard 8051), allowing numerous analog and digital peripherals to interrupt the controller. An interrupt driven system requires less intervention by the MCU, giving it more effective throughput. The extra interrupt sources are very useful when building multi-tasking, real-time systems.

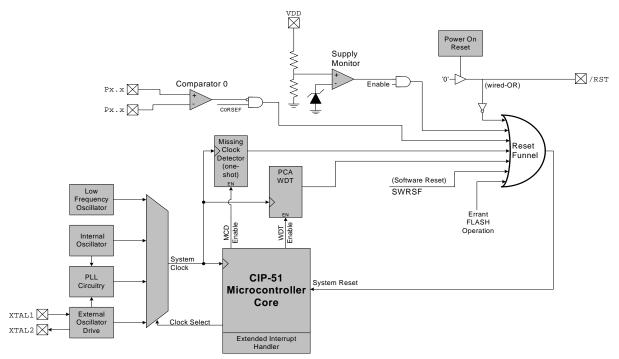

Eight reset sources are available: power-on reset circuitry (POR), an on-chip  $V_{DD}$  Monitor (forces reset when power supply voltage drops below  $V_{RST}$  as given in Table 12.1 on page 134), a Watchdog Timer, a Missing Clock Detector, a voltage level detection from Comparator0, a forced software reset, an external reset pin, and an illegal Flash access protection circuit. Each reset source except for the POR, Reset Input Pin, or Flash error may be disabled by the user in software. The WDT may be permanently enabled in software after a power-on reset during MCU initialization.

The internal oscillator factory calibrated to 24.5 MHz ±2%. This internal oscillator period may be user programmed in ~0.5% increments. An additional low-frequency oscillator is also available which facilitates low-power operation. An external oscillator drive circuit is included, allowing an external crystal, ceramic resonator, capacitor, RC, or CMOS clock source to generate the system clock. If desired, the system clock source may be switched on-the-fly between both internal and external oscillator circuits. An external oscillator can also be extremely useful in low power applications, allowing the MCU to run from a slow (power saving) source, while periodically switching to the fast (up to 25 MHz) internal oscillator as needed. Additionally, an on-chip PLL is provided to achieve higher system clock speeds for increased throughput.

Figure 1.5. On-Chip Clock and Reset

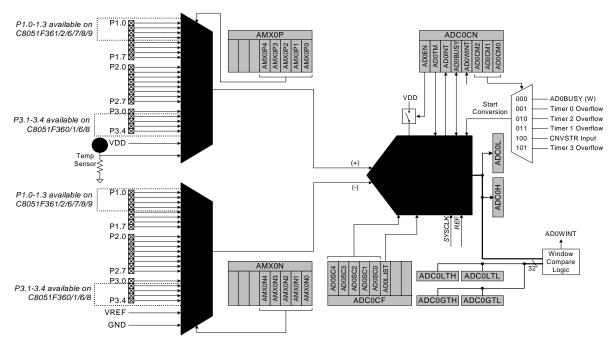

## 5. 10-Bit ADC (ADC0, C8051F360/1/2/6/7/8/9)

The ADC0 subsystem for the C8051F360/1/2/6/7/8/9 consists of two analog multiplexers (referred to collectively as AMUX0) with 23 total input selections, and a 200 ksps, 10-bit successive-approximation-register ADC with integrated track-and-hold and programmable window detector. The AMUX0, data conversion modes, and window detector are all configurable under software control via the Special Function Registers shown in Figure 5.1. ADC0 operates in both Single-ended and Differential modes, and may be configured to measure P1.0-P3.4 (where available), the Temperature Sensor output, or V<sub>DD</sub> with respect to P1.0-P3.4, VREF, or GND. The ADC0 subsystem is enabled only when the AD0EN bit in the ADC0 Control register (ADC0CN) is set to logic '1'. The ADC0 subsystem is in low power shutdown when this bit is logic '0'.

Figure 5.1. ADC0 Functional Block Diagram

| R       | R                 | R                         | R/W                                                             | R/W                             | R/W          | R/W               | R/W          | Reset Valu |  |  |

|---------|-------------------|---------------------------|-----------------------------------------------------------------|---------------------------------|--------------|-------------------|--------------|------------|--|--|

| -       | -                 | -                         | AMX0N4                                                          | AMX0N3                          | AMX0N2       | AMX0N1            | AMX0N0       | 0000000    |  |  |

| Bit7    | Bit6              | Bit5                      | Bit4                                                            | Bit3                            | Bit2         | Bit1              | Bit0         |            |  |  |

| ∘s7_5·I | INUSED R          | ead – 000                 | b; Write = do                                                   | n't care                        |              |                   |              |            |  |  |

|         |                   |                           | legative Inpu                                                   |                                 |              |                   |              |            |  |  |

|         |                   |                           | s selected as                                                   | -                               | •            | •                 | -            |            |  |  |

| r       | node. For al      | l other Ne                | gative Input                                                    | selections,                     | ADC0 opera   | ates in Diffe     | erential mod | e.         |  |  |

| Г       |                   | AMX0N4                    | L-0                                                             |                                 |              | ative Input       |              |            |  |  |

| -       |                   | 00000 <sup>(1</sup>       |                                                                 |                                 | -            | .0 <sup>(1)</sup> |              |            |  |  |

| -       |                   | 000001 <sup>(1</sup>      |                                                                 |                                 |              | .1 <sup>(1)</sup> |              |            |  |  |

| -       |                   | 00001                     |                                                                 |                                 |              | .2 <sup>(1)</sup> |              |            |  |  |

| ŀ       |                   | 00010                     |                                                                 |                                 |              | .2 <sup>(1)</sup> |              |            |  |  |

| ŀ       |                   | 00011                     |                                                                 |                                 |              | -                 |              |            |  |  |

| -       |                   | 00100                     |                                                                 |                                 | P1.4<br>P1.5 |                   |              |            |  |  |

| -       |                   | 00110                     |                                                                 |                                 |              | 1.6               |              |            |  |  |

| _       |                   | 00111                     |                                                                 |                                 | P            | 1.7               |              |            |  |  |

|         |                   | 01000                     |                                                                 |                                 |              | 2.0               |              |            |  |  |

| _       |                   | 01001                     |                                                                 |                                 |              | 2.1               |              |            |  |  |

| -       |                   | 01010                     |                                                                 |                                 | P2.2<br>P2.3 |                   |              |            |  |  |

| -       |                   | 01011<br>01100            |                                                                 |                                 | P2.4         |                   |              |            |  |  |

|         |                   | 01100                     |                                                                 |                                 |              | 2.4               |              |            |  |  |

| -       |                   | 01110                     |                                                                 |                                 |              | 2.6               |              |            |  |  |

|         |                   | 01111                     |                                                                 |                                 | P2           | 2.7               |              |            |  |  |

|         |                   | 10000                     |                                                                 |                                 |              | 3.0               |              |            |  |  |

|         |                   | 10001 <sup>(2</sup>       | 2)                                                              |                                 | P3.          | .1 <sup>(2)</sup> |              |            |  |  |

|         |                   | 10010 <sup>(2</sup>       |                                                                 |                                 | P3.          | 2 <sup>(2)</sup>  |              |            |  |  |

|         |                   | 10011 <sup>(2</sup>       | 2)                                                              |                                 | P3.          | .3 <sup>(2)</sup> |              |            |  |  |

| F       |                   | 10100 <sup>(2</sup>       | 2)                                                              |                                 | P3.          | 4 <sup>(2)</sup>  |              |            |  |  |

| F       |                   | 10101–11                  |                                                                 |                                 |              | RVED              |              |            |  |  |

|         |                   | 11110                     |                                                                 |                                 |              | REF               |              |            |  |  |

|         |                   | 11111                     |                                                                 |                                 | GI           | ND                |              |            |  |  |

|         | RESE<br>2. Only a | RVED on C<br>applies to C | 8051F361/2/6<br>28051F360 (4<br>8051F360/1/6<br>/9 (28-pin) dev | 8-pin) device<br>5/8 (48-pin ar |              |                   | ERVED        |            |  |  |

# C8051F360/1/2/3/4/5/6/7/8/9

complete Port I/O configuration details. The TEMPE bit in register REF0CN enables/disables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any ADC0 measurements performed on the sensor result in meaningless data.

| R                                                                                                                                  | R                                                               | R           | R                 | R/W         | R/W    | R/W   | R/W   | Reset Value |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------|-------------------|-------------|--------|-------|-------|-------------|--|--|--|--|--|

| -                                                                                                                                  | -                                                               | -           | -                 | REFSL       | TEMPE  | BIASE | REFBE | 00000000    |  |  |  |  |  |

| Bit7                                                                                                                               | Bit6                                                            | Bit5        | Bit4              | Bit3        | Bit2   | Bit1  | Bit0  | <b>_</b>    |  |  |  |  |  |

|                                                                                                                                    |                                                                 |             |                   |             |        |       |       |             |  |  |  |  |  |

| Bits 7–4: UNUSED. Read = 0000b; Write = don't care.                                                                                |                                                                 |             |                   |             |        |       |       |             |  |  |  |  |  |

| Bit 3:                                                                                                                             | REFSL: Voltage Reference Select.                                |             |                   |             |        |       |       |             |  |  |  |  |  |

|                                                                                                                                    | This bit selects the source for the internal voltage reference. |             |                   |             |        |       |       |             |  |  |  |  |  |

|                                                                                                                                    | 0: VREF pin used as voltage reference.                          |             |                   |             |        |       |       |             |  |  |  |  |  |

|                                                                                                                                    | 1: V <sub>DD</sub> used as voltage reference.                   |             |                   |             |        |       |       |             |  |  |  |  |  |

| Bit 2:                                                                                                                             | TEMPE: Ten                                                      | nperature S | Sensor Enab       | ole Bit.    |        |       |       |             |  |  |  |  |  |

|                                                                                                                                    | 0: Internal Te                                                  | emperature  | Sensor off.       |             |        |       |       |             |  |  |  |  |  |

|                                                                                                                                    | 1: Internal Te                                                  | emperature  | Sensor on.        |             |        |       |       |             |  |  |  |  |  |

| Bit 1:                                                                                                                             | BIASE: Inter                                                    | nal Analog  | <b>Bias Gener</b> | ator Enable | e Bit. |       |       |             |  |  |  |  |  |

|                                                                                                                                    | 0: Internal Bi                                                  | as Genera   | tor off.          |             |        |       |       |             |  |  |  |  |  |

|                                                                                                                                    | 1: Internal Bi                                                  | as Genera   | tor on.           |             |        |       |       |             |  |  |  |  |  |

| Bit 0:                                                                                                                             | REFBE: Inte                                                     | rnal Refere | ence Buffer       | Enable Bit. |        |       |       |             |  |  |  |  |  |

|                                                                                                                                    | 0: Internal R                                                   | eference B  | uffer disable     | ed.         |        |       |       |             |  |  |  |  |  |

| 0: Internal Reference Buffer disabled.<br>1: Internal Reference Buffer enabled. Internal voltage reference driven on the VREF pin. |                                                                 |             |                   |             |        |       |       |             |  |  |  |  |  |

## C8051F360/1/2/3/4/5/6/7/8/9

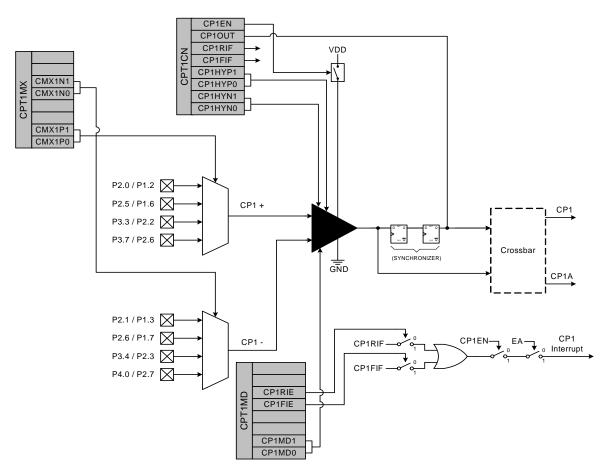

Figure 8.2. Comparator1 Functional Block Diagram

A Comparator output can be polled in software, used as an interrupt source, and/or routed to a Port pin. When routed to a Port pin, the Comparator outputs are available asynchronous or synchronous to the system clock; the asynchronous outputs are available even in STOP mode (with no system clock active). When disabled, the Comparator outputs (if assigned to a Port I/O pin via the Crossbar) default to the logic low state, and their supply current falls to less than 100 nA. See Section "17.1. Priority Crossbar Decoder" on page 184 for details on configuring Comparator outputs via the digital Crossbar. Comparator inputs can be externally driven from -0.25 V to (V<sub>DD</sub>) + 0.25 V without damage or upset. The complete Comparator electrical specifications are given in Table 8.1.

The Comparator response time may be configured in software via the CPT0MD and CPT1MD registers (see SFR Definition 8.3 and SFR Definition 8.6). Selecting a longer response time reduces the Comparator supply current. See Table 8.1 for complete timing and power consumption specifications.

#### SFR Definition 9.1. SFR0CN: SFR Page Control

| R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W      | R/W      | R/W      | R/W      | R/W      | R/W      | R/W     | Reset Valu |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|---------|------------|--|--|--|

| Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Reserved | Reserved | Reserved | Reserved | Reserved | Reserved | SFRPGEN | 0000001    |  |  |  |

| Bit7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Bit6     | Bit5     | Bit4     | Bit3     | Bit2     | Bit1     | Bit0    | ·          |  |  |  |

| <ul> <li>Bit 0: SFRPGEN: SFR Automatic Page Control Enable.</li> <li>Upon interrupt, the C8051 Core will vector to the specified interrupt service routine and aut matically switch to SFR page 0. This bit is used to control this autopaging function.</li> <li>0: SFR Automatic Paging disabled. C8051 core will not automatically change to SFR page 0.</li> <li>1: SFR Automatic Paging enabled. Upon interrupt, the C8051 will automatically switch to SFR page 0.</li> </ul> |          |          |          |          |          |          |         |            |  |  |  |

#### SFR Definition 9.2. SFRPAGE: SFR Page

| R/W  | R/W                                                                                                                           | R/W                                                                               | R/W                                                        | R/W                                                          | R/W                                                     | R/W                                       | R/W         | Reset Value |

|------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------|-------------|-------------|

|      |                                                                                                                               |                                                                                   |                                                            |                                                              |                                                         |                                           |             | 0000000     |

| Bit7 | Bit6                                                                                                                          | Bit5                                                                              | Bit4                                                       | Bit3                                                         | Bit2                                                    | Bit1                                      | Bit0        |             |

|      | ifying SFR's.<br>Write: Sets th<br>Read: Byte is<br>When enable<br>switch to SFR<br>(unless SFR<br>SFRPAGE is<br>caused by in | he SFR Pa<br>s the SFR p<br>ed in the SF<br>R Page 0x0<br>Stack was<br>the top by | FR Page Cc<br>00 and retur<br>altered befo<br>te of the SF | ontrol Regis<br>in to the pre<br>ore a return<br>iR Page Sta | ter (SFR0C<br>vious SFR<br>ing from the<br>ick, and pus | page upon<br>e interrupt).<br>sh/pop ever | return fror | n interrupt |

#### Table 9.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| Register | Address | SFR<br>Page | Description                      | Page No.              |

|----------|---------|-------------|----------------------------------|-----------------------|

| EMI0CF   | 0xC7    | F           | EMIF Configuration               | page 155 <sup>2</sup> |

| EMI0CN   | 0xAA    | All Pages   | EMIF Control                     | page 154 <sup>2</sup> |

| EMI0TC   | 0xF7    | F           | EMIF Timing Control              | page 160 <sup>2</sup> |

| FLKEY    | 0xB7    | 0           | Flash Lock and Key               | page 142              |

| FLSCL    | 0xB6    | 0           | Flash Scale                      | page 143              |

| FLSTAT   | 0xAC    | F           | Flash Status                     | page 152              |

| IDA0CN   | 0xB9    | All Pages   | IDAC0 Control                    | page 65 <sup>1</sup>  |

| IDA0H    | 0x97    | All Pages   | IDAC0 High Byte                  | page 65 <sup>1</sup>  |

| IDA0L    | 0x96    | All Pages   | IDAC0 Low Byte                   | page 66 <sup>1</sup>  |

| IE       | 0xA8    | All Pages   | Interrupt Enable                 | page 110              |

| IP       | 0xB8    | All Pages   | Interrupt Priority               | page 111              |

| IT01CF   | 0xE4    | All Pages   | INT0/INT1 Configuration          | page 116              |

| MAC0ACC0 | 0xD2    | 0           | MAC0 Accumulator Byte 0 (LSB)    | page 126              |

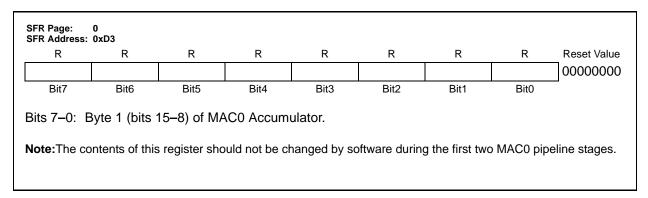

| MAC0ACC1 | 0xD3    | 0           | MAC0 Accumulator Byte 1          | page 125              |

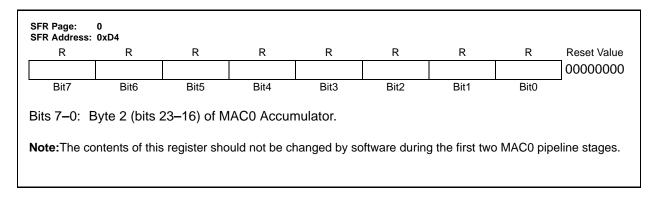

| MAC0ACC2 | 0xD4    | 0           | MAC0 Accumulator Byte 2          | page 125              |

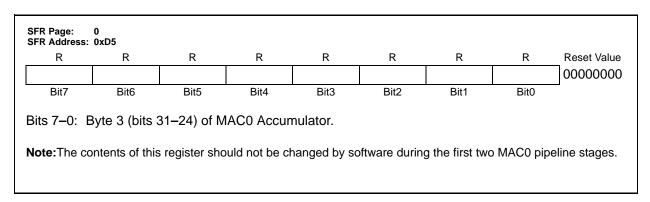

| MAC0ACC3 | 0xD5    | 0           | MAC0 Accumulator Byte 3 (MSB)    | page 125              |

| MAC0AH   | 0xA5    | 0           | MAC0 A Register High Byte        | page 123              |

| MAC0AL   | 0xA4    | 0           | MAC0 A Register Low Byte         | page 124              |

| MAC0BH   | 0xF2    | 0           | MAC0 B Register High Byte        | page 124              |

| MAC0BL   | 0xF1    | 0           | MAC0 B Register Low Byte         | page 124              |

| MAC0CF   | 0xD7    | 0           | MAC0 Configuration               | page 122              |

| MAC0OVR  | 0xD6    | 0           | MAC0 Accumulator Overflow        | page 126              |

| MACORNDH | 0xAF    | 0           | MAC0 Rounding Register High Byte | page 126              |

| MACORNDL | 0xAE    | 0           | MAC0 Rounding Register Low Byte  | page 127              |

| MACOSTA  | 0xCF    | 0           | MAC0 Status Register             | page 123              |

| OSCICL   | 0xBF    | F           | Internal Oscillator Calibration  | page 169              |

| OSCICN   | 0xB7    | F           | Internal Oscillator Control      | page 170              |

| OSCLCN   | 0xAD    | F           | Internal L-F Oscillator Control  | page 171              |

| OSCXCN   | 0xB6    | F           | External Oscillator Control      | page 174              |

| P0       | 0x80    | All Pages   | Port 0 Latch                     | page 189              |

| POMASK   | 0xF4    | 0           | Port 0 Mask                      | page 191              |

2. Refers to a register in the C8051F360/3 only.

#### 11.2. Integer and Fractional Math

MAC0 is capable of interpreting the 16-bit inputs stored in MAC0A and MAC0B as signed integers or as signed fractional numbers. When the MAC0FM bit (MAC0CF.1) is cleared to '0', the inputs are treated as 16-bit, 2's complement, integer values. After the operation, the accumulator will contain a 40-bit, 2's complement, integer value. Figure 11.2 shows how integers are stored in the SFRs.

#### MAC0A and MAC0B Bit Weighting

|                                     | High Byte       |                 |     |     |                |    | Low Byte |                |                |    |                |                |                |    |

|-------------------------------------|-----------------|-----------------|-----|-----|----------------|----|----------|----------------|----------------|----|----------------|----------------|----------------|----|

| -(2 <sup>15</sup> ) 2 <sup>14</sup> | 2 <sup>13</sup> | 2 <sup>12</sup> | 211 | 210 | 2 <sup>9</sup> | 28 | 27       | 2 <sup>6</sup> | 2 <sup>5</sup> | 24 | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 20 |

| MAC0 Accumulator Bit Weighting |  |

|--------------------------------|--|

|--------------------------------|--|

| MACOOVR                                                             | MAC0ACC3 : MAC0ACC2 : MAC0ACC1 : MAC0ACC0              |

|---------------------------------------------------------------------|--------------------------------------------------------|

| -(2 <sup>39</sup> ) 2 <sup>38</sup> 2 <sup>33</sup> 2 <sup>32</sup> | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |

#### Figure 11.2. Integer Mode Data Representation

When the MACOFM bit is set to '1', the inputs are treated at 16-bit, 2's complement, fractional values. The decimal point is located between bits 15 and 14 of the data word. After the operation, the accumulator will contain a 40-bit, 2's complement, fractional value, with the decimal point located between bits 31 and 30. Figure 11.3 shows how fractional numbers are stored in the SFRs.

#### MAC0A, and MAC0B Bit Weighting

| High Byte |     |     |                 |     |     |     |     |     |     | Low  | Byte |                         |                  |                  |                  |  |

|-----------|-----|-----|-----------------|-----|-----|-----|-----|-----|-----|------|------|-------------------------|------------------|------------------|------------------|--|

| -1        | 2-1 | 2-2 | 2 <sup>-3</sup> | 2-4 | 2-5 | 2-6 | 2-7 | 2-8 | 2-9 | 2-10 | 2-11 | <b>2</b> <sup>-12</sup> | 2 <sup>-13</sup> | 2 <sup>-14</sup> | 2 <sup>-15</sup> |  |

#### MAC0 Accumulator Bit Weighting

| MAC0OVR                                          |    | MAC0ACC3 : MAC0ACC2 : MAC0ACC1 : MAC0ACC0 |     |                 |                 |    |                  |                  |      |                  |                  |

|--------------------------------------------------|----|-------------------------------------------|-----|-----------------|-----------------|----|------------------|------------------|------|------------------|------------------|

| -(2 <sup>8</sup> ) 2 <sup>7</sup> 2 <sup>2</sup> | 21 | 20                                        | 2-1 | 2 <sup>-2</sup> | 2 <sup>-3</sup> | 22 | 2 <sup>-27</sup> | 2 <sup>-28</sup> | 2-29 | 2 <sup>-30</sup> | 2 <sup>-31</sup> |

#### MACORND Bit Weighting

| High Byte |   |     |     |                 |     | Low Byte |     |     |     |     |      |      |                         |                  |      |      |

|-----------|---|-----|-----|-----------------|-----|----------|-----|-----|-----|-----|------|------|-------------------------|------------------|------|------|

| * -2      | 1 | 2-1 | 2-2 | 2 <sup>-3</sup> | 2-4 | 2-5      | 2-6 | 2-7 | 2-8 | 2-9 | 2-10 | 2-11 | <b>2</b> <sup>-12</sup> | 2 <sup>-13</sup> | 2-14 | 2-15 |

\* The MACORND register contains the 16 LSBs of a two's complement number. The MACON Flag can be used to determine the sign of the MACORND register.

#### Figure 11.3. Fractional Mode Data Representation

#### 11.3. Operating in Multiply and Accumulate Mode

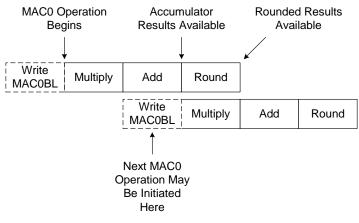

MAC0 operates in Multiply and Accumulate (MAC) mode when the MACOMS bit (MAC0CF.0) is cleared to '0'. When operating in MAC mode, MAC0 performs a 16-by-16 bit multiply on the contents of the MAC0A and MAC0B registers, and adds the result to the contents of the 40-bit MAC0 accumulator. Figure 11.4 shows the MAC0 pipeline. There are three stages in the pipeline, each of which takes exactly one SYSCLK cycle to complete. The MAC operation is initiated with a write to the MAC0BL register. After the MAC0BL register is written, MAC0A and MAC0B are multiplied on the first SYSCLK cycle. During the second stage of the MAC0 pipeline, the results of the multiplication are added to the current accumulator contents, and the result of the addition is stored in the MAC0 accumulator. The status flags in the MAC0STA register are set after the end of the second pipeline stage. During the second stage of the pipeline, the next multiplication are determined by writing to the MAC0BL register, if it is desired. The rounded (and optionally, saturated) result is available in the MAC0RNDH and MAC0RNDL registers at the end of the third pipeline stage. If the MAC0CA bit (MAC0CF.3) is set to '1' when the MAC operation is initiated, the accumulator and all MAC0STA flags will be cleared during the next cycle of the controller's clock (SYSCLK). The MAC0CA bit will clear itself to '0' when the clear operation is complete.

Figure 11.4. MAC0 Pipeline

#### 11.4. Operating in Multiply Only Mode

MAC0 operates in Multiply Only mode when the MAC0MS bit (MAC0CF.0) is set to '1'. Multiply Only mode is identical to Multiply and Accumulate mode, except that the multiplication result is added with a value of zero before being stored in the MAC0 accumulator (i.e. it overwrites the current accumulator contents). The result of the multiplication is available in the MAC0 accumulator registers at the end of the second MAC0 pipeline stage (two SYSCLKs after writing to MAC0BL). As in MAC mode, the rounded result is available in the MAC0 Rounding Registers after the third pipeline stage. Note that in Multiply Only mode, the MAC0HO flag is not affected.

#### 11.5. Accumulator Shift Operations

MAC0 contains a 1-bit arithmetic shift function which can be used to shift the contents of the 40-bit accumulator left or right by one bit. The accumulator shift is initiated by writing a '1' to the MAC0SC bit (MAC0CF.5), and takes one SYSCLK cycle (the rounded result is available in the MAC0 Rounding Registers after a second SYSCLK cycle, and MAC0SC is cleared to '0'). The direction of the arithmetic shift is controlled by the MAC0SD bit (MAC0CF.4). When this bit is cleared to '0', the MAC0 accumulator will shift left. When the MAC0SD bit is set to '1', the MAC0 accumulator will shift right. Right-shift operations are sign-extended with the current value of bit 39. Note that the status flags in the MAC0STA register are not affected by shift operations.

#### SFR Definition 11.7. MAC0ACC3: MAC0 Accumulator Byte 3

#### SFR Definition 11.8. MAC0ACC2: MAC0 Accumulator Byte 2

### SFR Definition 11.9. MAC0ACC1: MAC0 Accumulator Byte 1

#### 15.2. Configuring the External Memory Interface

Configuring the External Memory Interface consists of five steps:

- 1. Configure the Output Modes of the associated port pins as either push-pull or open-drain (push-pull is most common), and skip the associated pins in the crossbar.

- 2. Configure Port latches to "park" the EMIF pins in a dormant state (usually by setting them to logic '1').

- 3. Select Multiplexed mode or Non-multiplexed mode.

- 4. Select the memory mode (on-chip only, split mode without bank select, split mode with bank select, or off-chip only).

- 5. Set up timing to interface with off-chip memory or peripherals.

Each of these five steps is explained in detail in the following sections. The Port selection, Multiplexed mode selection, and Mode bits are located in the EMI0CF register shown in SFR Definition 15.2.

#### 15.3. Port Configuration

The External Memory Interface appears on Ports 1, 2 (non-multiplexed mode only), 3, and 4 when it is used for off-chip memory access. When the EMIF is used in multiplexed mode, the Crossbar should be configured to skip over the ALE control line (P0.0) using the POSKIP register. The other control lines, /RD (P4.4) and /WR (P4.5), are not available on the Crossbar and do not need to be skipped. For more information about configuring the Crossbar, see Section "17.3. General Purpose Port I/O" on page 189. The EMIF pinout is shown in Table 15.1 on page 154.

The External Memory Interface claims the associated Port pins for memory operations ONLY during the execution of an off-chip MOVX instruction. Once the MOVX instruction has completed, control of the Port pins reverts to the Port latches or to the Crossbar settings for those pins. See Section "17. Port Input/Output" on page 182 for more information about the Crossbar and Port operation and configuration. **The Port latches should be explicitly configured to 'park' the External Memory Interface pins in a dormant state, most commonly by setting them to a logic '1'**.

During the execution of the MOVX instruction, the External Memory Interface will explicitly disable the drivers on all Port pins that are acting as Inputs (Data[7:0] during a READ operation, for example). The Output mode of the Port pins (whether the pin is configured as Open-Drain or Push-Pull) is unaffected by the External Memory Interface operation, and remains controlled by the PnMDOUT registers. In most cases, the output modes of all EMIF pins should be configured for push-pull mode.

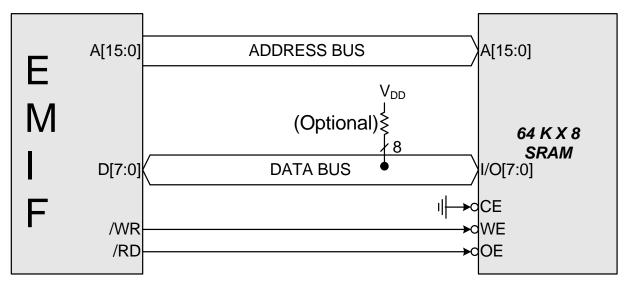

#### 15.4.2. Non-multiplexed Configuration

In Non-multiplexed mode, the Data Bus and the Address Bus pins are not shared. An example of a Non-multiplexed Configuration is shown in Figure 15.2. See Section "15.6.1. Non-multiplexed Mode" on page 161 for more information about Non-multiplexed operation.

Figure 15.2. Non-multiplexed Configuration Example

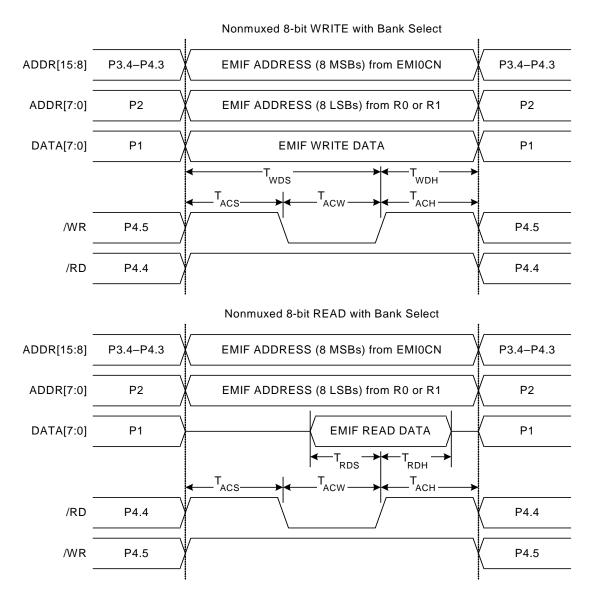

15.6.1.3.8-bit MOVX with Bank Select: EMI0CF[4:2] = '110'.

Figure 15.6. Non-multiplexed 8-bit MOVX with Bank Select Timing

| R         | R/W           | R/W                                   | R/W                  | R                     | R/W                     | R/W      | R/W         | Reset Value |

|-----------|---------------|---------------------------------------|----------------------|-----------------------|-------------------------|----------|-------------|-------------|

| XTLVLD    | XOSCME        | 02 XOSCMD1                            | XOSCMD0              | Reserved              | XFCN2                   | XFCN1    | XFCN0       | 0000000     |

| Bit7      | Bit6          | Bit5                                  | Bit4                 | Bit3                  | Bit2                    | Bit1     | Bit0        |             |

| Bit 7:    | XTLVLD: C     | Crystal Oscilla                       | tor Valid Fla        | g.                    |                         |          |             |             |

|           | (Valid only   | when XOS                              | CMD = 11x.)          | -                     |                         |          |             |             |

|           | •             | Oscillator is u                       |                      | •                     |                         |          |             |             |

|           |               | Oscillator is ru                      |                      |                       |                         |          |             |             |

| Bits 6–4: |               | 2–0: External                         |                      | ode Bits.             |                         |          |             |             |

|           |               | nal Oscillator                        |                      |                       |                         |          |             |             |

|           |               | nal CMOS Clo                          |                      | مرط مانينام م         | O ata sa                |          |             |             |

|           |               | nal CMOS Clo<br>scillator Mode        |                      | th divide by          | z stage.                |          |             |             |

|           |               | citor Oscillato                       |                      |                       |                         |          |             |             |

|           | •             | al Oscillator N                       |                      |                       |                         |          |             |             |

|           | •             | al Oscillator N                       |                      | vide by 2 sta         | ae                      |          |             |             |

| Bit 3:    |               | D. Read = $0b$                        |                      |                       | 90.                     |          |             |             |

|           |               | External Osc                          |                      |                       | ol Bits.                |          |             |             |

|           |               | ee table belov                        |                      | ,                     |                         |          |             |             |

| Γ         | XFCN          | Crystal (XO                           | SCMD = 11x           | () RC (XO             | SCMD = 10               | 00) C (X | OSCMD =     | 101)        |

|           | 000           | f ≤ 3                                 | 2 kHz                | f ≤                   | 25 kHz                  | KI       | actor = 0.8 | 37          |

|           | 001           | 32 kHz <                              | f ≤ 84 kHz           | 25 kHz                | < f ≤ 50 kH             | lz K     | Factor = 2. | 6           |

|           | 010           | 84 kHz < f                            | ≤ 225 kHz            | 50 kHz                | < f ≤ 100 kl            | Hz K     | Factor = 7. | 7           |

|           | 011           | 225 kHz <                             | f ≤ 590 kHz          | 100 kHz               | $< f \le 200 \text{ k}$ | Hz K     | Factor = 22 | 2           |

|           | 100           | 590 kHz <                             | f ≤ 1.5 MHz          | 200 kHz               | $< f \le 400 \text{ k}$ | Hz K     | Factor = 6  | 5           |

|           | 101           | 1.5 MHz <                             | ∶f≤4 MHz             | 400 kHz               | < f ≤ 800 k             | Hz K     | Factor = 18 | 30          |

|           | 110           | 4 MHz < f                             | <sup>-</sup> ≤10 MHz | 800 kHz               | < f ≤ 1.6 M             | IHz K    | Factor = 66 | 64          |

|           | 111           | 10 MHz <                              | f ≤ 30 MHz           | 1.6 MHz               | $< f \le 3.2 \text{ M}$ | IHz K F  | actor = 15  | 90          |

| CDVCTA    |               | irouit from Fic                       |                      | ntion 1, VOC          |                         | y)       |             |             |

| CRISIA    |               | ircuit from Fig<br>FCN value to       |                      |                       |                         | X)       |             |             |

|           |               | om Figure 16                          |                      |                       |                         |          |             |             |

|           |               | CN value to                           |                      |                       | 10/1                    |          |             |             |

|           |               | 0 <sup>3</sup> )/(R * C), wh          |                      | eneg renger           |                         |          |             |             |

|           | •             | icy of oscillati                      |                      |                       |                         |          |             |             |

|           |               | tor value in p                        |                      |                       |                         |          |             |             |

|           |               | resistor value                        |                      |                       |                         |          |             |             |

| C MODE    | (Circuit fror | n Figure 16.1                         | , Option 3; X        | (OSCMD = <sup>2</sup> | 10x)                    |          |             |             |

|           |               | Factor (KF) for                       | or the oscilla       | tion frequen          | cy desired:             |          |             |             |

|           | f = KF/(C *   | <sup>r</sup> V <sub>DD</sub> ), where |                      |                       |                         |          |             |             |

|           | f = frequen   | cy of oscillati                       | on in MHz            |                       |                         |          |             |             |

|           |               | tor value on X                        |                      |                       | -                       |          |             |             |

|           |               | er Supply on                          | MOLL in Male         | 1-                    |                         |          |             |             |

#### SFR Definition 16.5. OSCXCN: External Oscillator Control

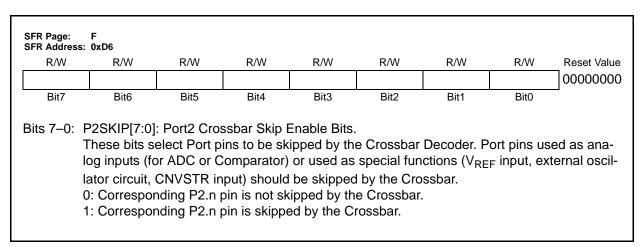

#### SFR Definition 17.18. P2SKIP: Port2 Skip

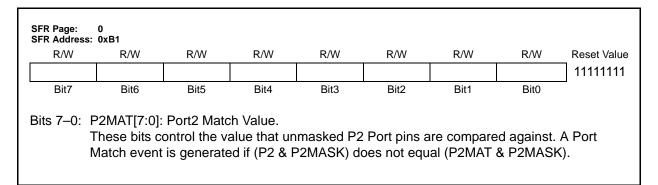

#### SFR Definition 17.19. P2MAT: Port2 Match

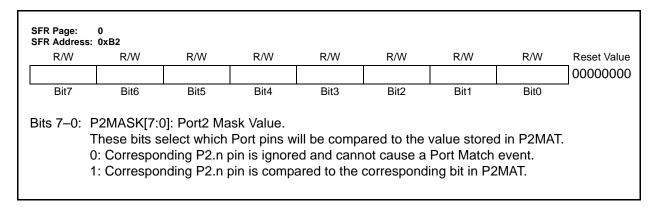

### SFR Definition 17.20. P2MASK: Port2 Mask

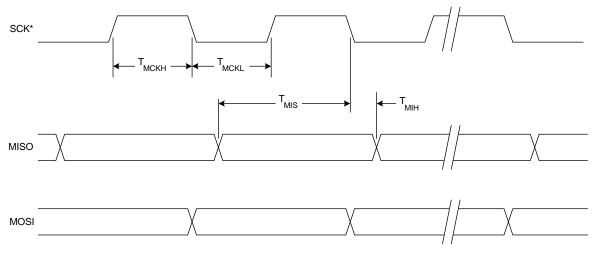

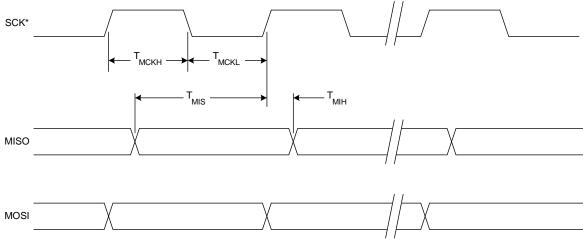

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

#### Figure 20.9. SPI Master Timing (CKPHA = 1)

### 22. Programmable Counter Array

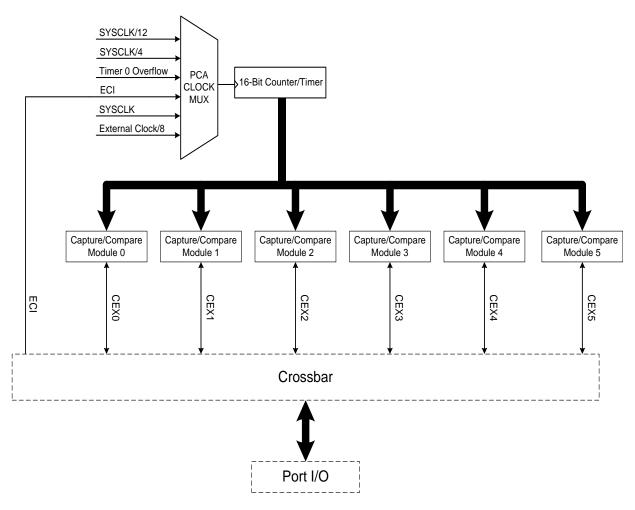

The Programmable Counter Array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. PCA0 consists of a dedicated 16-bit counter/timer and six 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled (See Section "17.3. General Purpose Port I/O" on page 189). The counter/timer is driven by a programmable timebase that can select between six inputs as its source: system clock, system clock divided by four, system clock divided by twelve, the external oscillator clock source divided by 8, Timer 0 overflow, or an external clock signal on the ECI line. Each capture/compare module may be configured to operate independently in one of six modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8-Bit PWM, or 16-Bit PWM (each is described in Section 22.2). The PCA is configured and controlled through the system controller's Special Function Registers. The basic PCA block diagram is shown in Figure 22.1.

**Important Note:** The PCA Module 5 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. Access to certain PCA registers is restricted while WDT mode is enabled. See Section 22.3 for details.

Figure 22.1. PCA Block Diagram

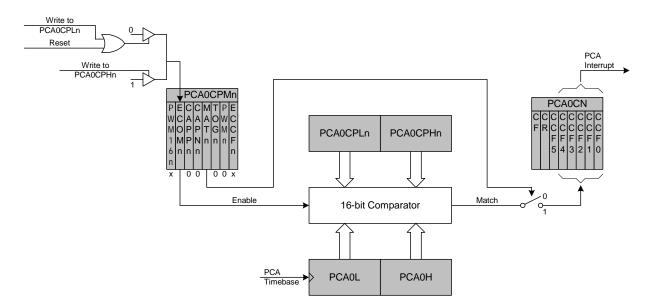

#### 22.2.2. Software Timer (Compare) Mode

In Software Timer mode, the PCA0 counter/timer is compared to the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic '1' and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the ECOMn and MATn bits in the PCA0CPMn register enables Software Timer mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

Figure 22.5. PCA Software Timer Mode Diagram

| System Clock (Hz)                                                                                                  | PCA0CPL5 | Timeout Interval (ms)     |

|--------------------------------------------------------------------------------------------------------------------|----------|---------------------------|

| 24,500,000                                                                                                         | 255      | 32.1                      |

| 24,500,000                                                                                                         | 128      | 16.2                      |

| 24,500,000                                                                                                         | 32       | 4.1                       |

| 18,432,000                                                                                                         | 255      | 42.7                      |

| 18,432,000                                                                                                         | 128      | 21.5                      |

| 18,432,000                                                                                                         | 32       | 5.5                       |

| 11,059,200                                                                                                         | 255      | 71.1                      |

| 11,059,200                                                                                                         | 128      | 35.8                      |

| 11,059,200                                                                                                         | 32       | 9.2                       |

| 3,062,500 <sup>2</sup>                                                                                             | 255      | 257                       |

| 3,062,500 <sup>2</sup>                                                                                             | 128      | 129.5                     |

| 3,062,500 <sup>2</sup>                                                                                             | 32       | 33.1                      |

| 191,406                                                                                                            | 255      | 4109                      |

| 191,406                                                                                                            | 128      | 2070                      |

| 191,406                                                                                                            | 32       | 530                       |

| 32,000                                                                                                             | 255      | 24576                     |

| 32,000                                                                                                             | 128      | 12384                     |

| 32,000                                                                                                             | 32       | 3168                      |

| <ul> <li>Iotes:</li> <li>1. Assumes SYSCLK/<br/>of 0x00 at the updat</li> <li>2. Internal oscillator re</li> </ul> | e time.  | source, and a PCA0L value |

## Table 22.3. Watchdog Timer Timeout Intervals<sup>1</sup>