# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                              |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 100MHz                                                           |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART        |

| Peripherals                | POR, PWM, WDT                                                    |

| Number of I/O              | 39                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 1K x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                        |

| Data Converters            | -                                                                |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 48-TQFP                                                          |

| Supplier Device Package    | 48-TQFP (7x7)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f363-c-gq |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

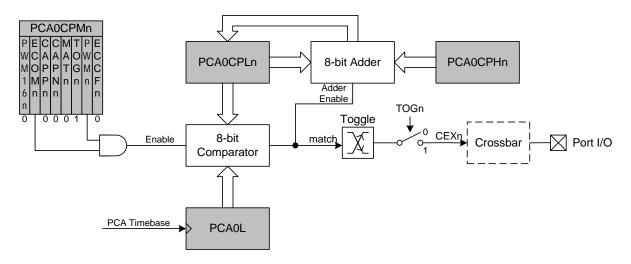

| Figure 22.7. PCA Frequency Output Mode                 | 268 |

|--------------------------------------------------------|-----|

| Figure 22.8. PCA 8-Bit PWM Mode Diagram                |     |

| Figure 22.9. PCA 16-Bit PWM Mode                       |     |

| Figure 22.10. PCA Module 5 with Watchdog Timer Enabled | 271 |

| 23. Revision Specific Behavior                         |     |

| Figure 23.1. Device Package - TQFP 48                  | 279 |

| Figure 23.2. Device Package - LQFP 32                  | 280 |

| Figure 23.3. Device Package - QFN 28                   | 280 |

| 24. C2 Interface                                       |     |

| Figure 24.1. Typical C2 Pin Sharing                    | 285 |

#### 5.3. Modes of Operation

ADC0 has a maximum conversion speed of 200 ksps. The ADC0 conversion clock is a divided version of the system clock, determined by the AD0SC bits in the ADC0CF register (system clock divided by (AD0SC + 1) for  $0 \le AD0SC \le 31$ ).

#### 5.3.1. Starting a Conversion

A conversion can be initiated in one of five ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM2-0) in register ADC0CN. Conversions may be initiated by one of the following:

- 1. Writing a '1' to the AD0BUSY bit of register ADC0CN

- 2. A Timer 0 overflow (i.e., timed continuous conversions)

- 3. A Timer 2 overflow

- 4. A Timer 1 overflow

- 5. A rising edge on the CNVSTR input signal

- 6. A Timer 3 overflow

Writing a '1' to AD0BUSY provides software control of ADC0 whereby conversions are performed "ondemand". During conversion, the AD0BUSY bit is set to logic '1' and reset to logic '0' when the conversion is complete. The falling edge of AD0BUSY triggers an interrupt (when enabled) and sets the ADC0 interrupt flag (AD0INT). Note: When polling for ADC conversion completions, the ADC0 interrupt flag (AD0INT) should be used. Converted data is available in the ADC0 data registers, ADC0H:ADC0L, when bit AD0INT is logic '1'. Note that when Timer 2 or Timer 3 overflows are used as the conversion source, Low Byte overflows are used if Timer 2/3 is in 8-bit mode; High byte overflows are used if Timer 2/3 is in 16-bit mode. See Section "21. Timers" on page 245 for timer configuration.

**Important Note About Using CNVSTR:** The CNVSTR input pin also functions as Port pin P0.7 on the C8051F360 devices and Port pin P0.6 on the C8051F361/2/6/7/8/9 devices. When the CNVSTR input is used as the ADC0 conversion source, the corresponding port pin should be skipped by the Digital Crossbar. To configure the Crossbar to skip the port pin, set the appropriate bit to '1' in register P0SKIP. See Section "17. Port Input/Output" on page 182 for details on Port I/O configuration.

### SFR Definition 8.5. CPT1MX: Comparator1 MUX Selection

|           | R/W                   | R/W                      | R/W R/W                                                     |                           | R/W        | R/W           | R/W      | Reset Value |

|-----------|-----------------------|--------------------------|-------------------------------------------------------------|---------------------------|------------|---------------|----------|-------------|

| -         | -                     | CMX1N <sup>2</sup>       | CMX1N0                                                      |                           |            | CMX1P1        | CMX1P0   | 11111111    |

| Bit7      | Bit6                  | Bit5                     | Bit4                                                        | Bit3                      | Bit2       | Bit1          | Bit0     |             |

| Bits 7–6: | UNUSED.               | Read = 11b               | , Write = don                                               | 't care.                  |            |               |          |             |

| Bits 5–4: | CMX1N1-               | CMX1N0: C                | comparator1                                                 | Negative I                | nput MUX S | Select.       |          |             |

|           | These bits            | select whic              | h Port pin is ι                                             | used as th                | e Compara  | tor1 negative | e input. |             |

|           | CMX1N1                | CMX1N0                   | C8051F                                                      | 360/3                     | C8051F36   | 61/2/4/5/6/7/ | 8/9      |             |

|           | CIVIATINT             |                          | Negative                                                    | Input                     | Nega       | tive Input    |          |             |

|           | 0                     | 0                        | P2.1                                                        |                           |            | P1.3          |          |             |

|           | 0                     | 1                        | P2.6                                                        |                           |            | P1.7          |          |             |

|           | 1                     | 0                        | P3.4                                                        |                           |            | P2.3          |          |             |

|           | 1                     | 1                        | P4.0                                                        |                           |            | P2.7          |          |             |

|           | CMX1P1–<br>These bits | CMX1P0: C<br>select whic | ο, Write = don<br>omparator1 F<br>h Port pin is ι<br>C8051F | Positive In<br>used as th | e Compara  |               |          |             |

|           | CMX1P1 CMX1           |                          | Positive                                                    |                           |            | tive Input    | 0/3      |             |

|           | 0                     | 0                        | POSITIVE<br>P2.0                                            |                           | FUS        | P1.2          |          |             |

|           | 0                     | 1                        | P2.0                                                        |                           |            | P1.2<br>P1.6  |          |             |

|           | 0                     | 0                        | P2.5<br>P3.3                                                |                           |            | P2.2          |          |             |

|           | 1                     | •                        | P3.3<br>P3.7                                                |                           | P2.6       |               |          |             |

|           | 1                     | 1                        | P3.,                                                        | /                         |            |               |          |             |

| ADDRESS | SFR Page | 0(8)   | 1(9)             | 2(A)               | 3(B)               | 4(C)               | 5(D)               | 6(E)                | 7(F)                |

|---------|----------|--------|------------------|--------------------|--------------------|--------------------|--------------------|---------------------|---------------------|

| F8      | 0<br>F   | SPIOCN | PCA0L            | PCA0H              | PCA0CPL0           | PCA0CPH0           | PCA0CPL4           | PCA0CPH4            | VDM0CN              |

| F0      | 0<br>F   | В      | MAC0BL<br>P0MDIN | MAC0BH<br>P1MDIN   | P0MAT<br>P2MDIN    | P0MASK<br>P3MDIN   | PCA0CPL5           | PCA0CPH5            | -<br>EMI0TC         |

| E8      | 0<br>F   | ADC0CN | PCA0CPL1         | PCA0CPH1           | PCA0CPL2           | PCA0CPH2           | PCA0CPL3           | PCA0CPH3            | RSTSRC              |

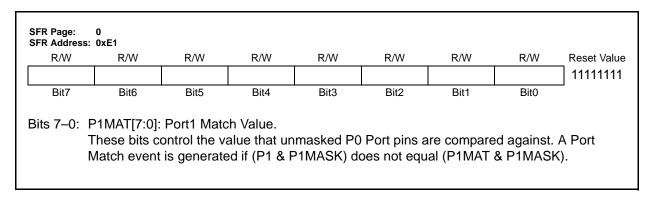

| E0      | 0<br>F   | ACC    | P1MAT<br>XBR0    | P1MASK<br>XBR1     | -                  | IT01CF             | -<br>SFR0CN        | EIE1                | EIE2                |

| D8      | 0<br>F   | PCA0CN | PCA0MD           | PCA0CPM0           | PCA0CPM1           | PCA0CPM2           | PCA0CPM3           | PCA0CPM4            | PCA0CPM5            |

| D0      | 0<br>F   | PSW    | REF0CN           | MAC0ACC0<br>CCH0LC | MAC0ACC1<br>CCH0MA | MAC0ACC2<br>P0SKIP | MAC0ACC3<br>P1SKIP | MAC0OVR<br>P2SKIP   | MAC0CF<br>P3SKIP    |

| C8      | 0<br>F   | TMR2CN | -<br>CCH0TN      | TMR2RLL            | TMR2RLH            | TMR2L              | TMR2H              | -<br>EIP1           | MAC0STA<br>EIP2     |

| C0      | 0<br>F   | SMB0CN | SMB0CF           | SMB0DAT            | ADC0GTL            | ADC0GTH            | ADC0LTL            | ADC0LTH             | -<br>EMI0CF         |

| B8      | 0<br>F   | IP     | IDA0CN           | AMX0N              | AMX0P              | ADC0CF             | ADC0L              | ADC0H               | -<br>OSCICL         |

| B0      | 0<br>F   | P3     | P2MAT<br>PLL0MUL | P2MASK<br>PLL0FLT  | -<br>PLL0CN        | -                  | P4                 | FLSCL<br>OSCXCN     | FLKEY<br>OSCICN     |

| A8      | 0<br>F   | IE     | -<br>PLL0DIV     | EMIOCN             | -                  | -<br>FLSTAT        | -<br>OSCLCN        | MAC0RNDL<br>P4MDOUT | MACORNDH<br>P3MDOUT |

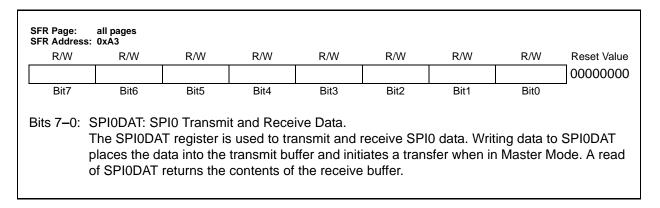

| A0      | 0<br>F   | P2     | SPI0CFG          | SPI0CKR            | SPI0DAT            | MAC0AL<br>P0MDOUT  | MAC0AH<br>P1MDOUT  | -<br>P2MDOUT        | SFRPAGE             |

| 98      | 0<br>F   | SCON0  | SBUF0            | CPT1CN             | CPT0CN             | CPT1MD             | CPT0MD             | CPT1MX              | CPT0MX              |

| 90      | 0<br>F   | P1     | TMR3CN           | TMR3RLL            | TMR3RLH            | TMR3L              | TMR3H              | IDA0L               | IDA0H               |

| 88      | 0<br>F   | TCON   | TMOD             | TL0                | TL1                | TH0                | TH1                | CKCON               | PSCTL<br>CLKSEL     |

| 80      | 0<br>F   | P0     | SP               | DPL                | DPH                | -<br>CCH0CN        | SFRNEXT            | SFRLAST             | PCON                |

|         |          | 0(8)   | 1(9)             | 2(A)               | 3(B)               | 4(C)               | 5(D)               | 6(E)                | 7(F)                |

Table 9.2. Special Function Register (SFR) Memory Map

bit-addressable shaded SFRs are accessible on all SFR Pages regardless of the contents of SFRPAGE

| (subtractio<br>AC: Auxilia<br>This bit is s<br>from (subt<br>F0: User F<br>This is a b<br>RS1–RS0:<br>These bits<br><b>RS1</b><br>0<br>0                                       | set when t<br>on). It is cle<br>ary Carry I<br>set when t<br>raction) th<br>Flag 0.<br>it-address<br>: Register                                                    | R/W<br>RS1<br>Bit4<br>the last arithmetic<br>eared to 0 by all of<br>Flag<br>he last arithmetic<br>e high order nibb<br>able, general pu<br>Bank Select.<br>ich register bank<br>Register Bank<br>0<br>1                          | other arith<br>c operation<br>ble. It is cle<br>rpose flag<br>k is used c<br>Addr<br>0x00-                                                                                                                                                                                                                                                                              | metic oper<br>n resulted ir<br>eared to 0 l<br>for use un<br>luring regis<br>ess<br>0x07                                                                                                                                                                                                                                                                                                                                                      | ations.<br>n a carry int<br>by all other<br>der softwar                                                                                                                                                                                                                                                                                                                                                                                                                                                    | o (addition)<br>arithmetic o<br>e control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | or a borrow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                           |                                                                                                                |                                                                                                     |                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Bit6<br>CY: Carry<br>This bit is s<br>(subtractio<br>AC: Auxilia<br>This bit is s<br>from (subt<br>F0: User F<br>This is a b<br>RS1–RS0:<br>These bits<br><b>RS1</b><br>0<br>0 | Bit5<br>Flag.<br>set when t<br>on). It is cle<br>ary Carry I<br>set when t<br>raction) th<br>Flag 0.<br>it-address<br>: Register<br>s select wh<br><b>RS0</b><br>0 | Bit4<br>Bit4<br>Bit4<br>Bared to 0 by all of<br>Flag<br>he last arithmetic<br>e high order nibb<br>able, general pu<br>Bank Select.<br>ich register bank<br>Register Bank<br>0                                                    | Bit3<br>c operatio<br>other arith<br>c operatior<br>ole. It is clo<br>rpose flag<br>c is used c<br>Addr<br>0x00–                                                                                                                                                                                                                                                        | Bit2<br>n resulted<br>metic oper<br>n resulted ir<br>eared to 0 l<br>for use un<br>luring regis<br>ess<br>0x07                                                                                                                                                                                                                                                                                                                                | Bit1<br>Bit1<br>in a carry (a<br>ations.<br>n a carry int<br>oy all other<br>der softwar                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit0<br>addition) or<br>to (addition)<br>arithmetic o<br>re control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | a borrow<br>or a borrow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                           |                                                                                                                |                                                                                                     |                                                                  |

| CY: Carry<br>This bit is<br>(subtractio<br>AC: Auxilia<br>This bit is s<br>from (subt<br>F0: User F<br>This is a b<br>RS1–RS0:<br>These bits<br><b>RS1</b><br>0<br>0           | Flag.<br>set when to<br>on). It is cleary Carry F<br>set when to<br>raction) the<br>Flag 0.<br>it-address<br>: Register<br>s select when<br><b>RS0</b><br>0        | the last arithmeti<br>eared to 0 by all<br>Flag<br>he last arithmetic<br>e high order nibb<br>able, general pu<br>Bank Select.<br>ich register bank<br>Register Bank                                                              | c operatio<br>other arith<br>c operatior<br>ole. It is clo<br>rpose flag<br>c is used c<br>Addr<br>0x00-                                                                                                                                                                                                                                                                | n resulted<br>metic oper<br>n resulted ir<br>eared to 0 l<br>for use un<br>luring regis<br>ess<br>0x07                                                                                                                                                                                                                                                                                                                                        | in a carry (a<br>ations.<br>n a carry int<br>by all other<br>der softwar                                                                                                                                                                                                                                                                                                                                                                                                                                   | addition) or<br>to (addition)<br>arithmetic o<br>re control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | or a borrow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                           |                                                                                                                |                                                                                                     |                                                                  |

| This bit is<br>(subtractio<br>AC: Auxilia<br>This bit is<br>from (subt<br>F0: User F<br>This is a b<br>RS1–RS0:<br>These bits<br><b>RS1</b><br>0<br>0                          | set when t<br>on). It is cle<br>ary Carry I<br>set when t<br>raction) th<br>flag 0.<br>iit-address<br>: Register<br>: select wh<br><b>RS0</b><br>0                 | eared to 0 by all o<br>Flag<br>he last arithmetic<br>e high order nibb<br>able, general pu<br>Bank Select.<br>ich register bank<br>Register Bank<br>0                                                                             | other arith<br>c operation<br>ble. It is cle<br>rpose flag<br>k is used c<br>Addr<br>0x00-                                                                                                                                                                                                                                                                              | metic oper<br>o resulted in<br>eared to 0 l<br>for use un<br>luring regis<br>ess<br>0x07                                                                                                                                                                                                                                                                                                                                                      | ations.<br>n a carry int<br>by all other<br>der softwar                                                                                                                                                                                                                                                                                                                                                                                                                                                    | o (addition)<br>arithmetic o<br>e control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | or a borrow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                           |                                                                                                                |                                                                                                     |                                                                  |

| (subtractio<br>AC: Auxilia<br>This bit is s<br>from (subt<br>F0: User F<br>This is a b<br>RS1–RS0:<br>These bits<br><b>RS1</b><br>0<br>0                                       | on). It is cle<br>ary Carry I<br>set when t<br>raction) th<br>Flag 0.<br>it-address<br>: Register<br>s select wh<br><b>RS0</b><br>0                                | eared to 0 by all o<br>Flag<br>he last arithmetic<br>e high order nibb<br>able, general pu<br>Bank Select.<br>ich register bank<br>Register Bank<br>0                                                                             | other arith<br>c operation<br>ble. It is cle<br>rpose flag<br>k is used c<br>Addr<br>0x00-                                                                                                                                                                                                                                                                              | metic oper<br>o resulted in<br>eared to 0 l<br>for use un<br>luring regis<br>ess<br>0x07                                                                                                                                                                                                                                                                                                                                                      | ations.<br>n a carry int<br>by all other<br>der softwar                                                                                                                                                                                                                                                                                                                                                                                                                                                    | o (addition)<br>arithmetic o<br>e control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | or a borrow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                           |                                                                                                                |                                                                                                     |                                                                  |

| AC: Auxilia<br>This bit is s<br>from (subt<br>F0: User F<br>This is a b<br>RS1–RS0:<br>These bits<br><b>RS1</b><br>0<br>0                                                      | ary Carry I<br>set when t<br>raction) th<br>Flag 0.<br>it-address<br>: Register<br>s select wh<br><b>RS0</b><br>0                                                  | Flag<br>he last arithmetic<br>e high order nibb<br>able, general pu<br>Bank Select.<br>ich register bank<br>Register Bank<br>0                                                                                                    | c operation<br>ole. It is clo<br>rpose flag<br>c is used c<br>Addr<br>0x00–                                                                                                                                                                                                                                                                                             | n resulted in<br>eared to 0 l<br>for use un<br>luring regis<br>ess<br>0x07                                                                                                                                                                                                                                                                                                                                                                    | n a carry int<br>by all other<br>der softwar                                                                                                                                                                                                                                                                                                                                                                                                                                                               | arithmetic o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                           |                                                                                                                |                                                                                                     |                                                                  |

| This bit is s<br>from (subt<br>F0: User F<br>This is a b<br>RS1–RS0:<br>These bits<br><b>RS1</b><br>0<br>0                                                                     | set when t<br>raction) th<br>Flag 0.<br>it-address<br>: Register<br>s select wh<br><b>RS0</b><br>0                                                                 | he last arithmetic<br>e high order nibb<br>able, general pu<br>Bank Select.<br>ich register bank<br>Register Bank<br>0                                                                                                            | ole. It is clo<br>rpose flag<br>( is used c<br>Addr<br>0x00-                                                                                                                                                                                                                                                                                                            | eared to 0 for use un<br>luring regis<br>ess<br>0x07                                                                                                                                                                                                                                                                                                                                                                                          | by all other<br>der softwar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | arithmetic o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                           |                                                                                                                |                                                                                                     |                                                                  |

| F0: User F<br>This is a b<br>RS1–RS0:<br>These bits<br><b>RS1</b><br>0<br>0                                                                                                    | Flag 0.<br>it-address<br>: Register<br>: select wh<br>RS0<br>0                                                                                                     | able, general pu<br>Bank Select.<br>ich register bank<br><b>Register Bank</b><br>0                                                                                                                                                | rpose flag<br>k is used c<br>Addr<br>0x00–                                                                                                                                                                                                                                                                                                                              | for use un<br>luring regis<br><b>ess</b><br>0x07                                                                                                                                                                                                                                                                                                                                                                                              | der softwar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | e control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                           |                                                                                                                |                                                                                                     |                                                                  |

| This is a b<br>RS1–RS0<br>These bits<br><b>RS1</b><br>0<br>0                                                                                                                   | it-address<br>: Register<br>: select wh<br>RS0<br>0                                                                                                                | Bank Select.<br>ich register bank<br>Register Bank<br>0                                                                                                                                                                           | k is used c<br>Addr<br>0x00-                                                                                                                                                                                                                                                                                                                                            | luring regis<br><b>ess</b><br>0x07                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                           |                                                                                                                |                                                                                                     |                                                                  |

| RS1–RS0:<br>These bits<br>RS1<br>0<br>0                                                                                                                                        | : Register<br>select wh<br><b>RS0</b><br>0                                                                                                                         | Bank Select.<br>ich register bank<br>Register Bank<br>0                                                                                                                                                                           | k is used c<br>Addr<br>0x00-                                                                                                                                                                                                                                                                                                                                            | luring regis<br><b>ess</b><br>0x07                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                           |                                                                                                                |                                                                                                     |                                                                  |

| These bits RS1 0 0                                                                                                                                                             | select wh                                                                                                                                                          | ich register bank<br>Register Bank<br>0                                                                                                                                                                                           | Addr<br>0x00-                                                                                                                                                                                                                                                                                                                                                           | <b>ess</b><br>0x07                                                                                                                                                                                                                                                                                                                                                                                                                            | ter accesse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | es.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                           |                                                                                                                |                                                                                                     |                                                                  |

| <b>RS1</b><br>0<br>0                                                                                                                                                           | <b>RS0</b><br>0                                                                                                                                                    | Register Bank                                                                                                                                                                                                                     | Addr<br>0x00-                                                                                                                                                                                                                                                                                                                                                           | <b>ess</b><br>0x07                                                                                                                                                                                                                                                                                                                                                                                                                            | ter access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | es.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                           |                                                                                                                |                                                                                                     |                                                                  |

| 0<br>0                                                                                                                                                                         | 0                                                                                                                                                                  | 0                                                                                                                                                                                                                                 | 0x00-                                                                                                                                                                                                                                                                                                                                                                   | 0x07                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                           |                                                                                                                |                                                                                                     |                                                                  |

| 0                                                                                                                                                                              |                                                                                                                                                                    |                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                           |                                                                                                                |                                                                                                     |                                                                  |

|                                                                                                                                                                                | 1                                                                                                                                                                  | 1                                                                                                                                                                                                                                 | 0x08–                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                           |                                                                                                                |                                                                                                     |                                                                  |

|                                                                                                                                                                                |                                                                                                                                                                    |                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                         | 0 1 1 0x08–0x0F                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                           |                                                                                                                |                                                                                                     |                                                                  |

| 1         0         2         0x10–0x17           1         1         3         0x18–0x1F                                                                                      |                                                                                                                                                                    |                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                           |                                                                                                                |                                                                                                     |                                                                  |

|                                                                                                                                                                                |                                                                                                                                                                    |                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | This bit is :<br>• An ADD,<br>• A MUL in<br>• A DIV ins<br>The OV bit<br>cases.<br>F1: User F<br>This is a b<br>PARITY: P | set to 1 ur<br>ADDC, or<br>astruction c<br>struction c<br>t is cleared<br>Flag 1.<br>it-address<br>Parity Flag | SUBB instruction<br>results in an over<br>auses a divide-b<br>d to 0 by the ADI<br>able, general pu | on causes<br>rflow (resu<br>y-zero cor<br>D, ADDC,<br>rpose flag |