Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                              |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 100MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                 |

| Peripherals                | POR, PWM, WDT                                                    |

| Number of I/O              | 25                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 1K x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                        |

| Data Converters            | -                                                                |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 28-VFQFN Exposed Pad                                             |

| Supplier Device Package    | 28-QFN (5x5)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f365-c-gm |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | Figure 8.2. Comparator1 Functional Block Diagram<br>Figure 8.3. Comparator Hysteresis Plot |       |

|-----|--------------------------------------------------------------------------------------------|-------|

| 9.  | CIP-51 Microcontroller                                                                     |       |

|     | Figure 9.1. CIP-51 Block Diagram                                                           |       |

|     | Figure 9.2. Memory Map                                                                     | . 86  |

|     | Figure 9.3. SFR Page Stack                                                                 |       |

|     | Figure 9.4. SFR Page Stack While Using SFR Page 0x0F To Access OSCICN                      |       |

|     | Figure 9.5. SFR Page Stack After ADC0 Window Comparator Interrupt Occurs                   |       |

|     | Figure 9.6. SFR Page Stack Upon PCA Interrupt Occurring During an ADC0 ISR                 |       |

|     | Figure 9.7. SFR Page Stack Upon Return From PCA Interrupt                                  |       |

|     | Figure 9.8. SFR Page Stack Upon Return From ADC2 Window Interrupt                          | . 93  |

|     | Interrupt Handler                                                                          |       |

| 11. | Multiply And Accumulate (MAC0)                                                             |       |

|     | Figure 11.1. MAC0 Block Diagram                                                            | 117   |

|     | Figure 11.2. Integer Mode Data Representation                                              |       |

|     | Figure 11.3. Fractional Mode Data Representation                                           |       |

|     | Figure 11.4. MAC0 Pipeline                                                                 | 119   |

| 12  | Reset Sources                                                                              |       |

|     | Figure 12.1. Reset Sources                                                                 |       |

|     | Figure 12.2. Power-On and VDD Monitor Reset Timing                                         | 129   |

| 13  | Flash Memory                                                                               |       |

|     | Figure 13.1. Flash Program Memory Map                                                      | 138   |

| 14  | Branch Target Cache                                                                        |       |

|     | Figure 14.1. Branch Target Cache Data Flow                                                 |       |

|     | Figure 14.2. Branch Target Cache Organization                                              |       |

|     | Figure 14.3. Cache Lock Operation                                                          | 147   |

| 15  | External Data Memory Interface and On-Chip XRAM                                            | . = 0 |

|     | Figure 15.1. Multiplexed Configuration Example                                             |       |

|     | Figure 15.2. Non-multiplexed Configuration Example                                         |       |

|     | Figure 15.3. EMIF Operating Modes                                                          |       |

|     | Figure 15.4. Non-multiplexed 16-bit MOVX Timing                                            |       |

|     | Figure 15.5. Non-multiplexed 8-bit MOVX without Bank Select Timing                         |       |

|     | Figure 15.6. Non-multiplexed 8-bit MOVX with Bank Select Timing                            |       |

|     | Figure 15.7. Multiplexed 16-bit MOVX Timing                                                |       |

|     | Figure 15.8. Multiplexed 8-bit MOVX without Bank Select Timing                             |       |

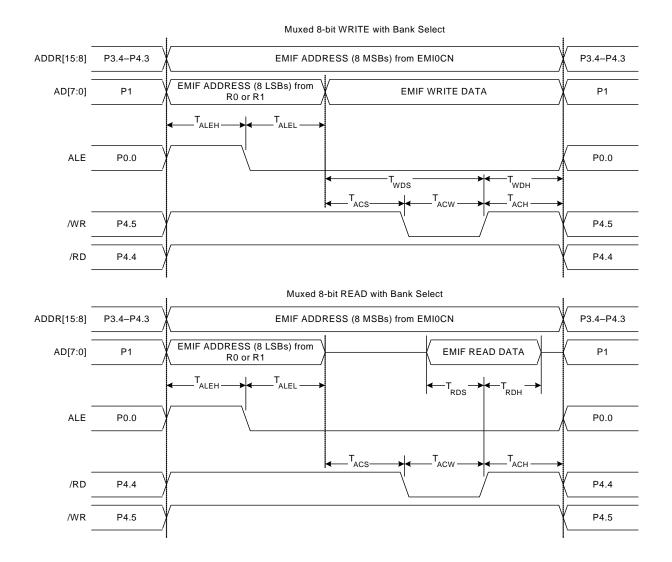

| 40  | Figure 15.9. Multiplexed 8-bit MOVX with Bank Select Timing                                | 166   |

| 16  | Oscillators                                                                                | 400   |

|     | Figure 16.1. Oscillator Diagram                                                            |       |

|     | Figure 16.2. 32.768 kHz External Crystal Example                                           |       |

| 47  | Figure 16.3. PLL Block Diagram                                                             | 1//   |

| 17. | Port Input/Output                                                                          | 100   |

|     | Figure 17.1. Port I/O Functional Block Diagram (Port 0 through Port 3)                     |       |

|     | Figure 17.2. Port I/O Cell Block Diagram                                                   |       |

|     | Figure 17.3. Crossbar Priority Decoder with No Pins Skipped                                |       |

|     | Figure 17.4. Crossbar Priority Decoder with Port Pins Skipped                              | 100   |

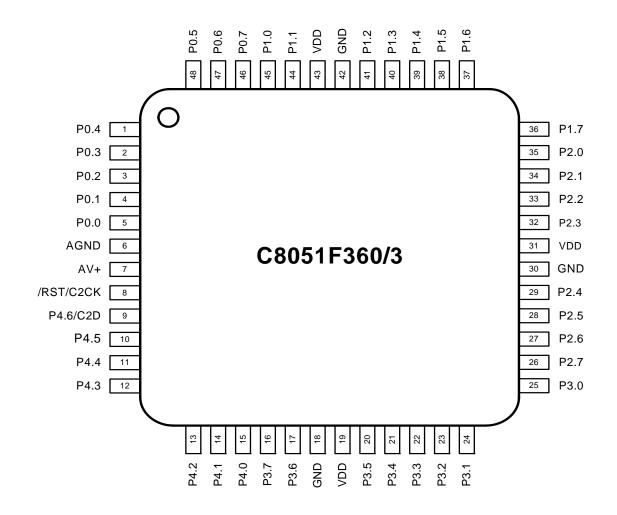

Figure 4.1. TQFP-48 Pinout Diagram (Top View)

complete Port I/O configuration details. The TEMPE bit in register REF0CN enables/disables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any ADC0 measurements performed on the sensor result in meaningless data.

| R      | R                       | R           | R                 | R/W         | R/W          | R/W         | R/W   | Reset Value |

|--------|-------------------------|-------------|-------------------|-------------|--------------|-------------|-------|-------------|

| -      | -                       | -           | -                 | REFSL       | TEMPE        | BIASE       | REFBE | 00000000    |

| Bit7   | Bit6                    | Bit5        | Bit4              | Bit3        | Bit2         | Bit1        | Bit0  | J           |

|        |                         |             |                   | 1           |              |             |       |             |

|        | UNUSED. R               |             | -                 | ion't care. |              |             |       |             |

| Bit 3: | REFSL: Volt             | •           |                   |             | ,            |             |       |             |

|        | This bit selec          |             |                   |             | ige referenc | e.          |       |             |

|        | 0: VREF pin             |             | •                 | ence.       |              |             |       |             |

|        | 1: V <sub>DD</sub> used | as voltage  | reference.        |             |              |             |       |             |

| Bit 2: | TEMPE: Ten              | nperature S | Sensor Enab       | ole Bit.    |              |             |       |             |

|        | 0: Internal Te          | emperature  | Sensor off.       |             |              |             |       |             |

|        | 1: Internal Te          | emperature  | Sensor on.        |             |              |             |       |             |

| Bit 1: | BIASE: Inter            | nal Analog  | <b>Bias Gener</b> | ator Enable | e Bit.       |             |       |             |

|        | 0: Internal Bi          | as Genera   | tor off.          |             |              |             |       |             |

|        | 1: Internal Bi          | as Genera   | tor on.           |             |              |             |       |             |

| Bit 0: | REFBE: Inte             | rnal Refere | ence Buffer       | Enable Bit. |              |             |       |             |

|        | 0: Internal R           | eference B  | uffer disable     | ed.         |              |             |       |             |

|        |                         |             |                   |             |              | rence drive |       |             |

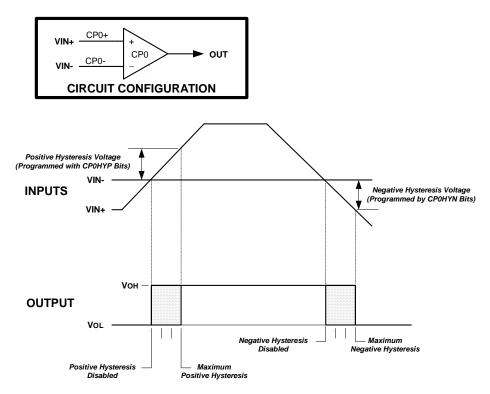

Figure 8.3. Comparator Hysteresis Plot

The Comparator hysteresis is software-programmable via the Comparator Control registers CPT0CN and CPT1CN. The user can program both the amount of hysteresis voltage (referred to the input voltage) and the positive and negative-going symmetry of this hysteresis around the threshold voltage.

The Comparator hysteresis is programmed using Bits3–0 in the Comparator Control registers CPT0CN and CPT1CN (shown in SFR Definition 8.1 and SFR Definition 8.4). The amount of negative hysteresis voltage is determined by the settings of the CP0HYN and CP1HYN bits. As shown in Figure 8.3, settings of 20, 10 or 5 mV of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CP0HYP and CP1HYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see Section "10. Interrupt Handler" on page 107). The CP0FIF or CP1FIF flag is set to logic '1' upon a Comparator falling-edge occurrence, and the CP0RIF or CP1RIF flag is set to logic '1' upon the Comparator rising-edge occurrence. Once set, these bits remain set until cleared by software. The Comparator rising-edge interrupt mask is enabled by setting CP0RIE or CP1RIE to a logic '1'. The Comparator falling-edge interrupt mask is enabled by setting CP0FIE or CP1FIE to a logic '1'.

The output state of the Comparator can be obtained at any time by reading the CP0OUT or CP1OUT bit. The Comparator is enabled by setting the CP0EN or CP1EN bit to logic '1', and is disabled by clearing this bit to logic '0'.

Note that false rising edges and falling edges can be detected when the comparator is first powered on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic '0' a short time after the comparator is enabled or its mode bits have been changed. This Power Up Time is specified in Table 8.1 on page 79.

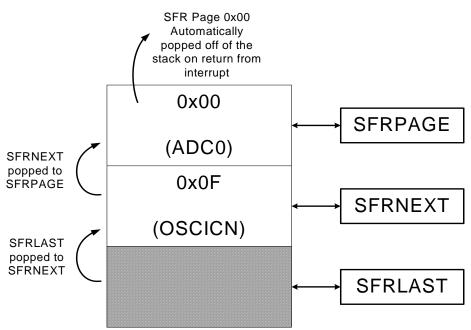

On exit from the PCA interrupt service routine, the CIP-51 will return to the ADC0 Window Comparator ISR. On execution of the RETI instruction, SFR Page 0x00 used to access the PCA registers will be automatically popped off of the SFR Page Stack, and the contents of the SFRNEXT register will be moved to the SFRPAGE register. Software in the ADC0 ISR can continue to access SFR's as it did prior to the PCA interrupt. Likewise, the contents of SFRLAST are moved to the SFRNEXT register. Recall this was the SFR Page value 0x0F being used to access OSCICN before the ADC0 interrupt occurred. See Figure 9.7 below.

Figure 9.7. SFR Page Stack Upon Return From PCA Interrupt

| SFR Addre   |                               |      | essable) | DAA           | DAA                                 |          | DAA  | Deschild    |

|-------------|-------------------------------|------|----------|---------------|-------------------------------------|----------|------|-------------|

| R           | R/W                           | R/W  | R/W      | R/W           | R/W                                 | R/W      | R/W  | Reset Value |

| _           | PSPI0                         | PT2  | PS0      | PT1           | PX1                                 | PT0      | PX0  | 1000000     |

| Bit7        | Bit6                          | Bit5 | Bit4     | Bit3          | Bit2                                | Bit1     | Bit0 |             |

| Bit 7:      | UNUSED. R                     |      |          |               |                                     |          |      |             |

| Bit 6:      | PSPI0: Seria                  | •    | ,        | ,             | rupt Priority                       | Control. |      |             |

|             | This bit sets                 |      |          |               |                                     |          |      |             |

|             | 0: SPI0 inter                 |      |          |               |                                     |          |      |             |

|             | 1: SPI0 inter                 |      |          |               |                                     |          |      |             |

| Bit 5:      | PT2: Timer 2                  |      |          |               |                                     |          |      |             |

|             | This bit sets                 |      |          |               | t.                                  |          |      |             |

|             | 0: Timer 2 int                |      |          |               |                                     |          |      |             |

| <b>D</b> 11 | 1: Timer 2 int                |      | • •      |               |                                     |          |      |             |

| Bit 4:      | PS0: UARTO                    |      |          |               |                                     |          |      |             |

|             | This bit sets                 |      |          |               | τ.                                  |          |      |             |

|             | 0: UART0 int                  |      |          |               |                                     |          |      |             |

| Bit 3:      | 1: UART0 int                  | •    | • •      |               |                                     |          |      |             |

| DIL J.      | PT1: Timer 1<br>This bit sets |      |          |               | +                                   |          |      |             |

|             | 0: Timer 1 inf                |      |          |               | ι.                                  |          |      |             |

|             | 1: Timer 1 int                |      |          |               |                                     |          |      |             |

| Bit 2:      | PX1: Externa                  |      | • •      |               |                                     |          |      |             |

| DIL Z.      | This bit sets                 |      |          |               | ot 1 interrup                       | .+       |      |             |

|             | 0: External Ir                |      |          |               | ot i interiup                       | <i>.</i> |      |             |

|             | 1: External Ir                |      |          |               |                                     |          |      |             |

| Bit 1:      | PT0: Timer 0                  |      | • •      |               |                                     |          |      |             |

| Dit 1.      | This bit sets                 |      |          |               | t                                   |          |      |             |

|             | 0: Timer 0 int                |      |          |               |                                     |          |      |             |

|             | 1: Timer 0 int                |      |          |               |                                     |          |      |             |

| Bit 0:      | PX0: Externa                  |      |          |               |                                     |          |      |             |

| 2.1 01      | This bit sets                 |      |          |               | ot 0 interrup                       | ot.      |      |             |

|             | 0: External Ir                |      |          |               | · · · · · · · · · · · · · · · · · · |          |      |             |

|             |                               |      |          | iority level. |                                     |          |      |             |

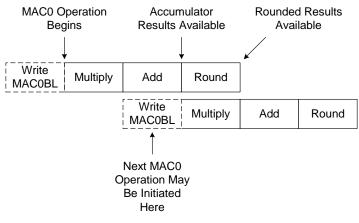

#### 11.3. Operating in Multiply and Accumulate Mode

MAC0 operates in Multiply and Accumulate (MAC) mode when the MACOMS bit (MAC0CF.0) is cleared to '0'. When operating in MAC mode, MAC0 performs a 16-by-16 bit multiply on the contents of the MAC0A and MAC0B registers, and adds the result to the contents of the 40-bit MAC0 accumulator. Figure 11.4 shows the MAC0 pipeline. There are three stages in the pipeline, each of which takes exactly one SYSCLK cycle to complete. The MAC operation is initiated with a write to the MAC0BL register. After the MAC0BL register is written, MAC0A and MAC0B are multiplied on the first SYSCLK cycle. During the second stage of the MAC0 pipeline, the results of the multiplication are added to the current accumulator contents, and the result of the addition is stored in the MAC0 accumulator. The status flags in the MAC0STA register are set after the end of the second pipeline stage. During the second stage of the pipeline, the next multiplication are determined by writing to the MAC0BL register, if it is desired. The rounded (and optionally, saturated) result is available in the MAC0RNDH and MAC0RNDL registers at the end of the third pipeline stage. If the MAC0CA bit (MAC0CF.3) is set to '1' when the MAC operation is initiated, the accumulator and all MAC0STA flags will be cleared during the next cycle of the controller's clock (SYSCLK). The MAC0CA bit will clear itself to '0' when the clear operation is complete.

Figure 11.4. MAC0 Pipeline

#### 11.4. Operating in Multiply Only Mode

MAC0 operates in Multiply Only mode when the MAC0MS bit (MAC0CF.0) is set to '1'. Multiply Only mode is identical to Multiply and Accumulate mode, except that the multiplication result is added with a value of zero before being stored in the MAC0 accumulator (i.e. it overwrites the current accumulator contents). The result of the multiplication is available in the MAC0 accumulator registers at the end of the second MAC0 pipeline stage (two SYSCLKs after writing to MAC0BL). As in MAC mode, the rounded result is available in the MAC0 Rounding Registers after the third pipeline stage. Note that in Multiply Only mode, the MAC0HO flag is not affected.

#### 11.5. Accumulator Shift Operations

MAC0 contains a 1-bit arithmetic shift function which can be used to shift the contents of the 40-bit accumulator left or right by one bit. The accumulator shift is initiated by writing a '1' to the MAC0SC bit (MAC0CF.5), and takes one SYSCLK cycle (the rounded result is available in the MAC0 Rounding Registers after a second SYSCLK cycle, and MAC0SC is cleared to '0'). The direction of the arithmetic shift is controlled by the MAC0SD bit (MAC0CF.4). When this bit is cleared to '0', the MAC0 accumulator will shift left. When the MAC0SD bit is set to '1', the MAC0 accumulator will shift right. Right-shift operations are sign-extended with the current value of bit 39. Note that the status flags in the MAC0STA register are not affected by shift operations.

The replacement algorithm is selected with the Cache Algorithm bit, CHALGM (CCH0TN.3). When CHALGM is cleared to '0', the cache will use the rebound algorithm to replace cache locations. The rebound algorithm replaces locations in order from the beginning of cache memory to the end, and then from the end of cache memory to the beginning. When CHALGM is set to '1', the cache will use the pseudo-random algorithm to replace cache locations. The pseudo-random algorithm uses a pseudo-random number to determine which cache location to replace. The cache can be manually emptied by writing a '1' to the CHFLUSH bit (CCH0CN.4).

### 14.2. Cache and Prefetch Optimization

By default, the branch target cache is configured to provide code speed improvements for a broad range of circumstances. **In most applications, the cache control registers should be left in their reset states.** Sometimes it is desirable to optimize the execution time of a specific routine or critical timing loop. The branch target cache includes options to exclude caching of certain types of data, as well as the ability to pre-load and lock time-critical branch locations to optimize execution speed.

The most basic level of cache control is implemented with the Cache Miss Penalty Threshold bits, CHMSTH (CCH0TN.1–0). If the processor is stalled during a prefetch operation for more clock cycles than the number stored in CHMSTH, the requested data will be cached when it becomes available. The CHMSTH bits are set to zero by default, meaning that any time the processor is stalled, the new data will be cached. If, for example, CHMSTH is equal to 2, any cache miss causing a delay of 3 or 4 clock cycles will be cached, while a cache miss causing a delay of 1–2 clock cycles will not be cached.

#### 15.6.2.3.8-bit MOVX with Bank Select: EMI0CF[4:2] = '010'.

Figure 15.9. Multiplexed 8-bit MOVX with Bank Select Timing

| R/W       | R/W                                     | R/W                       | R/W          | R/W           | R/W           | R/W            | R/W           | Reset Value  |

|-----------|-----------------------------------------|---------------------------|--------------|---------------|---------------|----------------|---------------|--------------|

| Reserve   | d Reserved                              | CLKDIV1                   | CLKDIV0      | Reserved      | CLKSL2        | CLKSL1         | CLKSL0        | 00000000     |

| Bit7      | Bit6                                    | Bit5                      | Bit4         | Bit3          | Bit2          | Bit1           | Bit0          | 1            |

| 2.10 . 0. | RESERVED                                |                           |              |               |               |                |               |              |

| Bits 5–4: | CLKDIV1-0:                              | •                         |              |               |               |                |               |              |

|           | These bits ca                           | an be used                | to pre-divid | e SYSCLK      | before it is  | output to a    | port pin thr  | ough the     |

|           | crossbar.<br>00: Output w               | ill ha SVSC               | אוי          |               |               |                |               |              |

|           | 00. Output w                            |                           |              |               |               |                |               |              |

|           | 10: Output w                            |                           |              |               |               |                |               |              |

|           | 11: Output w                            |                           |              |               |               |                |               |              |

|           | See Section                             |                           |              | on page 18    | 2 for more    | details abou   | ut routing th | is output to |

|           | a port pin.                             |                           |              | 1 0           |               |                | Ū             | •            |

| Bit 3:    | RESERVED                                | . Read = 0b               | . Must Writ  | e 0b.         |               |                |               |              |

| Bits 2–0: | CLKSL2-0:                               | System Clo                | ck Source S  | Select Bits.  |               |                |               |              |

|           | 000: SYSCL<br>IFCN bits                 | K derived fi<br>in OSCICN | •            | n-frequency   | Internal Os   | scillator, and | d scaled as   | per the      |

|           | 001: SYSCL                              | K derived fi              | om the Exte  | ernal Oscilla | ator circuit. |                |               |              |

|           | 010: SYSCL<br>OSCLD b                   | K derived fi              |              | -frequency    | nternal Os    | cillator, and  | scaled as p   | per the      |

|           |                                         |                           |              |               |               |                |               |              |

|           | 011: RESER                              | VED.                      |              |               |               |                |               |              |

|           | 011: RESER<br>100: SYSCL<br>101-11x: RE | K derived f               | om the PLL   |               |               |                |               |              |

### SFR Definition 16.4. CLKSEL: System Clock Selection

#### 16.8.3. Powering on and Initializing the PLL

To set up and use the PLL as the system clock after power-up of the device, the following procedure should be implemented:

- Step 1. Ensure that the reference clock to be used (internal or external) is running and stable.

- Step 2. Set the PLLSRC bit (PLL0CN.2) to select the desired clock source for the PLL.

- Step 3. Program the Flash read timing bits, FLRT (FLSCL.5–4) to the appropriate value for the new clock rate (see Section "13. Flash Memory" on page 135).

- Step 4. Enable power to the PLL by setting PLLPWR (PLL0CN.0) to '1'.

- Step 5. Program the PLL0DIV register to produce the divided reference frequency to the PLL.

- Step 6. Program the PLLLP3–0 bits (PLL0FLT.3–0) to the appropriate range for the divided reference frequency.

- Step 7. Program the PLLICO1–0 bits (PLL0FLT.5–4) to the appropriate range for the PLL output frequency.

- Step 8. Program the PLLOMUL register to the desired clock multiplication factor.

- Step 9. Wait at least 5 µs, to provide a fast frequency lock.

- Step 10. Enable the PLL by setting PLLEN (PLL0CN.1) to '1'.

- Step 11. Poll PLLLCK (PLL0CN.4) until it changes from '0' to '1'.

- Step 12. Switch the System Clock source to the PLL using the CLKSEL register.

If the PLL characteristics need to be changed when the PLL is already running, the following procedure should be implemented:

- Step 1. The system clock should first be switched to either the internal oscillator or an external clock source that is running and stable, using the CLKSEL register.

- Step 2. Ensure that the reference clock to be used for the new PLL setting (internal or external) is running and stable.

- Step 3. Set the PLLSRC bit (PLL0CN.2) to select the new clock source for the PLL.

- Step 4. If moving to a faster frequency, program the Flash read timing bits, FLRT (FLSCL.5–4) to the appropriate value for the new clock rate (see Section "13. Flash Memory" on page 135).

- Step 5. Disable the PLL by setting PLLEN (PLL0CN.1) to '0'.

- Step 6. Program the PLL0DIV register to produce the divided reference frequency to the PLL.

- Step 7. Program the PLLLP3–0 bits (PLL0FLT.3–0) to the appropriate range for the divided reference frequency.

- Step 8. Program the PLLICO1-0 bits (PLL0FLT.5–4) to the appropriate range for the PLL output frequency.

- Step 9. Program the PLLOMUL register to the desired clock multiplication factor.

- Step 10. Enable the PLL by setting PLLEN (PLL0CN.1) to '1'.

- Step 11. Poll PLLLCK (PLL0CN.4) until it changes from '0' to '1'.

- Step 12. Switch the System Clock source to the PLL using the CLKSEL register.

- Step 13. If moving to a slower frequency, program the Flash read timing bits, FLRT (FLSCL.5–4) to the appropriate value for the new clock rate (see Section "13. Flash Memory" on page 135). Important Note: Cache reads, cache writes, and the prefetch engine should be disabled whenever the FLRT bits are changed to a lower setting.

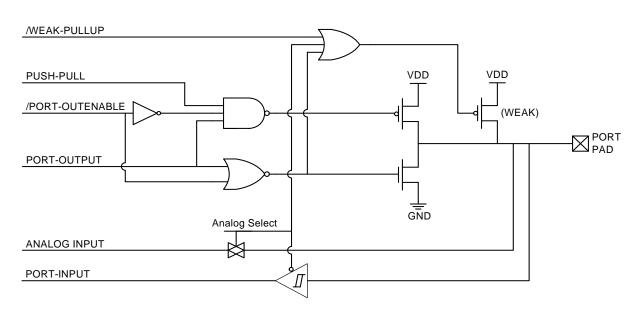

Figure 17.2. Port I/O Cell Block Diagram

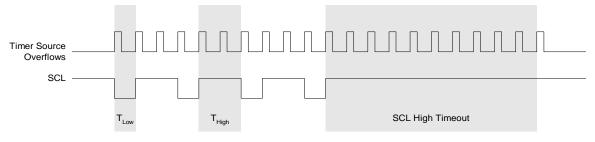

Figure 18.4 shows the typical SCL generation described by Equation 18.2. Notice that  $T_{HIGH}$  is typically twice as large as  $T_{LOW}$ . The actual SCL output may vary due to other devices on the bus (SCL may be extended low by slower slave devices, or driven low by contending master devices). The bit rate when operating as a master will never exceed the limits defined by equation Equation 18.1.

Figure 18.4. Typical SMBus SCL Generation

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 18.2 shows the minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| EXTHOLD   | Minimum SDA Setup Time                  | Minimum SDA Hold Time                                                                                                 |

|-----------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

|           | T <sub>low</sub> – 4 system clocks      |                                                                                                                       |

| 0         | or                                      | 3 system clocks                                                                                                       |

|           | 1 system clock + s/w delay*             |                                                                                                                       |

| 1         | 11 system clocks                        | 12 system clocks                                                                                                      |

| delay occ | if SI is cleared in the same write that | MSB of all data transfers. The s/w<br>ACK is written and when SI is cleared.<br>t defines the outgoing ACK value, s/w |

Table 18.2. Minimum SDA Setup and Hold Times

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "18.3.3. SCL Low Timeout" on page 202). The SMBus interface will force Timer 3 to reload while SCL is high, and allow Timer 3 to count when SCL is low. The Timer 3 interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 18.4). When a Free Timeout is detected, the interface will respond as if a STOP was detected (an interrupt will be generated, and STO will be set).

### 19.1. Enhanced Baud Rate Generation

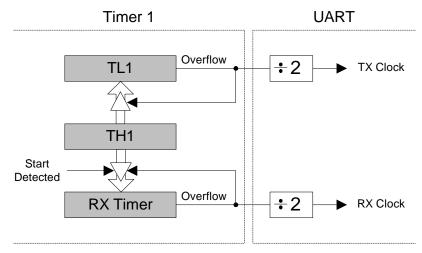

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 19.2), which is not useraccessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

Figure 19.2. UART0 Baud Rate Logic

Timer 1 should be configured for Mode 2, 8-bit auto-reload (see Section "21.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload" on page 247). The Timer 1 reload value should be set so that overflows will occur at two times the desired UART baud rate frequency. Note that Timer 1 may be clocked by one of six sources: SYSCLK, SYSCLK / 4, SYSCLK / 12, SYSCLK / 48, the external oscillator clock / 8, or an external input T1. For any given Timer 1 clock source, the UART0 baud rate is determined by Equation 19.1-A and Equation 19.1-B.

A) UartBaudRate =

$$\frac{1}{2} \times T1_Overflow_Rate$$

B) T1\_Overflow\_Rate =  $\frac{T1_{CLK}}{256 - TH1}$

### Equation 19.1. UART0 Baud Rate

Where  $T1_{CLK}$  is the frequency of the clock supplied to Timer 1, and T1H is the high byte of Timer 1 (reload value). Timer 1 clock frequency is selected as described in Section "21. Timers" on page 245. A quick reference for typical baud rates and system clock frequencies is given in Table 19.1 through Table 19.6. Note that the internal oscillator may still generate the system clock when the external oscillator is driving Timer 1.

#### 21.1. Timer 0 and Timer 1

Each timer is implemented as a 16-bit register accessed as two separate bytes: a low byte (TL0 or TL1) and a high byte (TH0 or TH1). The Counter/Timer Control register (TCON) is used to enable Timer 0 and Timer 1 as well as indicate status. Timer 0 interrupts can be enabled by setting the ET0 bit in the IE register (Section "10.4. Interrupt Register Descriptions" on page 109); Timer 1 interrupts can be enabled by setting the ET1 bit in the IE register (Section 10.4). Both counter/timers operate in one of four primary modes selected by setting the Mode Select bits T1M1–T0M0 in the Counter/Timer Mode register (TMOD). Each timer can be configured independently. Each operating mode is described below.

#### 21.1.1. Mode 0: 13-bit Counter/Timer

Timer 0 and Timer 1 operate as 13-bit counter/timers in Mode 0. The following describes the configuration and operation of Timer 0. However, both timers operate identically, and Timer 1 is configured in the same manner as described for Timer 0.

The TH0 register holds the eight MSBs of the 13-bit counter/timer. TL0 holds the five LSBs in bit positions TL0.4–TL0.0. The three upper bits of TL0 (TL0.7–TL0.5) are indeterminate and should be masked out or ignored when reading. As the 13-bit timer register increments and overflows from 0x1FFF (all ones) to 0x0000, the timer overflow flag TF0 (TCON.5) is set and an interrupt will occur if Timer 0 interrupts are enabled.

The C/T0 bit (TMOD.2) selects the counter/timer's clock source. When C/T0 is set to logic '1', high-to-low transitions at the selected Timer 0 input pin (T0) increment the timer register (Refer to Section "17.1. Priority Crossbar Decoder" on page 184 for information on selecting and configuring external I/O pins). Clearing C/T selects the clock defined by the T0M bit (CKCON.3). When T0M is set, Timer 0 is clocked by the system clock. When T0M is cleared, Timer 0 is clocked by the source selected by the Clock Scale bits in CKCON (see SFR Definition 21.3).

Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic '0' or the input signal /INT0 is active as defined by bit IN0PL in register IT01CF (see SFR Definition 10.7). Setting GATE0 to '1' allows the timer to be controlled by the external input signal /INT0 (see Section "10.4. Interrupt Register Descriptions" on page 109), facilitating pulse width measurements

| TR0             | GATE0 | /INT0 | Counter/Timer |

|-----------------|-------|-------|---------------|

| 0               | Х     | Х     | Disabled      |

| 1               | 0     | Х     | Enabled       |

| 1               | 1     | 0     | Disabled      |

| 1               | 1     | 1     | Enabled       |

| Note: X = Don't | Care  |       |               |

Setting TR0 does not force the timer to reset. The timer registers should be loaded with the desired initial value before the timer is enabled.

TL1 and TH1 form the 13-bit register for Timer 1 in the same manner as described above for TL0 and TH0. Timer 1 is configured and controlled using the relevant TCON and TMOD bits just as with Timer 0. The input signal /INT1 is used with Timer 1; the /INT1 polarity is defined by bit IN1PL in register IT01CF (see SFR Definition 10.7).

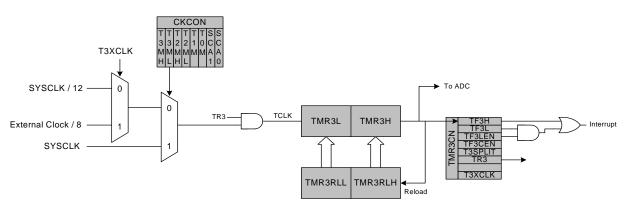

### 21.3. Timer 3

Timer 3 is a 16-bit timer formed by two 8-bit SFRs: TMR3L (low byte) and TMR3H (high byte). Timer 3 may operate in 16-bit auto-reload mode or (split) 8-bit auto-reload mode. The T3SPLIT bit (TMR3CN.3) defines the Timer 3 operation mode.

Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator source divided by 8. The external clock mode is ideal for real-time clock (RTC) functionality, where the internal oscillator drives the system clock while Timer 3 (and/or the PCA) is clocked by an external precision oscillator. Note that the external oscillator source divided by 8 is synchronized with the system clock.

#### 21.3.1. 16-bit Timer with Auto-Reload

When T3SPLIT (TMR3CN.3) is zero, Timer 3 operates as a 16-bit timer with auto-reload. Timer 3 can be clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 3 reload registers (TMR3RLH and TMR3RLL) is loaded into the Timer 3 register as shown in Figure 21.6, and the Timer 3 High Byte Overflow Flag (TMR3CN.7) is set. If Timer 3 interrupts are enabled (if EIE1.7 is set), an interrupt will be generated on each Timer 3 overflow. Additionally, if Timer 3 interrupts are enabled and the TF3LEN bit is set (TMR3CN.5), an interrupt will be generated each time the lower 8 bits (TMR3L) overflow from 0xFF to 0x00.

Figure 21.6. Timer 3 16-Bit Mode Block Diagram

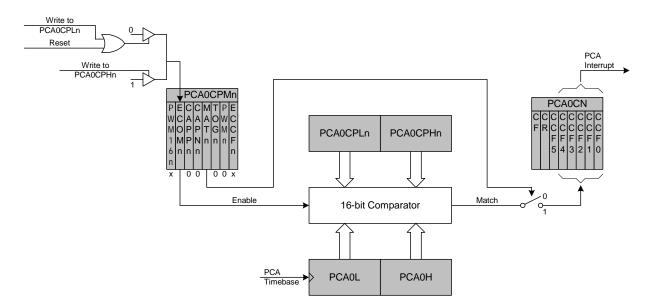

#### 22.2.2. Software Timer (Compare) Mode

In Software Timer mode, the PCA0 counter/timer is compared to the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic '1' and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the ECOMn and MATn bits in the PCA0CPMn register enables Software Timer mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

Figure 22.5. PCA Software Timer Mode Diagram

| System Clock (Hz)                                                                                               | PCA0CPL5 | Timeout Interval (ms)     |

|-----------------------------------------------------------------------------------------------------------------|----------|---------------------------|

| 24,500,000                                                                                                      | 255      | 32.1                      |

| 24,500,000                                                                                                      | 128      | 16.2                      |

| 24,500,000                                                                                                      | 32       | 4.1                       |

| 18,432,000                                                                                                      | 255      | 42.7                      |

| 18,432,000                                                                                                      | 128      | 21.5                      |

| 18,432,000                                                                                                      | 32       | 5.5                       |

| 11,059,200                                                                                                      | 255      | 71.1                      |

| 11,059,200                                                                                                      | 128      | 35.8                      |

| 11,059,200                                                                                                      | 32       | 9.2                       |

| 3,062,500 <sup>2</sup>                                                                                          | 255      | 257                       |

| 3,062,500 <sup>2</sup>                                                                                          | 128      | 129.5                     |

| 3,062,500 <sup>2</sup>                                                                                          | 32       | 33.1                      |

| 191,406                                                                                                         | 255      | 4109                      |

| 191,406                                                                                                         | 128      | 2070                      |

| 191,406                                                                                                         | 32       | 530                       |

| 32,000                                                                                                          | 255      | 24576                     |

| 32,000                                                                                                          | 128      | 12384                     |

| 32,000                                                                                                          | 32       | 3168                      |

| <ul> <li>Assumes SYSCLK/<sup>2</sup></li> <li>of 0x00 at the updat</li> <li>Internal oscillator rest</li> </ul> | e time.  | source, and a PCA0L value |

## Table 22.3. Watchdog Timer Timeout Intervals<sup>1</sup>

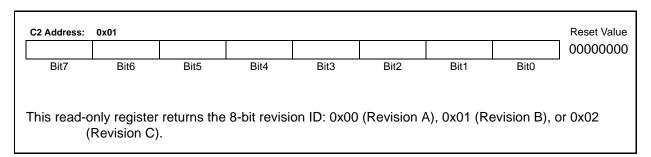

### C2 Register Definition 24.3. REVID: C2 Revision ID

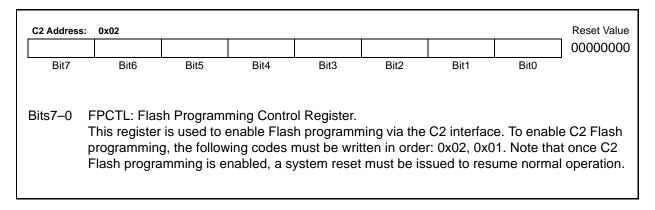

### C2 Register Definition 24.4. FPCTL: C2 Flash Programming Control

### C2 Register Definition 24.5. FPDAT: C2 Flash Programming Data

| C2 Address         | : 0xB4                              |                                                     |                                                  | 1                     |      |             |             | Reset Valu |

|--------------------|-------------------------------------|-----------------------------------------------------|--------------------------------------------------|-----------------------|------|-------------|-------------|------------|

| Bit7               | Bit6                                | Bit5                                                | Bit4                                             | Bit3                  | Bit2 | Bit1        | Bit0        | 0000000    |

|                    |                                     |                                                     |                                                  |                       |      |             |             |            |

| Dits <i>i</i> –0.  | This reg                            | C2 Flash Progrister is used to<br>s. Valid comma    | pass Flash                                       | commands              |      | s, and data | during C2 F | lash       |

| DIIS <i>I</i> – U. | This reg                            | ister is used to                                    | pass Flash<br>ands are list                      | commands              |      | s, and data | during C2 F | Flash      |

| 5ii5 <i>1</i> – U. | This reg<br>accesse                 | ister is used to                                    | pass Flash<br>ands are list<br><b>Con</b>        | commands<br>ed below. |      | s, and data | during C2 F | lash       |

| οπο <i>τ</i> =0.   | This reg<br>accesse                 | ister is used to<br>s. Valid comma                  | pass Flash<br>ands are list<br><b>Con</b><br>ead | commands<br>ed below. |      | s, and data | during C2 F | Flash      |

| UIUS <i>I</i> −U.  | This reg<br>accesse<br>Code<br>0x06 | ister is used to<br>s. Valid comma<br>Flash Block R | pass Flash<br>ands are list<br>Con<br>ead        | commands<br>ed below. |      | s, and data | during C2 F | Flash      |

## DOCUMENT CHANGE LIST

#### **Revision 0.1 to Revision 0.2**

- Updated specification tables with most recently available characterization data.

- Fixed an error with the SYSCLK specification in Table 3.1, "Global Electrical Characteristics," on page 33.

- Corrected the name of the PMAT bit in SFR Definition 10.2. IP: Interrupt Priority.

- Corrected the reset value for SFR Definition 22.2. PCA0MD: PCA0 Mode.

### **Revision 0.2 to Revision 1.0**

- Updated specification tables with characterization data.

- Fixed Table 1.1, "Product Selection Guide," on page 19 to reflect the correct number of Port I/O pins for the C8051F361/2/4/5.

- Updated Section "10. Interrupt Handler" on page 107.

- Added note describing EA change behavior when followed by single cycle instruction.

- Updated SFR Definition 11.1

- Changed the MAC0SC (MAC0CF.5) bit description to correctly refer to the MAC0SD bit.

- Updated SFR Definition 15.2.

- Changed the EMI0CF description to properly describe the 1k XRAM boundaries.

- Added Table 16.2, "Internal Low Frequency Oscillator Electrical Characteristics," on page 171.

- Updated SFR Definition 16.9:

- Specified that the undefined states for PLLLP3–0 are RESERVED.

- Added Table 19.7 and Table 19.8 on page 231 for UART Baud Rates when using the PLL.

- Updated Table 22.1, "PCA Timebase Input Options," on page 263:

Specified that the undefined states of CPS2–0 are RESERVED.

- Added Revision B to "Revision Specific Behavior" on page 279.

### Revision 1.0 to Revision 1.1

- Updated ordering table with Revision C part numbers.

- Updated Figure 17.2. 'Port I/O Cell Block Diagram' on page 183 to refer to VDD instead of VIO.

- Added Revision C to "Revision Specific Behavior" on page 279.

- Added Revision C to the REVID C2 register in C2 Register Definition 24.3.

- Updated "Digital Supply Current (Stop Mode, shutdown)" typical value in Table 3.1, "Global Electrical Characteristics," on page 33.

- Updated "Missing Clock Detector Timeout" typical value in Table 12.1, "Reset Electrical Characteristics," on page 134.