#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                              |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 50MHz                                                            |

| Connectivity               | SMBus (2-Wire/I²C), SPI, UART/USART                              |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                       |

| Number of I/O              | 29                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 1K x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                      |

| Data Converters            | A/D 21x10b; D/A 1x10b                                            |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 32-LQFP                                                          |

| Supplier Device Package    | 32-LQFP (7x7)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f366-c-gq |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 13.3.2.16.4.2 PSWE Maintenance                             | 141 |

|------------------------------------------------------------|-----|

| 13.3.3.System Clock                                        | 141 |

| 13.4.Flash Read Timing                                     | 143 |

| 14. Branch Target Cache                                    | 145 |

| 14.1.Cache and Prefetch Operation                          | 145 |

| 14.2.Cache and Prefetch Optimization                       |     |

| 15. External Data Memory Interface and On-Chip XRAM        | 152 |

| 15.1.Accessing XRAM                                        |     |

| 15.1.1.16-Bit MOVX Example                                 | 152 |

| 15.1.2.8-Bit MOVX Example                                  | 152 |

| 15.2.Configuring the External Memory Interface             |     |

| 15.3.Port Configuration                                    | 153 |

| 15.4.Multiplexed and Non-multiplexed Selection             | 156 |

| 15.4.1.Multiplexed Configuration                           | 156 |

| 15.4.2.Non-multiplexed Configuration                       | 157 |

| 15.5.Memory Mode Selection                                 | 158 |

| 15.5.1.Internal XRAM Only                                  | 158 |

| 15.5.2.Split Mode without Bank Select                      |     |

| 15.5.3.Split Mode with Bank Select                         | 158 |

| 15.5.4.External Only                                       | 159 |

| 15.6.Timing                                                | 159 |

| 15.6.1.Non-multiplexed Mode                                | 161 |

| 15.6.2.Multiplexed Mode                                    | 164 |

| 16. Oscillators                                            |     |

| 16.1.Programmable Internal High-Frequency (H-F) Oscillator | 168 |

| 16.1.1. Internal Oscillator Suspend Mode                   |     |

| 16.2. Programmable Internal Low-Frequency (L-F) Oscillator | 170 |

| 16.2.1.Calibrating the Internal L-F Oscillator             |     |

| 16.3.External Oscillator Drive Circuit                     | 172 |

| 16.4.System Clock Selection                                | 172 |

| 16.5.External Crystal Example                              | 175 |

| 16.6.External RC Example                                   | 176 |

| 16.7.External Capacitor Example                            |     |

| 16.8.Phase-Locked Loop (PLL)                               | 177 |

| 16.8.1.PLL Input Clock and Pre-divider                     |     |

| 16.8.2.PLL Multiplication and Output Clock                 |     |

| 16.8.3.Powering on and Initializing the PLL                |     |

| 17. Port Input/Output                                      |     |

| 17.1.Priority Crossbar Decoder                             |     |

| 17.2.Port I/O Initialization                               |     |

| 17.3.General Purpose Port I/O                              |     |

| 18. SMBus                                                  | 200 |

|                                                            |     |

| 18.1.Supporting Documents                                  | 200 |

## List of Figures

| 1. | System Overview                                                           |                |

|----|---------------------------------------------------------------------------|----------------|

|    | Figure 1.1. C8051F360/3 Block Diagram                                     | 20             |

|    | Figure 1.2. C8051F361/4/6/8 Block Diagram                                 | 21             |

|    | Figure 1.3. C8051F362/5/7/9 Block Diagram                                 | 21             |

|    | Figure 1.4. Comparison of Peak MCU Execution Speeds                       | 22             |

|    | Figure 1.5. On-Chip Clock and Reset                                       | 23             |

|    | Figure 1.6. On-Board Memory Map                                           | 24             |

|    | Figure 1.7. Development/In-System Debug Diagram                           | 25             |

|    | Figure 1.8. Digital Crossbar Diagram (Port 0 to Port 3)                   | 26             |

|    | Figure 1.9. PCA Block Diagram                                             | 27             |

|    | Figure 1.10. PCA Block Diagram                                            | 27             |

|    | Figure 1.11. 10-Bit ADC Block Diagram                                     | 28             |

|    | Figure 1.12. Comparator0 Block Diagram                                    | 29             |

|    | Figure 1.13. Comparator1 Block Diagram                                    | 30             |

|    | Figure 1.14. IDA0 Functional Block Diagram                                | 31             |

|    | Absolute Maximum Ratings                                                  |                |

| 3. | Global Electrical Characteristics                                         |                |

| 4. | Pinout and Package Definitions                                            |                |

|    | Figure 4.1. TQFP-48 Pinout Diagram (Top View)                             |                |

|    | Figure 4.2. TQFP-48 Package Diagram                                       |                |

|    | Figure 4.3. LQFP-32 Pinout Diagram (Top View)                             |                |

|    | Figure 4.4. LQFP-32 Package Diagram                                       |                |

|    | Figure 4.5. QFN-28 Pinout Diagram (Top View)                              |                |

|    | Figure 4.6. QFN-28 Package Drawing                                        |                |

|    | Figure 4.7. Typical QFN-28 Landing Diagram                                |                |

|    | Figure 4.8. QFN-28 Solder Paste Recommendation                            | 46             |

| 5. | 10-Bit ADC (ADC0, C8051F360/1/2/6/7/8/9)                                  |                |

|    | Figure 5.1. ADC0 Functional Block Diagram                                 |                |

|    | Figure 5.2. Typical Temperature Sensor Transfer Function                  |                |

|    | Figure 5.3. Temperature Sensor Error with 1-Point Calibration             |                |

|    | Figure 5.4. 10-Bit ADC Track and Conversion Example Timing                |                |

|    | Figure 5.5. ADC0 Equivalent Input Circuits                                |                |

|    | Figure 5.6. ADC Window Compare Example: Right-Justified Single-Ended Data |                |

|    | Figure 5.7. ADC Window Compare Example: Left-Justified Single-Ended Data  |                |

|    | Figure 5.8. ADC Window Compare Example: Right-Justified Differential Data |                |

| •  | Figure 5.9. ADC Window Compare Example: Left-Justified Differential Data  | 61             |

| 6. | 10-Bit Current Mode DAC (IDA0, C8051F360/1/2/6/7/8/9)                     | ~~             |

|    | Figure 6.1. IDA0 Functional Block Diagram                                 |                |

| -  | Figure 6.2. IDA0 Data Word Mapping                                        | 64             |

| 1. | Voltage Reference (C8051F360/1/2/6/7/8/9)                                 | ~ <del>7</del> |

| 0  | Figure 7.1. Voltage Reference Functional Block Diagram                    | 67             |

| ŏ. | Comparators                                                               | 70             |

|    | Figure 8.1. Comparator0 Functional Block Diagram                          | 70             |

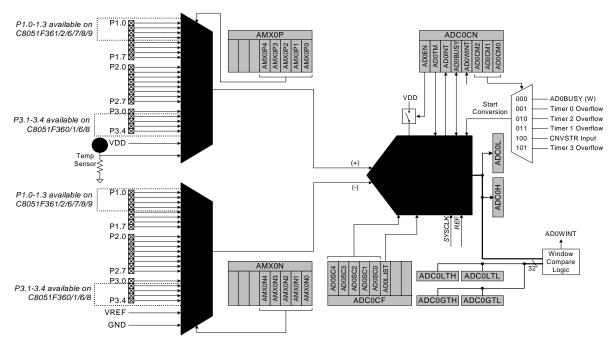

### 5. 10-Bit ADC (ADC0, C8051F360/1/2/6/7/8/9)

The ADC0 subsystem for the C8051F360/1/2/6/7/8/9 consists of two analog multiplexers (referred to collectively as AMUX0) with 23 total input selections, and a 200 ksps, 10-bit successive-approximation-register ADC with integrated track-and-hold and programmable window detector. The AMUX0, data conversion modes, and window detector are all configurable under software control via the Special Function Registers shown in Figure 5.1. ADC0 operates in both Single-ended and Differential modes, and may be configured to measure P1.0-P3.4 (where available), the Temperature Sensor output, or V<sub>DD</sub> with respect to P1.0-P3.4, VREF, or GND. The ADC0 subsystem is enabled only when the AD0EN bit in the ADC0 Control register (ADC0CN) is set to logic '1'. The ADC0 subsystem is in low power shutdown when this bit is logic '0'.

Figure 5.1. ADC0 Functional Block Diagram

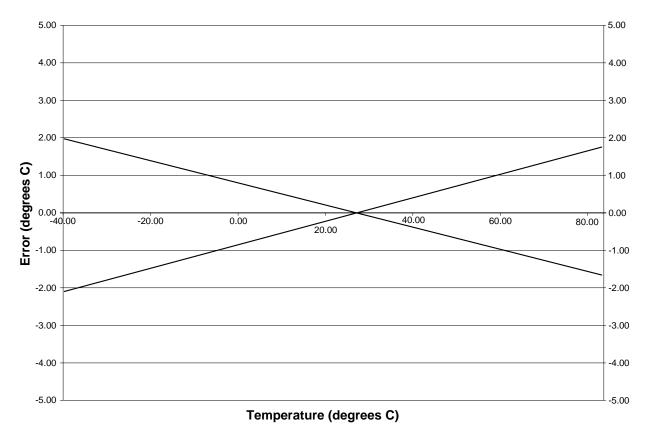

Figure 5.3. Temperature Sensor Error with 1-Point Calibration

#### SFR Definition 5.6. ADC0CN: ADC0 Control

| R/W       | R/W                         | R/W           | R/W             | R/W            | R/W            | R/W           | R/W               | Reset Valu  |

|-----------|-----------------------------|---------------|-----------------|----------------|----------------|---------------|-------------------|-------------|

| AD0EN     | AD0TM                       | AD0INT        | AD0BUSY         | <b>ADOWINT</b> | AD0CM2         | AD0CM1        | AD0CM0            | 0000000     |

| Bit7      | Bit6                        | Bit5          | Bit4            | Bit3           | Bit2           | Bit1          | Bit0              |             |

| Bit 7:    | AD0EN: AD0                  | C0 Enable     | Bit.            |                |                |               |                   |             |

|           | 0: ADC0 Disa                | abled. ADC    | C0 is in low-p  | ower shutde    | own.           |               |                   |             |

|           | 1: ADC0 Ena                 |               |                 |                |                | ersions.      |                   |             |

| Bit 6:    | AD0TM: AD0                  | C0 Track N    | lode Bit.       |                |                |               |                   |             |

|           | 0: Normal Tra               | ack Mode:     | When ADC0       | is enabled,    | tracking is    | continuous    | unless a coi      | nversion is |

|           | in progress.                |               |                 |                |                |               |                   |             |

|           | 1: Low-powe                 |               |                 |                |                | ) bits (see b | elow).            |             |

| Bit 5:    | AD0INT: AD0                 |               | •               | •              | -              |               |                   |             |

|           | 0: ADC0 has                 |               |                 |                | since the las  | st time AD0I  | NT was clea       | ared.       |

|           | 1: ADC0 has                 | •             |                 | ersion.        |                |               |                   |             |

| Bit 4:    | ADOBUSY: A                  | ADC0 Busy     | Bit.            |                |                |               |                   |             |

|           | Read:                       |               |                 |                |                |               |                   |             |

|           | 0: ADC0 con                 |               |                 |                | i is not curre | enuy in prog  | ress. ADOIN       | vi is set t |

|           | 1: ADC0 con                 | -             | edge of ADC     | DU31.          |                |               |                   |             |

|           | Write:                      |               | in progress.    |                |                |               |                   |             |

|           | 0: No Effect.               |               |                 |                |                |               |                   |             |

|           | 1: Initiates A              | DC0 Conve     | ersion if AD0   | CM2-0 = 00     | 00b            |               |                   |             |

| Bit 3:    | ADOWINT: A                  |               |                 |                |                |               |                   |             |

|           | 0: ADC0 Wir                 |               |                 |                |                | d since this  | flag was las      | t cleared.  |

|           | 1: ADC0 Wir                 |               |                 |                |                |               | U                 |             |

| Bits 2–0: | AD0CM2-0:                   | ADC0 Star     | rt of Convers   | ion Mode S     | elect.         |               |                   |             |

|           | When AD0TI                  | M = 0:        |                 |                |                |               |                   |             |

|           | 000: ADC0 c                 | onversion     | initiated on e  | very write c   | f '1' to AD0   | BUSY.         |                   |             |

|           | 001: ADC0 c                 |               |                 |                |                |               |                   |             |

|           | 010: ADC0 c                 |               |                 |                |                |               |                   |             |

|           | 011: ADC0 c                 |               |                 |                |                |               |                   |             |

|           | 100: ADC0 c                 |               |                 |                |                | NVSTR.        |                   |             |

|           | 101: ADC0 c                 |               | initiated on o  | vertiow of I   | imer 3.        |               |                   |             |

|           | 11x: Reserve                | -             |                 |                |                |               |                   |             |

|           | When AD0TI<br>000: Tracking |               | on write of '1' |                | SV and lasts   |               | eks followo       | hy con-     |

|           | versio                      | -             |                 |                |                |               |                   |             |

|           | 001: Tracking               |               | on overflow o   | f Timer 0 ar   | nd lasts 3 S   | AR clocks f   | ollowed by a      | conversio   |

|           | 010: Tracking               | •             |                 |                |                |               | •                 |             |

|           | 011: Tracking               | •             |                 |                |                |               |                   |             |

|           | 100: ADC0 ti<br>edge.       |               |                 |                |                |               |                   |             |

|           | 101: Tracking               |               |                 | (T) 0          |                |               | مالمينية والمبيرة |             |

|           |                             | n initiated ( | n overtiow o    | t limer i ar   | nd lasts X S   | AR CIOCKS T   | ollowen nv r      | CONVERSION  |

#### 5.4. Programmable Window Detector

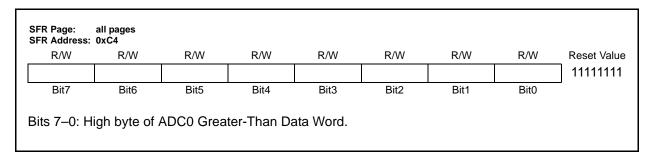

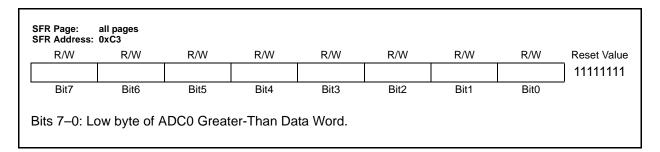

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

#### SFR Definition 5.7. ADC0GTH: ADC0 Greater-Than Data High Byte

#### SFR Definition 5.8. ADC0GTL: ADC0 Greater-Than Data Low Byte

### SFR Definition 8.5. CPT1MX: Comparator1 MUX Selection

|           | R/W                   | R/W                      | R/W                                                         | R/W                       | R/W        | R/W           | R/W      | Reset Value |

|-----------|-----------------------|--------------------------|-------------------------------------------------------------|---------------------------|------------|---------------|----------|-------------|

| -         | -                     | CMX1N <sup>2</sup>       | CMX1N0                                                      | -                         | -          | CMX1P1        | CMX1P0   | 11111111    |

| Bit7      | Bit6                  | Bit5                     | Bit4                                                        | Bit3                      | Bit2       | Bit1          | Bit0     |             |

| Bits 7–6: | UNUSED.               | Read = 11b               | , Write = don                                               | 't care.                  |            |               |          |             |

| Bits 5–4: | CMX1N1-               | CMX1N0: C                | comparator1                                                 | Negative I                | nput MUX S | Select.       |          |             |

|           | These bits            | select whic              | h Port pin is ι                                             | used as th                | e Compara  | tor1 negative | e input. |             |

|           | CMX1N1                | CMX1N0                   | C8051F                                                      | 360/3                     | C8051F36   | 61/2/4/5/6/7/ | 8/9      |             |

|           | CIVIATINT             |                          | Negative                                                    | Input                     | Nega       | tive Input    |          |             |

|           | 0                     | 0                        | P2.7                                                        | 1                         |            | P1.3          |          |             |

|           | 0                     | 1                        | P2.6                                                        | 6                         |            | P1.7          |          |             |

|           | 1                     | 0                        | P3.4                                                        | 4                         |            | P2.3          |          |             |

|           | 1                     | 1                        | P4.(                                                        | C                         |            | P2.7          |          |             |

|           | CMX1P1–<br>These bits | CMX1P0: C<br>select whic | ο, Write = don<br>omparator1 F<br>h Port pin is ι<br>C8051F | Positive In<br>used as th | e Compara  |               |          |             |

|           | CMX1P1                | CMX1P0                   | Positive                                                    |                           |            | tive Input    | 0/3      |             |

|           | 0                     | 0                        | POSITIVE<br>P2.0                                            |                           | FUS        | P1.2          |          |             |

|           | 0                     | 1                        | P2.5                                                        | -                         |            | P1.6          |          |             |

|           | 0                     | 0                        | P3.3                                                        | -                         |            | P2.2          |          |             |

|           | 1                     | •                        |                                                             |                           |            | P2.6          |          |             |

|           | 1                     | 1                        | P3.7                                                        | /                         |            |               |          |             |

| Mnemonic             | Description                                                                                                     | Bytes | Clock<br>Cycles |

|----------------------|-----------------------------------------------------------------------------------------------------------------|-------|-----------------|

| JZ rel               | Jump if A equals zero                                                                                           | 2     | 2/3*            |

| JNZ rel              | Jump if A does not equal zero                                                                                   | 2     | 2/3*            |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal                                                                  | 3     | 3/4*            |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal                                                                    | 3     | 3/4*            |

| CJNE Rn, #data, rel  | Compare immediate to Register and jump if not equal                                                             | 3     | 3/4*            |

| CJNE @Ri, #data, rel | Compare immediate to indirect and jump if not equal                                                             | 3     | 4/5*            |

| DJNZ Rn, rel         | Decrement Register and jump if not zero                                                                         | 2     | 2/3*            |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero                                                                      | 3     | 3/4*            |

| NOP                  | No operation                                                                                                    | 1     | 1               |

|                      | incur a cache-miss penalty if the branch target location<br>See Section "14. Branch Target Cache" on page 145 f |       |                 |

#### Table 9.1. CIP-51 Instruction Set Summary (Continued)

#### Notes on Registers, Operands and Addressing Modes:

Rn - Register R0-R7 of the currently selected register bank.

**@Ri** - Data RAM location addressed indirectly through R0 or R1.

**rel** - 8-bit, signed (2s complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00-0x7F) or an SFR (0x80-0xFF).

#data - 8-bit constant

#data16 - 16-bit constant

bit - Direct-accessed bit in Data RAM or SFR

**addr11** - 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2K-byte page of program memory as the first byte of the following instruction.

**addr16** - 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 64K-byte program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

| R/W  | R/W                                        | R/W                                                        | R/W                                                       | R/W                                                                          | R/W                                                                  | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W                                                   | Reset Valu                               |

|------|--------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------|

| Bit7 | Bit6                                       | Bit5                                                       | Bit4                                                      | Bit3                                                                         | Bit2                                                                 | Bit1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit0                                                  | 0000000                                  |

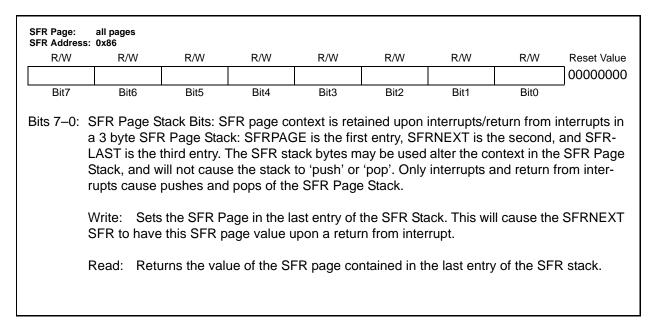

|      | a 3 byte SFI<br>LAST is the                | •                                                          |                                                           | GE is the fire                                                               | st entry, SF                                                         | RNEXT is t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       | , and SFR-                               |

|      | LAST is the<br>Stack, and v<br>rupts cause | third entry.<br>vill not caus<br>pushes and                | The SFR st<br>e the stack<br>I pops of th                 | GE is the firs<br>ack bytes m<br>to 'push' or<br>e SFR Page                  | st entry, SF<br>ay be used<br>'pop'. Only<br>e Stack.                | RNEXT is the contract of the c | he second<br>ontext in th<br>and return               | , and SFR-<br>le SFR Page<br>from inter- |

|      | LAST is the Stack, and v                   | third entry.<br>vill not caus<br>pushes and<br>s the SFR P | The SFR st<br>e the stack<br>d pops of th<br>rage contair | GE is the firs<br>ack bytes m<br>to 'push' or<br>e SFR Page<br>ned in the se | st entry, SF<br>hay be used<br>'pop'. Only<br>e Stack.<br>econd byte | RNEXT is the alter the contract interrupts a of the SFR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | he second<br>ontext in th<br>and return<br>Stack. Thi | , and SFR-<br>le SFR Page<br>from inter- |

#### SFR Definition 9.3. SFRNEXT: SFR Next Register

### SFR Definition 9.4. SFRLAST: SFR Last Register

| SFR Page:<br>SFR Addres | all pages<br>ss: 0xA8 | `             | ressable)     |               |                             |               |             |             |

|-------------------------|-----------------------|---------------|---------------|---------------|-----------------------------|---------------|-------------|-------------|

| R/W                     | R/W                   | R/W           | R/W           | R/W           | R/W                         | R/W           | R/W         | Reset Valu  |

| EA                      | ESPI0                 | ET2           | ES0           | ET1           | EX1                         | ET0           | EX0         | 0000000     |

| Bit7                    | Bit6                  | Bit5          | Bit4          | Bit3          | Bit2                        | Bit1          | Bit0        |             |

| Bit 7:                  | EA: Global I          | nterrupt En   | able.         |               |                             |               |             |             |

|                         | This bit glob         | ally enable   | s/disables a  | II interrupts | . It overrides              | s the individ | ual interru | pt mask set |

|                         | tings.                |               |               |               |                             |               |             |             |

|                         | 0: Disable a          |               |               |               |                             |               |             |             |

|                         | 1: Enable ea          | ach interrup  | t according   | to its indivi | dual mask s                 | etting.       |             |             |

| Bit 6:                  | ESPI0: Enat           | ole Serial P  | eripheral In  | terface (SP   | <ol><li>Interrupt</li></ol> |               |             |             |

|                         | This bit sets         |               |               | 10 interrupt  | S.                          |               |             |             |

|                         | 0: Disable a          | II SPI0 inte  | rrupts.       |               |                             |               |             |             |

|                         | 1: Enable in          | terrupt requ  | uests genera  | ated by SPI   | 0.                          |               |             |             |

| Bit 5:                  | ET2: Enable           | e Timer 2 In  | terrupt.      |               |                             |               |             |             |

|                         | This bit sets         | the maskir    | ng of the Tin | ner 2 interru | ıpt.                        |               |             |             |

|                         | 0: Disable T          | imer 2 intei  | rupt.         |               |                             |               |             |             |

|                         | 1: Enable in          | terrupt requ  | lests genera  | ated by the   | TF2L or TF2                 | 2H flags.     |             |             |

| Bit 4:                  | ES0: Enable           | e UART0 In    | terrupt.      |               |                             |               |             |             |

|                         | This bit sets         | the maskir    | ng of the UA  | RT0 interru   | ipt.                        |               |             |             |

|                         | 0: Disable U          | ART0 inter    | rupt.         |               |                             |               |             |             |

|                         | 1: Enable U           | ART0 interi   | rupt.         |               |                             |               |             |             |

| Bit 3:                  | ET1: Enable           | e Timer 1 In  | terrupt.      |               |                             |               |             |             |

|                         | This bit sets         | the maskir    | ng of the Tin | ner 1 interru | ipt.                        |               |             |             |

|                         | 0: Disable a          | ll Timer 1 ir | nterrupt.     |               | -                           |               |             |             |

|                         | 1: Enable in          | terrupt requ  | uests genera  | ated by the   | TF1 flag.                   |               |             |             |

| Bit 2:                  | EX1: Enable           | External I    | nterrupt 1.   | -             | -                           |               |             |             |

|                         | This bit sets         | the maskir    | ng of Extern  | al Interrupt  | 1.                          |               |             |             |

|                         | 0: Disable e          | xternal inte  | rrupt 1.      |               |                             |               |             |             |

|                         | 1: Enable in          | terrupt requ  | Jests genera  | ated by the   | /INT1 input.                |               |             |             |

| Bit 1:                  | ET0: Enable           |               |               |               |                             |               |             |             |

|                         | This bit sets         | the maskir    | ng of the Tin | ner 0 interru | ipt.                        |               |             |             |

|                         | 0: Disable a          |               | •             |               | •                           |               |             |             |

|                         | 1: Enable in          |               |               | ated by the   | TF0 flag.                   |               |             |             |

| Bit 0:                  | EX0: Enable           |               |               |               | 0                           |               |             |             |

|                         | This bit sets         |               |               | al Interrupt  | 0.                          |               |             |             |

|                         | 0: Disable e          |               | •             | - 1           |                             |               |             |             |

|                         |                       |               |               |               |                             |               |             |             |

#### SFR Definition 10.1. IE: Interrupt Enable

#### 12.2. Power-Fail Reset/V<sub>DD</sub> Monitor

When a power-down transition or power irregularity causes  $V_{DD}$  to drop below  $V_{RST}$ , the power supply monitor will drive the RST pin low and hold the CIP-51 in a reset state (see Figure 12.2). When  $V_{DD}$  returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state. Note that even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below the level required for data retention. If the PORSF flag reads '1', the data may no longer be valid. The  $V_{DD}$  Monitor is enabled after power-on resets; however its defined state (enabled/disabled) is not altered by any other reset source. For example, if the  $V_{DD}$  Monitor is disabled and a software reset is performed, the  $V_{DD}$  Monitor will still be disabled after the reset. To protect the integrity of Flash contents, the VDD Monitor must be enabled and selected as a reset source if software contains routines which erase or write Flash memory. If the VDD Monitor is not enabled, any erase or write performed on Flash memory will cause a Flash Error device reset.

The V<sub>DD</sub> Monitor must be enabled before it is selected as a reset source. Selecting the V<sub>DD</sub> Monitor as a reset source before it is enabled and stabilized may cause a system reset. The procedure for configuring the V<sub>DD</sub> Monitor as a reset source is shown below:

- Step 1. Enable the  $V_{DD}$  Monitor (VDMEN bit in VDM0CN = '1').

- Step 2. Wait for the VDD Monitor to stabilize (approximately 5 μs). Note: This delay should be omitted if software contains routines which erase or write Flash memory.

- Step 3. Select the  $V_{DD}$  Monitor as a reset source (PORSF bit in RSTSRC = '1').

See Table 12.1 for complete electrical characteristics of the  $V_{\text{DD}}$  Monitor.

Note: Software should take care not to inadvertently disable the VDD Monitor as a reset source when writing to RSTSRC to enable other reset sources or to trigger a software reset. All writes to RSTSRC should explicitly set PORSF to '1' to keep the VDD Monitor enabled as a reset source.

| R/W       | R/W                                                                                                                                          | R/W                                                                                                                                         | R/W                                                                                                                                                                    | R/W                                                                                                                                                                  | R/W                                                                                                                                                  | R/W                                                                                                                                | R/W                                                                                          | Reset Value                                                       |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| _         | -                                                                                                                                            | _                                                                                                                                           | EMD2                                                                                                                                                                   | EMD1                                                                                                                                                                 | EMD0                                                                                                                                                 | EALE1                                                                                                                              | EALE0                                                                                        | 00000011                                                          |

| Bit7      | Bit6                                                                                                                                         | Bit5                                                                                                                                        | Bit4                                                                                                                                                                   | Bit3                                                                                                                                                                 | Bit2                                                                                                                                                 | Bit1                                                                                                                               | Bit0                                                                                         | -                                                                 |

| Bits 7–5: | UNUSED. R                                                                                                                                    | ead = 000k                                                                                                                                  | o. Write = do                                                                                                                                                          | on't care.                                                                                                                                                           |                                                                                                                                                      |                                                                                                                                    |                                                                                              |                                                                   |

| Bit 4:    | EMD2: EMIF                                                                                                                                   | Multiplex                                                                                                                                   | Mode Selec                                                                                                                                                             | :t.                                                                                                                                                                  |                                                                                                                                                      |                                                                                                                                    |                                                                                              |                                                                   |

|           | 0: EMIF oper                                                                                                                                 | ates in mu                                                                                                                                  | Itiplexed ad                                                                                                                                                           | dress/data                                                                                                                                                           | mode.                                                                                                                                                |                                                                                                                                    |                                                                                              |                                                                   |

|           | 1: EMIF oper                                                                                                                                 | ates in no                                                                                                                                  | n-multiplexe                                                                                                                                                           | d mode (se                                                                                                                                                           | parate addi                                                                                                                                          | ress and da                                                                                                                        | ta pins).                                                                                    |                                                                   |

| 3its 3–2: | EMD1-0: EM                                                                                                                                   | IIF Operat                                                                                                                                  | ing Mode Se                                                                                                                                                            | elect.                                                                                                                                                               |                                                                                                                                                      |                                                                                                                                    |                                                                                              |                                                                   |

|           | These bits co                                                                                                                                | ontrol the c                                                                                                                                | perating mo                                                                                                                                                            | ode of the E                                                                                                                                                         | xternal Mer                                                                                                                                          | nory Interfa                                                                                                                       | ce.                                                                                          |                                                                   |

|           | 00: Internal C                                                                                                                               | Only: MOV                                                                                                                                   | X accesses                                                                                                                                                             | on-chip XR                                                                                                                                                           | AM only. Al                                                                                                                                          | I effective a                                                                                                                      | ddresses a                                                                                   | alias to                                                          |

|           | on-chip r                                                                                                                                    | nemory sp                                                                                                                                   | ace.                                                                                                                                                                   |                                                                                                                                                                      |                                                                                                                                                      |                                                                                                                                    |                                                                                              |                                                                   |

|           | 01: Split Mod                                                                                                                                | e without I                                                                                                                                 | Rank Salact                                                                                                                                                            |                                                                                                                                                                      | المطابين مامط                                                                                                                                        | 1 I                                                                                                                                |                                                                                              |                                                                   |

|           |                                                                                                                                              | c without i                                                                                                                                 | Dalik Select                                                                                                                                                           | . Accesses                                                                                                                                                           | below the 1                                                                                                                                          | k boundar                                                                                                                          | y are direct                                                                                 | ed on-chip                                                        |

|           | •                                                                                                                                            |                                                                                                                                             | e 1 k bound                                                                                                                                                            |                                                                                                                                                                      |                                                                                                                                                      |                                                                                                                                    | •                                                                                            | •                                                                 |

|           | Accesse                                                                                                                                      | s above th                                                                                                                                  |                                                                                                                                                                        | ary are dire                                                                                                                                                         | cted off-chi                                                                                                                                         | p. 8-bit off-o                                                                                                                     | hip MOVX                                                                                     | operations                                                        |

|           | Accesse<br>use the c                                                                                                                         | s above th<br>urrent con                                                                                                                    | e 1 k bound                                                                                                                                                            | ary are dire<br>Address Hiç                                                                                                                                          | cted off-chi<br>gh port latch                                                                                                                        | p. 8-bit off-ones to resolv                                                                                                        | hip MOVX<br>ve upper ac                                                                      | operations                                                        |

|           | Accesse<br>use the c<br>Note tha<br>containe                                                                                                 | s above th<br>current con<br>t in order to<br>d in the on                                                                                   | e 1 k bound<br>tents of the<br>b access off<br>-chip addres                                                                                                            | ary are dire<br>Address Hig<br>-chip space<br>ss space.                                                                                                              | cted off-chi<br>gh port latch<br>, EMI0CN r                                                                                                          | p. 8-bit off-ones to resolven<br>nust be set                                                                                       | chip MOVX<br>ve upper ac<br>to a page t                                                      | operations<br>dress byte<br>hat is not                            |

|           | Accesse<br>use the c<br>Note tha                                                                                                             | s above th<br>current con<br>t in order to<br>d in the on                                                                                   | e 1 k bound<br>tents of the<br>b access off<br>-chip addres                                                                                                            | ary are dire<br>Address Hig<br>-chip space<br>ss space.                                                                                                              | cted off-chi<br>gh port latch<br>, EMI0CN r                                                                                                          | p. 8-bit off-ones to resolven<br>nust be set                                                                                       | chip MOVX<br>ve upper ac<br>to a page t                                                      | operations<br>dress byte<br>hat is not                            |

|           | Accesse<br>use the c<br>Note tha<br>containe<br>10: Split Moc<br>Accesse                                                                     | s above th<br>current con<br>t in order to<br>d in the on<br>le with Bar<br>s above th                                                      | e 1 k bound<br>tents of the<br>o access off<br>-chip addres<br>nk Select: Ac<br>e 1 k bound                                                                            | ary are dire<br>Address Hig<br>-chip space<br>ss space.<br>ccesses bel<br>ary are dire                                                                               | cted off-chi<br>gh port latch<br>, EMI0CN r<br>ow the 1 k l<br>cted off-chi                                                                          | p. 8-bit off-o<br>nes to resolv<br>nust be set<br>boundary a<br>p. 8-bit off-o                                                     | chip MOVX<br>ve upper ac<br>to a page t<br>re directed<br>chip MOVX                          | operations<br>dress byte<br>hat is not<br>on-chip.                |

|           | Accesse<br>use the c<br>Note that<br>containe<br>10: Split Moc<br>Accesse<br>use the c                                                       | s above th<br>current con<br>t in order to<br>d in the on<br>e with Bar<br>s above th<br>contents of                                        | e 1 k bound<br>tents of the<br>o access off<br>-chip addres<br>k Select: Ac<br>e 1 k bound<br>EMI0CN to                                                                | ary are dire<br>Address Hig<br>-chip space<br>ss space.<br>ccesses bel<br>ary are dire<br>determine                                                                  | cted off-chi<br>gh port latch<br>, EMI0CN r<br>ow the 1 k l<br>cted off-chi<br>the high-by                                                           | p. 8-bit off-<br>nes to resolv<br>nust be set<br>boundary a<br>p. 8-bit off-<br>te of the ad                                       | chip MOVX<br>ve upper ac<br>to a page t<br>re directed<br>chip MOVX<br>dress.                | operations<br>dress byte<br>hat is not<br>on-chip.<br>operations  |

|           | Accesse<br>use the c<br>Note tha<br>containe<br>10: Split Moc<br>Accesse                                                                     | s above th<br>current con<br>t in order to<br>d in the on<br>e with Bar<br>s above th<br>contents of                                        | e 1 k bound<br>tents of the<br>o access off<br>-chip addres<br>k Select: Ac<br>e 1 k bound<br>EMI0CN to                                                                | ary are dire<br>Address Hig<br>-chip space<br>ss space.<br>ccesses bel<br>ary are dire<br>determine                                                                  | cted off-chi<br>gh port latch<br>, EMI0CN r<br>ow the 1 k l<br>cted off-chi<br>the high-by                                                           | p. 8-bit off-<br>nes to resolv<br>nust be set<br>boundary a<br>p. 8-bit off-<br>te of the ad                                       | chip MOVX<br>ve upper ac<br>to a page t<br>re directed<br>chip MOVX<br>dress.                | operations<br>dress byte<br>hat is not<br>on-chip.<br>operations  |

| Bits 1–0: | Accesse<br>use the c<br>Note that<br>containe<br>10: Split Moc<br>Accesse<br>use the c<br>11: External                                       | s above th<br>current con<br>t in order to<br>d in the on<br>le with Bar<br>s above th<br>contents of<br>Only: MOV                          | e 1 k bound<br>tents of the .<br>o access off<br>-chip addres<br>hk Select: Ad<br>e 1 k bound<br>EMI0CN to<br>/X accesses                                              | ary are dire<br>Address Hig<br>-chip space<br>ss space.<br>ccesses bel<br>ary are dire<br>determine<br>s off-chip XF                                                 | cted off-chi<br>gh port latch<br>, EMIOCN r<br>ow the 1 k l<br>cted off-chi<br>the high-by<br>RAM only. C                                            | p. 8-bit off-<br>nes to resolv<br>nust be set<br>boundary a<br>p. 8-bit off-c<br>te of the ad<br>on-chip XRA                       | chip MOVX<br>ve upper ac<br>to a page t<br>re directed<br>chip MOVX<br>dress.<br>M is not vi | operations<br>dress byte<br>hat is not<br>on-chip.<br>operations  |

| Bits 1–0: | Accesse<br>use the c<br>Note tha<br>containe<br>10: Split Moc<br>Accesse<br>use the c<br>11: External<br>CPU.                                | s above th<br>current con<br>t in order to<br>d in the on<br>le with Bar<br>s above th<br>contents of<br>Only: MOV                          | e 1 k bound<br>tents of the<br>o access off<br>-chip addres<br>k Select: Ac<br>e 1 k bound<br>EMI0CN to<br>/X accesses                                                 | ary are dire<br>Address Hig<br>-chip space<br>ss space.<br>ccesses bel<br>ary are dire<br>determine<br>s off-chip XF<br>Bits (only h                                 | cted off-chi<br>gh port latch<br>, EMIOCN r<br>ow the 1 k l<br>cted off-chi<br>the high-by<br>&AM only. C<br>as effect w                             | p. 8-bit off-<br>nes to resolve<br>nust be set<br>boundary a<br>p. 8-bit off-o<br>te of the ad<br>on-chip XRA<br>hen EMD2          | chip MOVX<br>ve upper ac<br>to a page t<br>re directed<br>chip MOVX<br>dress.<br>M is not vi | operations<br>dress byte<br>hat is not<br>on-chip.<br>operations  |

| Bits 1–0: | Accesse<br>use the c<br>Note that<br>contained<br>10: Split Moc<br>Accesse<br>use the c<br>11: External<br>CPU.<br>EALE1–0: Al               | s above th<br>current con<br>t in order to<br>d in the on<br>le with Bar<br>s above th<br>contents of<br>Only: MOV<br>LE Pulse-V<br>and ALE | e 1 k bound<br>tents of the<br>o access off<br>-chip addres<br>k Select: Ac<br>e 1 k bound<br>EMI0CN to<br>/X accesses<br>Vidth Select<br>low pulse wi                 | ary are dire<br>Address Hig<br>-chip space<br>ss space.<br>ccesses bel<br>ary are dire<br>determine<br>s off-chip XF<br>Bits (only h<br>idth = 1 SYS                 | cted off-chi<br>gh port latch<br>, EMI0CN r<br>ow the 1 k l<br>cted off-chi<br>the high-by<br>RAM only. C<br>as effect w<br>SCLK cycle               | p. 8-bit off-cones to resolve<br>nust be set<br>boundary and<br>p. 8-bit off-cones<br>te of the ad<br>on-chip XRA<br>hen EMD2      | chip MOVX<br>ve upper ac<br>to a page t<br>re directed<br>chip MOVX<br>dress.<br>M is not vi | operations<br>dress byte<br>hat is not<br>on-chip.<br>operations  |

| 3its 1–0: | Accesse<br>use the c<br>Note tha<br>containe<br>10: Split Moc<br>Accesse<br>use the c<br>11: External<br>CPU.<br>EALE1–0: AI<br>00: ALE high | s above th<br>current con<br>t in order to<br>d in the on<br>le with Bar<br>s above th<br>contents of<br>Only: MOV<br>LE Pulse-V<br>and ALE | e 1 k bound<br>tents of the<br>o access off<br>-chip addres<br>k Select: Ad<br>e 1 k bound<br>EMI0CN to<br>/X accesses<br>Vidth Select<br>low pulse wi<br>low pulse wi | ary are dire<br>Address Hig<br>-chip space<br>ss space.<br>ccesses bel<br>ary are dire<br>determine<br>s off-chip XF<br>Bits (only h<br>idth = 1 SYS<br>idth = 2 SYS | cted off-chi<br>gh port latch<br>, EMI0CN r<br>ow the 1 k l<br>cted off-chi<br>the high-by<br>RAM only. C<br>as effect w<br>SCLK cycle<br>SCLK cycle | p. 8-bit off-cones to resolve<br>nust be set<br>boundary and<br>p. 8-bit off-cone<br>te of the ad<br>on-chip XRA<br>hen EMD2<br>s. | chip MOVX<br>ve upper ac<br>to a page t<br>re directed<br>chip MOVX<br>dress.<br>M is not vi | operations<br>Idress byte<br>hat is not<br>on-chip.<br>operations |

#### SFR Definition 15.2. EMI0CF: External Memory Configuration

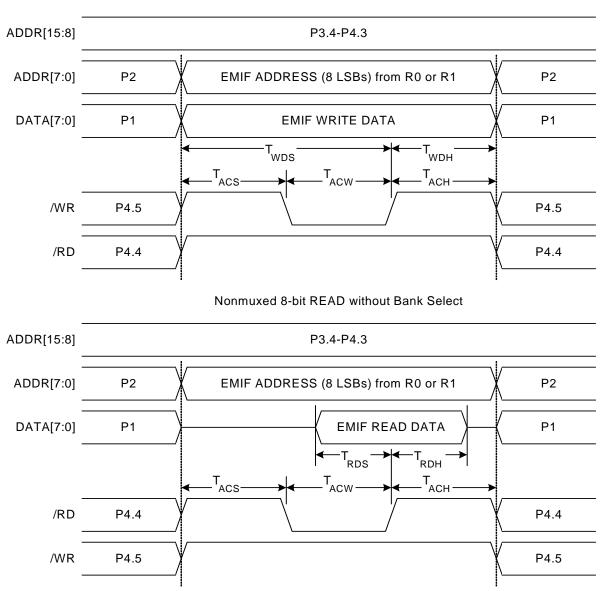

#### 15.6.1.2.8-bit MOVX without Bank Select: EMI0CF[4:2] = '101' or '111'.

Nonmuxed 8-bit WRITE without Bank Select

Figure 15.5. Non-multiplexed 8-bit MOVX without Bank Select Timing

| R/W       | R/W                          | R/W        | R/W          | R/W          | R/W         | R/W        | R/W       | Reset Value |

|-----------|------------------------------|------------|--------------|--------------|-------------|------------|-----------|-------------|

| WEAKPU    | JD XBARE                     | T1E        | T0E          | ECIE         |             | PCA0ME     |           | 0000000     |

| Bit7      | Bit6                         | Bit5       | Bit4         | Bit3         | Bit2        | Bit1       | Bit0      |             |

| Bit 7:    | WEAKPUD: F                   | ort I/O We | eak Pullup I | Disable.     |             |            |           |             |

|           | 0: Weak Pullu                | ps enable  | d (except fo | or Ports who | ose I/O are | configured | as analog | input).     |

|           | 1: Weak Pullu                | ps disable | d.           |              |             |            |           |             |

| Bit 6:    | XBARE: Cros                  | sbar Enab  | le.          |              |             |            |           |             |

|           | 0: Crossbar d                | sabled.    |              |              |             |            |           |             |

|           | 1: Crossbar e                | nabled.    |              |              |             |            |           |             |

| Bit 5:    | T1E: T1 Enab                 |            |              |              |             |            |           |             |

|           | 0: T1 unavaila               |            | •            |              |             |            |           |             |

|           | 1: T1 routed to              |            |              |              |             |            |           |             |