#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                               |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 50MHz                                                             |

| Connectivity               | SMBus (2-Wire/I²C), SPI, UART/USART                               |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                        |

| Number of I/O              | 29                                                                |

| Program Memory Size        | 16KB (16K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 1K x 8                                                            |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                       |

| Data Converters            | A/D 21x10b; D/A 1x10b                                             |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 32-LQFP                                                           |

| Supplier Device Package    | 32-LQFP (7x7)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f368-c-gqr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1. | System Overview                                       | 18 |

|----|-------------------------------------------------------|----|

|    | 1.1. CIP-51 <sup>™</sup> Microcontroller Core         |    |

|    | 1.1.1. Fully 8051 Compatible                          |    |

|    | 1.1.2. Improved Throughput                            | 22 |

|    | 1.1.3. Additional Features                            |    |

|    | 1.2. On-Chip Memory                                   | 23 |

|    | 1.3. On-Chip Debug Circuitry                          | 24 |

|    | 1.4. Programmable Digital I/O and Crossbar            | 25 |

|    | 1.5. Serial Ports                                     |    |

|    | 1.6. Programmable Counter Array                       | 26 |

|    | 1.7. 10-Bit Analog to Digital Converter               | 27 |

|    | 1.8. Comparators                                      |    |

|    | 1.9. 10-bit Current Output DAC                        | 30 |

| 2. | Absolute Maximum Ratings                              |    |

| 3. | Global Electrical Characteristics                     | 33 |

| 4. | Pinout and Package Definitions                        |    |

| 5. | 10-Bit ADC (ADC0, C8051F360/1/2/6/7/8/9)              |    |

|    | 5.1. Analog Multiplexer                               |    |

|    | 5.2. Temperature Sensor                               |    |

|    | 5.3. Modes of Operation                               |    |

|    | 5.3.1. Starting a Conversion                          |    |

|    | 5.3.2. Tracking Modes                                 |    |

|    | 5.3.3. Settling Time Requirements                     |    |

|    | 5.4. Programmable Window Detector                     |    |

|    | 5.4.1. Window Detector In Single-Ended Mode           |    |

|    | 5.4.2. Window Detector In Differential Mode           |    |

| 6. | 10-Bit Current Mode DAC (IDA0, C8051F360/1/2/6/7/8/9) |    |

|    | 6.1. IDA0 Output Scheduling                           |    |

|    | 6.1.1. Update Output On-Demand                        |    |

|    | 6.1.2. Update Output Based on Timer Overflow          |    |

|    | 6.1.3. Update Output Based on CNVSTR Edge             |    |

|    | 6.2. IDAC Output Mapping                              |    |

|    | Voltage Reference (C8051F360/1/2/6/7/8/9)             |    |

| 8. |                                                       | 70 |

| 9. |                                                       |    |

|    | 9.1. Performance                                      |    |

|    | 9.2. Programming and Debugging Support                |    |

|    | 9.3. Instruction Set                                  |    |

|    | 9.3.1. Instruction and CPU Timing                     |    |

|    | 9.3.2. MOVX Instruction and Program Memory            |    |

|    | 9.4. Memory Organization                              |    |

|    | 9.4.1. Program Memory                                 |    |

|    | 9.4.2. Data Memory                                    | 87 |

| 18. | SMBus                  |                                                    |     |

|-----|------------------------|----------------------------------------------------|-----|

|     | Figure 18.1.           | SMBus Block Diagram                                | 200 |

|     |                        | Typical SMBus Configuration                        |     |

|     |                        | SMBus Transaction                                  |     |

|     | Figure 18.4.           | Typical SMBus SCL Generation                       | 205 |

|     | Figure 18.5.           | Typical Master Transmitter Sequence                | 211 |

|     | Figure 18.6.           | Typical Master Receiver Sequence                   | 212 |

|     |                        | Typical Slave Receiver Sequence                    |     |

|     | Figure 18.8.           | Typical Slave Transmitter Sequence                 | 214 |

| 19. | UART0                  |                                                    |     |

|     |                        | UART0 Block Diagram                                |     |

|     |                        | UART0 Baud Rate Logic                              |     |

|     |                        | UART Interconnect Diagram                          |     |

|     |                        | 8-Bit UART Timing Diagram                          |     |

|     |                        | 9-Bit UART Timing Diagram                          |     |

|     |                        | UART Multi-Processor Mode Interconnect Diagram     | 222 |

|     |                        | Serial Peripheral Interface (SPI0)                 |     |

|     | •                      | SPI Block Diagram                                  |     |

|     |                        | Multiple-Master Mode Connection Diagram            | 235 |

|     | Figure 20.3.           | 3-Wire Single Master and 3-Wire Single Slave Mode  |     |

|     |                        | Connection Diagram                                 | 235 |

|     | Figure 20.4.           | 4-Wire Single Master Mode and 4-Wire Slave Mode    |     |

|     |                        | Connection Diagram                                 |     |

|     |                        | Master Mode Data/Clock Timing                      |     |

|     |                        | Slave Mode Data/Clock Timing (CKPHA = 0)           |     |

|     | Figure 20.7.           | Slave Mode Data/Clock Timing (CKPHA = 1)           | 238 |

|     |                        | SPI Master Timing (CKPHA = 0)                      |     |

|     |                        | SPI Master Timing (CKPHA = 1)                      |     |

|     |                        | ). SPI Slave Timing (CKPHA = 0)                    |     |

|     | Figure 20.11<br>Timers | I. SPI Slave Timing (CKPHA = 1)                    | 243 |

|     |                        | To Made O Pleak Diagram                            | 247 |

|     | -                      | T0 Mode 0 Block Diagram                            |     |

|     | •                      | T0 Mode 2 Block Diagram<br>T0 Mode 3 Block Diagram |     |

|     | -                      | Timer 2 16-Bit Mode Block Diagram                  |     |

|     | -                      | Timer 2 8-Bit Mode Block Diagram                   |     |

|     | •                      | Timer 3 16-Bit Mode Block Diagram                  |     |

|     |                        | Timer 3 8-Bit Mode Block Diagram                   |     |

|     |                        | able Counter Array                                 | 200 |

|     | •                      | PCA Block Diagram                                  | 262 |

|     |                        | PCA Counter/Timer Block Diagram                    |     |

|     |                        | PCA Interrupt Block Diagram                        |     |

|     | •                      | PCA Capture Mode Diagram                           |     |

|     |                        | PCA Software Timer Mode Diagram                    |     |

|     |                        | PCA High Speed Output Mode Diagram                 |     |

|     | 3                      |                                                    |     |

## 1. System Overview

C8051F36x devices are fully integrated mixed-signal System-on-a-Chip MCUs. Highlighted features are listed below. Refer to Table 1.1 for specific product feature selection.

- High-speed pipelined 8051-compatible microcontroller core (up to 100 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- True 10-bit 200 ksps 16-channel single-ended/differential ADC with analog multiplexer

- 10-bit Current Output DAC

- 2-cycle 16 by 16 Multiply and Accumulate Engine

- Precision programmable 25 MHz internal oscillator

- Up to 32 kB of on-chip Flash memory—1024 bytes are reserved

- 1024 bytes of on-chip RAM

- External Data Memory Interface with 64 kB address space

- SMBus/I2C, Enhanced UART, and Enhanced SPI serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

- Programmable Counter/Timer Array (PCA) with six capture/compare modules and Watchdog Timer function

- On-chip Power-On Reset, V<sub>DD</sub> Monitor, and Temperature Sensor

- Two on-chip Voltage Comparators

- up to 39 Port I/O (5 V tolerant)

With on-chip Power-On Reset,  $V_{DD}$  Monitor, Watchdog Timer, and clock oscillator, the C8051F36x devices are truly stand-alone System-on-a-Chip solutions. The Flash memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

Each device is specified for 3.0 to 3.6 V (100 MIPS) operation or 2.7 to 3.6 V (50 MIPS) operation over the industrial temperature range (-40 to +85 °C). The Port I/O and RST pins are tolerant of input signals up to 5 V. The C8051F36x devices are available in 48-pin TQFP packages, and C8051F36x devices are available in 32-pin LQFP and 28-pin QFN packages (also referred to as MLP or MLF packages). All package types are lead-free (RoHS compliant). See Table 1.1 for ordering part numbers. Block diagrams are included in Figure 1.1, Figure 1.2, and Figure 1.3.

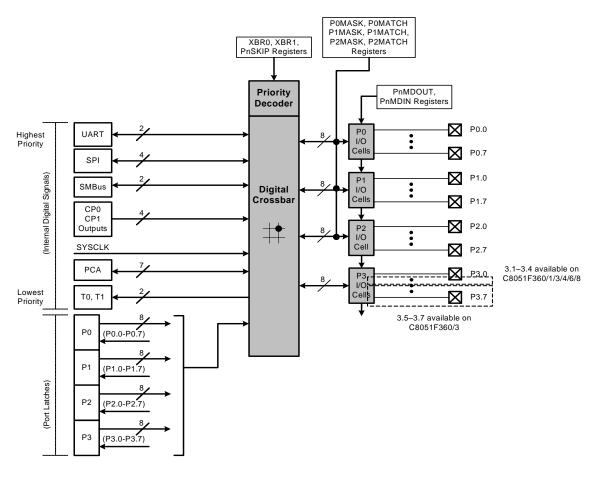

The Digital Crossbar allows mapping of internal digital system resources to Port I/O pins. (See Figure 1.8.) On-chip counter/timers, serial buses, HW interrupts, comparator output, and other digital signals in the controller can be configured to appear on the Port I/O pins specified in the Crossbar Control registers. This allows the user to select the exact mix of general purpose Port I/O and digital resources needed for the particular application.

## 1.5. Serial Ports

The C8051F36x Family includes an SMBus/I<sup>2</sup>C interface, a full-duplex UART with enhanced baud rate configuration, and an Enhanced SPI interface. Each of the serial buses is fully implemented in hardware and makes extensive use of the CIP-51's interrupts, thus requiring very little CPU intervention.

### 1.6. Programmable Counter Array

An on-chip Programmable Counter/Timer Array (PCA) is included in addition to the four 16-bit general purpose counter/timers. The PCA consists of a dedicated 16-bit counter/timer time base with three programmable capture/compare modules. The PCA clock is derived from one of six sources: the system clock divided by 12, the system clock divided by 4, Timer 0 overflows, an External Clock Input (ECI), the system clock, or the external oscillator clock source divided by 8. The external clock source selection is useful for

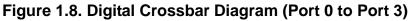

Figure 1.13. Comparator1 Block Diagram

## 1.9. 10-bit Current Output DAC

The C8051F360/1/2/6/7/8/9 devices includes a 10-bit current-mode Digital-to-Analog Converter (IDA0). The maximum current output of the IDA0 can be adjusted for three different current settings; 0.5 mA, 1 mA, and 2 mA. IDA0 features a flexible output update mechanism which allows for seamless full-scale changes and supports jitter-free updates for waveform generation. Three update modes are provided, allowing IDA0 output updates on a write to IDA0H, on a Timer overflow, or on an external pin edge.

## SFR Definition 5.6. ADC0CN: ADC0 Control

| R/W       | R/W                         | R/W           | R/W             | R/W            | R/W            | R/W           | R/W           | Reset Valu  |

|-----------|-----------------------------|---------------|-----------------|----------------|----------------|---------------|---------------|-------------|

| AD0EN     | AD0TM                       | AD0INT        | AD0BUSY         | <b>ADOWINT</b> | AD0CM2         | AD0CM1        | AD0CM0        | 0000000     |

| Bit7      | Bit6                        | Bit5          | Bit4            | Bit3           | Bit2           | Bit1          | Bit0          |             |

| Bit 7:    | AD0EN: AD0                  | C0 Enable     | Bit.            |                |                |               |               |             |

|           | 0: ADC0 Disa                | abled. ADC    | C0 is in low-p  | ower shutde    | own.           |               |               |             |

|           | 1: ADC0 Ena                 |               |                 |                |                | ersions.      |               |             |

| Bit 6:    | AD0TM: AD0                  | C0 Track N    | lode Bit.       |                |                |               |               |             |

|           | 0: Normal Tra               | ack Mode:     | When ADC0       | is enabled,    | tracking is    | continuous    | unless a coi  | nversion is |

|           | in progress.                |               |                 |                |                |               |               |             |

|           | 1: Low-powe                 |               |                 |                |                | ) bits (see b | elow).        |             |

| Bit 5:    | AD0INT: AD0                 |               | •               | •              | -              |               |               |             |

|           | 0: ADC0 has                 |               |                 |                | since the las  | st time AD0I  | NT was clea   | ared.       |

|           | 1: ADC0 has                 | •             |                 | ersion.        |                |               |               |             |

| Bit 4:    | ADOBUSY: A                  | ADC0 Busy     | Bit.            |                |                |               |               |             |

|           | Read:                       |               |                 |                |                |               |               |             |

|           | 0: ADC0 con                 |               |                 |                | i is not curre | enuy in prog  | ress. ADOIN   | vi is set t |

|           | 1: ADC0 con                 | -             | edge of ADC     | DU31.          |                |               |               |             |

|           | Write:                      |               | in progress.    |                |                |               |               |             |

|           | 0: No Effect.               |               |                 |                |                |               |               |             |

|           | 1: Initiates A              | DC0 Conve     | ersion if AD0   | CM2-0 = 00     | 00b            |               |               |             |

| Bit 3:    | ADOWINT: A                  |               |                 |                |                |               |               |             |

|           | 0: ADC0 Wir                 |               |                 |                |                | d since this  | flag was las  | t cleared.  |

|           | 1: ADC0 Wir                 |               |                 |                |                |               | U             |             |

| Bits 2–0: | AD0CM2-0:                   | ADC0 Star     | rt of Convers   | ion Mode S     | elect.         |               |               |             |

|           | When AD0TI                  | M = 0:        |                 |                |                |               |               |             |

|           | 000: ADC0 c                 | onversion     | initiated on e  | very write c   | f '1' to AD0   | BUSY.         |               |             |

|           | 001: ADC0 c                 |               |                 |                |                |               |               |             |

|           | 010: ADC0 c                 |               |                 |                |                |               |               |             |

|           | 011: ADC0 c                 |               |                 |                |                |               |               |             |

|           | 100: ADC0 c                 |               |                 |                |                | NVSTR.        |               |             |

|           | 101: ADC0 c                 |               | initiated on o  | vertiow of I   | imer 3.        |               |               |             |

|           | 11x: Reserve                | -             |                 |                |                |               |               |             |

|           | When AD0TI<br>000: Tracking |               | on write of '1' |                | SV and lasts   |               | eks followo   | hy con-     |

|           | versio                      | -             |                 |                |                |               |               |             |

|           | 001: Tracking               |               | on overflow o   | f Timer 0 ar   | nd lasts 3 S   | AR clocks f   | ollowed by a  | conversio   |

|           | 010: Tracking               | •             |                 |                |                |               | •             |             |

|           | 011: Tracking               | •             |                 |                |                |               |               |             |

|           | 100: ADC0 ti<br>edge.       |               |                 |                |                |               |               |             |

|           | 101: Tracking               |               |                 | (T) 0          |                |               | مالمين مالمين |             |

|           |                             | n initiateo o | n overtiow o    | t limer i ar   | nd lasts X S   | AR CIOCKS T   | ollowen nv r  | CONVERSION  |

## SFR Definition 9.1. SFR0CN: SFR Page Control

| R/W      | R/W      | R/W        | R/W         | R/W            | R/W          | R/W      | R/W                             | Reset Valu |

|----------|----------|------------|-------------|----------------|--------------|----------|---------------------------------|------------|

| Reserved | Reserved | Reserved   | Reserved    | Reserved       | Reserved     | Reserved | SFRPGEN                         | 0000000    |

| Bit7     | Bit6     | Bit5       | Bit4        | Bit3           | Bit2         | Bit1     | Bit0                            | ·          |

|          | •        | tch to SFR | page 0. Thi | is bit is used | d to control | •        | ervice routine<br>ging functior | ı.         |

## SFR Definition 9.2. SFRPAGE: SFR Page

| R/W  | R/W                                                                                                                           | R/W                                                                               | R/W                                                        | R/W                                                          | R/W                                                     | R/W                                       | R/W         | Reset Value |

|------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------|-------------|-------------|

|      |                                                                                                                               |                                                                                   |                                                            |                                                              |                                                         |                                           |             | 0000000     |

| Bit7 | Bit6                                                                                                                          | Bit5                                                                              | Bit4                                                       | Bit3                                                         | Bit2                                                    | Bit1                                      | Bit0        |             |

|      | ifying SFR's.<br>Write: Sets th<br>Read: Byte is<br>When enable<br>switch to SFR<br>(unless SFR<br>SFRPAGE is<br>caused by in | he SFR Pa<br>s the SFR p<br>ed in the SF<br>R Page 0x0<br>Stack was<br>the top by | FR Page Cc<br>00 and retur<br>altered befo<br>te of the SF | ontrol Regis<br>in to the pre<br>ore a return<br>iR Page Sta | ter (SFR0C<br>vious SFR<br>ing from the<br>ick, and pus | page upon<br>e interrupt).<br>sh/pop ever | return fror | n interrupt |

## SFR Definition 9.11. PCON: Power Control

| R/W     | R/W                                                                                               | R/W                                                         | R/W                                               | R/W                        | R/W            | R/W                    | R/W         | Reset Value |

|---------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------|----------------------------|----------------|------------------------|-------------|-------------|

| Reserve | d Reserved                                                                                        | Reserved                                                    | Reserved                                          | Reserved                   | Reserved       | STOP                   | IDLE        | 00000000    |

| Bit7    | Bit6                                                                                              | Bit5                                                        | Bit4                                              | Bit3                       | Bit2           | Bit1                   | Bit0        |             |

| Bit 0:  | Writing a '1'<br>1: CIP-51 for<br>IDLE: IDLE I<br>Writing a '1'<br>1: CIP-51 for<br>and all perip | rced into po<br>Mode Selec<br>to this bit w<br>rced into ID | wer-down r<br>t.<br>ill place the<br>LE mode. (\$ | node. (Turn<br>CIP-51 into | s off oscillat | tor).<br>e. This bit v | vill always | read '0'.   |

| SFR Addre   |                               |      | essable) | DAA           | DAA                                 |          | DAA  | Descrive    |

|-------------|-------------------------------|------|----------|---------------|-------------------------------------|----------|------|-------------|

| R           | R/W                           | R/W  | R/W      | R/W           | R/W                                 | R/W      | R/W  | Reset Value |

| _           | PSPI0                         | PT2  | PS0      | PT1           | PX1                                 | PT0      | PX0  | 1000000     |

| Bit7        | Bit6                          | Bit5 | Bit4     | Bit3          | Bit2                                | Bit1     | Bit0 |             |

| Bit 7:      | UNUSED. R                     |      |          |               |                                     |          |      |             |

| Bit 6:      | PSPI0: Seria                  | •    | ,        | ,             | rupt Priority                       | Control. |      |             |

|             | This bit sets                 |      |          |               |                                     |          |      |             |

|             | 0: SPI0 inter                 |      |          |               |                                     |          |      |             |

|             | 1: SPI0 inter                 |      |          |               |                                     |          |      |             |

| Bit 5:      | PT2: Timer 2                  |      |          |               |                                     |          |      |             |

|             | This bit sets                 |      |          |               | t.                                  |          |      |             |

|             | 0: Timer 2 int                |      |          |               |                                     |          |      |             |

| <b>D</b> 14 | 1: Timer 2 int                |      | • •      |               |                                     |          |      |             |

| Bit 4:      | PS0: UARTO                    |      |          |               |                                     |          |      |             |

|             | This bit sets                 |      |          |               | τ.                                  |          |      |             |

|             | 0: UART0 int                  |      |          |               |                                     |          |      |             |

| Bit 3:      | 1: UART0 int                  | •    | • •      |               |                                     |          |      |             |

| BIT 3:      | PT1: Timer 1<br>This bit sets |      |          |               |                                     |          |      |             |

|             | 0: Timer 1 inf                |      |          |               | ι.                                  |          |      |             |

|             | 1: Timer 1 int                |      |          |               |                                     |          |      |             |

| Bit 2:      | PX1: Externa                  |      | • •      |               |                                     |          |      |             |

| DIL Z.      | This bit sets                 |      |          |               | ot 1 interrup                       | .+       |      |             |

|             | 0: External Ir                |      |          |               | ot i interiup                       | <i>.</i> |      |             |

|             | 1: External Ir                |      |          |               |                                     |          |      |             |

| Bit 1:      | PT0: Timer 0                  |      | • •      |               |                                     |          |      |             |

| Dit 1.      | This bit sets                 |      |          |               | t                                   |          |      |             |

|             | 0: Timer 0 int                |      |          |               |                                     |          |      |             |

|             | 1: Timer 0 int                |      |          |               |                                     |          |      |             |

| Bit 0:      | PX0: Externa                  |      |          |               |                                     |          |      |             |

| 2.1 01      | This bit sets                 |      |          |               | ot 0 interrup                       | ot.      |      |             |

|             | 0: External Ir                |      |          |               | · · · · · · · · · · · · · · · · · · |          |      |             |

|             |                               |      |          | iority level. |                                     |          |      |             |

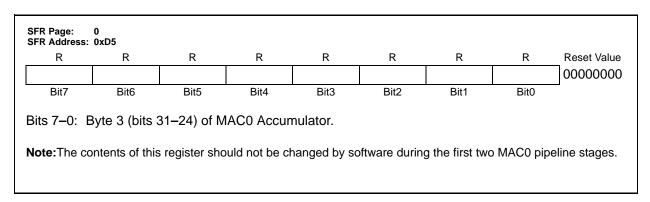

### SFR Definition 11.7. MAC0ACC3: MAC0 Accumulator Byte 3

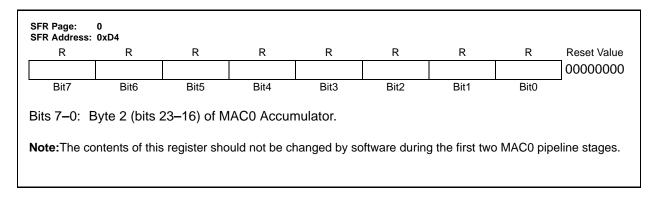

## SFR Definition 11.8. MAC0ACC2: MAC0 Accumulator Byte 2

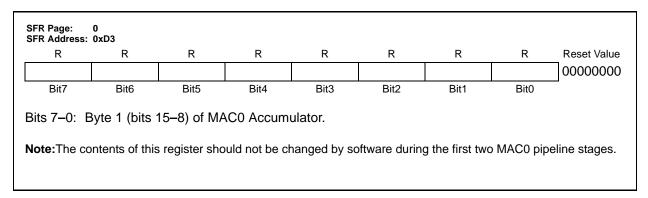

## SFR Definition 11.9. MAC0ACC1: MAC0 Accumulator Byte 1

| R/W    | R/W                         | R/W           | R/W           | R/W            | R/W         | R/W            | R/W         | Reset Value |

|--------|-----------------------------|---------------|---------------|----------------|-------------|----------------|-------------|-------------|

| CHWRE  | N CHRDEN                    | CHPFEN        | CHFLSH        | CHRETI         | CHISR       | CHMOVC         | CHBLKW      | 11100110    |

| Bit7   | Bit6                        | Bit5          | Bit4          | Bit3           | Bit2        | Bit1           | Bit0        |             |

| Bit 7: | CHWREN: C                   | Cache Write   | Enable.       |                |             |                |             |             |

|        | This bit enab               |               |               |                |             |                |             |             |

|        | locks.                      |               |               | <b>U</b>       | except dur  | ing Flash writ | tes/erasure | s or cache  |

|        | 1: Writes to                |               |               | wed.           |             |                |             |             |

| Bit 6: | CHRDEN: C                   |               |               |                |             |                |             |             |

|        |                             |               |               |                |             | he cache me    |             |             |

|        |                             |               |               |                |             | refetch engin  | e.          |             |

|        | 1: Instruction              |               |               | cache (whe     | en availabl | e).            |             |             |

| Bit 5: | CHPFEN: C                   |               |               |                |             |                |             |             |

|        | This bit enab               |               | •             | э.             |             |                |             |             |

|        | 0: Prefetch e               | •             |               |                |             |                |             |             |

| Bit 4: | 1: Prefetch e<br>CHFLSH: Ca | •             | ableu.        |                |             |                |             |             |

| Dit 4. |                             |               | is hit cloars | the cache (    | contents ]  | This bit alway | e roade 'O' |             |

| Bit 3: | CHRETI: Ca                  |               |               |                | Jointenito. | nis bit alway  | 316003 0.   |             |

| Dit 0. | This bit enab               |               |               |                | ess to he   | cached         |             |             |

|        | 0: Destinatio               |               |               |                |             |                |             |             |

|        | 1: RETI dest                |               |               |                |             |                |             |             |

| Bit 2: | CHISR: Cac                  | he ISR Ena    | ble.          |                |             |                |             |             |

|        | This bit allow              | vs instructio | ns which ar   | e part of an   | Interrupt S | Service Routi  | ne (ISR) to | be cached   |

|        | 0: Instruction              | ns in ISRs w  | ill not be lo | aded into ca   | ache mem    | ory.           |             |             |

|        | 1: Instruction              | ns in ISRs c  | an be cach    | ed.            |             |                |             |             |

| Bit 1: | CHMOVC: C                   | Cache MOV     | C Enable.     |                |             |                |             |             |

|        |                             |               |               |                |             | be loaded inte | o the cache | e memory.   |

|        | 0: Data requ                |               |               |                |             |                |             |             |

|        |                             |               |               | ctions will be | e loaded ir | nto cache me   | mory.       |             |

| Bit 0: | CHBLKW: B                   |               |               |                |             |                |             |             |

|        | This bit allow              |               |               |                |             |                |             |             |

|        | 0: Each byte                |               |               |                |             |                |             |             |

|        | 1: Flash byte               | es are writte | n in groups   | s of four (for | code space  | ce writes).    |             |             |

## SFR Definition 14.1. CCH0CN: Cache Control

| Multiplexe  | d Mode   | Non Multiple | exed Mode |

|-------------|----------|--------------|-----------|

| Signal Name | Port Pin | Signal Name  | Port Pin  |

| /RD         | P4.4     | /RD          | P4.4      |

| /WR         | P4.5     | /WR          | P4.5      |

| ALE         | P0.0     | ALE          | P0.0      |

| D0/A0       | P1.0     | D0           | P1.0      |

| D1/A1       | P1.1     | D1           | P1.1      |

| D2/A2       | P1.2     | D2           | P1.2      |

| D3/A3       | P1.3     | D3           | P1.3      |

| D4/A4       | P1.4     | D4           | P1.4      |

| D5/A5       | P1.5     | D5           | P1.5      |

| D6/A6       | P1.6     | D6           | P1.6      |

| D7/A7       | P1.7     | D7           | P1.7      |

| A8          | P3.4     | A0           | P2.0      |

| A9          | P3.5     | A1           | P2.1      |

| A10         | P3.6     | A2           | P2.2      |

| A11         | P3.7     | A3           | P2.3      |

| A12         | P4.0     | A4           | P2.4      |

| A13         | P4.1     | A5           | P2.5      |

| A14         | P4.2     | A6           | P2.6      |

| A15         | P4.3     | A7           | P2.7      |

| -           | -        | A8           | P3.4      |

| -           | -        | A9           | P3.5      |

| -           | -        | A10          | P3.6      |

| -           | -        | A11          | P3.7      |

| _           | _        | A12          | P4.0      |

| _           | _        | A13          | P4.1      |

| -           | -        | A14          | P4.2      |

| _           | _        | A15          | P4.3      |

Table 15.1. EMIF Pinout (C8051F360/3)

## SFR Definition 15.1. EMI0CN: External Memory Interface Control

| R/W    | R/W                               | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | Reset Value |

|--------|-----------------------------------|--------|--------|--------|--------|--------|--------|-------------|

| PGSEL7 | PGSEL6                            | PGSEL5 | PGSEL4 | PGSEL3 | PGSEL2 | PGSEL1 | PGSEL0 | 0000000     |

| Bit7   | Bit6                              | Bit5   | Bit4   | Bit3   | Bit2   | Bit1   | Bit0   |             |

| a      | The XRAM F<br>address whe<br>RAM. |        |        |        |        |        |        |             |

## 15.5. Memory Mode Selection

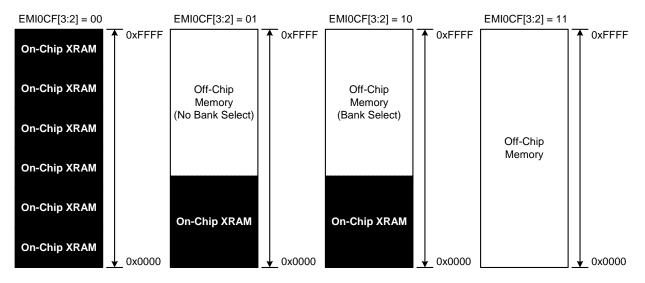

The external data memory space can be configured in one of four modes, shown in Figure 15.3, based on the EMIF Mode bits in the EMI0CF register (SFR Definition 15.2). These modes are summarized below. More information about the different modes can be found in Section "15.6. Timing" on page 159.

Figure 15.3. EMIF Operating Modes

#### 15.5.1. Internal XRAM Only

When EMI0CF.[3:2] are set to '00', all MOVX instructions will target the internal XRAM space on the device. Memory accesses to addresses beyond the populated space will wrap on 1k boundaries. As an example, the addresses 0x0400 and 0x1000 both evaluate to address 0x0000 in on-chip XRAM space.

- 8-bit MOVX operations use the contents of EMI0CN to determine the high-byte of the effective address and R0 or R1 to determine the low-byte of the effective address.

- 16-bit MOVX operations use the contents of the 16-bit DPTR to determine the effective address.

#### 15.5.2. Split Mode without Bank Select

When EMI0CF.[3:2] are set to '01', the XRAM memory map is split into two areas, on-chip space and off-chip space.

- Effective addresses below the internal XRAM size boundary will access on-chip XRAM space.

- Effective addresses above the internal XRAM size boundary will access off-chip space.

- 8-bit MOVX operations use the contents of EMI0CN to determine whether the memory access is on-chip or off-chip. However, in the "No Bank Select" mode, an 8-bit MOVX operation will not drive the upper 8-bits A[15:8] of the Address Bus during an off-chip access. This allows the user to manipulate the upper address bits at will by setting the Port state directly via the port latches. This behavior is in contrast with "Split Mode with Bank Select" described below. The lower 8-bits of the Address Bus A[7:0] are driven, determined by R0 or R1.

- 16-bit MOVX operations use the contents of DPTR to determine whether the memory access is on-chip or off-chip, and unlike 8-bit MOVX operations, the full 16-bits of the Address Bus A[15:0] are driven during the off-chip transaction.

# C8051F360/1/2/3/4/5/6/7/8/9

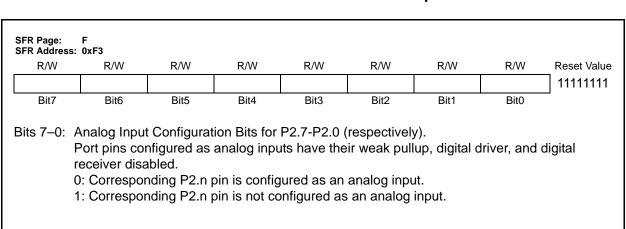

## SFR Definition 17.16. P2MDIN: Port2 Input Mode

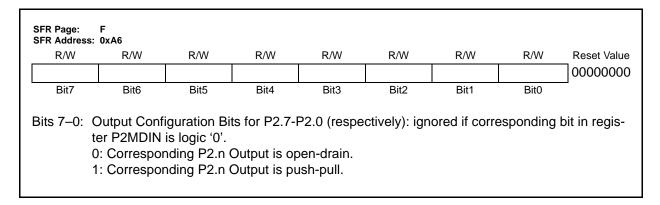

## SFR Definition 17.17. P2MDOUT: Port2 Output Mode

# C8051F360/1/2/3/4/5/6/7/8/9

| SFR Address:<br>R | 0xB5<br>R/W                   | R/W  | R/W  | R/W          | R/W        | R/W       | R/W       | Reset Value |

|-------------------|-------------------------------|------|------|--------------|------------|-----------|-----------|-------------|

| _                 | P4.6                          | P4.5 | P4.4 | P4.3         | P4.2       | P4.1      | P4.0      | 01111111    |

| Bit7              | Bit6                          | Bit5 | Bit4 | Bit3         | Bit2       | Bit1      | Bit0      |             |

|                   | 0: Logic Low<br>1: Logic High |      |      | ce if corres | ponding P4 | MDOUT.n l | oit = 0). |             |

## SFR Definition 17.25. P4: Port4

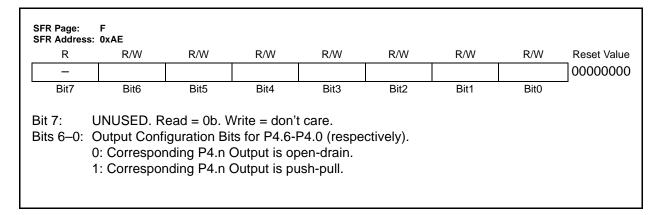

## SFR Definition 17.26. P4MDOUT: Port4 Output Mode

# C8051F360/1/2/3/4/5/6/7/8/9

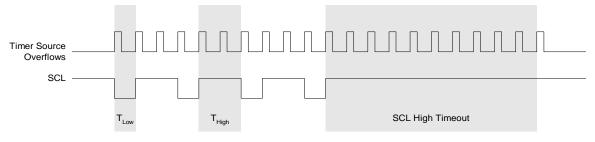

Figure 18.4 shows the typical SCL generation described by Equation 18.2. Notice that  $T_{HIGH}$  is typically twice as large as  $T_{LOW}$ . The actual SCL output may vary due to other devices on the bus (SCL may be extended low by slower slave devices, or driven low by contending master devices). The bit rate when operating as a master will never exceed the limits defined by equation Equation 18.1.

Figure 18.4. Typical SMBus SCL Generation

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 18.2 shows the minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| EXTHOLD                                                                                                                                                                                                                                                                     | Minimum SDA Setup Time             | Minimum SDA Hold Time |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|--|--|--|--|

|                                                                                                                                                                                                                                                                             | T <sub>low</sub> – 4 system clocks |                       |  |  |  |  |

| 0                                                                                                                                                                                                                                                                           | or                                 | 3 system clocks       |  |  |  |  |

|                                                                                                                                                                                                                                                                             | 1 system clock + s/w delay*        |                       |  |  |  |  |

| 1                                                                                                                                                                                                                                                                           | 11 system clocks                   | 12 system clocks      |  |  |  |  |

| *Note: Setup Time for ACK bit transmissions and the MSB of all data transfers. The s/w delay occurs between the time SMB0DAT or ACK is written and when SI is cleared. Note that if SI is cleared in the same write that defines the outgoing ACK value, s/w delay is zero. |                                    |                       |  |  |  |  |

Table 18.2. Minimum SDA Setup and Hold Times

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "18.3.3. SCL Low Timeout" on page 202). The SMBus interface will force Timer 3 to reload while SCL is high, and allow Timer 3 to count when SCL is low. The Timer 3 interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 18.4). When a Free Timeout is detected, the interface will respond as if a STOP was detected (an interrupt will be generated, and STO will be set).

## 20.3. SPI0 Slave Mode Operation

When SPI0 is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPI0 logic counts SCK edges. When 8 bits have been shifted through the shift register, the SPIF flag is set to logic '1', and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPI0DAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPI0DAT. Writes to SPI0DAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data, the SPI will load the shift register with the transmit buffer's contents after the last SCK edge of the next (or current) SPI transfer.

When configured as a slave, SPI0 can be configured for 4-wire or 3-wire operation. The default, 4-wire slave mode, is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In 4-wire mode, the NSS signal is routed to a port pin and configured as a digital input. SPI0 is enabled when NSS is logic '0', and disabled when NSS is logic '1'. The bit counter is reset on a falling edge of NSS. Note that the NSS signal must be driven low at least 2 system clocks before the first active edge of SCK for each byte transfer. Figure 20.4 shows a connection diagram between two slave devices in 4-wire slave mode and a master device.

3-wire slave mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. NSS is not used in this mode, and is not mapped to an external port pin through the crossbar. Since there is no way of uniquely addressing the device in 3-wire slave mode, SPI0 must be the only slave device present on the bus. It is important to note that in 3-wire slave mode there is no external means of resetting the bit counter that determines when a full byte has been received. The bit counter can only be reset by disabling and re-enabling SPI0 with the SPIEN bit. Figure 20.3 shows a connection diagram between a slave device in 3-wire slave mode and a master device.

### 20.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to logic '1':

All of the following bits must be cleared by software.

- 1. The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic '1' at the end of each byte transfer. This flag can occur in all SPI0 modes.

- 2. The Write Collision Flag, WCOL (SPI0CN.6) is set to logic '1' if a write to SPI0DAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes.

- 3. The Mode Fault Flag MODF (SPI0CN.5) is set to logic '1' when SPI0 is configured as a master, and for multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTEN and SPIEN bits in SPI0CN are set to logic '0' to disable SPI0 and allow another master device to access the bus.

- 4. The Receive Overrun Flag RXOVRN (SPI0CN.4) is set to logic '1' when configured as a slave, and a transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

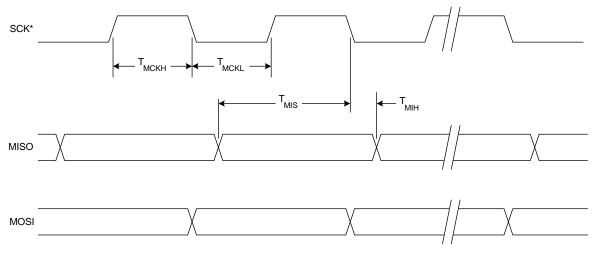

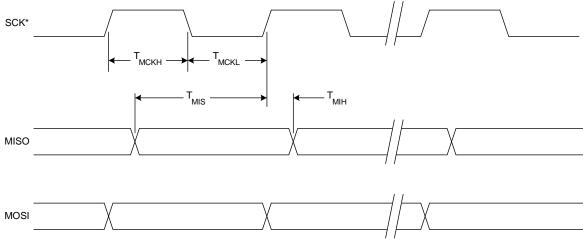

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

## Figure 20.9. SPI Master Timing (CKPHA = 1)

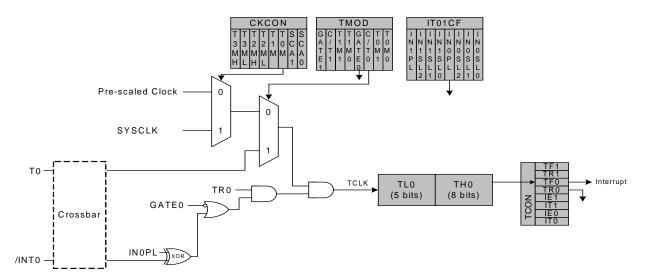

Figure 21.1. T0 Mode 0 Block Diagram

#### 21.1.2. Mode 1: 16-bit Counter/Timer

Mode 1 operation is the same as Mode 0, except that the counter/timer registers use all 16 bits. The counter/timers are enabled and configured in Mode 1 in the same manner as for Mode 0.

#### 21.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic '0' or when the input signal /INT0 is active as defined by bit IN0PL in register IT01CF (see Section "10.5. External Interrupts" on page 115 for details on the external input signals /INT0 and /INT1).

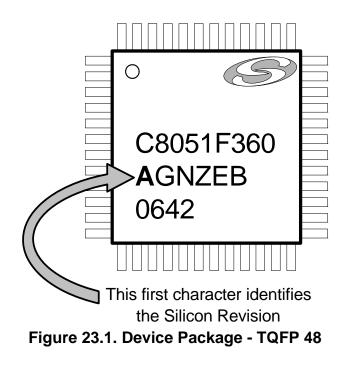

## 23. Revision Specific Behavior

This chapter contains behavioral differences between the C8051F36x hardware revisions and behavior as stated in the data sheet.

#### 23.1. Revision Identification

The Lot ID Code on the top side of the device package can be used for decoding device revision information. On C8051F36x devices the revision letter is the first letter of the Lot ID Code.

Figures 23.1, 23.2, and 23.3 show how to find the Lot ID Code on the top side of the device package.