Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 72MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB             |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT             |

| Number of I/O              | 37                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 10K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                |

| Data Converters            | A/D 10x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 48-LQFP                                                                  |

| Supplier Device Package    | -                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103c6t6atr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 8 | Revis | ion hist | ory                                     | 96   |

|---|-------|----------|-----------------------------------------|------|

| 7 | Order | ing info | rmation scheme                          | 95   |

|   |       | 6.6.2    | Selecting the product temperature range | . 93 |

|   |       | 6.6.1    | Reference document                      | . 92 |

|   | 6.6   | Thermal  | characteristics                         | 92   |

|   | 6.5   | LQFP48   | package information                     | 88   |

| Figure 41. | UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |    |

|------------|---------------------------------------------------------------------------|----|

| -          | package outline                                                           | 79 |

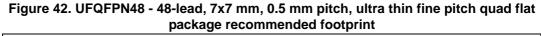

| Figure 42. | UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |    |

|            | package recommended footprint                                             | 30 |

| Figure 43. | UFQFPN48 marking example (package view                                    | 31 |

| Figure 44. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline         | 32 |

| Figure 45. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package                 |    |

|            | recommended footprint                                                     | 33 |

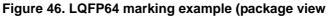

| Figure 46. | LQFP64 marking example (package view                                      | 34 |

| Figure 47. | TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch thin profile fine pitch ball    |    |

|            | grid array package outline                                                | 35 |

| Figure 48. | TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball   |    |

|            | grid array, recommended footprint                                         | 36 |

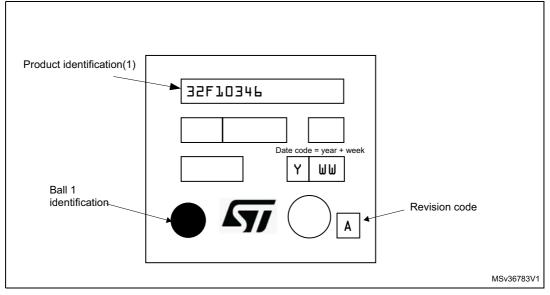

| Figure 49. | TFBGA64 marking example (package view                                     |    |

| Figure 50. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline           |    |

| Figure 51. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                   |    |

| -          | recommended footprint                                                     | 90 |

| Figure 52. | LQFP48 marking example (package view                                      |    |

| Figure 53. | LQFP64 P <sub>D</sub> max vs. T <sub>A</sub>                              |    |

# 2 Description

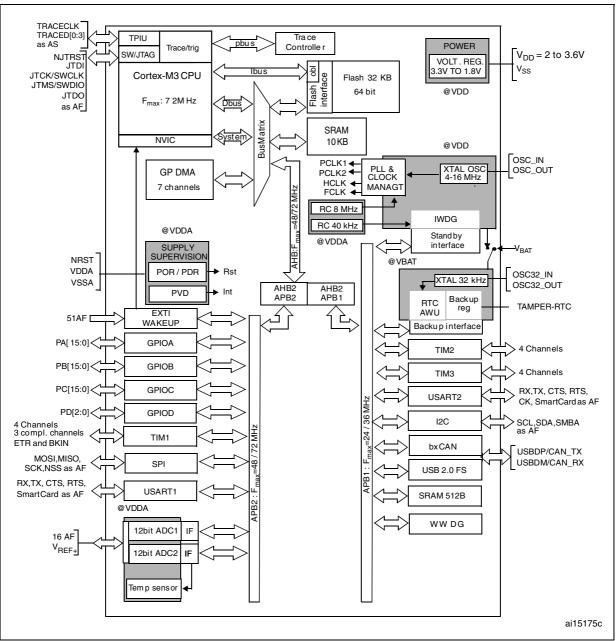

The STM32F103x4 and STM32F103x6 performance line family incorporates the highperformance ARM® Cortex<sup>™</sup>-M3 32-bit RISC core operating at a 72 MHz frequency, highspeed embedded memories (Flash memory up to 32 Kbytes and SRAM up to 6 Kbytes), and an extensive range of enhanced I/Os and peripherals connected to two APB buses. All devices offer two 12-bit ADCs, three general purpose 16-bit timers plus one PWM timer, as well as standard and advanced communication interfaces: up to two I<sup>2</sup>Cs and SPIs, three USARTs, an USB and a CAN.

The STM32F103xx low-density performance line family operates from a 2.0 to 3.6 V power supply. It is available in both the -40 to +85 °C temperature range and the -40 to +105 °C extended temperature range. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F103xx low-density performance line family includes devices in four different package types: from 36 pins to 64 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the STM32F103xx low-density performance line microcontroller family suitable for a wide range of applications such as motor drives, application control, medical and handheld equipment, PC and gaming peripherals, GPS platforms, industrial applications, PLCs, inverters, printers, scanners, alarm systems, video intercoms, and HVACs.

Figure 1. STM32F103xx performance line block diagram

1.  $T_A = -40$  °C to +105 °C (junction temperature up to 125 °C).

2. AF = alternate function on I/O port pin.

This hardware block provides flexible interrupt management features with minimal interrupt latency.

## 2.3.6 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 19 edge detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 51 GPIOs can be connected to the 16 external interrupt lines.

## 2.3.7 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-16 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the configuration of the AHB frequency, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the AHB and the high-speed APB domains is 72 MHz. The maximum allowed frequency of the low-speed APB domain is 36 MHz. See *Figure 2* for details on the clock tree.

#### 2.3.8 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from User Flash

- Boot from System Memory

- Boot from embedded SRAM

The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART1. For further details please refer to AN2606.

#### 2.3.9 Power supply schemes

- $V_{DD} = 2.0$  to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through  $V_{DD}$  pins.

- $V_{SSA}$ ,  $V_{DDA} = 2.0$  to 3.6 V: external analog power supplies for ADC, reset blocks, RCs and PLL (minimum voltage to be applied to  $V_{DDA}$  is 2.4 V when the ADC is used).  $V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD}$  and  $V_{SS}$ , respectively.

- V<sub>BAT</sub> = 1.8 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to *Figure 11: Power supply scheme*.

## 2.3.10 Power supply supervisor

The device has an integrated power-on reset (POR)/power-down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains

in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

Refer to Table 11: Embedded reset and power control block characteristics for the values of  $V_{POR/PDR}$  and  $V_{PVD}$ .

#### 2.3.11 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in the nominal regulation mode (Run)

- LPR is used in the Stop mode

- Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost)

This regulator is always enabled after reset. It is disabled in Standby mode, providing high impedance output.

#### 2.3.12 Low-power modes

The STM32F103xx performance line supports three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

The Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm or the USB wakeup.

• Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm occurs.

The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

Note:

DocID15060 Rev 7

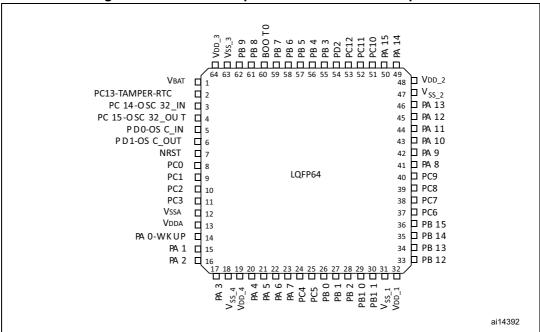

# 3 Pinouts and pin description

|                          |                                                                                                                                                 |                                                                                                                                          |                                                          | Тур <sup>(1)</sup>                                       |                                                          |                          | Max                            |          |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|--------------------------|--------------------------------|----------|--|

| Symbol                   | Parameter                                                                                                                                       | Conditions                                                                                                                               | V <sub>DD</sub> /V <sub>BA</sub><br><sub>T</sub> = 2.0 V | V <sub>DD</sub> /V <sub>BA</sub><br><sub>T</sub> = 2.4 V | V <sub>DD</sub> /V <sub>BA</sub><br><sub>T</sub> = 3.3 V | T <sub>A</sub> =<br>85 ℃ | T <sub>A</sub> =<br>105 °<br>C | Uni<br>t |  |

|                          | Supply<br>current in                                                                                                                            | Regulator in Run mode, low-speed<br>and high-speed internal RC<br>oscillators and high-speed oscillator<br>OFF (no independent watchdog) | -                                                        | 21.3                                                     | 21.7                                                     | 160                      | 200                            |          |  |

| Stop mode                | Regulator in Low Power mode, low-<br>speed and high-speed internal RC<br>oscillators and high-speed oscillator<br>OFF (no independent watchdog) | -                                                                                                                                        | 11.3                                                     | 11.7                                                     | 145                                                      | 185                      |                                |          |  |

| .00                      | Supply<br>current in<br>Standby                                                                                                                 | Low-speed internal RC oscillator<br>and independent watchdog ON                                                                          | -                                                        | 2.75                                                     | 3.4                                                      | -                        | -                              | μA       |  |

|                          |                                                                                                                                                 | Low-speed internal RC oscillator<br>ON, independent watchdog OFF                                                                         | -                                                        | 2.55                                                     | 3.2                                                      | -                        | -                              |          |  |

| mode                     | Low-speed internal RC oscillator<br>and independent watchdog OFF,<br>low-speed oscillator and RTC OFF                                           | -                                                                                                                                        | 1.55                                                     | 1.9                                                      | 3.2                                                      | 4.5                      |                                |          |  |

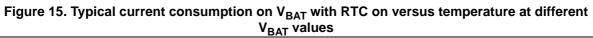

| I <sub>DD_VBA</sub><br>T | Backup<br>domain<br>supply<br>current                                                                                                           | Low-speed oscillator and RTC ON                                                                                                          | 0.9                                                      | 1.1                                                      | 1.4                                                      | 1.9 <sup>(2)</sup>       | 2.2                            |          |  |

|  | Table 16. Typical and maximum current consumpt | tions in Stop and Standby modes |

|--|------------------------------------------------|---------------------------------|

|--|------------------------------------------------|---------------------------------|

1. Typical values are measured at  $T_A = 25$  °C.

2. Based on characterization, not tested in production.

| Symbol            | Parameter           | Conditions                                                                               | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|---------------------|------------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

|                   |                     | Read mode<br>$f_{HCLK} = 72 \text{ MHz}$ with 2 wait<br>states, $V_{DD} = 3.3 \text{ V}$ | -                  | -   | 20                 | mA   |

| I <sub>DD</sub>   | Supply current      | Write / Erase modes<br>f <sub>HCLK</sub> = 72 MHz, V <sub>DD</sub> = 3.3 V               | -                  | -   | 5                  | mA   |

|                   |                     | Power-down mode / Halt,<br>$V_{DD} = 3.0$ to 3.6 V                                       | -                  | -   | 50                 | μA   |

| V <sub>prog</sub> | Programming voltage | -                                                                                        | 2                  | -   | 3.6                | V    |

Table 28. Flash memory characteristics (continued)

1. Guaranteed by design, not tested in production.

| Symbol           | Parameter      | tor Conditions                                                                          |    | Value |     |         |

|------------------|----------------|-----------------------------------------------------------------------------------------|----|-------|-----|---------|

| Symbol Parameter |                | Conditions                                                                              |    | Тур   | Max | Unit    |

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10 | -     | -   | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30 | -     | -   |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10 | -     | -   | Years   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20 | -     | -   |         |

#### Table 29. Flash memory endurance and data retention

1. Based on characterization, not tested in production.

2. Cycling performed over the whole temperature range.

## 5.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 30*. They are based on the EMS levels and classes defined in application note AN1709.

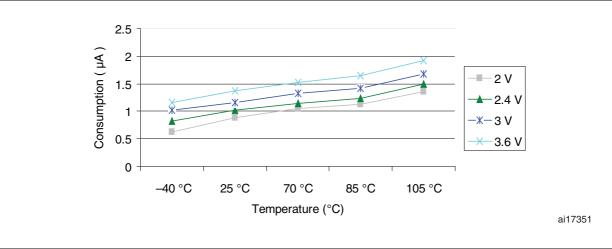

Figure 25. 5 V tolerant I/O input characteristics - CMOS port

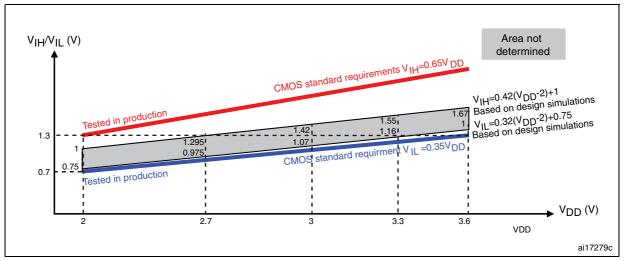

Figure 26. 5 V tolerant I/O input characteristics - TTL port

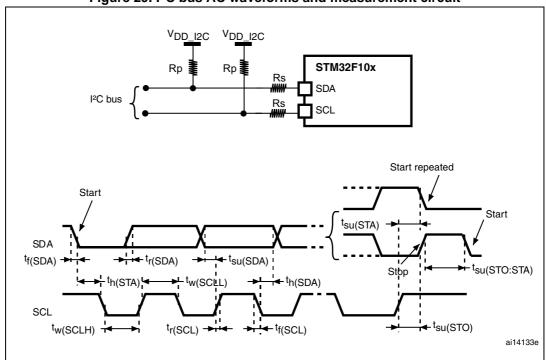

Figure 29. I<sup>2</sup>C bus AC waveforms and measurement circuit

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}.$

2. Rs = Series protection resistors, Rp = Pull-up resistors,  $V_{DD_{-12C}} = 12C$  bus supply.

| f <sub>SCL</sub> (kHz) | I2C_CCR value           |

|------------------------|-------------------------|

|                        | R <sub>P</sub> = 4.7 kΩ |

| 400                    | 0x801E                  |

| 300                    | 0x8028                  |

| 200                    | 0x803C                  |

| 100                    | 0x00B4                  |

| 50                     | 0x0168                  |

| 20                     | 0x0384                  |

#### Table 41. SCL frequency (fpci k1= 36 MHz., Vpc 12c = 3.3 V)<sup>(1)(2)</sup>

1.  $R_P$  = External pull-up resistance,  $f_{SCL} = I^2C$  speed,

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed ±2%. These variations depend on the accuracy of the external components used to design the application.

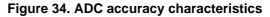

| Symbol | Parameter                    | Test conditions                                                                      | Тур  | Max <sup>(4)</sup> | Unit |  |

|--------|------------------------------|--------------------------------------------------------------------------------------|------|--------------------|------|--|

| ET     | Total unadjusted error       |                                                                                      | ±2   | ±5                 |      |  |

| EO     | Offset error                 | f <sub>PCLK2</sub> = 56 MHz,<br>f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ, | ±1.5 | ±2.5               |      |  |

| EG     | Gain error                   | $V_{DDA} = 2.4 \text{ V to } 3.6 \text{ V}$                                          | ±1.5 | ±3                 | LSB  |  |

| ED     | Differential linearity error | Measurements made after                                                              | ±1   | ±2                 |      |  |

| EL     | Integral linearity error     |                                                                                      | ±1.5 | ±3                 |      |  |

### Table 49. ADC accuracy<sup>(1) (2) (3)</sup>

1. ADC DC accuracy values are measured after internal calibration.

2. Better performance could be achieved in restricted  $V_{DD}$ , frequency and temperature ranges.

3. ADC Accuracy vs. Negative Injection Current: Injecting negative current on any of the standard (non-robust) analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 5.3.12 does not affect the ADC accuracy.

4. Based on characterization, not tested in production.

# 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

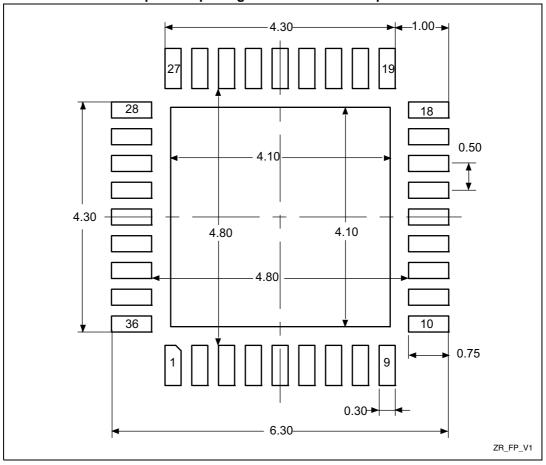

## 6.1 VFQFPN36 Package

Figure 38. VFQFPN36 - 36-pin, 6x6 mm, 0.5 mm pitch very thin profile fine pitch quad flat package outline

1. Drawing is not to scale.

# Figure 39. VFQFPN36 - 36-pin, 6x6 mm, 0.5 mm pitch very thin profile fine pitch quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Мах   | Min    | Тур                   | Max    |

| А      | 0.500 | 0.550       | 0.600 | 0.0197 | 0.0217                | 0.0236 |

| A1     | 0.000 | 0.020       | 0.050 | 0.0000 | 0.0008                | 0.0020 |

| D      | 6.900 | 7.000       | 7.100 | 0.2717 | 0.2756                | 0.2795 |

| E      | 6.900 | 7.000       | 7.100 | 0.2717 | 0.2756                | 0.2795 |

| D2     | 5.500 | 5.600       | 5.700 | 0.2165 | 0.2205                | 0.2244 |

| E2     | 5.500 | 5.600       | 5.700 | 0.2165 | 0.2205                | 0.2244 |

| L      | 0.300 | 0.400       | 0.500 | 0.0118 | 0.0157                | 0.0197 |

| Т      | -     | 0.152       | -     | -      | 0.0060                | -      |

| b      | 0.200 | 0.250       | 0.300 | 0.0079 | 0.0098                | 0.0118 |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |

| ddd    | -     | -           | 0.080 | -      | -                     | 0.0031 |

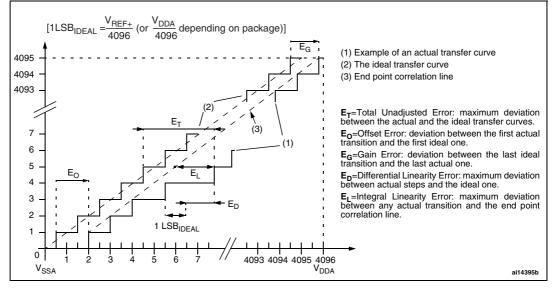

Table 52. UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flatpackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

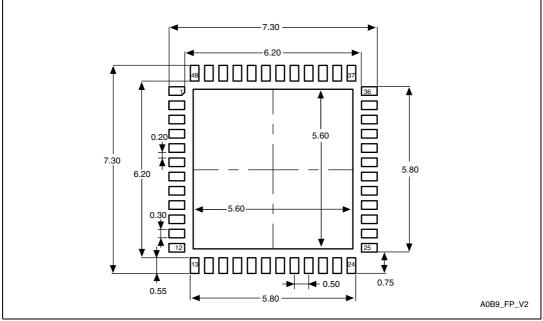

## **Device Marking for LQFP64**

The following figure gives an example of topside marking orientation versus ball 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

#### **Device Marking for TFBGA64**

The following figure gives an example of topside marking orientation versus ball 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

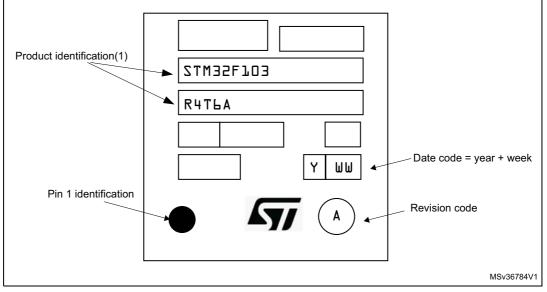

# 6.5 LQFP48 package information

SEATING PLANE A2 ŨŦŨŦŨŦŨŦĬĦŮ<del>Ÿ</del>ŨŦŨŦŨŦŨŦŎŹ F 0.25 mm GAUGE PLANE ĸ D A1 D1 L1 D3 24 37 Œ b **CHE** <u>ш</u> ш Ē ----------€ 48 13 PIN 1 IDENTIFICATION 1 12 e 5B\_ME\_V2

Figure 50. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

### 6.6.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Table 58: Ordering information scheme*.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature.

As applications do not commonly use the STM32F103xx at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.

The following examples show how to calculate the temperature range needed for a given application.

#### **Example 1: High-performance application**

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax} = 82$  °C (measured according to JESD51-2), I<sub>DDmax</sub> = 50 mA, V<sub>DD</sub> = 3.5 V, maximum 20 I/Os used at the same time in output at low level with I<sub>OL</sub> = 8 mA, V<sub>OL</sub>= 0.4 V and maximum 8 I/Os used at the same time in output at low level with I<sub>OL</sub> = 20 mA, V<sub>OL</sub>= 1.3 V

P<sub>INTmax =</sub> 50 mA × 3.5 V= 175 mW

P<sub>IOmax = 20</sub> × 8 mA × 0.4 V + 8 × 20 mA × 1.3 V = 272 mW

This gives:  $P_{INTmax} = 175 \text{ mW}$  and  $P_{IOmax} = 272 \text{ mW}$ :

P<sub>Dmax =</sub> 175 <sub>+</sub> 272 = 447 mW

Thus: P<sub>Dmax</sub> = 447 mW

Using the values obtained in *Table*  $57 T_{Jmax}$  is calculated as follows:

For LQFP64, 45 °C/W

T<sub>Jmax</sub> = 82 °C + (45 °C/W × 447 mW) = 82 °C + 20.115 °C = 102.115 °C

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ).

In this case, parts must be ordered at least with the temperature range suffix 6 (see *Table 58: Ordering information scheme*).

#### **Example 2: High-temperature application**

Using the same rules, it is possible to address applications that run at high ambient temperatures with a low dissipation, as long as junction temperature  $T_J$  remains within the specified range.

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax} = 115 \text{ °C}$  (measured according to JESD51-2),  $I_{DDmax} = 20 \text{ mA}$ ,  $V_{DD} = 3.5 \text{ V}$ , maximum 20 I/Os used at the same time in output at low level with  $I_{OL} = 8 \text{ mA}$ ,  $V_{OL} = 0.4 \text{ V}$   $P_{INTmax} = 20 \text{ mA} \times 3.5 \text{ V} = 70 \text{ mW}$   $P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} = 64 \text{ mW}$ This gives:  $P_{INTmax} = 70 \text{ mW}$  and  $P_{IOmax} = 64 \text{ mW}$ :  $P_{Dmax} = 70 + 64 = 134 \text{ mW}$ Thus:  $P_{Dmax} = 134 \text{ mW}$

DocID15060 Rev 7

| Date         | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14-May-2013  | 6        | Replaced VQFN48 package with UQFN48 in cover page packages, <i>Table 2:</i><br><i>STM32F103xx low-density device features and peripheral counts, Figure 6:</i><br><i>STM32F103xx performance line UFQFPN48 pinout, Table 5: Low-density</i><br><i>STM32F103xx pin definitions, Table 58: Ordering information scheme,</i> updated<br><i>Table 9: General operating conditions,</i> updated <i>Table 57: Package thermal</i><br><i>characteristics,</i> added <i>Figure 41: UFQFPN48 7 x 7 mm, 0.5 mm pitch, package</i><br><i>outline</i> and <i>Table 52: UFQFPN48 7 x 7 mm, 0.5 mm pitch, package mechanical</i><br><i>data</i><br>Added footnote for TFBGA ADC channels in <i>Table 2: STM32F103xx low-density</i><br><i>device features and peripheral counts</i><br>Updated 'All GPIOs are high current' in <i>Section 2.3.21: GPIOs (general-purpose</i><br><i>inputs/outputs)</i><br>Updated <i>Table 5: Low-density STM32F103xx pin definitions</i><br>Corrected Sigma letter in <i>Section 5.1.1: Minimum and maximum values</i><br>Updated <i>Table 7: Current characteristics</i><br>Added first sentence in <i>Section 5.3.16: Communications interfaces</i><br>Updated first sentence in <i>Section 5.3.16: Communications interfaces</i><br>Updated first sentence in <i>Output driving current</i><br>Added note 5. in <i>Table 24: HSI oscillator characteristics</i><br>Added notes to <i>Figure 23: Standard I/O input characteristics</i><br>Added notes to <i>Figure 23: Standard I/O input characteristics</i> - CMOS port,<br><i>Figure 24: Standard I/O input characteristics - TL port, Figure 25: 5 V tolerant I/O</i><br><i>input characteristics - CMOS port and Figure 26: 5 V tolerant I/O input</i><br><i>characteristics - TL port</i><br>Updated note 2. and 3,removed note "the device must internally" in <i>Table 40: f<sup>2</sup>C</i><br><i>characteristics</i><br>Updated Figure 29: <i>I<sup>2</sup>C bus AC waveforms and measurement circuit</i><br>Updated note 2. in <i>Table 49: ADC accuracy</i><br>Updated Figure 47: <i>TFBGA64 - 8 x 8 active ball array, 5 x 5 mm, 0.5 mm pitch,</i><br><i>package outline and Table 54: TFBGA64 - 8 x 8 active ball array, 5 x 5 mm, 0.5 mm pitch,</i><br><i>package mechanical data</i> |

| 01-June-2015 | 7        | <ul> <li>Added:</li> <li>Package's marking pictures(<i>Figure 40</i>, <i>Figure 43</i>, <i>Figure 46</i>, <i>Figure 49</i>, <i>Figure 52</i>)</li> <li>Updated:</li> <li>Table 40: I<sup>2</sup>C characteristics</li> <li>Section 6: Package information</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 59. Document revision history (continued)