Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 72MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB           |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT           |

| Number of I/O              | 51                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                |                                                                        |

| RAM Size                   | 6K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                              |

| Data Converters            | A/D 16x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-TFBGA                                                               |

| Supplier Device Package    | 64-TFBGA (5x5)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103r4h6a |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 5 | Electr | rical cha | aracteristics                                          |

|---|--------|-----------|--------------------------------------------------------|

|   | 5.1    | Parame    | ter conditions                                         |

|   |        | 5.1.1     | Minimum and maximum values                             |

|   |        | 5.1.2     | Typical values                                         |

|   |        | 5.1.3     | Typical curves                                         |

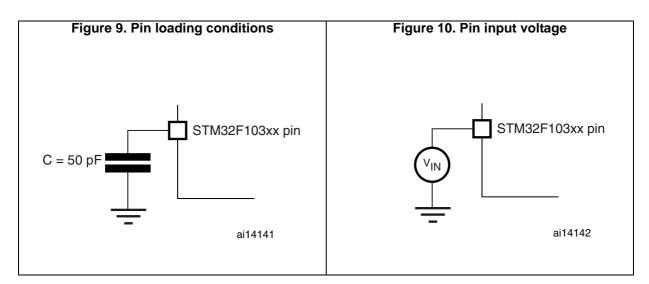

|   |        | 5.1.4     | Loading capacitor                                      |

|   |        | 5.1.5     | Pin input voltage                                      |

|   |        | 5.1.6     | Power supply scheme                                    |

|   |        | 5.1.7     | Current consumption measurement                        |

|   | 5.2    | Absolute  | e maximum ratings                                      |

|   | 5.3    | Operatir  | ng conditions                                          |

|   |        | 5.3.1     | General operating conditions                           |

|   |        | 5.3.2     | Operating conditions at power-up / power-down          |

|   |        | 5.3.3     | Embedded reset and power control block characteristics |

|   |        | 5.3.4     | Embedded reference voltage                             |

|   |        | 5.3.5     | Supply current characteristics                         |

|   |        | 5.3.6     | External clock source characteristics                  |

|   |        | 5.3.7     | Internal clock source characteristics                  |

|   |        | 5.3.8     | PLL characteristics                                    |

|   |        | 5.3.9     | Memory characteristics                                 |

|   |        | 5.3.10    | EMC characteristics                                    |

|   |        | 5.3.11    | Absolute maximum ratings (electrical sensitivity)55    |

|   |        | 5.3.12    | I/O current injection characteristics                  |

|   |        | 5.3.13    | I/O port characteristics                               |

|   |        | 5.3.14    | NRST pin characteristics                               |

|   |        | 5.3.15    | TIM timer characteristics                              |

|   |        | 5.3.16    | Communications interfaces64                            |

|   |        | 5.3.17    | CAN (controller area network) interface                |

|   |        | 5.3.18    | 12-bit ADC characteristics                             |

|   |        | 5.3.19    | Temperature sensor characteristics                     |

| 6 | Packa  | age info  | rmation                                                |

|   | 6.1    | VFQFP     | N36 Package                                            |

|   | 6.2    | UFQFP     | N48 package information                                |

|   | 6.3    |           | package information                                    |

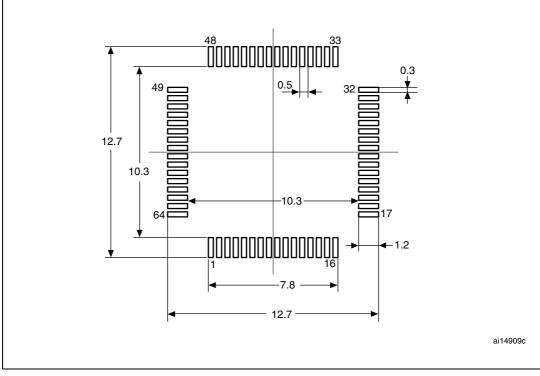

|   | 6.4    | TFBGA     | 64 package information 85                              |

DocID15060 Rev 7

| 8 | Revis | ion hist | ory                                     | 96   |

|---|-------|----------|-----------------------------------------|------|

| 7 | Order | ing info | rmation scheme                          | 95   |

|   |       | 6.6.2    | Selecting the product temperature range | . 93 |

|   |       | 6.6.1    | Reference document                      | . 92 |

|   | 6.6   | Thermal  | characteristics                         | 92   |

|   | 6.5   | LQFP48   | package information                     | 88   |

### 2 Description

The STM32F103x4 and STM32F103x6 performance line family incorporates the highperformance ARM® Cortex<sup>™</sup>-M3 32-bit RISC core operating at a 72 MHz frequency, highspeed embedded memories (Flash memory up to 32 Kbytes and SRAM up to 6 Kbytes), and an extensive range of enhanced I/Os and peripherals connected to two APB buses. All devices offer two 12-bit ADCs, three general purpose 16-bit timers plus one PWM timer, as well as standard and advanced communication interfaces: up to two I<sup>2</sup>Cs and SPIs, three USARTs, an USB and a CAN.

The STM32F103xx low-density performance line family operates from a 2.0 to 3.6 V power supply. It is available in both the -40 to +85 °C temperature range and the -40 to +105 °C extended temperature range. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F103xx low-density performance line family includes devices in four different package types: from 36 pins to 64 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the STM32F103xx low-density performance line microcontroller family suitable for a wide range of applications such as motor drives, application control, medical and handheld equipment, PC and gaming peripherals, GPS platforms, industrial applications, PLCs, inverters, printers, scanners, alarm systems, video intercoms, and HVACs.

### 2.3 Overview

#### 2.3.1 ARM<sup>®</sup> Cortex<sup>™</sup>-M3 core with embedded Flash and SRAM

The ARM<sup>®</sup> Cortex<sup>™</sup>-M3 processor is the latest generation of ARM<sup>®</sup> processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM<sup>®</sup> Cortex<sup>™</sup>-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The STM32F103xx performance line family having an embedded ARM core, is therefore compatible with all ARM tools and software.

*Figure 1* shows the general block diagram of the device family.

#### 2.3.2 Embedded Flash memory

16 or 32 Kbytes of embedded Flash is available for storing programs and data.

#### 2.3.3 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

#### 2.3.4 Embedded SRAM

Six or ten Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

#### 2.3.5 Nested vectored interrupt controller (NVIC)

The STM32F103xx performance line embeds a nested vectored interrupt controller able to handle up to 43 maskable interrupt channels (not including the 16 interrupt lines of Cortex<sup>™</sup>-M3) and 16 priority levels.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of *late arriving* higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

|                     | Pin    | s       |          |                   |                     |                            | •                                                | Alternate functi                                           | ons <sup>(4)</sup>                  |

|---------------------|--------|---------|----------|-------------------|---------------------|----------------------------|--------------------------------------------------|------------------------------------------------------------|-------------------------------------|

| LQFP48/<br>UFQFPN48 | LQFP64 | TFBGA64 | VFQFPN36 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                    | Remap                               |

| 18                  | 26     | F5      | 15       | PB0               | I/O                 | -                          | PB0                                              | ADC12_IN8/TIM3_CH3 <sup>(9)</sup>                          | TIM1_CH2N                           |

| 19                  | 27     | G5      | 16       | PB1               | I/O                 | -                          | PB1                                              | ADC12_IN9/TIM3_CH4 <sup>(9)</sup>                          | TIM1_CH3N                           |

| 20                  | 28     | G6      | 17       | PB2               | I/O                 | FT                         | PB2/BOOT1                                        | -                                                          | -                                   |

| 21                  | 29     | G7      | -        | PB10              | I/O                 | FT                         | PB10                                             | -                                                          | TIM2_CH3                            |

| 22                  | 30     | H7      | -        | PB11              | I/O                 | FT                         | PB11                                             | -                                                          | TIM2_CH4                            |

| 23                  | 31     | D6      | 18       | V <sub>SS_1</sub> | S                   | -                          | V <sub>SS_1</sub>                                | -                                                          | -                                   |

| 24                  | 32     | E6      | 19       | V <sub>DD_1</sub> | S                   | -                          | V <sub>DD_1</sub>                                | -                                                          | -                                   |

| 25                  | 33     | H8      | -        | PB12              | I/O                 | FT                         | PB12                                             | TIM1_BKIN <sup>(9)</sup>                                   | -                                   |

| 26                  | 34     | G8      | -        | PB13              | I/O                 | FT                         | PB13                                             | TIM1_CH1N <sup>(9)</sup>                                   | -                                   |

| 27                  | 35     | F8      | -        | PB14              | I/O                 | FT                         | PB14                                             | TIM1_CH2N <sup>(9)</sup>                                   | -                                   |

| 28                  | 36     | F7      | -        | PB15              | I/O                 | FT                         | PB15                                             | TIM1_CH3N <sup>(9)</sup>                                   | -                                   |

| -                   | 37     | F6      | -        | PC6               | I/O                 | FT                         | PC6                                              | -                                                          | TIM3_CH1                            |

| -                   | 38     | E7      | -        | PC7               | I/O                 | FT                         | PC7                                              | -                                                          | TIM3_CH2                            |

| -                   | 39     | E8      | -        | PC8               | I/O                 | FT                         | PC8                                              | -                                                          | TIM3_CH3                            |

| -                   | 40     | D8      | -        | PC9               | I/O                 | FT                         | PC9                                              | -                                                          | TIM3_CH4                            |

| 29                  | 41     | D7      | 20       | PA8               | I/O                 | FT                         | PA8                                              | USART1_CK/<br>TIM1_CH1/MCO                                 | -                                   |

| 30                  | 42     | C7      | 21       | PA9               | I/O                 | FT                         | PA9                                              | USART1_TX <sup>(9)</sup> /<br>TIM1_CH2 <sup>(9)</sup>      | -                                   |

| 31                  | 43     | C6      | 22       | PA10              | I/O                 | FT                         | PA10                                             | USART1_RX <sup>(9)</sup> / TIM1_CH3                        | -                                   |

| 32                  | 44     | C8      | 23       | PA11              | I/O                 | FT                         | PA11                                             | USART1_CTS/ CAN_RX <sup>(9)</sup> /<br>TIM1_CH4 / USBDM    | -                                   |

| 33                  | 45     | B8      | 24       | PA12              | I/O                 | FT                         | PA12                                             | USART1_RTS/ CAN_TX <sup>(9)</sup><br>/<br>TIM1_ETR / USBDP | -                                   |

| 34                  | 46     | A8      | 25       | PA13              | I/O                 | FT                         | JTMS/SWDIO                                       |                                                            | PA13                                |

| 35                  | 47     | D5      | 26       | V <sub>SS_2</sub> | S                   | -                          | V <sub>SS_2</sub>                                | -                                                          | -                                   |

| 36                  | 48     | E5      | 27       | V <sub>DD_2</sub> | S                   | -                          | V <sub>DD_2</sub>                                | -                                                          | -                                   |

| 37                  | 49     | A7      | 28       | PA14              | I/O                 | FT                         | JTCK/SWCLK                                       | -                                                          | PA14                                |

| 38                  | 50     | A6      | 29       | PA15              | I/O                 | FT                         | JTDI                                             | -                                                          | TIM2_CH1_ETR/<br>PA15 /<br>SPI1_NSS |

| -                   | 51     | B7      | -        | PC10              | I/O                 | FT                         | PC10                                             | -                                                          | -                                   |

| -                   | 52     | B6      | -        | PC11              | I/O                 | FT                         | PC11                                             | -                                                          | -                                   |

| -                   | 53     | C5      | -        | PC12              | I/O                 | FT                         | PC12                                             | -                                                          | -                                   |

| -                   | -      | C1      | 2        | PD0               | I/O                 | FT                         | PD0                                              | -                                                          | -                                   |

Table 5. Low-density STM32F103xx pin definitions (continued)

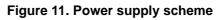

### 5.1.6 Power supply scheme

**Caution:** In *Figure 11*, the 4.7  $\mu$ F capacitor must be connected to V<sub>DD3</sub>.

| Symbol          | Parameter                                                                                           |                      | Min                                                    | Max  | Unit                     |    |

|-----------------|-----------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------|------|--------------------------|----|

|                 |                                                                                                     | Standard             | 1 10                                                   | -0.3 | V <sub>DD</sub> +<br>0.3 |    |

| V <sub>IN</sub> | I/O input voltage                                                                                   | FT 10 <sup>(3)</sup> | $2 \text{ V} < \text{V}_{\text{DD}} \le 3.6 \text{ V}$ | -0.3 | 5.5                      | V  |

|                 |                                                                                                     | FIIO                 | V <sub>DD</sub> = 2 V                                  | -0.3 | 5.2                      |    |

|                 |                                                                                                     | BOOT0                | ·                                                      | 0    | 5.5                      |    |

|                 |                                                                                                     | TFBGA6               | 4                                                      | -    | 308                      |    |

|                 | Power dissipation at $T_A =$<br>85 °C for suffix 6 or $T_A =$<br>105 °C for suffix 7 <sup>(4)</sup> | LQFP64               | LQFP64                                                 |      | 444                      | mW |

| P <sub>D</sub>  |                                                                                                     | LQFP48               | LQFP48                                                 |      | 363                      |    |

|                 |                                                                                                     | UFQFPN               | UFQFPN48                                               |      | 624                      |    |

|                 |                                                                                                     | VFQFPN               | VFQFPN36                                               |      | 1000                     |    |

|                 | Ambient temperature for 6                                                                           | Maximur              | Maximum power dissipation                              |      | 85                       |    |

| т.              | suffix version                                                                                      | Low pow              | Low power dissipation <sup>(5)</sup>                   |      | 105                      |    |

| TA              | Ambient temperature for 7                                                                           | Maximur              | Maximum power dissipation                              |      | 105                      | °C |

|                 | suffix version                                                                                      | Low pow              | Low power dissipation <sup>(5)</sup>                   |      | 125                      |    |

| т.              | lunction towns roture ronge                                                                         | 6 suffix v           | 6 suffix version                                       |      | 105                      |    |

| TJ              | Junction temperature range                                                                          | 7 suffix v           | 7 suffix version                                       |      | 125                      |    |

Table 9. General operating conditions (continued)

1. When the ADC is used, refer to Table 46: ADC characteristics.

2. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and operation.

- 3. To sustain a voltage higher than V<sub>DD</sub>+0.3 V, the internal pull-up/pull-down resistors must be disabled.

- If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see Table 6.6: Thermal characteristics on page 92).

- In low power dissipation state,  $T_A$  can be extended to this range as long as  $T_J$  does not exceed  $T_J$ max (see Table 6.6: Thermal characteristics on page 92). 5.

#### 5.3.2 Operating conditions at power-up / power-down

Subject to general operating conditions for T<sub>A</sub>.

| Table To. Operating conditions at power-up / power-down |                                |            |     |     |       |  |  |  |  |

|---------------------------------------------------------|--------------------------------|------------|-----|-----|-------|--|--|--|--|

| Symbol                                                  | Parameter                      | Conditions | Min | Max | Unit  |  |  |  |  |

| +                                                       | V <sub>DD</sub> rise time rate |            | 0   | ¥   | us/V  |  |  |  |  |

| t <sub>VDD</sub>                                        | V <sub>DD</sub> fall time rate | -          | 20  | ¥   | μ5/ ν |  |  |  |  |

#### Table 10 Operating conditions at power-up / power-down

#### 5.3.3 Embedded reset and power control block characteristics

The parameters given in Table 11 are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 9.

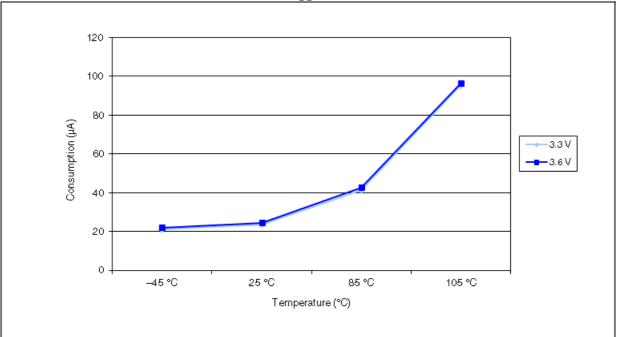

Figure 16. Typical current consumption in Stop mode with regulator in Run mode versus temperature at  $V_{DD}$  = 3.3 V and 3.6 V

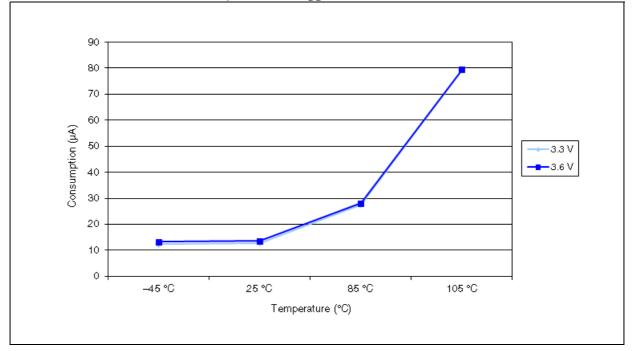

Figure 17. Typical current consumption in Stop mode with regulator in Low-power mode versus temperature at  $V_{DD}$  = 3.3 V and 3.6 V

#### Table 30. EMS characteristics

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                 | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD} = 3.3 \text{ V}, T_A = +25 \text{ °C},$<br>f <sub>HCLK</sub> = 72 MHz<br>conforms to IEC 61000-4-2 | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3 \text{ V}, T_A = +25 \text{ °C},$<br>f <sub>HCLK</sub> = 72 MHz<br>conforms to IEC 61000-4-4 | 4A              |

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                      | Monitored       | Max vs. [f | Unit     |      |

|------------------|------------|-------------------------------------------------|-----------------|------------|----------|------|

|                  | Farameter  |                                                 | frequency band  | 8/48 MHz   | 8/72 MHz | Onit |

| S <sub>EMI</sub> | Peak level | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> = 25 °C | 0.1 to 30 MHz   | 12         | 12       |      |

|                  |            |                                                 | 30 to 130 MHz   | 22         | 19       | dBµV |

|                  |            |                                                 | 130 MHz to 1GHz | 23         | 29       |      |

|                  |            |                                                 | SAE EMI Level   | 4          | 4        | -    |

Table 31. EMI characteristics

#### 5.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of spec current injection on adjacent pins or other functional failure (for example reset, oscillator frequency deviation).

The test results are given in Table 34

|                  |                                                            | Functional s       |                    |      |

|------------------|------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                | Negative injection | Positive injection | Unit |

|                  | Injected current on OSC_IN32,<br>OSC_OUT32, PA4, PA5, PC13 | -0                 | +0                 |      |

| I <sub>INJ</sub> | Injected current on all FT pins                            | -5                 | +0                 | mA   |

|                  | Injected current on any other pin                          | -5                 | +5                 |      |

#### Table 34. I/O current injection susceptibility

#### 5.3.13 I/O port characteristics

#### General input/output characteristics

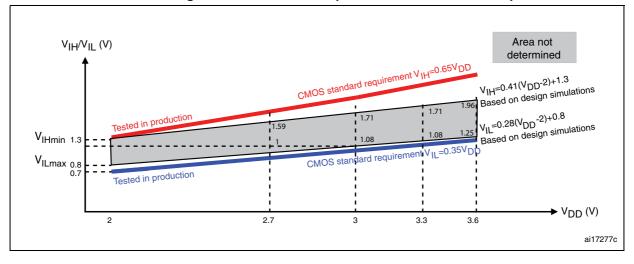

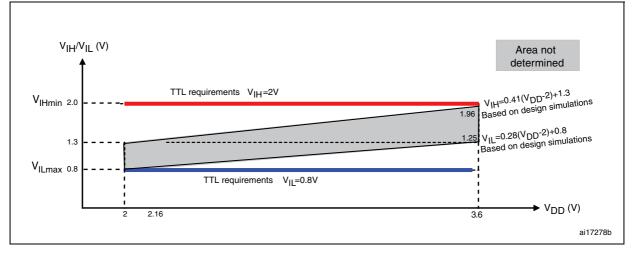

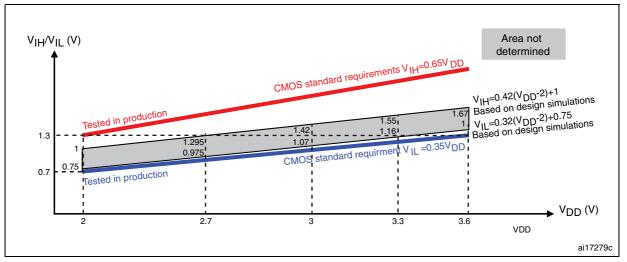

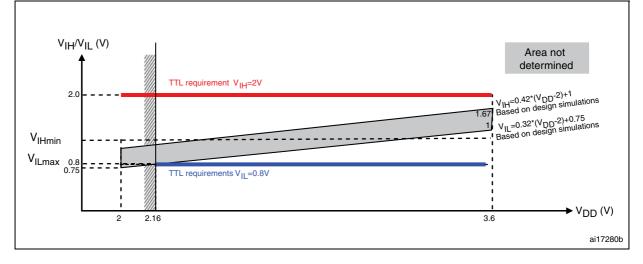

Unless otherwise specified, the parameters given in *Table 35* are derived from tests performed under the conditions summarized in *Table 9*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                                           | Conditions                                          | Min                                              | Тур | Мах                                              | Unit |

|------------------|---------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------|-----|--------------------------------------------------|------|

| VIL              |                                                                     | Standard IO<br>input low level<br>voltage           | -                                                | -   | 0.28*(V <sub>DD</sub> -2 V)+0.8 V <sup>(1)</sup> |      |

|                  | Low level input voltage                                             | IO FT <sup>(3)</sup> input<br>low level voltage     | -                                                | -   | 0.32*(V <sub>DD</sub> -2V)+0.75 V <sup>(1)</sup> |      |

|                  |                                                                     | All I/Os except<br>BOOT0                            | -                                                | -   | 0.35V <sub>DD</sub> <sup>(2)</sup>               |      |

| V <sub>IH</sub>  |                                                                     | Standard IO<br>input high level<br>voltage          | 0.41*(V <sub>DD</sub> -2 V)+1.3 V <sup>(1)</sup> | -   | -                                                | V    |

|                  | High level input<br>voltage                                         | IO FT <sup>(3)</sup> input<br>high level<br>voltage | 0.42*(V <sub>DD</sub> -2 V)+1 V <sup>(1)</sup>   | -   | -                                                |      |

|                  |                                                                     | All I/Os except<br>BOOT0                            | 0.65V <sub>DD</sub> <sup>(2)</sup>               | -   | -                                                |      |

| V <sub>hys</sub> | Standard IO Schmitt<br>trigger voltage<br>hysteresis <sup>(4)</sup> | -                                                   | 200                                              | -   | -                                                | mV   |

| -                | IO FT Schmitt trigger voltage hysteresis <sup>(4)</sup>             | -                                                   | 5% V <sub>DD</sub> <sup>(5)</sup>                | -   | -                                                |      |

| L.               | Input leakage current                                               | $V_{SS} \le V_{IN} \le V_{DD}$<br>Standard I/Os     | -                                                | -   | ±1                                               | μA   |

| l <sub>lkg</sub> | (6)                                                                 | V <sub>IN</sub> = 5 V<br>I/O FT                     | -                                                | -   | 3                                                | μΑ   |

| R <sub>PU</sub>  | Weak pull-up<br>equivalent resistor <sup>(7)</sup>                  | $V_{IN} = V_{SS}$                                   | 30                                               | 40  | 50                                               | kΩ   |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(7)</sup>                   | $V_{IN} = V_{DD}$                                   | 30                                               | 40  | 50                                               | N22  |

| C <sub>IO</sub>  | I/O pin capacitance                                                 | -                                                   | -                                                | 5   | -                                                | pF   |

1. Data based on design simulation.

2. Tested in production.

3. FT = Five-volt tolerant. In order to sustain a voltage higher than  $V_{DD}$ +0.3 the internal pull-up/pull-down resistors must be disabled.

4. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization, not tested in production.

5. With a minimum of 100 mV.

6. Leakage could be higher than max. if negative current is injected on adjacent pins.

7. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimum (~10% order).

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 23* and *Figure 24* for standard I/Os, and in *Figure 25* and *Figure 26* for 5 V tolerant I/Os.

Figure 23. Standard I/O input characteristics - CMOS port

Figure 25. 5 V tolerant I/O input characteristics - CMOS port

Figure 26. 5 V tolerant I/O input characteristics - TTL port

#### **SPI** interface characteristics

Unless otherwise specified, the parameters given in *Table 42* are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

Refer to Section 5.3.12: I/O current injection characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                            | Parameter                           | Conditions                                            | Min                | Max                | Unit |

|-------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------|--------------------|--------------------|------|

| f <sub>SCK</sub>                                                  |                                     | Master mode                                           | -                  | 18                 |      |

| 1/t <sub>c(SCK)</sub>                                             | SPI clock frequency                 | Slave mode                                            | -                  | 18                 | MHz  |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>                        | SPI clock rise and fall time        | Capacitive load: C = 30 pF                            |                    | 8                  | ns   |

| DuCy(SCK)                                                         | SPI slave input clock<br>duty cycle | Slave mode                                            | 30                 | 70                 | %    |

| t <sub>su(NSS)</sub> <sup>(1)</sup>                               | NSS setup time                      | Slave mode                                            | 4t <sub>PCLK</sub> | -                  |      |

| t <sub>h(NSS)</sub> <sup>(1)</sup>                                | NSS hold time                       | Slave mode                                            | 2t <sub>PCLK</sub> | -                  |      |

| $\begin{array}{c}t_{w(SCKH)}^{(1)}\\t_{w(SCKL)}^{(1)}\end{array}$ | SCK high and low time               | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | 50                 | 60                 | *    |

|                                                                   | Data input setup time               | Master mode                                           | 5                  | -                  |      |

| t <sub>su(MI)</sub> (1)<br>t <sub>su(SI)</sub> (1)                |                                     | Slave mode                                            | 5                  | -                  |      |

| t <sub>h(MI)</sub> <sup>(1)</sup>                                 | Data input hold time                | Master mode                                           | 5                  | -                  |      |

| t <sub>h(SI)</sub> <sup>(1)</sup>                                 | Data input noid time                | Slave mode                                            | 4                  | -                  | ns   |

| t <sub>a(SO)</sub> <sup>(1)(2)</sup>                              | Data output access time             | Slave mode, f <sub>PCLK</sub> = 20 MHz                | 0                  | 3t <sub>PCLK</sub> |      |

| t <sub>dis(SO)</sub> <sup>(1)(3)</sup>                            | Data output disable<br>time         | Slave mode                                            | 2                  | 10                 | *    |

| t <sub>v(SO)</sub> <sup>(1)</sup>                                 | Data output valid time              | Slave mode (after enable edge)                        | -                  | 25                 |      |

| t <sub>v(MO)</sub> <sup>(1)</sup>                                 | Data output valid time              | Master mode (after enable edge)                       | -                  | 5                  |      |

| t <sub>h(SO)</sub> <sup>(1)</sup>                                 | Data output hold time               | Slave mode (after enable edge)                        | 15                 | -                  |      |

| t <sub>h(MO)</sub> <sup>(1)</sup>                                 |                                     | Master mode (after enable edge)                       | 2                  | -                  |      |

| Table 42. | SPI | characteristics |

|-----------|-----|-----------------|

|-----------|-----|-----------------|

1. Based on characterization, not tested in production.

2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z

### Equation 1: $R_{AIN} \max_{T}$ formula:

$$R_{AIN} < \frac{r_{S}}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

| T <sub>s</sub> (cycles) | t <sub>S</sub> (μs) | R <sub>AIN</sub> max (kΩ) |

|-------------------------|---------------------|---------------------------|

| 1.5                     | 0.11                | 0.4                       |

| 7.5                     | 0.54                | 5.9                       |

| 13.5                    | 0.96                | 11.4                      |

| 28.5                    | 2.04                | 25.2                      |

| 41.5                    | 2.96                | 37.2                      |

| 55.5                    | 3.96                | 50                        |

| 71.5                    | 5.11                | NA                        |

| 239.5                   | 17.1                | NA                        |

1. Based on characterization, not tested in production.

| Table 40. Abo accuracy - initial test conditions |                              |                                                    |      |                    |      |

|--------------------------------------------------|------------------------------|----------------------------------------------------|------|--------------------|------|

| Symbol                                           | Parameter                    | Test conditions                                    | Тур  | Max <sup>(3)</sup> | Unit |

| ET                                               | Total unadjusted error       | f <sub>PCLK2</sub> = 56 MHz,                       | ±1.3 | ±2                 |      |

| EO                                               | Offset error                 | $f_{ADC}$ = 14 MHz, $R_{AIN}$ < 10 kΩ,             | ±1   | ±1.5               |      |

| EG                                               | Gain error                   | $V_{DDA} = 3 V$ to 3.6 V<br>T <sub>A</sub> = 25 °C | ±0.5 | ±1.5               | LSB  |

| ED                                               | Differential linearity error | Measurements made after                            | ±0.7 | ±1                 |      |

| EL                                               | Integral linearity error     | ADC calibration                                    | ±0.8 | ±1.5               |      |

| Table 48. ADC accuracy - limited test conditions <sup>(1) (2)</sup> |

|---------------------------------------------------------------------|

|---------------------------------------------------------------------|

1. ADC DC accuracy values are measured after internal calibration.

2. ADC Accuracy vs. Negative Injection Current: Injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 5.3.12 does not affect the ADC accuracy.

3. Based on characterization, not tested in production.

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Max   | Min                   | Тур    | Max    |

| E3     | -           | 7.500 | -     | -                     | 0.2953 | -      |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| К      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |

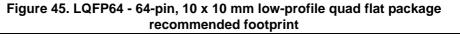

# Table 53. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flatpackage mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

#### 1. Dimensions are expressed in millimeters.

# Table 54. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ballgrid array package mechanical data (continued)

| Symbol | millimeters |       | inches <sup>(1)</sup> |     |        |        |

|--------|-------------|-------|-----------------------|-----|--------|--------|

| Symbol | Min         | Тур   | Max                   | Min | Тур    | Мах    |

| е      | -           | 0.500 | -                     | -   | 0.0197 | -      |

| F      | -           | 0.750 | -                     | -   | 0.0295 | -      |

| ddd    | -           | -     | 0.080                 | -   | -      | 0.0031 |

| eee    | -           | -     | 0.150                 | -   | -      | 0.0059 |

| fff    | -           | -     | 0.050                 | -   | -      | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

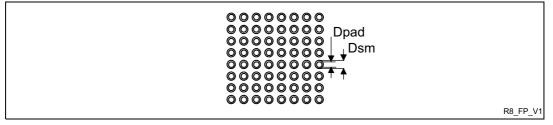

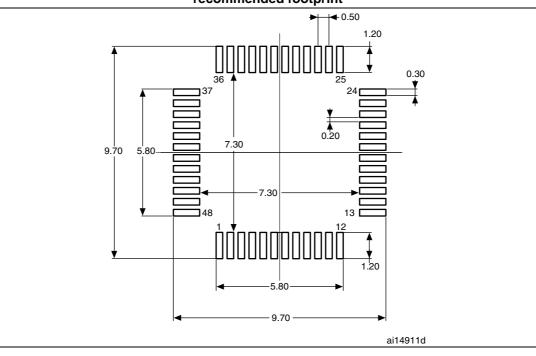

# Figure 48. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball grid array, recommended footprint

#### Table 55. TFBGA64 recommended PCB design rules (0.5 mm pitch BGA)

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.5                                                              |

| Dpad              | 0.280 mm                                                         |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.280 mm                                                         |

| Stencil thickness | Between 0.100 mm and 1.125 mm                                    |

| Pad trace width   | 0.100 mm                                                         |

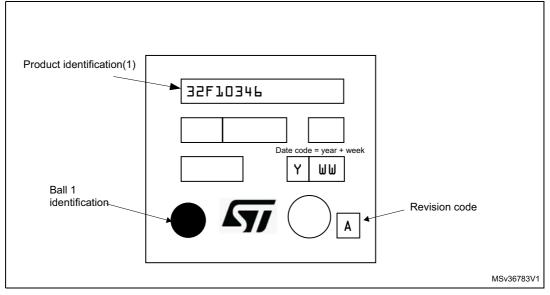

#### **Device Marking for TFBGA64**

The following figure gives an example of topside marking orientation versus ball 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# Figure 51. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

## 8 Revision history

| Data        | Table 59. Document revision history |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|-------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Date        | Revision                            | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 22-Sep-2008 | 1                                   | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 30-Mar-2009 | 2                                   | <ul> <li>"96-bit unique ID" feature added and I/O information clarified on page 1.</li> <li>Timers specified on page 1 (Motor control capability mentioned).</li> <li>Table 4: Timer feature comparison added.</li> <li>PB4, PB13, PB14, PB15, PB3/TRACESWO moved from Default column to Remap column, plus small additional changes in Table 5: Low-density STM32F103xx pin definitions.</li> <li>Figure 8: Memory map modified.</li> <li>References to V<sub>REF</sub>. removed: <ul> <li>Figure 1: STM32F103xx performance line block diagram modified,</li> <li>Figure 34: ADC accuracy characteristics modified</li> <li>Note modified in Table 49: ADC accuracy.</li> </ul> </li> <li>Table 20: High-speed external user clock characteristics and Table 21: Low-speed external user clock characteristics modified.</li> <li>Note modified in Table 13: Maximum current consumption in Run mode, code with data processing running from Flash and Table 15: Maximum current consumption in Sleep mode, code running from Flash or RAM.</li> <li>Figure 17 shows a typical curve (title modified). ACC<sub>HSI</sub> max values modified in Table 24: HSI oscillator characteristics.</li> <li>TFBGA64 package added (see Table 54 and Table 47).</li> </ul>                                                                                                                                                   |  |

| 24-Sep-2009 | 3                                   | Note 5 updated and Note 4 added in Table 5: Low-density STM32F103xx pin definitions.<br>$V_{RERINT}$ and $T_{Coeff}$ added to Table 12: Embedded internal reference voltage.<br>Typical I <sub>DD_VBAT</sub> value added in Table 16: Typical and maximum current<br>consumptions in Stop and Standby modes. Figure 15: Typical current consumption<br>on $V_{BAT}$ with RTC on versus temperature at different $V_{BAT}$ values added.<br>$f_{HSE_{ext}}$ min modified in Table 20: High-speed external user clock characteristics.<br>$C_{L1}$ and $C_{L2}$ replaced by C in Table 22: HSE 4-16 MHz oscillator characteristics<br>and Table 23: LSE oscillator characteristics ( $f_{LSE} = 32.768$ kHz), notes modified<br>and moved below the tables. Table 24: HSI oscillator characteristics modified.<br>Conditions removed from Table 26: Low-power mode wakeup timings.<br>Note 1 modified below Figure 21: Typical application with an 8 MHz crystal.<br>Figure 28: Recommended NRST pin protection modified.<br>Jitter added to Table 27: PLL characteristics on page 52.<br>IEC 1000 standard updated to IEC 61000 and SAE J1752/3 updated to IEC 61967-2 in Section 5.3.10: EMC characteristics on page 53.<br>$C_{ADC}$ and $R_{AIN}$ parameters modified in Table 46: ADC characteristics. $R_{AIN}$ max<br>values modified in Table 47: $R_{AIN}$ max for $f_{ADC} = 14$ MHz.<br>Small text changes. |  |

#### Table 59. Document revision history