Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 72MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB             |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT             |

| Number of I/O              | 51                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 10K × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103r6t6atr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 44.<br>Table 45. | USB DC electrical characteristics                                         |

|------------------------|---------------------------------------------------------------------------|

| Table 46.              | ADC characteristics                                                       |

| Table 47.              | $R_{AIN}$ max for $f_{ADC} = 14$ MHz                                      |

| Table 48.              | ADC accuracy - limited test conditions                                    |

| Table 49.              | ADC accuracy                                                              |

| Table 50.              | TS characteristics                                                        |

| Table 51.              | VFQFPN36 - 36-pin, 6x6 mm, 0.5 mm pitch very thin profile fine pitch      |

|                        | quad flat package mechanical data                                         |

| Table 52.              | UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |

|                        | package mechanical data                                                   |

| Table 53.              | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat                         |

|                        | package mechanical data                                                   |

| Table 54.              | TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball   |

|                        | grid array package mechanical data85                                      |

| Table 55.              | TFBGA64 recommended PCB design rules (0.5 mm pitch BGA)                   |

| Table 56.              | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                   |

|                        | mechanical data                                                           |

| Table 57.              | Package thermal characteristics                                           |

| Table 58.              | Ordering information scheme                                               |

| Table 59.              | Document revision history                                                 |

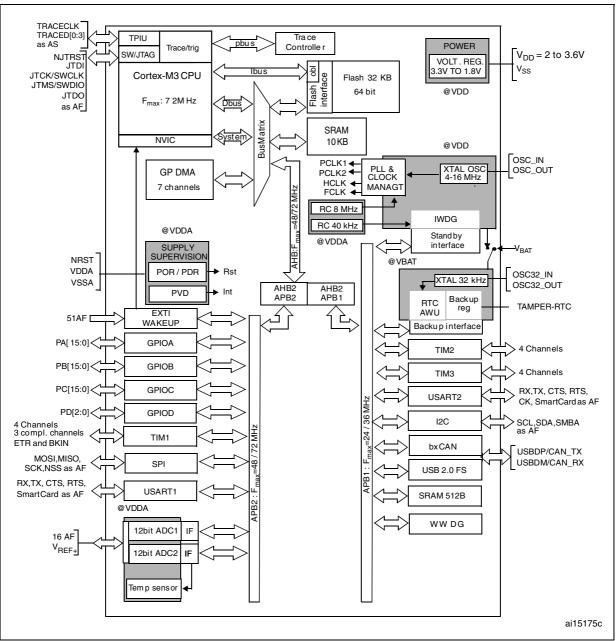

Figure 1. STM32F103xx performance line block diagram

1.  $T_A = -40$  °C to +105 °C (junction temperature up to 125 °C).

2. AF = alternate function on I/O port pin.

#### STM32F103x4, STM32F103x6

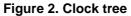

- 1. When the HSI is used as a PLL clock input, the maximum system clock frequency that can be achieved is 64 MHz.

- 2. For the USB function to be available, both HSE and PLL must be enabled, with USBCLK running at 48 MHz.

- 3. To have an ADC conversion time of 1  $\mu s,$  APB2 must be at 14 MHz, 28 MHz or 56 MHz.

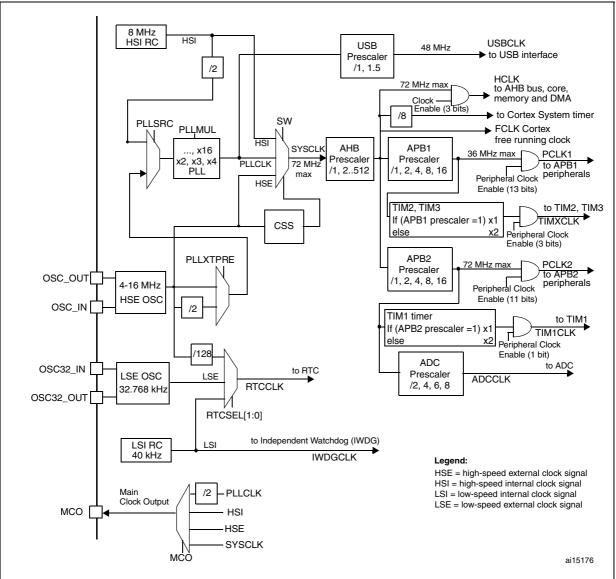

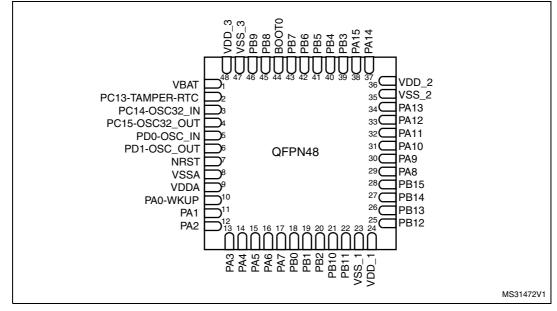

Figure 5. STM32F103xx performance line LQFP48 pinout

Figure 6. STM32F103xx performance line UFQFPN48 pinout

|                     | Pin    | IS      |          | able 5. Low-dell  |                     |                            |                                                  | Alternate functions <sup>(4)</sup> |                                |  |

|---------------------|--------|---------|----------|-------------------|---------------------|----------------------------|--------------------------------------------------|------------------------------------|--------------------------------|--|

| LQFP48/<br>UFQFPN48 | LQFP64 | TFBGA64 | VFQFPN36 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                            | Remap                          |  |

| -                   | -      | D1      | 3        | PD1               | I/O                 | FT                         | PD1                                              | -                                  | -                              |  |

| -                   | 54     | B5      | -        | PD2               | I/O                 | FT                         | PD2                                              | TIM3_ETR                           | -                              |  |

| 39                  | 55     | A5      | 30       | PB3               | I/O                 | FT                         | JTDO                                             | -                                  | TIM2_CH2 /<br>PB3/<br>TRACESWO |  |

| 40                  | 56     | A4      | 31       | PB4               | I/O                 | FT                         | NJTRST                                           | -                                  | TIM3_CH1 /PB4<br>SPI1_MISO     |  |

| 41                  | 57     | C4      | 32       | PB5               | I/O                 | -                          | PB5                                              | I2C1_SMBA                          | TIM3_CH2 /<br>SPI1_MOSI        |  |

| 42                  | 58     | D3      | 33       | PB6               | I/O                 | FT                         | PB6                                              | I2C1_SCL <sup>(9)</sup> /          | USART1_TX                      |  |

| 43                  | 59     | C3      | 34       | PB7               | I/O                 | FT                         | PB7                                              | I2C1_SDA <sup>(9)</sup>            | USART1_RX                      |  |

| 44                  | 60     | B4      | 35       | BOOT0             | Ι                   | -                          | BOOT0                                            | -                                  | -                              |  |

| 45                  | 61     | B3      | -        | PB8               | I/O                 | FT                         | PB8                                              | -                                  | I2C1_SCL<br>/CAN_RX            |  |

| 46                  | 62     | A3      | -        | PB9               | I/O                 | FT                         | PB9                                              | -                                  | I2C1_SDA /<br>CAN_TX           |  |

| 47                  | 63     | D4      | 36       | V <sub>SS_3</sub> | S                   | -                          | $V_{SS_3}$                                       | -                                  | -                              |  |

| 48                  | 64     | E4      | 1        | $V_{DD_3}$        | S                   | -                          | $V_{DD_3}$                                       | -                                  | -                              |  |

Table 5. Low-density STM32F103xx pin definitions (continued)

1. I = input, O = output, S = supply.

2. FT = 5 V tolerant.

Function availability depends on the chosen device. For devices having reduced peripheral counts, it is always the lower number of peripheral that is included. For example, if a device has only one SPI and two USARTs, they will be called SPI1 and USART1 & USART2, respectively. Refer to *Table 2 on page 11*.

4. If several peripherals share the same I/O pin, to avoid conflict between these alternate functions only one peripheral should be enabled at a time through the peripheral clock enable bit (in the corresponding RCC peripheral clock enable register).

- PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited: the speed should not exceed 2 MHz with a maximum load of 30 pF and these IOs must not be used as a current source (e.g. to drive an LED).

- 6. Main function after the first backup domain power-up. Later on, it depends on the contents of the Backup registers even after reset (because these registers are not reset by the main reset). For details on how to manage these IOs, refer to the Battery backup domain and BKP register description sections in the STM32F10xxx reference manual, available from the STMicroelectronics website: www.st.com.

- 7. The pins number 2 and 3 in the VFQFPN36 package, 5 and 6 in the LQFP48, UFQFPN48 and LQFP64 packages and C1 and C2 in the TFBGA64 package are configured as OSC\_IN/OSC\_OUT after reset, however the functionality of PD0 and PD1 can be remapped by software on these pins. For more details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual.

8. Unlike in the LQFP64 package, there is no PC3 in the TFBGA64 package. The V<sub>REF+</sub> functionality is provided instead.

This alternate function can be remapped by software to some other port pins (if available on the used package). For more

details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual,

available from the STMicroelectronics website: www.st.com.

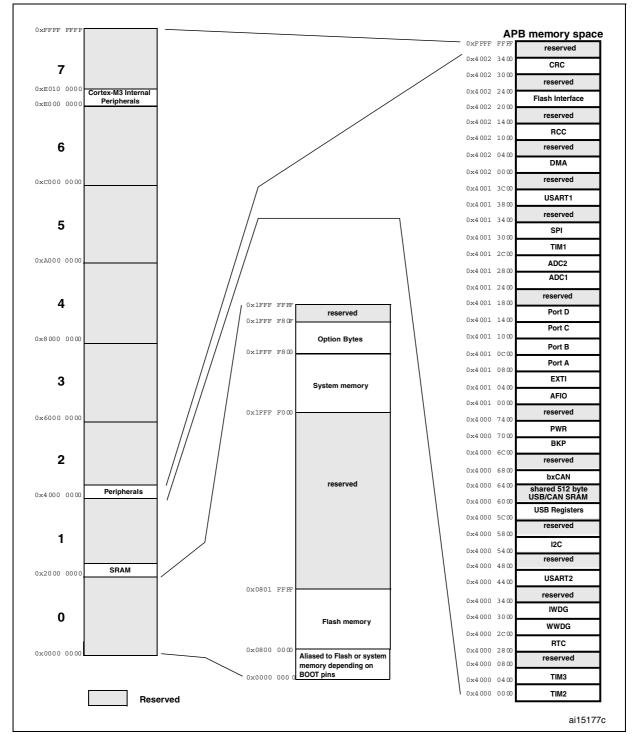

## 4 Memory mapping

The memory map is shown in Figure 8.

Figure 8. Memory map

DocID15060 Rev 7

| Symbol                               | Ratings                                                                 | Max.  | Unit |

|--------------------------------------|-------------------------------------------------------------------------|-------|------|

| I <sub>VDD</sub>                     | Total current into $V_{DD}/V_{DDA}$ power lines (source) <sup>(1)</sup> | 150   |      |

| I <sub>VSS</sub>                     | Total current out of $V_{SS}$ ground lines (sink) <sup>(1)</sup>        | 150   |      |

| 1                                    | Output current sunk by any I/O and control pin                          | 25    |      |

| IIO                                  | Output current source by any I/Os and control pin                       | -25   | mA   |

| ı (2)                                | Injected current on five volt tolerant pins <sup>(3)</sup>              | -5/+0 |      |

| I <sub>INJ(PIN)</sub> <sup>(2)</sup> | Injected current on any other pin <sup>(4)</sup>                        | ± 5   |      |

| $\Sigma I_{INJ(PIN)}$                | Total injected current (sum of all I/O and control pins) <sup>(5)</sup> | ± 25  |      |

#### Table 7. Current characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. Negative injection disturbs the analog performance of the device. See note 2. on page 71.

Positive injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 6: Voltage characteristics* for the maximum allowed input voltage values.

A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 6: Voltage characteristics* for the maximum allowed input voltage values.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

## 5.3 Operating conditions

#### 5.3.1 General operating conditions

#### Table 9. General operating conditions

| Symbol                          | Parameter                                  | Conditions                        | Min | Max | Unit |

|---------------------------------|--------------------------------------------|-----------------------------------|-----|-----|------|

| f <sub>HCLK</sub>               | Internal AHB clock frequency               | -                                 | 0   | 72  |      |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency              | -                                 | 0   | 36  | MHz  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency              | -                                 | 0   | 72  |      |

| V <sub>DD</sub>                 | Standard operating voltage                 | -                                 | 2   | 3.6 |      |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage<br>(ADC not used) | Must be the same potential        | 2   | 3.6 | V    |

| ⊻DDA` ′                         | Analog operating voltage<br>(ADC used)     | as V <sub>DD</sub> <sup>(2)</sup> | 2.4 | 3.6 | V    |

| V <sub>BAT</sub>                | Backup operating voltage                   | -                                 | 1.8 | 3.6 |      |

| Symbol          | Parameter                                                           |                                                    | Min                                                    | Max  | Unit                     |    |

|-----------------|---------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------|------|--------------------------|----|

|                 |                                                                     | Standard                                           | 1 10                                                   | -0.3 | V <sub>DD</sub> +<br>0.3 |    |

| V <sub>IN</sub> | I/O input voltage                                                   | FT 10 <sup>(3)</sup>                               | $2 \text{ V} < \text{V}_{\text{DD}} \le 3.6 \text{ V}$ | -0.3 | 5.5                      | V  |

|                 |                                                                     | FIIO                                               | V <sub>DD</sub> = 2 V                                  | -0.3 | 5.2                      |    |

|                 |                                                                     | BOOT0                                              | ·                                                      | 0    | 5.5                      |    |

|                 |                                                                     | TFBGA6                                             | 4                                                      | -    | 308                      |    |

|                 | Power dissipation at $T_A =$                                        | LQFP64                                             | LQFP64                                                 |      | 444                      | mW |

| P <sub>D</sub>  | 85 °C for suffix 6 or $T_A =$<br>105 °C for suffix 7 <sup>(4)</sup> | LQFP48                                             | LQFP48                                                 |      | 363                      |    |

|                 |                                                                     | UFQFPN                                             | UFQFPN48                                               |      | 624                      |    |

|                 |                                                                     | VFQFPN                                             | VFQFPN36                                               |      | 1000                     |    |

|                 | Ambient temperature for 6                                           | hbient temperature for 6 Maximum power dissipation |                                                        | -40  | 85                       |    |

| т.              | suffix version                                                      | Low pow                                            | Low power dissipation <sup>(5)</sup>                   |      | 105                      |    |

| TA              | Ambient temperature for 7                                           | Maximum power dissipation                          |                                                        | -40  | 105                      | °C |

|                 | suffix version                                                      | Low pow                                            | Low power dissipation <sup>(5)</sup>                   |      | 125                      |    |

| т.              | lunction towns roture ronge                                         | 6 suffix v                                         | 6 suffix version                                       |      | 105                      |    |

| TJ              | Junction temperature range                                          | 7 suffix v                                         | 7 suffix version                                       |      | 125                      |    |

Table 9. General operating conditions (continued)

1. When the ADC is used, refer to Table 46: ADC characteristics.

2. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and operation.

- 3. To sustain a voltage higher than V<sub>DD</sub>+0.3 V, the internal pull-up/pull-down resistors must be disabled.

- If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see Table 6.6: Thermal characteristics on page 92).

- In low power dissipation state,  $T_A$  can be extended to this range as long as  $T_J$  does not exceed  $T_J$ max (see Table 6.6: Thermal characteristics on page 92). 5.

#### 5.3.2 Operating conditions at power-up / power-down

Subject to general operating conditions for T<sub>A</sub>.

|                  | Table TU. Operating            | conditions at power- | up / power | -down |       |

|------------------|--------------------------------|----------------------|------------|-------|-------|

| Symbol           | Parameter                      | Conditions           | Min        | Max   | Unit  |

| +                | V <sub>DD</sub> rise time rate |                      | 0          | ¥     | us/V  |

| t <sub>VDD</sub> | V <sub>DD</sub> fall time rate | -                    | 20         | ¥     | μ5/ ν |

#### Table 10 Operating conditions at power-up / power-down

#### 5.3.3 Embedded reset and power control block characteristics

The parameters given in Table 11 are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 9.

| Cumhal          | Devementer                      | Conditions                          | 4      | Max                    | l Imit                  |      |  |

|-----------------|---------------------------------|-------------------------------------|--------|------------------------|-------------------------|------|--|

| Symbol          | Parameter                       | Conditions                          | fHCLK  | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |  |

|                 |                                 |                                     | 72 MHz | 26                     | 27                      |      |  |

|                 |                                 |                                     | 48 MHz | 17                     | 18                      |      |  |

|                 |                                 | External clock <sup>(2)</sup> , all | 36 MHz | 14                     | 15                      |      |  |

| I <sub>DD</sub> | Supply current in<br>Sleep mode | peripherals enabled                 | 24 MHz | 10                     | 11                      |      |  |

|                 |                                 |                                     | 16 MHz | 7                      | 8                       |      |  |

|                 |                                 |                                     | 8 MHz  | 4                      | 5                       | ~ ^  |  |

|                 |                                 | External clock <sup>(2)</sup> , all | 72 MHz | 7.5                    | 8                       | mA   |  |

|                 |                                 |                                     | 48 MHz | 6                      | 6.5                     |      |  |

|                 |                                 |                                     | 36 MHz | 5                      | 5.5                     |      |  |

|                 |                                 | peripherals disabled                | 24 MHz | 4.5                    | 5                       |      |  |

|                 |                                 |                                     | 16 MHz | 4                      | 4.5                     |      |  |

| 1               |                                 |                                     | 8 MHz  | 3                      | 4                       |      |  |

## Table 15. Maximum current consumption in Sleep mode, code running from Flash or RAM

1. based on characterization, tested in production at  $V_{\text{DD}\ \text{max}},\,f_{\text{HCLK}}$  max with peripherals enabled.

2. External clock is 8 MHz and PLL is on when  $f_{\text{HCLK}}$  > 8 MHz.

|                 |                                  |                                   |                   | Ту                                        | p <sup>(1)</sup>            | Unit |

|-----------------|----------------------------------|-----------------------------------|-------------------|-------------------------------------------|-----------------------------|------|

| Symbol          | Parameter                        | Conditions                        | f <sub>HCLK</sub> | All peripherals<br>enabled <sup>(2)</sup> | All peripherals<br>disabled |      |

|                 |                                  |                                   | 72 MHz            | 31.3                                      | 24.5                        |      |

|                 |                                  |                                   | 48 MHz            | 21.9                                      | 17.4                        |      |

|                 |                                  |                                   | 36 MHz            | 17.2                                      | 13.8                        |      |

|                 |                                  |                                   | 24 MHz            | 11.2                                      | 8.9                         |      |

|                 |                                  |                                   | 16 MHz            | 8.1                                       | 6.6                         |      |

|                 |                                  | External clock <sup>(3)</sup>     | 8 MHz             | 5                                         | 4.2                         | mA   |

|                 | Supply<br>current in<br>Run mode |                                   | 4 MHz             | 3                                         | 2.6                         |      |

|                 |                                  |                                   | 2 MHz             | 2                                         | 1.8                         |      |

|                 |                                  |                                   | 1 MHz             | 1.5                                       | 1.4                         |      |

|                 |                                  |                                   | 500 kHz           | 1.2                                       | 1.2                         |      |

| I <sub>DD</sub> |                                  |                                   | 125 kHz           | 1.05                                      | 1                           |      |

|                 |                                  | Running on high speed internal RC | 64 MHz            | 27.6                                      | 21.6                        |      |

|                 |                                  |                                   | 48 MHz            | 21.2                                      | 16.7                        |      |

|                 |                                  |                                   | 36 MHz            | 16.5                                      | 13.1                        |      |

|                 |                                  |                                   | 24 MHz            | 10.5                                      | 8.2                         |      |

|                 | 1                                |                                   | 16 MHz            | 7.4                                       | 5.9                         |      |

|                 |                                  | (HSI), AHB<br>prescaler used to   | 8 MHz             | 4.3                                       | 3.6                         | mA   |

|                 |                                  | reduce the                        | 4 MHz             | 2.4                                       | 2                           |      |

|                 |                                  | frequency                         | 2 MHz             | 1.5                                       | 1.3                         |      |

|                 |                                  |                                   | 1 MHz             | 1                                         | 0.9                         |      |

|                 |                                  |                                   | 500 kHz           | 0.7                                       | 0.65                        |      |

|                 |                                  |                                   | 125 kHz           | 0.5                                       | 0.45                        |      |

| Table 17. Typical current consumption in Run mode, code with data processing |

|------------------------------------------------------------------------------|

| running from Flash                                                           |

1. Typical values are measures at  $T_{A}$  = 25 °C,  $V_{DD}$  = 3.3 V.

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

### 5.3.6 External clock source characteristics

#### High-speed external user clock generated from an external source

The characteristics given in *Table 20* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 9*.

| Symbol                                     | Parameter                                           | Conditions                                        | Min                | Тур | Мах                | Unit |

|--------------------------------------------|-----------------------------------------------------|---------------------------------------------------|--------------------|-----|--------------------|------|

| f <sub>HSE_ext</sub>                       | User external clock source frequency <sup>(1)</sup> |                                                   | 1                  | 8   | 25                 | MHz  |

| V <sub>HSEH</sub>                          | OSC_IN input pin high level voltage                 |                                                   | 0.7V <sub>DD</sub> | -   | V <sub>DD</sub>    | V    |

| V <sub>HSEL</sub>                          | OSC_IN input pin low level voltage                  |                                                   | V <sub>SS</sub>    | -   | 0.3V <sub>DD</sub> | v    |

| t <sub>w(HSE)</sub><br>t <sub>w(HSE)</sub> | OSC_IN high or low time <sup>(1)</sup>              | -                                                 | 5                  | -   | -                  | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | OSC_IN rise or fall time <sup>(1)</sup>             |                                                   | -                  | -   | 20                 | 115  |

| C <sub>in(HSE)</sub>                       | OSC_IN input capacitance <sup>(1)</sup>             | -                                                 | -                  | 5   | -                  | pF   |

| DuCy <sub>(HSE)</sub>                      | Duty cycle                                          | -                                                 | 45                 | -   | 55                 | %    |

| ١L                                         | OSC_IN Input leakage current                        | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub> | -                  | -   | ±1                 | μA   |

Table 20. High-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

### Low-speed external user clock generated from an external source

The characteristics given in *Table 21* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 9*.

| Symbol                                     | Parameter                                           | Conditions                       | Min                | Тур    | Max                | Unit |

|--------------------------------------------|-----------------------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source frequency <sup>(1)</sup> |                                  | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage               |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSE)</sub><br>t <sub>w(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>            |                                  | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>           |                                  | -                  | -      | 50                 | 115  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>           | -                                | -                  | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                          | -                                | 30                 | -      | 70                 | %    |

| ١L                                         | OSC32_IN Input leakage current                      | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

Table 21. Low-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

#### **Output driving current**

The GPIOs (general-purpose inputs/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed V<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14 and PC15 which can sink or source up to  $\pm /-3$ mA. When using the GPIOs PC13 to PC15 in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 5.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD</sub> (see *Table 7*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS</sub> (see *Table 7*).

#### Output voltage levels

Unless otherwise specified, the parameters given in *Table 36* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*. All I/Os are CMOS and TTL compliant.

| Symbol                            | Parameter                                                                                                                            | Conditions                                                 | Min                  | Max | Unit |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(1)</sup>    | Output low level voltage for an I/O pin when 8 pins are sunk at same time                                                            | CMOS port <sup>(2)</sup> ,<br>I <sub>IO</sub> = +8 mA      | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin when 8 pins are sourced at same time                                                        | $1_{O} = 40 \text{ mg}$<br>2.7 V < V <sub>DD</sub> < 3.6 V | V <sub>DD</sub> 0.4  | -   | v    |

| V <sub>OL</sub> <sup>(1)</sup>    | Output low level voltage for an I/O pin<br>when 8 pins are sunk at same time                                                         |                                                            | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin when 8 pins are sourced at same time                                                        |                                                            |                      | -   | v    |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time                                                            | l <sub>IO</sub> = +20 mA                                   | -                    | 1.3 | V    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time $2.7 \text{ V} < \text{V}_{\text{DD}} < 3.6 \text{ V}$ |                                                            | V <sub>DD</sub> -1.3 | -   | v    |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Dutput low level voltage for an I/O pin<br>when 8 pins are sunk at same time $I_{IO} = +6 \text{ mA}$                                |                                                            | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time                                                        | 2 V < V <sub>DD</sub> < 2.7 V                              | V <sub>DD</sub> 0.4  | -   | v    |

#### Table 36. Output voltage characteristics

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 7* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 7 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Based on characterization data, not tested in production.

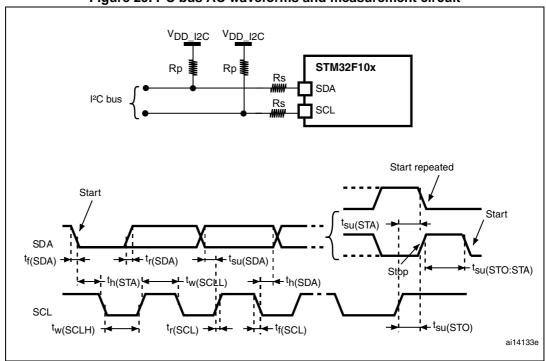

### 5.3.16 Communications interfaces

### I<sup>2</sup>C interface characteristics

The STM32F103xx performance line  $I^2C$  interface meets the requirements of the standard  $I^2C$  communication protocol with the following restrictions: the I/O pins SDA and SCL are mapped to are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 40*. Refer also to *Section 5.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol                                     | Parameter                               | Standard mode<br>I <sup>2</sup> C <sup>(1)(2)</sup> |                     | Fast mode I <sup>2</sup> C <sup>(1)(2)</sup> |                    | Unit |

|--------------------------------------------|-----------------------------------------|-----------------------------------------------------|---------------------|----------------------------------------------|--------------------|------|

|                                            |                                         | Min                                                 | Max                 | Min                                          | Max                |      |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7                                                 | -                   | 1.3                                          | -                  |      |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0                                                 | -                   | 0.6                                          | -                  | μs   |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250                                                 | -                   | 100                                          | -                  |      |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | -                                                   | 3450 <sup>(3)</sup> | -                                            | 900 <sup>(3)</sup> |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   | -                                                   | 1000                | -                                            | 300                | ns   |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   | -                                                   | 300                 | -                                            | 300                |      |

| t <sub>h(STA)</sub>                        | Start condition hold time               | 4.0                                                 | -                   | 0.6                                          | -                  |      |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time     | 4.7                                                 | -                   | 0.6                                          | -                  | μs   |

| t <sub>su(STO)</sub>                       | Stop condition setup time 4.0 - 0.6     |                                                     | -                   | μs                                           |                    |      |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free) | 4.7                                                 | -                   | 1.3                                          | -                  | μs   |

| Cb                                         | Capacitive load for each bus line       | -                                                   | 400                 | -                                            | 400                | pF   |

| Table 40. I <sup>2</sup> C | characteristics |

|----------------------------|-----------------|

|----------------------------|-----------------|

1. Guaranteed by design, not tested in production.

f<sub>PCLK1</sub> must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve fast mode I<sup>2</sup>C frequencies. It must be a multiple of 10 MHz to reach the 400 kHz maximum I2C fast mode clock.

3. The maximum Data hold time has only to be met if the interface does not stretch the low period of SCL signal.

Figure 29. I<sup>2</sup>C bus AC waveforms and measurement circuit

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}.$

2. Rs = Series protection resistors, Rp = Pull-up resistors,  $V_{DD_{-12C}} = 12C$  bus supply.

| £ (/LU-)               | I2C_CCR value           |

|------------------------|-------------------------|

| f <sub>SCL</sub> (kHz) | R <sub>P</sub> = 4.7 kΩ |

| 400                    | 0x801E                  |

| 300                    | 0x8028                  |

| 200                    | 0x803C                  |

| 100                    | 0x00B4                  |

| 50                     | 0x0168                  |

| 20                     | 0x0384                  |

### Table 41. SCL frequency (f<sub>PCI K1</sub>= 36 MHz., V<sub>DD 12C</sub> = 3.3 V)<sup>(1)(2)</sup>

1.  $R_P$  = External pull-up resistance,  $f_{SCL} = I^2C$  speed,

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed ±2%. These variations depend on the accuracy of the external components used to design the application.

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Мах   | Min    | Тур                   | Max    |

| А      | 0.800 | 0.900       | 1.000 | 0.0315 | 0.0354                | 0.0394 |

| A1     | -     | 0.020       | 0.050 | -      | 0.0008                | 0.0020 |

| A2     | -     | 0.650       | 1.000 | -      | 0.0256                | 0.0394 |

| A3     | -     | 0.200       | -     | -      | 0.0079                | -      |

| b      | 0.180 | 0.230       | 0.300 | 0.0071 | 0.0091                | 0.0118 |

| D      | 5.875 | 6.000       | 6.125 | 0.2313 | 0.2362                | 0.2411 |

| D2     | 1.750 | 3.700       | 4.250 | 0.0689 | 0.1457                | 0.1673 |

| E      | 5.875 | 6.000       | 6.125 | 0.2313 | 0.2362                | 0.2411 |

| E2     | 1.750 | 3.700       | 4.250 | 0.0689 | 0.1457                | 0.1673 |

| е      | 0.450 | 0.500       | 0.550 | 0.0177 | 0.0197                | 0.0217 |

| L      | 0.350 | 0.550       | 0.750 | 0.0138 | 0.0217                | 0.0295 |

| К      | 0.250 | -           | -     | 0.0098 | -                     | -      |

| ddd    | -     | -           | 0.080 | -      | -                     | 0.0031 |

# Table 51. VFQFPN36 - 36-pin, 6x6 mm, 0.5 mm pitch very thin profile fine pitchquad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

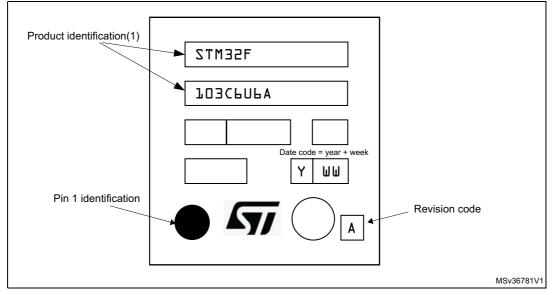

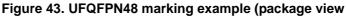

#### **Device Marking for UFQFPN48**

The following figure gives an example of topside marking orientation versus ball 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

## Table 54. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ballgrid array package mechanical data (continued)

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Max   | Min                   | Тур    | Мах    |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| F      | -           | 0.750 | -     | -                     | 0.0295 | -      |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |

| eee    | -           | -     | 0.150 | -                     | -      | 0.0059 |

| fff    | -           | -     | 0.050 | -                     | -      | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

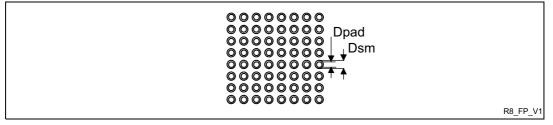

# Figure 48. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball grid array, recommended footprint

#### Table 55. TFBGA64 recommended PCB design rules (0.5 mm pitch BGA)

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.5                                                              |

| Dpad              | 0.280 mm                                                         |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.280 mm                                                         |

| Stencil thickness | Between 0.100 mm and 1.125 mm                                    |

| Pad trace width   | 0.100 mm                                                         |

| Symbol | Symbol |       |       |        | inches <sup>(1)</sup> |        |

|--------|--------|-------|-------|--------|-----------------------|--------|

| Symbol | Min    | Тур   | Max   | Min    | Тур                   | Мах    |

| А      | -      | -     | 1.600 | -      | -                     | 0.0630 |

| A1     | 0.050  | -     | 0.150 | 0.0020 | -                     | 0.0059 |

| A2     | 1.350  | 1.400 | 1.450 | 0.0531 | 0.0551                | 0.0571 |

| b      | 0.170  | 0.220 | 0.270 | 0.0067 | 0.0087                | 0.0106 |

| с      | 0.090  | -     | 0.200 | 0.0035 | -                     | 0.0079 |

| D      | 8.800  | 9.000 | 9.200 | 0.3465 | 0.3543                | 0.3622 |

| D1     | 6.800  | 7.000 | 7.200 | 0.2677 | 0.2756                | 0.2835 |

| D3     | -      | 5.500 | -     | -      | 0.2165                | -      |

| E      | 8.800  | 9.000 | 9.200 | 0.3465 | 0.3543                | 0.3622 |

| E1     | 6.800  | 7.000 | 7.200 | 0.2677 | 0.2756                | 0.2835 |

| E3     | -      | 5.500 | -     | -      | 0.2165                | -      |

| е      | -      | 0.500 | -     | -      | 0.0197                | -      |

| L      | 0.450  | 0.600 | 0.750 | 0.0177 | 0.0236                | 0.0295 |

| L1     | -      | 1.000 | -     | -      | 0.0394                | -      |

| k      | 0°     | 3.5°  | 7°    | 0°     | 3.5°                  | 7°     |

| CCC    | -      | -     | 0.080 | -      | -                     | 0.0031 |

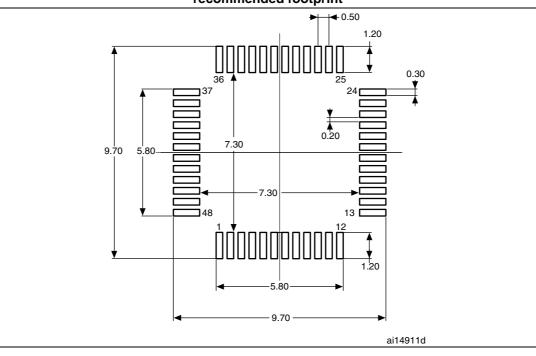

| Table 56. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |

|-------------------------------------------------------------------|

| mechanical data                                                   |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# Figure 51. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20-May-2010 | 4        | Added VFQFPN48 package.<br>Updated note 2 below Table 40: I <sup>2</sup> C characteristics<br>Updated Figure 29: I <sup>2</sup> C bus AC waveforms and measurement circuit<br>Updated Figure 28: Recommended NRST pin protection<br>Updated Section 5.3.12: I/O current injection characteristics                                                                                                                                                 |

| 19-Apr-2011 | 5        | Updated footnotes below Table 6: Voltage characteristics on page 32 and Table 7:<br>Current characteristics on page 33<br>Updated tw min in Table 20: High-speed external user clock characteristics on<br>page 46<br>Updated startup time in Table 23: LSE oscillator characteristics ( $f_{LSE}$ = 32.768 kHz)<br>on page 49<br>Added Section 5.3.12: I/O current injection characteristics<br>Updated Section 5.3.13: I/O port characteristics |

| Table 59. Document revision | on history (continued) |

|-----------------------------|------------------------|

|                             |                        |