Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Discontinued at Digi-Key                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                       |

| Core Size                  | 16/32-Bit                                                                     |

| Speed                      | 66MHz                                                                         |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI          |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                          |

| Number of I/O              | 118                                                                           |

| Program Memory Size        | 768KB (768K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 82K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                     |

| Data Converters            | A/D 24x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 144-LQFP Exposed Pad                                                          |

| Supplier Device Package    | PG-LQFP-144-4                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/kx228796f66l82acxt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Summary of Features**

#### Table 1XC228x Derivative Synopsis (cont'd)

| Derivative <sup>1)</sup> | Temp.<br>Range      | Program<br>Memory <sup>2)</sup> | PSRAM <sup>3)</sup> | CCU6<br>Mod. | ADC <sup>4)</sup><br>Chan. | Interfaces <sup>4)</sup>       |

|--------------------------|---------------------|---------------------------------|---------------------|--------------|----------------------------|--------------------------------|

| SAK-XC2285-<br>56FxxL    | -40 °C to<br>125 °C | 448 Kbytes<br>Flash             | 16 Kbytes           | 0, 1         | 16                         | 2 CAN Nodes,<br>4 Serial Chan. |

| SAF-XC2285-<br>56FxxL    | -40 °C to<br>85 °C  | 448 Kbytes<br>Flash             | 16 Kbytes           | 0, 1         | 16                         | 2 CAN Nodes,<br>4 Serial Chan. |

1) This Data Sheet is valid for devices starting with and including design step AC.

2) Specific inormation about the on-chip Flash memory in Table 2.

3) All derivatives additionally provide 1 Kbyte SBRAM, 2 Kbytes DPRAM, and 16 Kbytes DSRAM.

Specific information about the available channels in Table 3.

Analog input channels are listed for each Analog/Digital Converter module separately (ADC0 + ADC1).

#### **General Device Information**

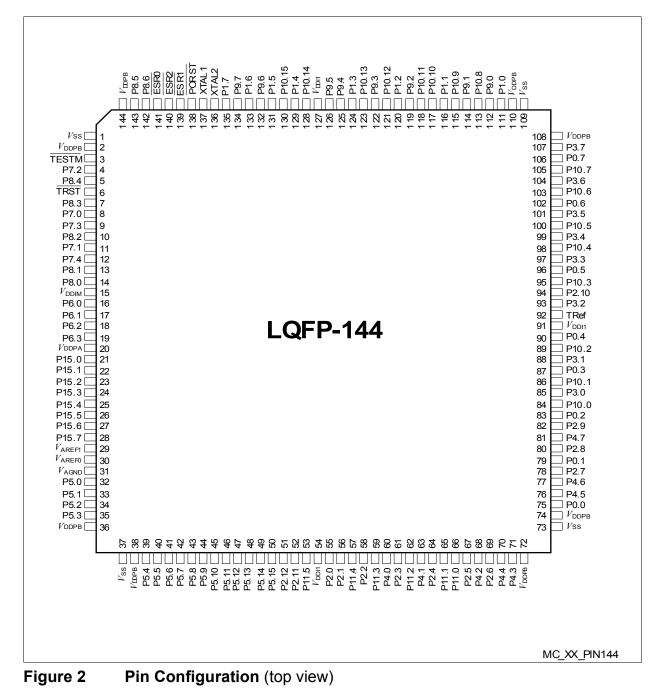

# 2.1 Pin Configuration and Definition

The pins of the XC228x are described in detail in **Table 4**, which includes all alternate functions. For further explanations please refer to the footnotes at the end of the table. **Figure 2** summarizes all pins, showing their locations on the four sides of the package.

# XC2287 / XC2286 / XC2285 XC2000 Family Derivatives

| Table | Table 4Pin Definitions and Functions (cont'd) |        |      |                                               |  |  |  |  |

|-------|-----------------------------------------------|--------|------|-----------------------------------------------|--|--|--|--|

| Pin   | Symbol                                        | Ctrl.  | Туре | Function                                      |  |  |  |  |

| 71    | P4.3                                          | O0 / I | St/B | Bit 3 of Port 4, General Purpose Input/Output |  |  |  |  |

|       | CC2_27                                        | O3 / I | St/B | CAPCOM2 CC27IO Capture Inp./ Compare Out.     |  |  |  |  |

|       | CS3                                           | OH     | St/B | External Bus Interface Chip Select 3 Output   |  |  |  |  |

|       | RxDC2A                                        | 1      | St/B | CAN Node 2 Receive Data Input                 |  |  |  |  |

|       | T2EUD                                         | 1      | St/B | GPT1 Timer T2 External Up/Down Control Input  |  |  |  |  |

| 75    | P0.0                                          | O0 / I | St/B | Bit 0 of Port 0, General Purpose Input/Output |  |  |  |  |

|       | U1C0_DOUT                                     | 01     | St/B | USIC1 Channel 0 Shift Data Output             |  |  |  |  |

|       | CCU61_<br>CC60                                | O3 / I | St/B | CCU61 Channel 0 Input/Output                  |  |  |  |  |

|       | A0                                            | ОН     | St/B | External Bus Interface Address Line 0         |  |  |  |  |

|       | U1C0_DX0A                                     | I      | St/B | USIC1 Channel 0 Shift Data Input              |  |  |  |  |

| 76    | P4.5                                          | O0 / I | St/B | Bit 5 of Port 4, General Purpose Input/Output |  |  |  |  |

|       | CC2_29                                        | O3 / I | St/B | CAPCOM2 CC29IO Capture Inp./Compare Out.      |  |  |  |  |

| 77    | P4.6                                          | O0 / I | St/B | Bit 6 of Port 4, General Purpose Input/Output |  |  |  |  |

|       | CC2_30                                        | O3 / I | St/B | CAPCOM2 CC30IO Capture Inp./ Compare Out.     |  |  |  |  |

|       | T4IN                                          | I      | St/B | GPT1 Timer T4 Count/Gate Input                |  |  |  |  |

| 78    | P2.7                                          | O0 / I | St/B | Bit 7 of Port 2, General Purpose Input/Output |  |  |  |  |

|       | U0C1_<br>SELO0                                | 01     | St/B | USIC0 Channel 1 Select/Control 0 Output       |  |  |  |  |

|       | U0C0_<br>SELO1                                | 02     | St/B | USIC0 Channel 0 Select/Control 1 Output       |  |  |  |  |

|       | CC2_20                                        | O3 / I | St/B | CAPCOM2 CC20IO Capture Inp./ Compare Out.     |  |  |  |  |

|       | A20                                           | ОН     | St/B | External Bus Interface Address Line 20        |  |  |  |  |

|       | U0C1_DX2C                                     | 1      | St/B | USIC0 Channel 1 Shift Control Input           |  |  |  |  |

|       | RxDC1C                                        | 1      | St/B | CAN Node 1 Receive Data Input                 |  |  |  |  |

# XC2287 / XC2286 / XC2285 XC2000 Family Derivatives

| Table | Table 4Pin Definitions and Functions (cont'd) |        |      |                                                |  |  |  |

|-------|-----------------------------------------------|--------|------|------------------------------------------------|--|--|--|

| Pin   | Symbol                                        | Ctrl.  | Туре | Function                                       |  |  |  |

| 83    | P0.2                                          | O0 / I | St/B | Bit 2 of Port 0, General Purpose Input/Output  |  |  |  |

|       | U1C0_<br>SCLKOUT                              | 01     | St/B | USIC1 Channel 0 Shift Clock Output             |  |  |  |

|       | TxDC0                                         | 02     | St/B | CAN Node 0 Transmit Data Output                |  |  |  |

|       | CCU61_<br>CC62                                | O3 / I | St/B | CCU61 Channel 2 Input/Output                   |  |  |  |

|       | A2                                            | ОН     | St/B | External Bus Interface Address Line 2          |  |  |  |

|       | U1C0_DX1B                                     | l      | St/B | USIC1 Channel 0 Shift Clock Input              |  |  |  |

| 84    | P10.0                                         | O0 / I | St/B | Bit 0 of Port 10, General Purpose Input/Output |  |  |  |

|       | U0C1_DOUT                                     | 01     | St/B | USIC0 Channel 1 Shift Data Output              |  |  |  |

|       | CCU60_<br>CC60                                | 02 / I | St/B | CCU60 Channel 0 Input/Output                   |  |  |  |

|       | AD0                                           | OH/I   | St/B | External Bus Interface Address/Data Line 0     |  |  |  |

|       | ESR1_2                                        | I      | St/B | ESR1 Trigger Input 2                           |  |  |  |

|       | U0C0_DX0A                                     | I      | St/B | USIC0 Channel 0 Shift Data Input               |  |  |  |

|       | U0C1_DX0A                                     | I      | St/B | USIC0 Channel 1 Shift Data Input               |  |  |  |

| 85    | P3.0                                          | O0 / I | St/B | Bit 0 of Port 3, General Purpose Input/Output  |  |  |  |

|       | U2C0_DOUT                                     | 01     | St/B | USIC2 Channel 0 Shift Data Output              |  |  |  |

|       | BREQ                                          | OH     | St/B | External Bus Request Output                    |  |  |  |

|       | ESR1_1                                        | I      | St/B | ESR1 Trigger Input 1                           |  |  |  |

|       | U2C0_DX0A                                     | I      | St/B | USIC2 Channel 0 Shift Data Input               |  |  |  |

|       | RxDC3B                                        | I      | St/B | CAN Node 3 Receive Data Input                  |  |  |  |

|       | U2C0_DX1A                                     | I      | St/B | USIC2 Channel 0 Shift Clock Input              |  |  |  |

| 86    | P10.1                                         | O0 / I | St/B | Bit 1 of Port 10, General Purpose Input/Output |  |  |  |

|       | U0C0_DOUT                                     | 01     | St/B | USIC0 Channel 0 Shift Data Output              |  |  |  |

|       | CCU60_<br>CC61                                | 02 / I | St/B | CCU60 Channel 1 Input/Output                   |  |  |  |

|       | AD1                                           | OH/I   | St/B | External Bus Interface Address/Data Line 1     |  |  |  |

|       | U0C0_DX0B                                     | I      | St/B | USIC0 Channel 0 Shift Data Input               |  |  |  |

|       | U0C0_DX1A                                     | I      | St/B | USIC0 Channel 0 Shift Clock Input              |  |  |  |

| Pin | Symbol           | Ctrl.  | Туре | Function                                       |

|-----|------------------|--------|------|------------------------------------------------|

| 92  | TRef             | Ю      | Sp/1 | Control Pin for Core Voltage Generation 2)     |

| 93  | P3.2             | O0 / I | St/B | Bit 2 of Port 3, General Purpose Input/Output  |

|     | U2C0_<br>SCLKOUT | 01     | St/B | USIC2 Channel 0 Shift Clock Output             |

|     | TxDC3            | 02     | St/B | CAN Node 3 Transmit Data Output                |

|     | U2C0_DX1B        | I      | St/B | USIC2 Channel 0 Shift Clock Input              |

|     | HOLD             | 1      | St/B | External Bus Master Hold Request Input         |

| 94  | P2.10            | O0 / I | St/B | Bit 10 of Port 2, General Purpose Input/Output |

|     | U0C1_DOUT        | 01     | St/B | USIC0 Channel 1 Shift Data Output              |

|     | U0C0_<br>SELO3   | 02     | St/B | USIC0 Channel 0 Select/Control 3 Output        |

|     | CC2_23           | O3 / I | St/B | CAPCOM2 CC23IO Capture Inp./ Compare Out.      |

|     | A23              | OH     | St/B | External Bus Interface Address Line 23         |

|     | U0C1_DX0E        | I      | St/B | USIC0 Channel 1 Shift Data Input               |

|     | CAPIN            | I      | St/B | GPT2 Register CAPREL Capture Input             |

| 95  | P10.3            | O0 / I | St/B | Bit 3 of Port 10, General Purpose Input/Output |

|     | CCU60_<br>COUT60 | O2     | St/B | CCU60 Channel 0 Output                         |

|     | AD3              | OH/I   | St/B | External Bus Interface Address/Data Line 3     |

|     | U0C0_DX2A        | I      | St/B | USIC0 Channel 0 Shift Control Input            |

|     | U0C1_DX2A        | I      | St/B | USIC0 Channel 1 Shift Control Input            |

| 96  | P0.5             | O0 / I | St/B | Bit 5 of Port 0, General Purpose Input/Output  |

|     | U1C1_<br>SCLKOUT | 01     | St/B | USIC1 Channel 1 Shift Clock Output             |

|     | U1C0_<br>SELO2   | 02     | St/B | USIC1 Channel 0 Select/Control 2 Output        |

|     | CCU61_<br>COUT62 | O3     | St/B | CCU61 Channel 2 Output                         |

|     | A5               | OH     | St/B | External Bus Interface Address Line 5          |

|     | U1C1_DX1A        | I      | St/B | USIC1 Channel 1 Shift Clock Input              |

|     | U1C0_DX1C        | 1      | St/B | USIC1 Channel 0 Shift Clock Input              |

| Table | Table 4Pin Definitions and Functions (cont'd) |        |      |                                                 |  |  |  |

|-------|-----------------------------------------------|--------|------|-------------------------------------------------|--|--|--|

| Pin   | Symbol                                        | Ctrl.  | Туре | Function                                        |  |  |  |

| 115   | P10.9                                         | O0 / I | St/B | Bit 9 of Port 10, General Purpose Input/Output  |  |  |  |

|       | U0C0_<br>SELO4                                | 01     | St/B | USIC0 Channel 0 Select/Control 4 Output         |  |  |  |

|       | U0C1_<br>MCLKOUT                              | O2     | St/B | USIC0 Channel 1 Master Clock Output             |  |  |  |

|       | AD9                                           | OH/I   | St/B | External Bus Interface Address/Data Line 9      |  |  |  |

|       | CCU60_<br>CCPOS2A                             | I      | St/B | CCU60 Position Input 2                          |  |  |  |

|       | ТСК_В                                         | I      | St/B | JTAG Clock Input                                |  |  |  |

| 116   | P1.1                                          | O0 / I | St/B | Bit 1 of Port 1, General Purpose Input/Output   |  |  |  |

|       | CCU62_<br>COUT62                              | 01     | St/B | CCU62 Channel 2 Output                          |  |  |  |

|       | U1C0_<br>SELO5                                | O2     | St/B | USIC1 Channel 0 Select/Control 5 Output         |  |  |  |

|       | U2C1_DOUT                                     | O3     | St/B | USIC2 Channel 1 Shift Data Output               |  |  |  |

|       | A9                                            | OH     | St/B | External Bus Interface Address Line 9           |  |  |  |

|       | ESR2_3                                        | I      | St/B | ESR2 Trigger Input 3                            |  |  |  |

|       | EX1BINA                                       | I      | St/B | External Interrupt Trigger Input                |  |  |  |

|       | U2C1_DX0C                                     | I      | St/B | USIC2 Channel 1 Shift Data Input                |  |  |  |

| 117   | P10.10                                        | O0 / I | St/B | Bit 10 of Port 10, General Purpose Input/Output |  |  |  |

|       | U0C0_<br>SELO0                                | 01     | St/B | USIC0 Channel 0 Select/Control 0 Output         |  |  |  |

|       | CCU60_<br>COUT63                              | O2     | St/B | CCU60 Channel 3 Output                          |  |  |  |

|       | AD10                                          | OH/I   | St/B | External Bus Interface Address/Data Line 10     |  |  |  |

|       | U0C0_DX2C                                     | I      | St/B | USIC0 Channel 0 Shift Control Input             |  |  |  |

|       | TDI_B                                         | I      | St/B | JTAG Test Data Input                            |  |  |  |

|       | U0C1_DX1A                                     | I      | St/B | USIC0 Channel 1 Shift Clock Input               |  |  |  |

This common memory space consists of 16 Mbytes organized as 256 segments of 64 Kbytes; each segment contains four data pages of 16 Kbytes. The entire memory space can be accessed bytewise or wordwise. Portions of the on-chip DPRAM and the register spaces (ESFR/SFR) additionally are directly bit addressable.

The internal data memory areas and the Special Function Register areas (SFR and ESFR) are mapped into segment 0, the system segment.

The Program Management Unit (PMU) handles all code fetches and, therefore, controls access to the program memories such as Flash memory and PSRAM.

The Data Management Unit (DMU) handles all data transfers and, therefore, controls access to the DSRAM and the on-chip peripherals.

Both units (PMU and DMU) are connected to the high-speed system bus so that they can exchange data. This is required if operands are read from program memory, code or data is written to the PSRAM, code is fetched from external memory, or data is read from or written to external resources. These include peripherals on the LXBus such as USIC or MultiCAN. The system bus allows concurrent two-way communication for maximum transfer performance.

**Up to 64 Kbytes of on-chip Program SRAM (PSRAM)** are provided to store user code or data. The PSRAM is accessed via the PMU and is optimized for code fetches. A section of the PSRAM with programmable size can be write-protected.

Note: The actual size of the PSRAM depends on the chosen derivative (see Table 1).

**16 Kbytes of on-chip Data SRAM (DSRAM)** are used for storage of general user data. The DSRAM is accessed via a separate interface and is optimized for data access.

**2 Kbytes of on-chip Dual-Port RAM (DPRAM)** provide storage for user-defined variables, for the system stack, and for general purpose register banks. A register bank can consist of up to 16 word-wide (R0 to R15) and/or byte-wide (RL0, RH0, ..., RL7, RH7) General Purpose Registers (GPRs).

The upper 256 bytes of the DPRAM are directly bit addressable. When used by a GPR, any location in the DPRAM is bit addressable.

**1 Kbyte of on-chip Stand-By SRAM (SBRAM)** provides storage for system-relevant user data that must be preserved while the major part of the device is powered down. The SBRAM is accessed via a specific interface and is powered in domain M.

# 3.7 Capture/Compare Units CCU6x

The XC228x features up to four CCU6 units (CCU60, CCU61, CCU62, CCU63).

The CCU6 is a high-resolution capture and compare unit with application-specific modes. It provides inputs to start the timers synchronously, an important feature in devices with several CCU6 modules.

The module provides two independent timers (T12, T13), that can be used for PWM generation, especially for AC motor control. Additionally, special control modes for block commutation and multi-phase machines are supported.

#### Timer 12 Features

- Three capture/compare channels, where each channel can be used either as a capture or as a compare channel.

- Supports generation of a three-phase PWM (six outputs, individual signals for highside and low-side switches)

- 16-bit resolution, maximum count frequency = peripheral clock

- Dead-time control for each channel to avoid short circuits in the power stage

- Concurrent update of the required T12/13 registers

- Center-aligned and edge-aligned PWM can be generated

- Single-shot mode supported

- · Many interrupt request sources

- Hysteresis-like control mode

- Automatic start on a HW event (T12HR, for synchronization purposes)

#### **Timer 13 Features**

- One independent compare channel with one output

- 16-bit resolution, maximum count frequency = peripheral clock

- Can be synchronized to T12

- Interrupt generation at period match and compare match

- Single-shot mode supported

- Automatic start on a HW event (T13HR, for synchronization purposes)

#### Additional Features

- Block commutation for brushless DC drives implemented

- Position detection via Hall sensor pattern

- Automatic rotational speed measurement for block commutation

- Integrated error handling

- Fast emergency stop without CPU load via external signal (CTRAP)

- · Control modes for multi-channel AC drives

- Output levels can be selected and adapted to the power stage

# 3.10 A/D Converters

For analog signal measurement, up to two 10-bit A/D converters (ADC0, ADC1) with 16 + 8 multiplexed input channels and a sample and hold circuit have been integrated on-chip. They use the successive approximation method. The sample time (to charge the capacitors) and the conversion time are programmable so that they can be adjusted to the external circuit. The A/D converters can also operate in 8-bit conversion mode, further reducing the conversion time.

Several independent conversion result registers, selectable interrupt requests, and highly flexible conversion sequences provide a high degree of programmability to meet the application requirements. Both modules can be synchronized to allow parallel sampling of two input channels.

For applications that require more analog input channels, external analog multiplexers can be controlled automatically.

For applications that require fewer analog input channels, the remaining channel inputs can be used as digital input port pins.

The A/D converters of the XC228x support two types of request sources which can be triggered by several internal and external events.

- Parallel requests are activated at the same time and then executed in a predefined sequence.

- Queued requests are executed in a user-defined sequence.

In addition, the conversion of a specific channel can be inserted into a running sequence without disturbing that sequence. All requests are arbitrated according to the priority level assigned to them.

Data reduction features, such as limit checking or result accumulation, reduce the number of required CPU access operations allowing the precise evaluation of analoginputs (high conversion rate) even at a low CPU speed.

The Peripheral Event Controller (PEC) can be used to control the A/D converters or to automatically store conversion results to a table in memory for later evaluation, without requiring the overhead of entering and exiting interrupt routines for each data transfer. Each A/D converter contains eight result registers which can be concatenated to build a result FIFO. Wait-for-read mode can be enabled for each result register to prevent the loss of conversion data.

In order to decouple analog inputs from digital noise and to avoid input trigger noise, those pins used for analog input can be disconnected from the digital input stages under software control. This can be selected for each pin separately with registers P5\_DIDIS and P15\_DIDIS (Port x Digital Input Disable).

The Auto-Power-Down feature of the A/D converters minimizes the power consumption when no conversion is in progress.

#### **MultiCAN Features**

- CAN functionality conforming to CAN specification V2.0 B active for each CAN node (compliant to ISO 11898)

- Up to five independent CAN nodes

- Up to 128 independent message objects (shared by the CAN nodes)

- Dedicated control registers for each CAN node

- Data transfer rate up to 1 Mbit/s, individually programmable for each node

- Flexible and powerful message transfer control and error handling capabilities

- Full-CAN functionality for message objects:

- Can be assigned to one of the CAN nodes

- Configurable as transmit or receive objects, or as message buffer FIFO

- Handle 11-bit or 29-bit identifiers with programmable acceptance mask for filtering

- Remote Monitoring Mode, and frame counter for monitoring

- Automatic Gateway Mode support

- 16 individually programmable interrupt nodes

- Analyzer mode for CAN bus monitoring

# 3.13 Watchdog Timer

The Watchdog Timer is one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after an application reset of the chip. It can be disabled and enabled at any time by executing the instructions DISWDT and ENWDT respectively. The software has to service the Watchdog Timer before it overflows. If this is not the case because of a hardware or software failure, the Watchdog Timer overflows, generating a prewarning interrupt and then a reset request.

The Watchdog Timer is a 16-bit timer clocked with the system clock divided by 16,384 or 256. The Watchdog Timer register is set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the Watchdog Timer is reloaded and the prescaler is cleared.

Time intervals between 3.2  $\mu$ s and 13.4 s can be monitored (@ 80 MHz). The default Watchdog Timer interval after power-up is 6.5 ms (@ 10 MHz).

## 3.14 Clock Generation

The Clock Generation Unit can generate the system clock signal  $f_{SYS}$  for the XC228x from a number of external or internal clock sources:

- External clock signals with pad or core voltage levels

- External crystal using the on-chip oscillator

- On-chip clock source for operation without crystal

- Wake-up clock (ultra-low-power) to further reduce power consumption

The programmable on-chip PLL with multiple prescalers generates a clock signal for maximum system performance from standard crystals or from the on-chip clock source. See also **Section 4.6.2**.

The Oscillator Watchdog (OWD) generates an interrupt if the crystal oscillator frequency falls below a certain limit or stops completely. In this case, the system can be supplied with an emergency clock to enable operation even after an external clock failure.

All available clock signals can be output on one of two selectable pins.

# 3.17 Instruction Set Summary

Table 10 lists the instructions of the XC228x.

The addressing modes that can be used with a specific instruction, the function of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the "**Instruction Set Manual**".

This document also provides a detailed description of each instruction.

| Mnemonic      | Description                                                                                       | Bytes |

|---------------|---------------------------------------------------------------------------------------------------|-------|

| ADD(B)        | Add word (byte) operands                                                                          | 2/4   |

| ADDC(B)       | Add word (byte) operands with Carry                                                               | 2/4   |

| SUB(B)        | Subtract word (byte) operands                                                                     | 2/4   |

| SUBC(B)       | Subtract word (byte) operands with Carry                                                          | 2/4   |

| MUL(U)        | (Un)Signed multiply direct GPR by direct GPR (16- $\times$ 16-bit)                                | 2     |

| DIV(U)        | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                         | 2     |

| DIVL(U)       | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                         | 2     |

| CPL(B)        | Complement direct word (byte) GPR                                                                 | 2     |

| NEG(B)        | Negate direct word (byte) GPR                                                                     | 2     |

| AND(B)        | Bitwise AND, (word/byte operands)                                                                 | 2/4   |

| OR(B)         | Bitwise OR, (word/byte operands)                                                                  | 2/4   |

| XOR(B)        | Bitwise exclusive OR, (word/byte operands)                                                        | 2/4   |

| BCLR/BSET     | Clear/Set direct bit                                                                              | 2     |

| BMOV(N)       | Move (negated) direct bit to direct bit                                                           | 4     |

| BAND/BOR/BXOR | AND/OR/XOR direct bit with direct bit                                                             | 4     |

| BCMP          | Compare direct bit to direct bit                                                                  | 4     |

| BFLDH/BFLDL   | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data     | 4     |

| CMP(B)        | Compare word (byte) operands                                                                      | 2/4   |

| CMPD1/2       | Compare word data to GPR and decrement GPR by 1/2                                                 | 2/4   |

| CMPI1/2       | Compare word data to GPR and increment GPR by 1/2                                                 | 2/4   |

| PRIOR         | Determine number of shift cycles to normalize direct word GPR and store result in direct word GPR | 2     |

| SHL/SHR       | Shift left/right direct word GPR                                                                  | 2     |

#### Table 10Instruction Set Summary

#### Parameter Interpretation

The parameters listed in the following include both the characteristics of the XC228x and its demands on the system. To aid in correctly interpreting the parameters when evaluating them for a design, they are marked accordingly in the column "Symbol":

CC (Controller Characteristics):

The logic of the XC228x provides signals with the specified characteristics.

#### **SR** (System Requirement):

The external system must provide signals with the specified characteristics to the XC228x.

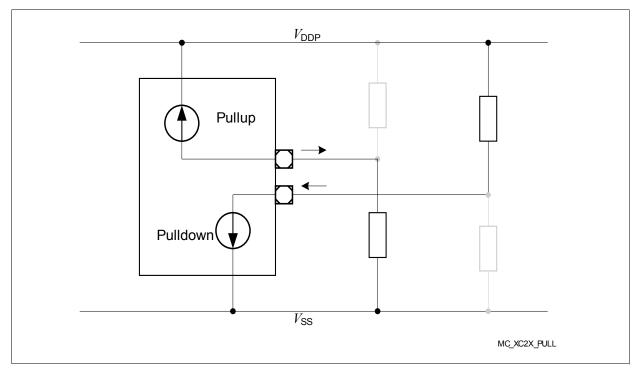

#### Pullup/Pulldown Device Behavior

Most pins of the XC228x feature pullup or pulldown devices. For some special pins these are fixed; for the port pins they can be selected by the application.

The specified current values indicate how to load the respective pin depending on the intended signal level. **Figure 12** shows the current paths.

The shaded resistors shown in the figure may be required to compensate system pull currents that do not match the given limit values.

Figure 12 Pullup/Pulldown Current Definition

## 4.4 System Parameters

The following parameters specify several aspects which are important when integrating the XC228x into an application system.

Note: These parameters are not subject to production test but verified by design and/or characterization.

| Parameter                                                    | Symbol                 |                            | Values          |                            |     | Note /                                                      |

|--------------------------------------------------------------|------------------------|----------------------------|-----------------|----------------------------|-----|-------------------------------------------------------------|

|                                                              |                        | Min. Typ.                  |                 | Max.                       |     | Test Condition                                              |

| Supply watchdog (SWD)<br>supervision level<br>(see Table 21) | V <sub>SWD</sub><br>CC | V <sub>LV</sub> -<br>0.150 | V <sub>LV</sub> | V <sub>LV</sub> +<br>0.100 | V   | $V_{\rm LV}$ = selected<br>voltage in upper<br>voltage area |

|                                                              |                        | V <sub>LV</sub> -<br>0.125 | V <sub>LV</sub> | V <sub>LV</sub> +<br>0.050 | V   | $V_{\rm LV}$ = selected<br>voltage in lower<br>voltage area |

| Core voltage (PVC)<br>supervision level<br>(see Table 22)    | V <sub>PVC</sub> CC    | V <sub>LV</sub> -<br>0.070 | V <sub>LV</sub> | V <sub>LV</sub> +<br>0.030 | V   | $V_{\rm LV}$ = selected voltage                             |

| Current control limit                                        | I <sub>CC</sub> CC     | 13                         | -               | 30                         | mA  | Power domain<br>DMP_M                                       |

|                                                              |                        | 90                         | -               | 150                        | mA  | Power domain<br>DMP_1                                       |

| Wakeup clock source frequency                                | f <sub>WU</sub> CC     | 400                        | 500             | 600                        | kHz | FREQSEL<br>= 00 <sub>B</sub>                                |

| Internal clock source frequency                              | $f_{\rm INT}$ CC       | 4.8                        | 5.0             | 5.2                        | MHz |                                                             |

| Startup time from stopover mode                              | $t_{\rm SSO}$ CC       | 200                        | 260             | 320                        | μS  | User instruction from PSRAM                                 |

| Startup time from standby mode                               | t <sub>SSB</sub> CC    | 2.5                        | 2.8             | 3.5                        | ms  | User instruction from Flash                                 |

#### Table 20Various System Parameters

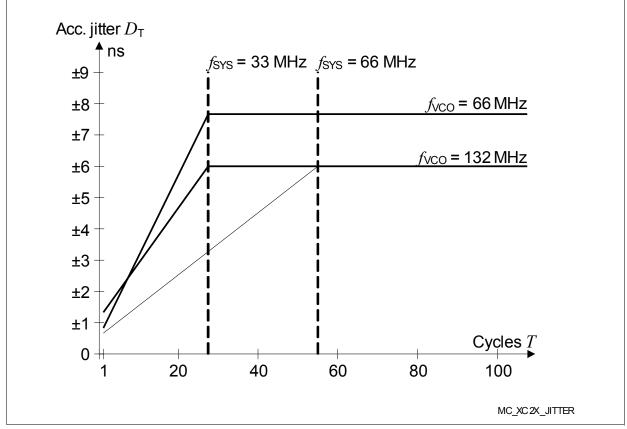

Figure 19 Approximated Accumulated PLL Jitter

Note: The specified PLL jitter values are valid if the capacitive load per pin does not exceed  $C_L$  = 20 pF (see **Table 12**).

The maximum peak-to-peak noise on the pad supply voltage (measured between  $V_{DDPB}$  pin 100/144 and  $V_{SS}$  pin 1) is limited to a peak-to-peak voltage of  $V_{PP}$  = 50 mV. This can be achieved by appropriate blocking of the supply voltage as close as possible to the supply pins and using PCB supply and ground planes.

Different frequency bands can be selected for the VCO so that the operation of the PLL can be adjusted to a wide range of input and output frequencies:

| PLLCON0.VCOSEL | VCO Frequency Range | Base Frequency Range |

|----------------|---------------------|----------------------|

| 00             | 50 110 MHz          | 10 40 MHz            |

| 01             | 100 160 MHz         | 20 80 MHz            |

| 1X             | Reserved            |                      |

| Table 25 | VCO Bands for PLL Operation <sup>1)</sup> |

|----------|-------------------------------------------|

|----------|-------------------------------------------|

1) Not subject to production test - verified by design/characterization.

# XC2287 / XC2286 / XC2285 XC2000 Family Derivatives

#### **Electrical Parameters**

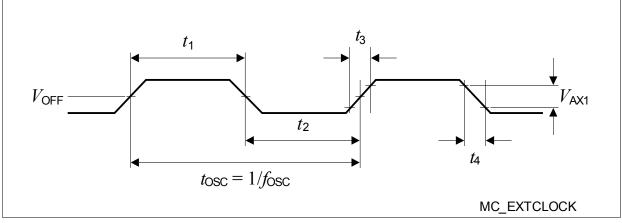

#### Figure 20 External Clock Drive XTAL1

Note: For crystal/resonator operation, it is strongly recommended to measure the oscillation allowance (negative resistance) in the final target system (layout) to determine the optimum parameters for oscillator operation. Please refer to the limits specified by the crystal/resonator supplier.

# Table 29External Bus Cycle Timing for Upper Voltage Range<br/>(Operating Conditions apply)

| Parameter                                                         | Symbol                    |           | Limits | 5    | Unit | Note |

|-------------------------------------------------------------------|---------------------------|-----------|--------|------|------|------|

|                                                                   |                           | Min. Typ. |        | Max. |      |      |

| Output valid delay for:<br>RD, WR(L/H)                            | <i>t</i> <sub>10</sub> CC | -         |        | 13   | ns   |      |

| Output valid delay for:<br>BHE, ALE                               | <i>t</i> <sub>11</sub> CC | -         |        | 13   | ns   |      |

| Output valid delay for:<br>A23 A16, A15 A0 (on P0/P1)             | <i>t</i> <sub>12</sub> CC | -         |        | 14   | ns   |      |

| Output valid delay for:<br>A15 A0 (on P2/P10)                     | <i>t</i> <sub>13</sub> CC | -         |        | 14   | ns   |      |

| Output valid delay for:                                           | <i>t</i> <sub>14</sub> CC | -         |        | 13   | ns   |      |

| Output valid delay for:<br>D15 D0 (write data, MUX-mode)          | <i>t</i> <sub>15</sub> CC | -         |        | 14   | ns   |      |

| Output valid delay for:<br>D15 … D0 (write data, DEMUX-<br>mode)  | <i>t</i> <sub>16</sub> CC | -         |        | 14   | ns   |      |

| Output hold time for:<br>RD, WR(L/H)                              | <i>t</i> <sub>20</sub> CC | 0         |        | 8    | ns   |      |

| Output hold time for:<br>BHE, ALE                                 | <i>t</i> <sub>21</sub> CC | 0         |        | 8    | ns   |      |

| Output hold time for:<br>A23 A16, A15 A0 (on P2/P10)              | <i>t</i> <sub>23</sub> CC | 0         |        | 8    | ns   |      |

| Output hold time for:<br>CS                                       | <i>t</i> <sub>24</sub> CC | 0         |        | 8    | ns   |      |

| Output hold time for:<br>D15 D0 (write data)                      | <i>t</i> <sub>25</sub> CC | 0         |        | 8    | ns   |      |

| Input setup time for:<br>READY, D15 … D0 (read data)              | <i>t</i> <sub>30</sub> SR | 18        |        | -    | ns   |      |

| Input hold time for:<br>READY, D15 … D0 (read data) <sup>1)</sup> | <i>t</i> <sub>31</sub> SR | -4        |        | -    | ns   |      |

Read data are latched with the same internal clock edge that triggers the address change and the rising edge of RD. Address changes before the end of RD have no impact on (demultiplexed) read cycles. Read data can change after the rising edge of RD.

# XC2287 / XC2286 / XC2285 XC2000 Family Derivatives

#### **Electrical Parameters**

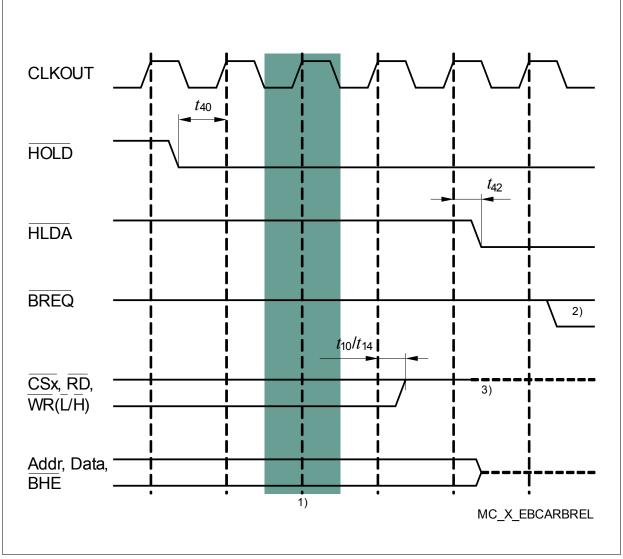

Figure 25 External Bus Arbitration, Releasing the Bus

#### Notes

- 1. The XC228x completes the currently running bus cycle before granting bus access.

- 2. This is the first possibility for  $\overline{BREQ}$  to get active.

- 3. The control outputs will be resistive high (pull-up) after being driven inactive (ALE will be low).

# 4.6.6 JTAG Interface Timing

The following parameters are applicable for communication through the JTAG debug interface. The JTAG module is fully compliant with IEEE1149.1-2000.

*Note:* These parameters are not subject to production test but verified by design and/or characterization.

| Parameter                                                       | Symbol                    |      | Values |      |    | Note /                 |

|-----------------------------------------------------------------|---------------------------|------|--------|------|----|------------------------|

|                                                                 |                           | Min. | Тур.   | Max. |    | Test Condition         |

| TCK clock period                                                | t <sub>1</sub> SR         | 60   | 50     | _    | ns | -                      |

| TCK high time                                                   | $t_2$ SR                  | 16   | _      | _    | ns | -                      |

| TCK low time                                                    | t <sub>3</sub> SR         | 16   | _      | _    | ns | -                      |

| TCK clock rise time                                             | t <sub>4</sub> SR         | _    | _      | 8    | ns | -                      |

| TCK clock fall time                                             | t <sub>5</sub> SR         | _    | _      | 8    | ns | -                      |

| TDI/TMS setup<br>to TCK rising edge                             | t <sub>6</sub> SR         | 6    | -      | -    | ns | -                      |

| TDI/TMS hold<br>after TCK rising edge                           | t <sub>7</sub> SR         | 6    | -      | -    | ns | -                      |

| TDO valid                                                       | t <sub>8</sub> CC         | _    | _      | 30   | ns | C <sub>L</sub> = 50 pF |

| after TCK falling edge <sup>1)</sup>                            | t <sub>8</sub> CC         | 10   | _      | _    | ns | C <sub>L</sub> = 20 pF |

| TDO high imped. to valid from TCK falling edge <sup>1)2)</sup>  | t <sub>9</sub> CC         | -    | -      | 30   | ns | C <sub>L</sub> = 50 pF |

| TDO valid to high imped.<br>from TCK falling edge <sup>1)</sup> | <i>t</i> <sub>10</sub> CC | -    | -      | 30   | ns | C <sub>L</sub> = 50 pF |

# Table 35JTAG Interface Timing Parameters<br/>(Operating Conditions apply)

1) The falling edge on TCK is used to generate the TDO timing.

2) The setup time for TDO is given implicitly by the TCK cycle time.