Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detailo                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | e200z0h                                                      |

| Core Size                  | 32-Bit Single-Core                                           |

| Speed                      | 64MHz                                                        |

| Connectivity               | CANbus, LINbus, SCI, SPI                                     |

| Peripherals                | DMA, POR, PWM, WDT                                           |

| Number of I/O              | 79                                                           |

| Program Memory Size        | 192KB (192K x 8)                                             |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 4K x 16                                                      |

| RAM Size                   | 12K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                    |

| Data Converters            | A/D 16x10b                                                   |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 100-LQFP                                                     |

| Supplier Device Package    | 100-LQFP (14x14)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=spc5601pef0mll6 |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

### 1.1 Document overview

This document provides electrical specifications, pin assignments, and package diagrams for the MPC5601P/2P series of microcontroller units (MCUs). It also describes the device features and highlights important electrical and physical characteristics. For functional characteristics, refer to the device reference manual.

## 1.2 Description

This 32-bit system-on-chip (SoC) automotive microcontroller family is the latest achievement in integrated automotive application controllers. It belongs to an expanding range of automotive-focused products designed to address chassis applications—specifically, electrical hydraulic power steering (EHPS) and electric power steering (EPS)—as well as airbag applications.

This family is one of a series of next-generation integrated automotive microcontrollers based on the Power Architecture<sup>®</sup> technology.

The advanced and cost-efficient host processor core of this automotive controller family complies with the Power Architecture embedded category. It operates at speeds of up to 64 MHz and offers high performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

## 1.3 Device comparison

Table 1 provides a summary of different members of the MPC5602P family and their features to enable a comparison among the family members and an understanding of the range of functionality offered within this family.

| Feature                                              | MPC5601P                 | MPC5602P                        |

|------------------------------------------------------|--------------------------|---------------------------------|

| Code flash memory (with ECC)                         | 192 KB                   | 256 KB                          |

| Data flash memory / EE option (with ECC)             | 64 KB (optic             | onal feature)                   |

| SRAM (with ECC)                                      | 12 KB                    | 20 KB                           |

| Processor core                                       | 32-bit e                 | 200z0h                          |

| Instruction set                                      | VLE (variable le         | ength encoding)                 |

| CPU performance                                      | 0–64                     | MHz                             |

| FMPLL (frequency-modulated phase-locked loop) module | ,                        | 1                               |

| INTC (interrupt controller) channels                 | 12                       | 20                              |

| PIT (periodic interrupt timer)                       | 1 (with four 3           | 32-bit timers)                  |

| eDMA (enhanced direct memory access) channels        | 1                        | 6                               |

| FlexCAN (controller area network)                    | 1 <sup>1,2</sup>         | 2 <sup>1,2</sup>                |

| Safety port                                          | Yes (via FlexCAN module) | Yes (via second FlexCAN module) |

| FCU (fault collection unit)                          | Ye                       | es                              |

| CTU (cross triggering unit)                          | No                       | Yes                             |

| eTimer                                               | 1 (16-bit, 6             | channels)                       |

Table 1. MPC5602P device comparison

| Block                                         | Function                                                                                                                                                                                                                         |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pulse width modulator (FlexPWM)               | Contains four PWM submodules, each of which capable of controlling a single half-bridge power stage and two fault input channels                                                                                                 |

| Reset generation module<br>(MC_RGM)           | Centralizes reset sources and manages the device reset sequence of the device                                                                                                                                                    |

| Static random-access memory (SRAM)            | Provides storage for program code, constants, and variables                                                                                                                                                                      |

| System integration unit lite (SIUL)           | Provides control over all the electrical pad controls and up 32 ports with 16 bits of bidirectional, general-purpose input and output signals and supports up to 32 external interrupts with trigger event configuration         |

| System status and configuration module (SSCM) | Provides system configuration and status data (such as memory size and status, device mode and security status), device identification data, debug status port enable and selection, and bus and peripheral abort enable/disable |

| System timer module (STM)                     | Provides a set of output compare events to support AUTOSAR <sup>1</sup> and operating system tasks                                                                                                                               |

| System watchdog timer (SWT)                   | Provides protection from runaway code                                                                                                                                                                                            |

| Wakeup unit (WKPU)                            | Supports up to 18 external sources that can generate interrupts or wakeup events, of which 1 can cause non-maskable interrupt requests or wakeup events                                                                          |

#### Table 2. MPC5602P series block summary (continued)

AUTOSAR: AUTomotive Open System ARchitecture (see http://www.autosar.org)

### 1.5 Feature details

1

#### 1.5.1 High performance e200z0 core processor

The e200z0 Power Architecture core provides the following features:

- High performance e200z0 core processor for managing peripherals and interrupts

- Single issue 4-stage pipeline in-order execution 32-bit Power Architecture CPU

- Harvard architecture

- Variable length encoding (VLE), allowing mixed 16- and 32-bit instructions

- Results in smaller code size footprint

- Minimizes impact on performance

- Branch processing acceleration using lookahead instruction buffer

- Load/store unit

- 1-cycle load latency

- Misaligned access support

- No load-to-use pipeline bubbles

- Thirty-two 32-bit general purpose registers (GPRs)

- Separate instruction bus and load/store bus Harvard architecture

- Hardware vectored interrupt support

- · Reservation instructions for implementing read-modify-write constructs

- Long cycle time instructions, except for guarded loads, do not increase interrupt latency

- Extensive system development support through Nexus debug port

- Non-maskable interrupt support

### 1.5.2 Crossbar switch (XBAR)

The XBAR multi-port crossbar switch supports simultaneous connections between three master ports and three slave ports. The crossbar supports a 32-bit address bus width and a 32-bit data bus width.

The crossbar allows for two concurrent transactions to occur from any master port to any slave port; but one of those transfers must be an instruction fetch from internal flash memory. If a slave port is simultaneously requested by more than one master port, arbitration logic will select the higher priority master and grant it ownership of the slave port. All other masters requesting that slave port will be stalled until the higher priority master completes its transactions. Requesting masters will be treated with equal priority and will be granted access a slave port in round-robin fashion, based upon the ID of the last master to be granted access.

The crossbar provides the following features:

- 3 master ports:

- e200z0 core complex instruction port

- e200z0 core complex Load/Store Data port

- eDMA

- 3 slave ports:

- Flash memory (Code and Data)

- SRAM

- Peripheral bridge

- 32-bit internal address, 32-bit internal data paths

- Fixed Priority Arbitration based on Port Master

- Temporary dynamic priority elevation of masters

### 1.5.3 Enhanced direct memory access (eDMA)

The enhanced direct memory access (eDMA) controller is a second-generation module capable of performing complex data movements via 16 programmable channels, with minimal intervention from the host processor. The hardware micro architecture includes a DMA engine which performs source and destination address calculations, and the actual data movement operations, along with an SRAM-based memory containing the transfer control descriptors (TCD) for the channels.

The eDMA module provides the following features:

- 16 channels support independent 8-, 16- or 32-bit single value or block transfers

- Supports variable-sized queues and circular queues

- · Source and destination address registers are independently configured to either post-increment or to remain constant

- Each transfer is initiated by a peripheral, CPU, or eDMA channel request

- Each eDMA channel can optionally send an interrupt request to the CPU on completion of a single value or block transfer

- DMA transfers possible between system memories, DSPIs, ADC, FlexPWM, eTimer and CTU

- Programmable DMA channel multiplexer allows assignment of any DMA source to any available DMA channel with as many as 30 request sources

- eDMA abort operation through software

### 1.5.4 Flash memory

The MPC5602P provides 320 KB of programmable, non-volatile, flash memory. The non-volatile memory (NVM) can be used for instruction and/or data storage. The flash memory module is interfaced to the system bus by a dedicated flash memory controller. It supports a 32-bit data bus width at the system bus port, and a 128-bit read data interface to flash memory. The module contains four 128-bit wide prefetch buffers. Prefetch buffer hits allow no-wait responses. Normal flash memory array accesses are registered and are forwarded to the system bus on the following cycle, incurring two wait-states.

| Port  | PCR      | Alternate                                   | Functions                                                 | Peripheral <sup>3</sup>                                    | I/O                             | Pad     | speed <sup>5</sup> | Р      | in      |

|-------|----------|---------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------|---------------------------------|---------|--------------------|--------|---------|

| pin   | register | function <sup>1,2</sup>                     | runctions                                                 | Peripheral                                                 | direction <sup>4</sup>          | SRC = 0 | SRC = 1            | 64-pin | 100-pin |

| A[8]  | PCR[8]   | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[8]<br>—<br>—<br>—<br>SIN                             | SIUL<br>—<br>—<br>DSPI_1                                   | I/O<br>—<br>—<br>—<br>I         | Slow    | Medium             | 4      | 6       |

| A[9]  | PCR[9]   | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | EIRQ[8]<br>GPIO[9]<br>CS1<br><br>B[3]<br>FAULT[0]         | SIUL<br>SIUL<br>DSPI_2<br><br>FlexPWM_0<br>FlexPWM_0       | <br> /O<br> <br> <br> <br> <br> | Slow    | Medium             | 60     | 94      |

| A[10] | PCR[10]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[10]<br>CS0<br>B[0]<br>X[2]<br>EIRQ[9]                | SIUL<br>DSPI_2<br>FlexPWM_0<br>FlexPWM_0<br>SIUL           | I/O<br>I/O<br>O<br>I            | Slow    | Medium             | 52     | 81      |

| A[11] | PCR[11]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[11]<br>SCK<br>A[0]<br>A[2]<br>EIRQ[10]               | SIUL<br>DSPI_2<br>FlexPWM_0<br>FlexPWM_0<br>SIUL           | I/O<br>I/O<br>O<br>I            | Slow    | Medium             | 53     | 82      |

| A[12] | PCR[12]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[12]<br>SOUT<br>A[2]<br>B[2]<br>EIRQ[11]              | SIUL<br>DSPI_2<br>FlexPWM_0<br>FlexPWM_0<br>SIUL           | I/O<br>O<br>O<br>I              | Slow    | Medium             | 54     | 83      |

| A[13] | PCR[13]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—<br>— | GPIO[13]<br>—<br>B[2]<br>—<br>SIN<br>FAULT[0]<br>EIRQ[12] | SIUL<br>—<br>FlexPWM_0<br>—<br>DSPI_2<br>FlexPWM_0<br>SIUL | /O<br><br>0<br><br>1<br>1<br>1  | Slow    | Medium             | 61     | 95      |

| A[14] | PCR[14]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[14]<br>TXD<br>—<br>—<br>EIRQ[13]                     | SIUL<br>Safety Port_0<br><br>SIUL                          | I/O<br>O<br><br>I               | Slow    | Medium             | 63     | 99      |

| A[15] | PCR[15]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[15]<br>—<br>—<br>—<br>RXD<br>EIRQ[14]                | SIUL<br>—<br>—<br>Safety Port_0<br>SIUL                    | I/O<br><br><br>                 | Slow    | Medium             | 64     | 100     |

Table 5. Pin muxing (continued)

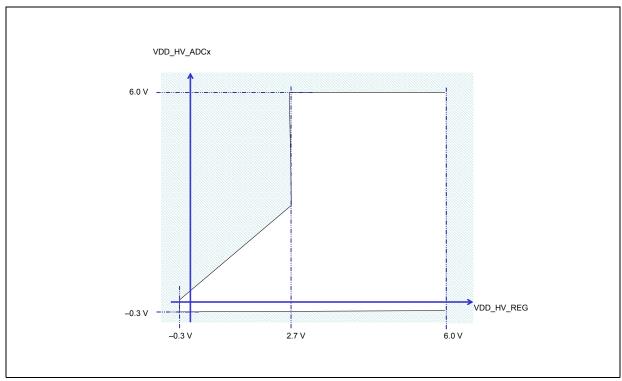

Figure 5. Independent ADC supply (–0.3 V  $\leq$  V\_{DD\_HV\_REG}  $\leq$  6.0 V)

## 3.4 Recommended operating conditions

| Symbol                              |    | Parameter                                               | Conditions                            | Val                         | ue                           | Unit |

|-------------------------------------|----|---------------------------------------------------------|---------------------------------------|-----------------------------|------------------------------|------|

| Symbol                              |    | Parameter                                               | Parameter Conditions                  |                             | Max <sup>1</sup>             | Unit |

| V <sub>SS</sub>                     | SR | Device ground                                           | —                                     | 0                           | 0                            | V    |

| V <sub>DD_HV_IOx</sub> <sup>2</sup> | SR | 5.0 V input/output supply voltage                       | _                                     | 4.5                         | 5.5                          | V    |

| V <sub>SS_HV_IOx</sub>              | SR | Input/output ground voltage                             | _                                     | 0                           | 0                            | V    |

| V <sub>DD_HV_OSC</sub>              | SR | 5.0 V crystal oscillator                                | —                                     | 4.5                         | 5.5                          | V    |

|                                     |    | amplifier supply voltage                                | Relative to<br>V <sub>DD_HV_IOx</sub> | $V_{DD_HV_IOx} - 0.1$       | $V_{DD_HV_IOx} + 0.1$        |      |

| V <sub>SS_HV_OSC</sub>              | SR | 5.0 V crystal oscillator<br>amplifier reference voltage |                                       | 0                           | 0                            | V    |

| V <sub>DD_HV_REG</sub>              | SR | 5.0 V voltage regulator                                 | —                                     | 4.5                         | 5.5                          | V    |

|                                     |    | supply voltage                                          | Relative to<br>V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> -0.1 | V <sub>DD_HV_IOx</sub> + 0.1 |      |

| V <sub>DD_HV_ADC0</sub>             | SR | 5.0 V ADC_0 supply and                                  | —                                     | 4.5                         | 5.5                          | V    |

|                                     |    | high reference voltage                                  | Relative to<br>V <sub>DD_HV_REG</sub> | V <sub>DD_HV_REG</sub> -0.1 | —                            |      |

| Symbol                                   |    | Parameter                                 | Conditions | Val | Unit             |      |

|------------------------------------------|----|-------------------------------------------|------------|-----|------------------|------|

| Symbol                                   |    | Parameter                                 | Conditions | Min | Max <sup>1</sup> | Onit |

| V <sub>SS_HV_ADC0</sub>                  |    | ADC_0 ground and low<br>reference voltage |            | 0   | 0                | V    |

| V <sub>DD_LV_REGCOR</sub> <sup>3,4</sup> | СС | Internal supply voltage                   | _          | —   | _                | V    |

| V <sub>SS_LV_REGCOR</sub> <sup>3</sup>   | SR | Internal reference voltage                | _          | 0   | 0                | V    |

| V <sub>DD_LV_CORx</sub> <sup>3,4</sup>   |    | Internal supply voltage                   | _          | —   | _                | V    |

| V <sub>SS_LV_CORx</sub> <sup>3</sup>     | SR | Internal reference voltage                |            | 0   | 0                | V    |

| T <sub>A</sub>                           | SR | Ambient temperature under bias            |            | -40 | 125              | °C   |

Table 9. Recommended operating conditions (3.3 V) (continued)

<sup>1</sup> Full functionality cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

<sup>2</sup> The difference between each couple of voltage supplies must be less than 100 mV,  $V_{DD_{-}HV_{-}IOy} - V_{DD_{-}HV_{-}IOx} | < 100 \text{ mV}.$

<sup>3</sup> To be connected to emitter of external NPN. Low voltage supplies are not under user control—they are produced by an on-chip voltage regulator—but for the device to function properly the low voltage grounds ( $V_{SS\_LV\_xxx}$ ) must be shorted to high voltage grounds ( $V_{SS\_HV\_xxx}$ ) and the low voltage supply pins ( $V_{DD\_LV\_xxx}$ ) must be connected to the external ballast emitter.

$^4~$  The low voltage supplies (V\_DD\_LV\_xxx) are not all independent.

$-V_{DD_LV_COR1}$  and  $V_{DD_LV_COR2}$  are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash memory module. Similarly,  $V_{SS_LV_COR1}$  and  $V_{SS_LV_COR2}$  are internally shorted.

$-V_{DD_LV\_REGCOR}$  and  $V_{DD_LV\_RECORx}$  are physically shorted internally, as are  $V_{SS\_LV\_REGCOR}$  and  $V_{SS\_LV\_CORx}$ .

## 3.5 Thermal characteristics

### 3.5.1 Package thermal characteristics

#### Table 10. LQFP thermal characteristics

| Symbol             | Parameter                                              | Conditions            | Туріса  | Unit                                                                                                |      |

|--------------------|--------------------------------------------------------|-----------------------|---------|-----------------------------------------------------------------------------------------------------|------|

| Cymbol             | i arameter                                             | Conditions            | 100-pin | Value           64-pin           57           41           22           13           22           1 | onic |

| $R_{\thetaJA}$     | Thermal resistance junction-to-ambient, natural        | Single layer board—1s | 63      | 57                                                                                                  | °C/W |

|                    | convection <sup>1</sup>                                | Four layer board—2s2p | 51      | 57<br>41<br>22<br>13                                                                                | °C/W |

| $R_{\theta J B}$   | Thermal resistance junction-to-board <sup>2</sup>      | Four layer board—2s2p | 33      | 22                                                                                                  | °C/W |

| $R_{\theta JCtop}$ | Thermal resistance junction-to-case (top) <sup>3</sup> | Single layer board—1s | 15      | 13                                                                                                  | °C/W |

| $\Psi_{JB}$        | Junction-to-board, natural convection <sup>4</sup>     | Operating conditions  | 33      | 22                                                                                                  | °C/W |

| $\Psi_{JC}$        | Junction-to-case, natural convection <sup>5</sup>      | Operating conditions  | 1       | 1                                                                                                   | °C/W |

<sup>1</sup> Junction-to-ambient thermal resistance determined per JEDEC JESD51-7. Thermal test board meets JEDEC specification for this package.

<sup>2</sup> Junction-to-board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package. When Greek letters are not available, the symbols are typed as RthJB or Theta-JB.

- <sup>3</sup> Junction-to-case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

- <sup>4</sup> Thermal characterization parameter indicating the temperature difference between the board and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

- <sup>5</sup> Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JC.

### 3.5.2 General notes for specifications at maximum junction temperature

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from Equation 1:

$$T_{J} = T_{A} + (R_{\theta JA} * P_{D}) \qquad \qquad Eqn. 1$$

where:

$T_A$  = ambient temperature for the package (°C)

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)

$P_D$  = power dissipation in the package (W)

The junction-to-ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed in Equation 2 as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA} \qquad \qquad Eqn. 2$$

## **3.6** Electromagnetic interference (EMI) characteristics

| Symbol           | Parameter                                      | Conditions                                                                                       | Clocks                                                                                                                                                                                                                                     | Frequency       | Level<br>(Typ)                                                                                                    | Unit |

|------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------|------|

| V <sub>EME</sub> | Radiated emissions                             | V <sub>DD</sub> = 5.0 V; T <sub>A</sub> = 25 °C                                                  | f <sub>OSC</sub> = 8 MHz                                                                                                                                                                                                                   | 150 kHz–150 MHz | (1yp)       z     11       13       M       z     8       12       N       z     9       12       M       z     7 | dBµV |

|                  |                                                | Other device configuration,                                                                      | device configuration,<br>onditions and EM testing<br>andard IEC61967-2<br>$f_{OSC} = 8 \text{ MHz}$ $f_{OPU} = 64 \text{ MHz}$ $f_{OPU} = 64 \text{ MHz}$ $f_{CPU} = 64 \text{ MHz}$ $f_{CPU} = 64 \text{ MHz}$ $f_{CPU} = 64 \text{ MHz}$ |                 | 13                                                                                                                |      |

|                  |                                                | test conditions and EM testing                                                                   |                                                                                                                                                                                                                                            |                 | М                                                                                                                 | —    |

|                  |                                                |                                                                                                  |                                                                                                                                                                                                                                            | 150 kHz–150 MHz | 8                                                                                                                 | dBµV |

|                  |                                                |                                                                                                  |                                                                                                                                                                                                                                            | 150–1000 MHz    | 12                                                                                                                |      |

|                  |                                                |                                                                                                  |                                                                                                                                                                                                                                            | IEC level       | Ν                                                                                                                 | —    |

|                  |                                                | 1                                                                                                | f <sub>OSC</sub> = 8 MHz<br>f <sub>CPU</sub> = 64 MHz<br>No PLL frequency                                                                                                                                                                  | 150 kHz–150 MHz | 9                                                                                                                 | dBµV |

|                  |                                                |                                                                                                  |                                                                                                                                                                                                                                            | 150–1000 MHz    | 12                                                                                                                |      |

|                  |                                                | test conditions and EM testing modulation<br>per standard IEC61967-2<br>f <sub>OSC</sub> = 8 MHz |                                                                                                                                                                                                                                            | IEC level       | М                                                                                                                 | —    |

|                  |                                                |                                                                                                  |                                                                                                                                                                                                                                            | 150 kHz–150 MHz | 7                                                                                                                 | dBµV |

|                  | f <sub>CPU</sub> = 64 MHz<br>±4% PLL frequency |                                                                                                  | 150–1000 MHz                                                                                                                                                                                                                               | 12              |                                                                                                                   |      |

|                  |                                                |                                                                                                  | modulation                                                                                                                                                                                                                                 | IEC level       | Ν                                                                                                                 | —    |

#### Table 11. EMI testing specifications

## 3.7 Electrostatic discharge (ESD) characteristics

#### Table 12. ESD ratings<sup>1,2</sup>

| Symbol                |    | Parameter                                      | Conditions | Value         | Unit |

|-----------------------|----|------------------------------------------------|------------|---------------|------|

| V <sub>ESD(HBM)</sub> | SR | Electrostatic discharge (Human Body Model)     | —          | 2000          | V    |

| V <sub>ESD(CDM)</sub> | SR | Electrostatic discharge (Charged Device Model) | —          | 750 (corners) | V    |

|                       |    |                                                |            | 500 (other)   |      |

<sup>1</sup> All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

<sup>2</sup> A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

### 3.8 Power management electrical characteristics

### 3.8.1 Voltage regulator electrical characteristics

The internal voltage regulator requires an external NPN ballast, approved ballast list availbale in Table 13, to be connected as shown in Figure 8. Capacitances should be placed on the board as near as possible to the associated pins. Care should also be taken to limit the serial inductance of the  $V_{DD \ HV \ REG}$  BCTRL and  $V_{DD \ LV \ CORx}$  pins to less than  $L_{Reg}$ . (refer to Table 14).

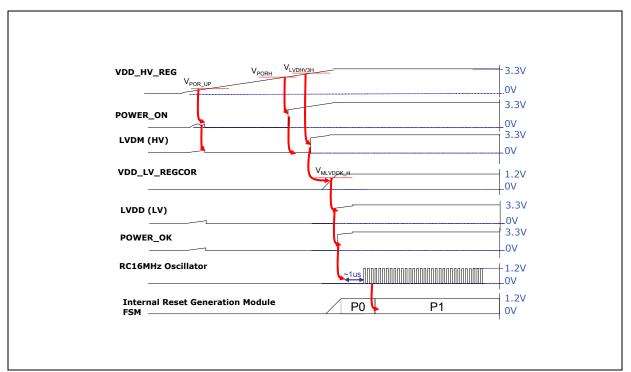

Figure 9. Power-up typical sequence

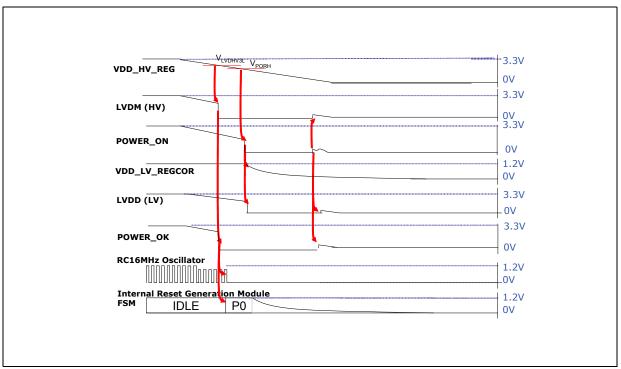

Figure 10. Power-down typical sequence

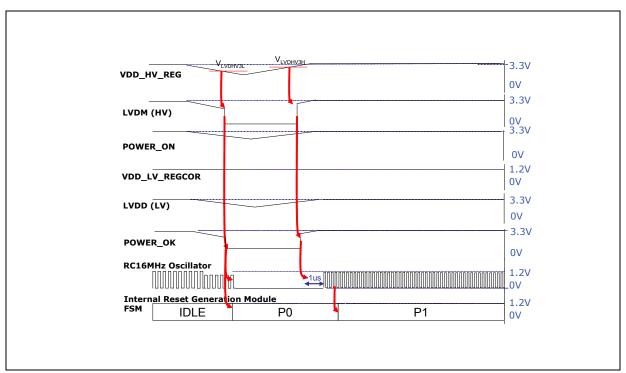

Figure 11. Brown-out typical sequence

## 3.10 DC electrical characteristics

### 3.10.1 NVUSRO register

Portions of the device configuration, such as high voltage supply and watchdog enable/disable after reset are controlled via bit values in the non-volatile user options (NVUSRO) register.

For a detailed description of the NVUSRO register, please refer to the device reference manual.

#### 3.10.1.1 NVUSRO[PAD3V5V] field description

The DC electrical characteristics are dependent on the PAD3V5V bit value. Table 16 shows how NVUSRO[PAD3V5V] controls the device configuration.

| Value <sup>1</sup> | Description                  |

|--------------------|------------------------------|

| 0                  | High voltage supply is 5.0 V |

| 1                  | High voltage supply is 3.3 V |

Table 16. PAD3V5V field description

Default manufacturing value before flash initialization is '1' (3.3 V).

### 3.10.2 DC electrical characteristics (5 V)

Table 17 gives the DC electrical characteristics at 5 V (4.5 V < V<sub>DD HV IOx</sub> < 5.5 V, NVUSRO[PAD3V5V] = 0).

## 3.10.3 DC electrical characteristics (3.3 V)

Table 19 gives the DC electrical characteristics at 3.3 V (3.0 V < V<sub>DD\_HV\_IOx</sub> < 3.6 V, NVUSRO[PAD3V5V] = 1); see Figure 12.

| Cumhal            | ~ | Deveneeter                                         | Conditions                        | Va                          | lue                         | 11   |

|-------------------|---|----------------------------------------------------|-----------------------------------|-----------------------------|-----------------------------|------|

| Symbol            | C | Parameter                                          | Conditions                        | Min                         | Max                         | Unit |

| V <sub>IL</sub>   | D | Low level input voltage                            | —                                 | -0.4 <sup>2</sup>           | —                           | V    |

|                   | Ρ |                                                    |                                   |                             | 0.35 V <sub>DD_HV_IOx</sub> | V    |

| V <sub>IH</sub>   | Ρ | High level input voltage                           | —                                 | 0.65 V <sub>DD_HV_IOx</sub> | —                           | V    |

|                   | D |                                                    | —                                 | —                           | $V_{DD_HV_IOx} + 0.4^2$     | V    |

| V <sub>HYS</sub>  | Т | Schmitt trigger hysteresis                         | —                                 | 0.1 V <sub>DD_HV_IOx</sub>  | —                           | V    |

| V <sub>OL_S</sub> | Ρ | Slow, low level output voltage                     | I <sub>OL</sub> = 1.5 mA          | —                           | 0.5                         | V    |

| $V_{OH_S}$        | Ρ | Slow, high level output voltage                    | I <sub>OH</sub> = -1.5 mA         | $V_{DD_HV_IOx} - 0.8$       | —                           | V    |

| $V_{OL_M}$        | Ρ | Medium, low level output voltage                   | I <sub>OL</sub> = 2 mA            | —                           | 0.5                         | V    |

| V <sub>OH_M</sub> | Ρ | Medium, high level output voltage                  | I <sub>OH</sub> = –2 mA           | $V_{DD_HV_IOx} - 0.8$       | —                           | V    |

| $V_{OL_F}$        | Ρ | Fast, low level output voltage                     | I <sub>OL</sub> = 11 mA           | —                           | 0.5                         | V    |

| V <sub>OH_F</sub> | Ρ | Fast, high level output voltage                    | I <sub>OH</sub> = -11 mA          | $V_{DD_HV_IOx} - 0.8$       | —                           | V    |

| I <sub>PU</sub>   | Ρ | Equivalent pull-up current                         | $V_{IN} = V_{IL}$                 | –130                        | —                           | μA   |

|                   |   |                                                    | V <sub>IN</sub> = V <sub>IH</sub> | —                           | -10                         |      |

| I <sub>PD</sub>   | Ρ | Equivalent pull-down current                       | $V_{IN} = V_{IL}$                 | 10                          | —                           | μA   |

|                   |   |                                                    | V <sub>IN</sub> = V <sub>IH</sub> | —                           | 130                         |      |

| IIL               | Ρ | Input leakage current (all<br>bidirectional ports) | $T_A = -40$ to 125 °C             | _                           | 1                           | μA   |

| IIL               | Ρ | Input leakage current (all ADC input-only ports)   | $T_A = -40$ to 125 °C             | _                           | 0.5                         | μA   |

| C <sub>IN</sub>   | D | Input capacitance                                  | —                                 | —                           | 10                          | pF   |

Table 19. DC electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)<sup>1</sup>

<sup>1</sup> These specifications are design targets and subject to change per device characterization.

$^2$  "SR" parameter values must not exceed the absolute maximum ratings shown in Table 7.

| Symbol                             |                        | с | Parameter                                                        | Conditions <sup>1</sup>                                     |                                               | Value |     |      | Unit |

|------------------------------------|------------------------|---|------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------|-------|-----|------|------|

|                                    |                        |   |                                                                  |                                                             |                                               | Min   | Тур | Max  | Unit |

| I <sub>SWTFST</sub> <sup>(2)</sup> | CC                     | D | for FAST                                                         | C <sub>L</sub> = 25 pF                                      | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     | _     | —   | 110  | mA   |

|                                    |                        |   | configuration                                                    |                                                             | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |       | _   | 50   |      |

| I <sub>RMSSLW</sub>                | I <sub>RMSSLW</sub> CC | D |                                                                  | C <sub>L</sub> = 25 pF, 2 MHz                               | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 | _     |     | 2.3  | mA   |

|                                    |                        |   |                                                                  | C <sub>L</sub> = 25 pF, 4 MHz                               |                                               |       |     | 3.2  |      |

|                                    |                        |   |                                                                  | C <sub>L</sub> = 100 pF, 2 MHz                              |                                               |       |     | 6.6  |      |

|                                    |                        |   |                                                                  | C <sub>L</sub> = 25 pF, 2 MHz                               | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _     |     | 1.6  |      |

|                                    |                        |   |                                                                  | C <sub>L</sub> = 25 pF, 4 MHz                               |                                               |       |     | 2.3  |      |

|                                    |                        |   |                                                                  | C <sub>L</sub> = 100 pF, 2 MHz                              |                                               | —     | —   | 4.7  |      |

| I <sub>RMSMED</sub> CC             | СС                     | D | Root medium square<br>I/O current for<br>MEDIUM<br>configuration | C <sub>L</sub> = 25 pF, 13 MHz                              | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 | —     |     | 6.6  | mA   |

|                                    |                        |   |                                                                  | C <sub>L</sub> = 25 pF, 40 MHz                              |                                               | —     | —   | 13.4 |      |

|                                    |                        |   |                                                                  | C <sub>L</sub> = 100 pF, 13 MHz                             |                                               | —     | —   | 18.3 |      |

|                                    |                        |   |                                                                  | C <sub>L</sub> = 25 pF, 13 MHz                              | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | —     | —   | 5    |      |

|                                    |                        |   |                                                                  | C <sub>L</sub> = 25 pF, 40 MHz                              |                                               | —     | —   | 8.5  |      |

|                                    |                        |   |                                                                  | C <sub>L</sub> = 100 pF, 13 MHz                             |                                               | —     | —   | 11   |      |

| I <sub>RMSFST</sub>                | CC                     | D |                                                                  | C <sub>L</sub> = 25 pF, 40 MHz                              | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 | —     |     | 22   | mA   |

|                                    |                        |   | I/O current for FAST<br>configuration                            | C <sub>L</sub> = 25 pF, 64 MHz                              |                                               | —     | —   | 33   |      |

|                                    |                        |   |                                                                  | C <sub>L</sub> = 100 pF, 40 MHz                             |                                               | —     | —   | 56   |      |

|                                    |                        |   |                                                                  | C <sub>L</sub> = 25 pF, 40 MHz                              | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | —     | —   | 14   |      |

|                                    |                        |   |                                                                  | C <sub>L</sub> = 25 pF, 64 MHz                              |                                               | _     | _   | 20   |      |

|                                    |                        |   |                                                                  | C <sub>L</sub> = 100 pF, 40 MHz                             |                                               | _     | _   | 35   |      |

| I <sub>AVGSEG</sub>                | SR                     | D | Sum of all the static                                            | nin a $\frac{33}{10} = 3.3 \text{ M} \pm 10\%$ PAD3//5/ = 1 |                                               | —     |     | 70   | mA   |

|                                    |                        |   | I/O current within a<br>supply segment                           |                                                             |                                               | —     | 65  |      |      |

| Table 22. | I/O | consumption | (continued) |

|-----------|-----|-------------|-------------|

|-----------|-----|-------------|-------------|

$\frac{1}{V_{DD}} = 3.3 \text{ V} \pm 10\% \text{ / } 5.0 \text{ V} \pm 10\%, \text{ } T_{A} = -40 \text{ to } 125 \text{ °C}, \text{ unless otherwise specified}$   $\frac{2}{Stated} \text{ maximum values represent peak consumption that lasts only a few ns during I/O transition.}$

#### 3.11 Main oscillator electrical characteristics

The MPC5602P provides an oscillator/resonator driver.

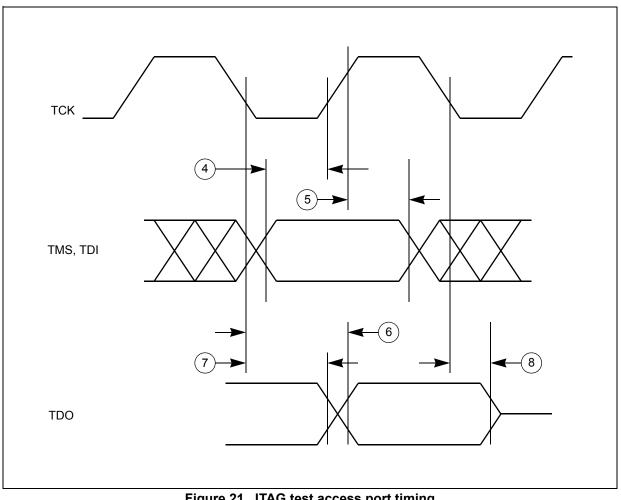

Figure 21. JTAG test access port timing

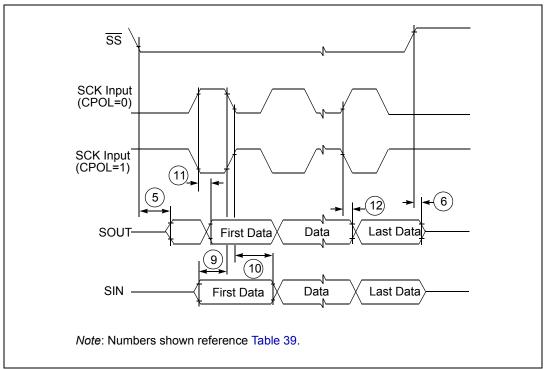

Figure 30. DSPI classic SPI timing – Slave, CPHA = 1

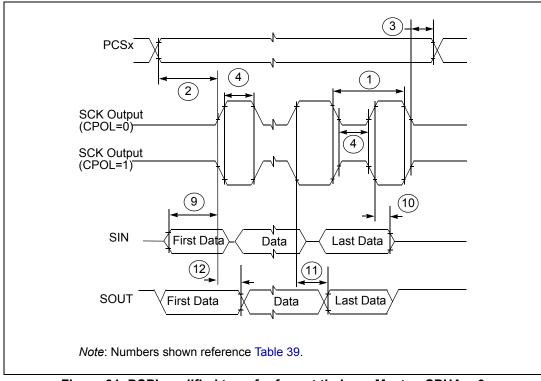

Figure 31. DSPI modified transfer format timing – Master, CPHA = 0

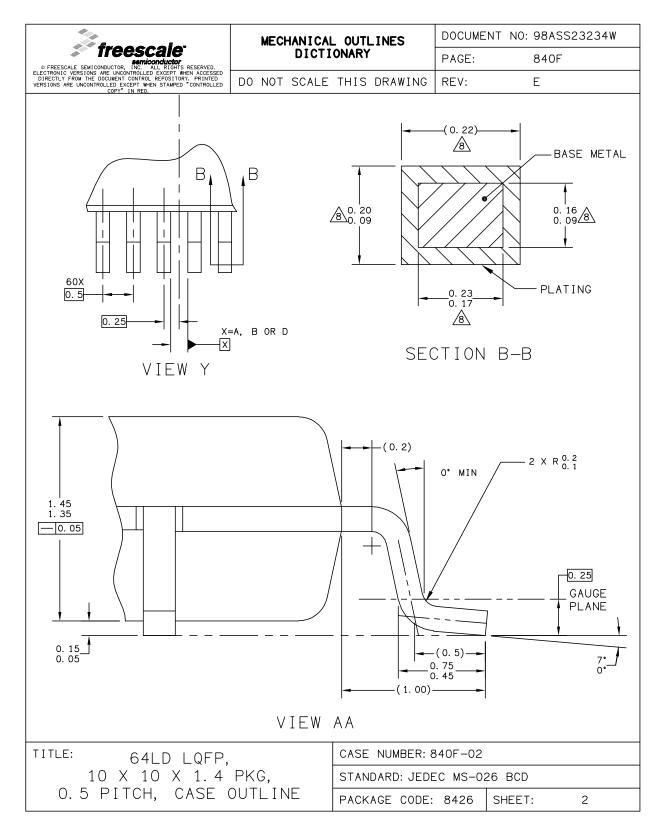

Figure 40. 64LQFP package mechanical drawing (part 2)

| OUTLINES<br>DNARY<br>THIS DRAWING<br>ASME Y14.5M-19<br>AT DATUM PLA<br>AT DATUM PLA<br>ATING PLANE C.<br>AMBAR PROTRUSI<br>AD WIDTH TO EX<br>ATERIAL CONDIT<br>FOOT. MINIMU<br>FOOT. MINIMU<br>FOOT. MINIMU<br>AND BE LESS<br>OLD PROTRUSION<br>ON IS MAXIMUM<br>CONAL.<br>SECTION OF T<br>IP. | ANE H.<br>ION. ALLOW<br>XCEED THE<br>TION. DAMB<br>JM SPACE B<br>THAN O. 07<br>N. ALLOWABL<br>PLASTIC B        | UPPER LIMIT<br>AR CANNOT BE<br>ETWEEN<br>mm.<br>E PROTRUSION<br>ODY SIZE                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| ASME Y14.5M-19<br>AT DATUM PLA<br>TING PLANE C.<br>MBAR PROTRUSI<br>D WIDTH TO EX<br>TERIAL CONDIT<br>FOOT. MINIMU<br>FOOT. MINIMU<br>NOT BE LESS<br>OLD PROTRUSION<br>ON IS MAXIMUM                                                                                                           | 994.<br>ANE H.<br>ION. ALLOW<br>XCEED THE<br>TION. DAMB<br>JM SPACE B<br>THAN 0.07<br>N. ALLOWABL<br>PLASTIC B | ABLE DAMBAR<br>UPPER LIMIT<br>AR CANNOT BE<br>ETWEEN<br>mm.<br>E PROTRUSION<br>ODY SIZE |

| AT DATUM PLA<br>ATING PLANE C.<br>AMBAR PROTRUSI<br>AD WIDTH TO EX<br>ATERIAL CONDIT<br>FOOT. MINIMU<br>FOOT. MINIMU<br>NOT BE LESS<br>OLD PROTRUSION<br>ON IS MAXIMUM                                                                                                                         | ANE H.<br>ION. ALLOW<br>XCEED THE<br>TION. DAMB<br>JM SPACE B<br>THAN O. 07<br>N. ALLOWABL<br>PLASTIC B        | UPPER LIMIT<br>AR CANNOT BE<br>ETWEEN<br>mm.<br>E PROTRUSION<br>ODY SIZE                |

| AT DATUM PLA<br>ATING PLANE C.<br>AMBAR PROTRUSI<br>AD WIDTH TO EX<br>ATERIAL CONDIT<br>FOOT. MINIMU<br>FOOT. MINIMU<br>NOT BE LESS<br>OLD PROTRUSION<br>ON IS MAXIMUM                                                                                                                         | ANE H.<br>ION. ALLOW<br>XCEED THE<br>TION. DAMB<br>JM SPACE B<br>THAN O. 07<br>N. ALLOWABL<br>PLASTIC B        | UPPER LIMIT<br>AR CANNOT BE<br>ETWEEN<br>mm.<br>E PROTRUSION<br>ODY SIZE                |

| AT DATUM PLA<br>ATING PLANE C.<br>AMBAR PROTRUSI<br>AD WIDTH TO EX<br>ATERIAL CONDIT<br>FOOT. MINIMU<br>FOOT. MINIMU<br>NOT BE LESS<br>OLD PROTRUSION<br>ON IS MAXIMUM                                                                                                                         | ANE H.<br>ION. ALLOW<br>XCEED THE<br>TION. DAMB<br>JM SPACE B<br>THAN O. 07<br>N. ALLOWABL<br>PLASTIC B        | UPPER LIMIT<br>AR CANNOT BE<br>ETWEEN<br>mm.<br>E PROTRUSION<br>ODY SIZE                |

| AT DATUM PLA<br>ATING PLANE C.<br>AMBAR PROTRUSI<br>AD WIDTH TO EX<br>ATERIAL CONDIT<br>FOOT. MINIMU<br>FOOT. MINIMU<br>NOT BE LESS<br>OLD PROTRUSION<br>ON IS MAXIMUM                                                                                                                         | ANE H.<br>ION. ALLOW<br>XCEED THE<br>TION. DAMB<br>JM SPACE B<br>THAN O. 07<br>N. ALLOWABL<br>PLASTIC B        | UPPER LIMIT<br>AR CANNOT BE<br>ETWEEN<br>mm.<br>E PROTRUSION<br>ODY SIZE                |

| ATING PLANE C.<br>MBAR PROTRUSI<br>ND WIDTH TO EX<br>TERIAL CONDIT<br>FOOT. MINIMU<br>NOT BE LESS<br>OLD PROTRUSION<br>N IS MAXIMUM                                                                                                                                                            | ION. ALLOW<br>XCEED THE<br>TION. DAMB<br>JM SPACE B<br>THAN 0.07<br>N. ALLOWABL<br>PLASTIC B                   | UPPER LIMIT<br>AR CANNOT BE<br>ETWEEN<br>mm.<br>E PROTRUSION<br>ODY SIZE                |

| MBAR PROTRUSI<br>ND WIDTH TO EX<br>TERIAL CONDIT<br>FOOT. MINIMU<br>NOT BE LESS<br>OLD PROTRUSION<br>N IS MAXIMUM                                                                                                                                                                              | ION. ALLOW<br>XCEED THE<br>TION. DAMB<br>JM SPACE B<br>THAN 0.07<br>N. ALLOWABL<br>PLASTIC B                   | UPPER LIMIT<br>AR CANNOT BE<br>ETWEEN<br>mm.<br>E PROTRUSION<br>ODY SIZE                |

| ON IS MAXIMUM<br>ONAL.<br>SECTION OF T                                                                                                                                                                                                                                                         | PLASTIC B                                                                                                      | ODY SIZE                                                                                |

| SECTION OF 1                                                                                                                                                                                                                                                                                   | THE LEAD B                                                                                                     | ETWEEN                                                                                  |

|                                                                                                                                                                                                                                                                                                | THE LEAD B                                                                                                     | ETWEEN                                                                                  |

| IP.                                                                                                                                                                                                                                                                                            |                                                                                                                |                                                                                         |

|                                                                                                                                                                                                                                                                                                |                                                                                                                |                                                                                         |

| CASE NUMBER: 8                                                                                                                                                                                                                                                                                 |                                                                                                                |                                                                                         |

|                                                                                                                                                                                                                                                                                                |                                                                                                                | CASE NUMBER: 840F-02<br>STANDARD: JEDEC MS-026                                          |

Figure 41. 64LQFP package mechanical drawing (part 3)

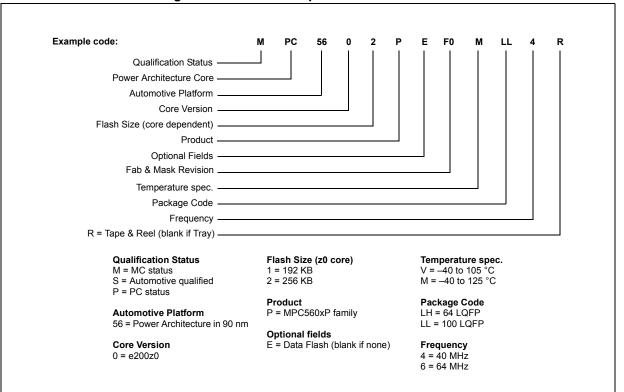

# 5 Ordering information

Figure 42. Commercial product code structure

# 6 Document revision history

Table 40 summarizes revisions to this document.

| Revision         | Date        | Description of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | 05 Aug 2009 | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2                | -           | Editorial updates<br>Editorial updates<br>Updated the following items in the "MPC5602P device comparison" table:<br>• The heading<br>• The "SRAM" row<br>• The "FlexAN" row<br>• The "FlexPWM" row<br>• The "LINFlex" row<br>• The "LINFlex" row<br>• The "DSPI" row<br>• Deleted the footnote No. 3<br>Added the "Wakeup unit" block in the MPC5602P block diagram<br>Updated the "Absolute Maximum Ratings" table<br>Updated the "Absolute Maximum Ratings" table<br>Updated the "Recommended operating conditions (5.0 V)" table<br>Updated the "EMI testing specifications" table: replaced all values in "Level (Max)"<br>column with TBD<br>Updated the "Electrical characteristics" section<br>• Added the "Introduction" section<br>• Added the "Independent ADC supply (-0.3 V $\leq V_{DD_{-}HV_{-}IOx} \leq 6.0$ V)" figure<br>• Added the "Independent ADC supply (-0.3 V $\leq V_{DD_{-}HV_{-}Rec} \leq 5.5$ V)" figure<br>• Added the "Independent ADC supply (0.0 V $\leq V_{DD_{-}HV_{-}Rec} \leq 5.5$ V)" figure<br>• Added the "Independent ADC supply (0.0 V $\leq V_{DD_{-}HV_{-}Rec} \leq 5.5$ V)" figure<br>• Added the "Independent ADC supply (0.0 V $\leq V_{DD_{-}HV_{-}Rec} \leq 5.5$ V)" figure<br>• Added the "Dc electrical characteristics" section<br>• Deleted the "Dc electrical characteristics " section<br>• Deleted the "DC electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)" section:<br>- Deleted all rows concerning RESET<br>- Deleted all rows concernin |

| 2<br>(continued) | 07 Apr 2010 | Added "Appendix A"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# Appendix A Abbreviations

Table A-1 lists abbreviations used in this document.

#### Table A-1. Abbreviations

| Abbreviation | Meaning                                 |

|--------------|-----------------------------------------|

| CMOS         | Complementary metal-oxide-semiconductor |

| СРНА         | Clock phase                             |

| CPOL         | Clock polarity                          |

| CS           | Peripheral chip select                  |

| DUT          | Device under test                       |

| ECC          | Error code correction                   |

| EVTO         | Event out                               |

| GPIO         | General purpose input / output          |

| MC           | Modulus counter                         |

| МСКО         | Message clock out                       |

| MCU          | Microcontroller unit                    |

| MDO          | Message data out                        |

| MSEO         | Message start/end out                   |

| MTFE         | Modified timing format enable           |

| NPN          | Negative-positive-negative              |

| NVUSRO       | Non-volatile user options register      |

| PTF          | Post trimming frequency                 |

| PWM          | Pulse width modulation                  |

| RISC         | Reduced instruction set computer        |

| SCK          | Serial communications clock             |

| SOUT         | Serial data out                         |

| ТВС          | To be confirmed                         |

| TBD          | To be defined                           |

| ТСК          | Test clock input                        |

| TDI          | Test data input                         |

| TDO          | Test data output                        |

| TMS          | Test mode select                        |