# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                 |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 64MHz                                                                   |

| Connectivity               | CANbus, LINbus, SCI, SPI                                                |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 79                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 16                                                                 |

| RAM Size                   | 20K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 16x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-LQFP                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5602pef0mll6 |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

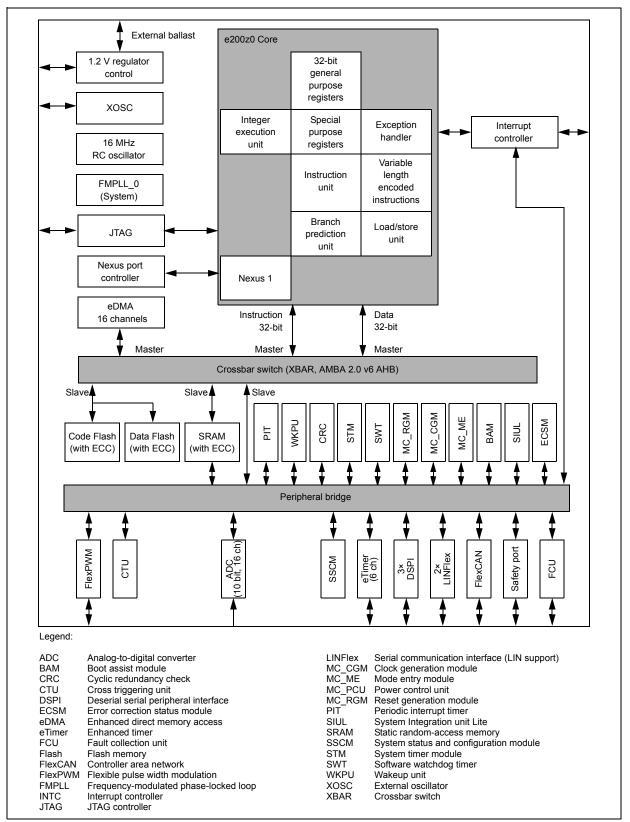

Figure 1. MPC5602P block diagram

- Frequency-modulated PLL

- Modulation enabled/disabled through software

- Triangle wave modulation

- Programmable modulation depth (±0.25% to ±4% deviation from center frequency): programmable modulation frequency dependent on reference frequency

- Self-clocked mode (SCM) operation

## 1.5.10 Main oscillator

The main oscillator provides these features:

- Input frequency range: 4–40 MHz

- Crystal input mode or oscillator input mode

- PLL reference

### 1.5.11 Internal RC oscillator

This device has an RC ladder phase-shift oscillator. The architecture uses constant current charging of a capacitor. The voltage at the capacitor is compared by the stable bandgap reference voltage.

The RC oscillator provides these features:

- Nominal frequency 16 MHz

- $\pm 5\%$  variation over voltage and temperature after process trim

- Clock output of the RC oscillator serves as system clock source in case loss of lock or loss of clock is detected by the PLL

- RC oscillator is used as the default system clock during startup

## 1.5.12 Periodic interrupt timer (PIT)

The PIT module implements these features:

- 4 general-purpose interrupt timers

- 32-bit counter resolution

- Clocked by system clock frequency

- Each channel usable as trigger for a DMA request

# 1.5.13 System timer module (STM)

The STM implements these features:

- One 32-bit up counter with 8-bit prescaler

- Four 32-bit compare channels

- Independent interrupt source for each channel

- Counter can be stopped in debug mode

## 1.5.14 Software watchdog timer (SWT)

The SWT has the following features:

- 32-bit time-out register to set the time-out period

- · Programmable selection of window mode or regular servicing

- Programmable transmit-first scheme: lowest ID or lowest buffer number

- Time stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Independent of the transmission medium (an external transceiver is assumed)

- High immunity to EMI

- · Short latency time due to an arbitration scheme for high-priority messages

- Transmit features

- Supports configuration of multiple mailboxes to form message queues of scalable depth

- Arbitration scheme according to message ID or message buffer number

- Internal arbitration to guarantee no inner or outer priority inversion

- Transmit abort procedure and notification

- Receive features

- Individual programmable filters for each mailbox

- 8 mailboxes configurable as a 6-entry receive FIFO

- 8 programmable acceptance filters for receive FIFO

- Programmable clock source

- System clock

- Direct oscillator clock to avoid PLL jitter

## 1.5.21 Safety port (FlexCAN)

The MPC5602P MCU has a second CAN controller synthesized to run at high bit rates to be used as a safety port. The CAN module of the safety port provides the following features:

- Identical to the FlexCAN module

- Bit rate up to 8 Mbit/s at 64 MHz CPU clock using direct connection between CAN modules (no physical transceiver required)

- 32 message buffers of up to 8-bytes data length

- Can be used as a second independent CAN module

### 1.5.22 Serial communication interface module (LINFlex)

The LINFlex (local interconnect network flexible) on the MPC5602P features the following:

- Supports LIN Master mode (both instances), LIN Slave mode (only one instance) and UART mode

- LIN state machine compliant to LIN1.3, 2.0 and 2.1 specifications

- Handles LIN frame transmission and reception without CPU intervention

- LIN features

- Autonomous LIN frame handling

- Message buffer to store Identifier and up to 8 data bytes

- Supports message length of up to 64 bytes

- Detection and flagging of LIN errors (sync field, delimiter, ID parity, bit framing, checksum, and time-out)

- Classic or extended checksum calculation

- Configurable Break duration of up to 36-bit times

- Programmable baud rate prescalers (13-bit mantissa, 4-bit fractional)

- Diagnostic features: Loop back; Self Test; LIN bus stuck dominant detection

- Interrupt-driven operation with 16 interrupt sources

- Clock frequency same as that used for e200z0h core

- PWM outputs can operate as complementary pairs or independent channels

- Can accept signed numbers for PWM generation

- Independent control of both edges of each PWM output

- · Synchronization to external hardware or other PWM supported

- Double buffered PWM registers

- Integral reload rates from 1 to 16

- Half cycle reload capability

- Multiple ADC trigger events can be generated per PWM cycle via hardware

- Write protection for critical registers

- Fault inputs can be assigned to control multiple PWM outputs

- Programmable filters for fault inputs

- Independently programmable PWM output polarity

- Independent top and bottom deadtime insertion

- Each complementary pair can operate with its own PWM frequency and deadtime values

- Individual software-control for each PWM output

- All outputs can be programmed to change simultaneously via a "Force Out" event

- PWMX pin can optionally output a third PWM signal from each submodule

- Channels not used for PWM generation can be used for buffered output compare functions

- Channels not used for PWM generation can be used for input capture functions

- Enhanced dual-edge capture functionality

- eDMA support with automatic reload

- 2 fault inputs

- · Capture capability for PWMA, PWMB, and PWMX channels not supported

#### 1.5.25 eTimer

The MPC5602P includes one eTimer module which provides six 16-bit general purpose up/down timer/counter units with the following features:

- Clock frequency same as that used for the e200z0h core

- Individual channel capability

- Input capture trigger

- Output compare

- Double buffer (to capture rising edge and falling edge)

- Separate prescaler for each counter

- Selectable clock source

- 0–100% pulse measurement

- Rotation direction flag (quad decoder mode)

- Maximum count rate

- External event counting: max. count rate = peripheral clock/2

- Internal clock counting: max. count rate = peripheral clock

- Counters are:

- Cascadable

- Preloadable

- Programmable count modulo

- Quadrature decode capabilities

| Port | PCR             | Alternate                                   | Functions                                                  | Peripheral <sup>3</sup>                                        | I/O                               | Pad s   | speed <sup>5</sup> | Р      | in      |  |

|------|-----------------|---------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------|---------|--------------------|--------|---------|--|

| pin  | register        | function <sup>1,2</sup>                     | Functions                                                  | Periprierai                                                    | direction <sup>4</sup>            | SRC = 0 | SRC = 1            | 64-pin | 100-pin |  |

|      | Port A (16-bit) |                                             |                                                            |                                                                |                                   |         |                    |        |         |  |

| A[0] | PCR[0]          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[0]<br>ETC[0]<br>SCK<br>F[0]<br>EIRQ[0]                | SIUL<br>eTimer_0<br>DSPI_2<br>FCU_0<br>SIUL                    | I/O<br>I/O<br>I/O<br>O<br>I       | Slow    | Medium             | _      | 51      |  |

| A[1] | PCR[1]          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[1]<br>ETC[1]<br>SOUT<br>F[1]<br>EIRQ[1]               | SIUL<br>eTimer_0<br>DSPI_2<br>FCU_0<br>SIUL                    | I/O<br>I/O<br>O<br>I              | Slow    | Medium             | _      | 52      |  |

| A[2] | PCR[2]          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—<br>— | GPIO[2]<br>ETC[2]<br>—<br>A[3]<br>SIN<br>ABS[0]<br>EIRQ[2] | SIUL<br>eTimer_0<br>—<br>FlexPWM_0<br>DSPI_2<br>MC_RGM<br>SIUL | /O<br> /O<br>—<br>0<br> <br> <br> | Slow    | Medium             | _      | 57      |  |

| A[3] | PCR[3]          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[3]<br>ETC[3]<br>CS0<br>B[3]<br>ABS[1]<br>EIRQ[3]      | SIUL<br>eTimer_0<br>DSPI_2<br>FlexPWM_0<br>MC_RGM<br>SIUL      | I/O<br>I/O<br>I/O<br>O<br>I<br>I  | Slow    | Medium             | 41     | 64      |  |

| A[4] | PCR[4]          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[4]<br>—<br>CS1<br>ETC[4]<br>FAB<br>EIRQ[4]            | SIUL<br>—<br>DSPI_2<br>eTimer_0<br>MC_RGM<br>SIUL              | I/O<br>—<br>0<br>I/O<br>I<br>I    | Slow    | Medium             | 48     | 75      |  |

| A[5] | PCR[5]          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[5]<br>CS0<br>—<br>CS7<br>EIRQ[5]                      | SIUL<br>DSPI_1<br><br>DSPI_0<br>SIUL                           | I/O<br>I/O<br>—<br>0<br>I         | Slow    | Medium             | 5      | 8       |  |

| A[6] | PCR[6]          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[6]<br>SCK<br>—<br>—<br>EIRQ[6]                        | SIUL<br>DSPI_1<br>—<br>SIUL                                    | I/O<br>I/O<br>—<br>I              | Slow    | Medium             | 2      | 2       |  |

| A[7] | PCR[7]          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[7]<br>SOUT<br>—<br>EIRQ[7]                            | SIUL<br>DSPI_1<br>—<br>SIUL                                    | I/O<br>O<br>—<br>I                | Slow    | Medium             | 3      | 4       |  |

Table 5. Pin muxing

| Port  | PCR      | Alternate                         | Functions                                   | Devin bevel <sup>3</sup>                     | I/O                                    | Pad     | speed <sup>5</sup> | Р        | in      |

|-------|----------|-----------------------------------|---------------------------------------------|----------------------------------------------|----------------------------------------|---------|--------------------|----------|---------|

| pin   | register | function <sup>1,2</sup>           | FUNCTIONS                                   | Peripheral <sup>3</sup>                      | direction <sup>4</sup>                 | SRC = 0 | SRC = 1            | 64-pin   | 100-pin |

| C[10] | PCR[42]  | ALT0<br>ALT1<br>ALT2              | GPIO[42]<br>CS2                             | SIUL<br>DSPI_2                               | I/O<br>O                               | Slow    | Medium             | —        | 78      |

|       |          | ALT3                              | A[3]<br>FAULT[1]                            | FlexPWM_0<br>FlexPWM_0                       | 0<br>                                  |         |                    |          |         |

| C[11] | PCR[43]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[43]<br>ETC[4]<br>CS2<br>—              | SIUL<br>eTimer_0<br>DSPI_2<br>—              | I/O<br>I/O<br>O<br>—                   | Slow    | Medium             | 33       | 55      |

| C[12] | PCR[44]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[44]<br>ETC[5]<br>CS3<br>—              | SIUL<br>eTimer_0<br>DSPI_2<br>—              | I/O<br>I/O<br>O                        | Slow    | Medium             | 34       | 56      |

| C[13] | PCR[45]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[45]<br>—<br>—<br>EXT_IN<br>EXT_SYNC    | SIUL<br>—<br>—<br>CTU_0<br>FlexPWM_0         | I/O<br>—<br>—<br>—<br>—<br>—<br>—<br>— | Slow    | Medium             | _        | 71      |

| C[14] | PCR[46]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[46]<br>—<br>EXT_TGR<br>—               | SIUL<br>—<br>CTU_0<br>—                      | I/O<br>—<br>—<br>—                     | Slow    | Medium             | —        | 72      |

| C[15] | PCR[47]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[47]<br>—<br>A[1]<br>EXT_IN<br>EXT_SYNC | SIUL<br>—<br>FlexPWM_0<br>CTU_0<br>FlexPWM_0 | I/O<br>—<br>—<br>0<br>I<br>I           | Slow    | Medium             | _        | 85      |

|       | 1        |                                   |                                             | Port D (16-                                  | -bit)                                  |         |                    | <u> </u> |         |

| D[0]  | PCR[48]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[48]<br>—<br>—<br>B[1]                  | SIUL<br>—<br>—<br>FlexPWM_0                  | I/O<br>—<br>—<br>—                     | Slow    | Medium             | —        | 86      |

| D[1]  | PCR[49]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[49]<br>—<br>EXT_TRG                    | SIUL<br>—<br><br>CTU_0                       | I/O<br>—<br>—<br>O                     | Slow    | Medium             | _        | 3       |

| D[2]  | PCR[50]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[50]<br>—<br>—<br>X[3]                  | SIUL<br>—<br><br>FlexPWM_0                   | I/O<br>—<br>—<br>O                     | Slow    | Medium             | _        | 97      |

| D[3]  | PCR[51]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[51]<br>—<br>—<br>A[3]                  | SIUL<br><br>FlexPWM_0                        | I/O<br>—<br>—<br>O                     | Slow    | Medium             |          | 89      |

Table 5. Pin muxing (continued)

| Port  | PCR      | Alternate                         | Functions                        | Peripheral <sup>3</sup>           | I/O                    | Pad     | speed <sup>5</sup> | Р      | in      |

|-------|----------|-----------------------------------|----------------------------------|-----------------------------------|------------------------|---------|--------------------|--------|---------|

| pin   | register | function <sup>1,2</sup>           | FUNCTIONS                        | Peripheral                        | direction <sup>4</sup> | SRC = 0 | SRC = 1            | 64-pin | 100-pin |

| D[4]  | PCR[52]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[52]<br>—<br>—<br>B[3]       | SIUL<br>—<br><br>FlexPWM_0        | I/O<br>—<br>—<br>O     | Slow    | Medium             | _      | 90      |

| D[5]  | PCR[53]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[53]<br>CS3<br>F[0]<br>—     | SIUL<br>DSPI_0<br>FCU_0<br>—      | I/O<br>O<br>O<br>—     | Slow    | Medium             | _      | 22      |

| D[6]  | PCR[54]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[54]<br>CS2<br>—<br>FAULT[1] | SIUL<br>DSPI_0<br>—<br>FlexPWM_0  | I/O<br>O<br>—<br>I     | Slow    | Medium             | _      | 23      |

| D[7]  | PCR[55]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[55]<br>CS3<br>F[1]<br>CS4   | SIUL<br>DSPI_1<br>FCU_0<br>DSPI_0 | I/O<br>O<br>O<br>O     | Slow    | Medium             | 17     | 26      |

| D[8]  | PCR[56]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[56]<br>CS2<br>—<br>CS5      | SIUL<br>DSPI_1<br><br>DSPI_0      | I/O<br>O<br>—<br>O     | Slow    | Medium             | 14     | 21      |

| D[9]  | PCR[57]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[57]<br>X[0]<br>TXD<br>—     | SIUL<br>FlexPWM_0<br>LIN_1<br>—   | I/O<br>O<br>O          | Slow    | Medium             | 8      | 15      |

| D[10] | PCR[58]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[58]<br>A[0]<br>—            | SIUL<br>FlexPWM_0<br>—            | I/O<br>O<br>—          | Slow    | Medium             | _      | 53      |

| D[11] | PCR[59]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[59]<br>B[0]<br>—            | SIUL<br>FlexPWM_0<br>—            | I/O<br>O<br>—          | Slow    | Medium             | _      | 54      |

| D[12] | PCR[60]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[60]<br>X[1]<br>—<br>RXD     | SIUL<br>FlexPWM_0<br><br>LIN_1    | I/O<br>O<br>—<br>I     | Slow    | Medium             | 45     | 70      |

| D[13] | PCR[61]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[61]<br>A[1]<br>—<br>—       | SIUL<br>FlexPWM_0<br>—            | I/O<br>O<br>—          | Slow    | Medium             | 44     | 67      |

| D[14] | PCR[62]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[62]<br>B[1]<br>—<br>—       | SIUL<br>FlexPWM_0<br>—            | I/O<br>O<br>—          | Slow    | Medium             | 46     | 73      |

Table 5. Pin muxing (continued)

| Port  | PCR      | Alternate                         | Functions                                  | Derinherel <sup>3</sup>                            | I/O                                | Pad | speed <sup>5</sup> | Р      | in      |

|-------|----------|-----------------------------------|--------------------------------------------|----------------------------------------------------|------------------------------------|-----|--------------------|--------|---------|

| pin   | register | function <sup>1,2</sup>           | Functions                                  | Peripheral <sup>3</sup>                            | direction <sup>4</sup> SRC = 0 SRC |     | SRC = 1            | 64-pin | 100-pin |

| D[15] | PCR[63]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[63]<br>—<br>—<br>AN[10]<br>emu. AN[4] | SIUL<br>—<br>—<br>ADC_0<br>emu. ADC_1 <sup>6</sup> | Input only                         | _   | _                  | _      | 41      |

|       |          |                                   |                                            | Port E (16-                                        | ·bit)                              |     |                    | 1      |         |

| E[1]  | PCR[65]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[65]<br>—<br>—<br>—<br>AN[4]           | SIUL<br>—<br>—<br>—<br>ADC_0                       | Input only                         | _   | _                  | 18     | 27      |

| E[2]  | PCR[66]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[66]<br>—<br>—<br>—<br>AN[5]           | SIUL<br>—<br>—<br>ADC_0                            | Input only                         | _   | _                  | 23     | 32      |

| E[3]  | PCR[67]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[67]<br>—<br>—<br>—<br>AN[6]           | SIUL<br>—<br>—<br>ADC_0                            | Input only                         |     | _                  | 30     | 42      |

| E[4]  | PCR[68]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[68]<br>—<br>—<br>—<br>AN[7]           | SIUL<br>—<br>—<br>—<br>ADC_0                       | Input only                         |     | _                  | _      | 44      |

| E[5]  | PCR[69]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[69]<br>—<br>—<br>—<br>AN[8]           | SIUL<br>—<br>—<br>—<br>ADC_0                       | Input only                         | _   | _                  | _      | 43      |

| E[6]  | PCR[70]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[70]<br>—<br>—<br>—<br>AN[9]           | SIUL<br>—<br>—<br>ADC_0                            | Input only                         | —   | _                  | _      | 45      |

| E[7]  | PCR[71]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[71]<br>—<br>—<br>—<br>AN[10]          | SIUL<br>—<br>—<br>ADC_0                            | Input only                         | —   | _                  | _      | 41      |

Table 5. Pin muxing (continued)

<sup>1</sup> ALT0 is the primary (default) function for each port after reset.

| Symbol                                   |    | Parameter                                 | Conditions | Val | ue               | Unit |  |

|------------------------------------------|----|-------------------------------------------|------------|-----|------------------|------|--|

| Symbol                                   |    | Parameter                                 | Conditions | Min | Max <sup>1</sup> |      |  |

| V <sub>SS_HV_ADC0</sub>                  |    | ADC_0 ground and low<br>reference voltage |            | 0   | 0                | V    |  |

| V <sub>DD_LV_REGCOR</sub> <sup>3,4</sup> | СС | Internal supply voltage                   | _          | —   | _                | V    |  |

| V <sub>SS_LV_REGCOR</sub> <sup>3</sup>   | SR | Internal reference voltage                | _          | 0   | 0                | V    |  |

| V <sub>DD_LV_CORx</sub> <sup>3,4</sup>   |    | Internal supply voltage                   | _          | —   | _                | V    |  |

| V <sub>SS_LV_CORx</sub> <sup>3</sup>     | SR | Internal reference voltage                |            | 0   | 0                | V    |  |

| T <sub>A</sub>                           | SR | Ambient temperature under bias            |            | -40 | 125              | °C   |  |

Table 9. Recommended operating conditions (3.3 V) (continued)

<sup>1</sup> Full functionality cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

<sup>2</sup> The difference between each couple of voltage supplies must be less than 100 mV,  $V_{DD_{-}HV_{-}IOy} - V_{DD_{-}HV_{-}IOx} | < 100 \text{ mV}.$

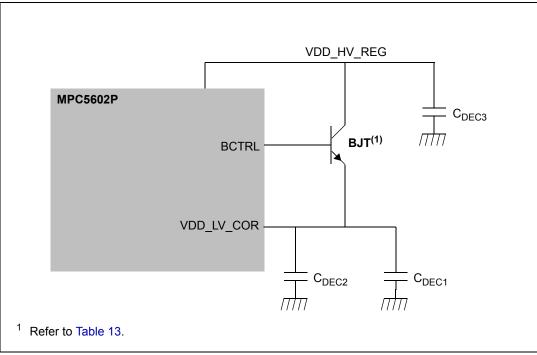

<sup>3</sup> To be connected to emitter of external NPN. Low voltage supplies are not under user control—they are produced by an on-chip voltage regulator—but for the device to function properly the low voltage grounds ( $V_{SS\_LV\_xxx}$ ) must be shorted to high voltage grounds ( $V_{SS\_HV\_xxx}$ ) and the low voltage supply pins ( $V_{DD\_LV\_xxx}$ ) must be connected to the external ballast emitter.

$^4~$  The low voltage supplies (V\_DD\_LV\_xxx) are not all independent.

$-V_{DD_LV_COR1}$  and  $V_{DD_LV_COR2}$  are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash memory module. Similarly,  $V_{SS_LV_COR1}$  and  $V_{SS_LV_COR2}$  are internally shorted.

$-V_{DD_LV\_REGCOR}$  and  $V_{DD_LV\_RECORx}$  are physically shorted internally, as are  $V_{SS\_LV\_REGCOR}$  and  $V_{SS\_LV\_CORx}$ .

where:

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  = junction-to-case thermal resistance (°C/W)

$R_{\theta CA}$  = case-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

To determine the junction temperature of the device in the application when heat sinks are not used, the Thermal Characterization Parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using Equation 3:

$$T_{J} = T_{T} + (\Psi_{JT} \times P_{D})$$

Eqn. 3

where:

$T_T$  = thermocouple temperature on top of the package (°C)

$\Psi_{JT}$  = thermal characterization parameter (°C/W)

$P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

References:

- Semiconductor Equipment and Materials International 3081 Zanker Road San Jose, CA 95134U.S.A. (408) 943-6900

- MIL-SPEC and EIA/JESD (JEDEC) specifications are available from Global Engineering Documents at (800) 854-7179 or (303) 397-7956.

- JEDEC specifications are available on the WEB at http://www.jedec.org.

- C.E. Triplett and B. Joiner, *An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module*, Proceedings of SemiTherm, San Diego, 1998, pp. 47–54.

- G. Kromann, S. Shidore, and S. Addison, *Thermal Modeling of a PBGA for Air-Cooled Applications*, Electronic Packaging and Production, pp. 53–58, March 1998.

- B. Joiner and V. Adams, *Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling*, Proceedings of SemiTherm, San Diego, 1999, pp. 212–220.

#### NOTE

The voltage regulator output cannot be used to drive external circuits. Output pins are to be used only for decoupling capacitance.

$V_{DD\_LV\_COR}$  must be generated using internal regulator and external NPN transistor. It is not possible to provide  $V_{DD\_LV\_COR}$  through external regulator.

For the MPC5602P microcontroller, capacitor(s), with total values not below  $C_{DEC1}$ , should be placed between  $V_{DD\_LV\_CORx}/V_{SS\_LV\_CORx}$  close to external ballast transistor emitter. 4 capacitors, with total values not below  $C_{DEC2}$ , should be placed close to microcontroller pins between each  $V_{DD\_LV\_CORx}/V_{SS\_LV\_CORx}$  supply pairs and the  $V_{DD\_LV\_REGCOR}/V_{SS\_LV\_REGCOR}$  pair . Additionally, capacitor(s) with total values not below  $C_{DEC3}$ , should be placed between the  $V_{DD\_HV\_REG}/V_{SS\_HV\_REG}$  pins close to ballast collector. Capacitors values have to take into account capacitor accuracy, aging and variation versus temperature.

All reported information are valid for voltage and temperature ranges described in recommended operating condition, Table 8 and Table 9.

Figure 8. Voltage regulator configuration

| Table 13. Approved NPM | I ballast components |

|------------------------|----------------------|

|------------------------|----------------------|

| Part  | Manufacturer | Approved derivatives <sup>1</sup> |

|-------|--------------|-----------------------------------|

| BCP68 | ON Semi      | BCP68                             |

|       | NXP          | BCP68-25                          |

|       | Infineon     | BCP68-25                          |

| BCX68 | Infineon     | BCX68-10; BCX68-16; BCX-25        |

| BC868 | NXP          | BC868                             |

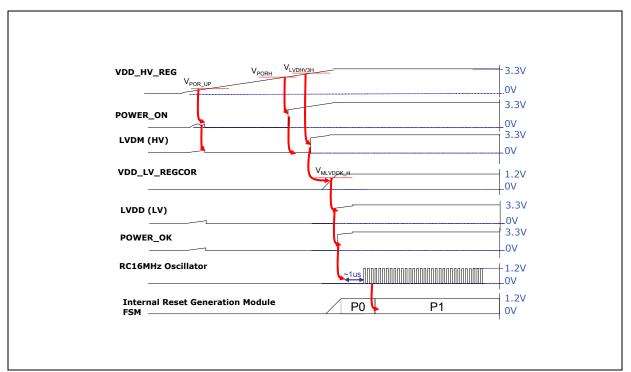

Figure 9. Power-up typical sequence

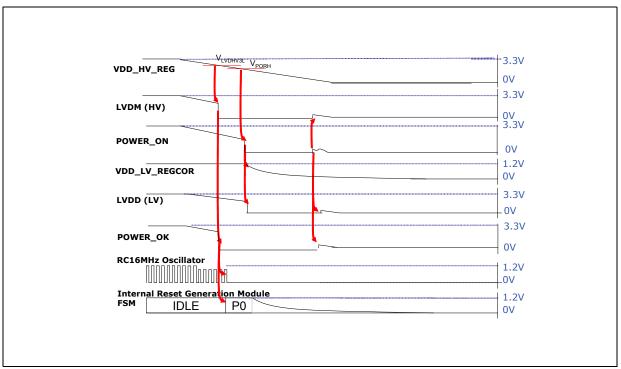

Figure 10. Power-down typical sequence

# 3.10.3 DC electrical characteristics (3.3 V)

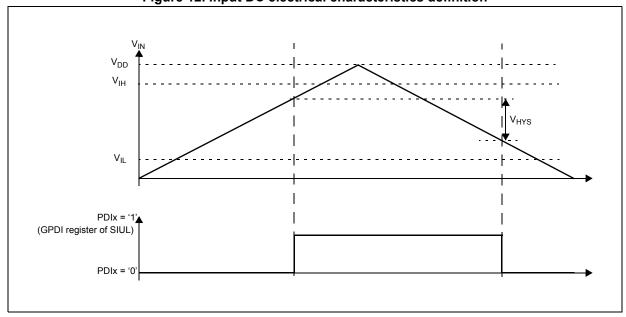

Table 19 gives the DC electrical characteristics at 3.3 V (3.0 V < V<sub>DD\_HV\_IOx</sub> < 3.6 V, NVUSRO[PAD3V5V] = 1); see Figure 12.

| Cumhal            | ~ | Deveneeter                                         | Conditions                        | Va                          | lue                         | 11   |

|-------------------|---|----------------------------------------------------|-----------------------------------|-----------------------------|-----------------------------|------|

| Symbol            | C | Parameter                                          | Conditions                        | Min                         | Max                         | Unit |

| V <sub>IL</sub>   | D | Low level input voltage                            | —                                 | -0.4 <sup>2</sup>           | —                           | V    |

|                   | Ρ |                                                    |                                   |                             | 0.35 V <sub>DD_HV_IOx</sub> | V    |

| V <sub>IH</sub>   | Ρ | High level input voltage                           | —                                 | 0.65 V <sub>DD_HV_IOx</sub> | —                           | V    |

|                   | D |                                                    | —                                 | —                           | $V_{DD_HV_IOx} + 0.4^2$     | V    |

| V <sub>HYS</sub>  | Т | Schmitt trigger hysteresis                         | —                                 | 0.1 V <sub>DD_HV_IOx</sub>  | —                           | V    |

| V <sub>OL_S</sub> | Ρ | Slow, low level output voltage                     | I <sub>OL</sub> = 1.5 mA          | —                           | 0.5                         | V    |

| $V_{OH_S}$        | Ρ | Slow, high level output voltage                    | I <sub>OH</sub> = -1.5 mA         | $V_{DD_HV_IOx} - 0.8$       | —                           | V    |

| $V_{OL_M}$        | Ρ | Medium, low level output voltage                   | I <sub>OL</sub> = 2 mA            | —                           | 0.5                         | V    |

| V <sub>OH_M</sub> | Ρ | Medium, high level output voltage                  | I <sub>OH</sub> = –2 mA           | $V_{DD_HV_IOx} - 0.8$       | —                           | V    |

| $V_{OL_F}$        | Ρ | Fast, low level output voltage                     | I <sub>OL</sub> = 11 mA           | —                           | 0.5                         | V    |

| V <sub>OH_F</sub> | Ρ | Fast, high level output voltage                    | I <sub>OH</sub> = -11 mA          | $V_{DD_HV_IOx} - 0.8$       | —                           | V    |

| I <sub>PU</sub>   | Ρ | Equivalent pull-up current                         | $V_{IN} = V_{IL}$                 | -130                        | —                           | μA   |

|                   |   |                                                    | V <sub>IN</sub> = V <sub>IH</sub> | —                           | -10                         |      |

| I <sub>PD</sub>   | Ρ | Equivalent pull-down current                       | $V_{IN} = V_{IL}$                 | 10                          | —                           | μA   |

|                   |   |                                                    | V <sub>IN</sub> = V <sub>IH</sub> | —                           | 130                         |      |

| IIL               | Ρ | Input leakage current (all<br>bidirectional ports) | $T_A = -40$ to 125 °C             | _                           | 1                           | μA   |

| IIL               | Ρ | Input leakage current (all ADC input-only ports)   | $T_A = -40$ to 125 °C             | _                           | 0.5                         | μA   |

| C <sub>IN</sub>   | D | Input capacitance                                  | —                                 | —                           | 10                          | pF   |

Table 19. DC electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)<sup>1</sup>

<sup>1</sup> These specifications are design targets and subject to change per device characterization.

$^2$  "SR" parameter values must not exceed the absolute maximum ratings shown in Table 7.

# 3.10.4 Input DC electrical characteristics definition

Figure 12 shows the DC electrical characteristics behavior as function of time.

## 3.10.5 I/O pad current specification

The I/O pads are distributed across the I/O supply segment. Each I/O supply segment is associated to a  $V_{DD}/V_{SS}$  supply pair as described in Table 21.

| Package  | Supply segment |             |             |             |             |  |  |  |

|----------|----------------|-------------|-------------|-------------|-------------|--|--|--|

| I ackage | 1              | 2           | 3           | 4           | 5           |  |  |  |

| 100 LQFP | pin15–pin26    | pin27–pin46 | pin51–pin61 | pin64–pin86 | pin89–pin10 |  |  |  |

| 64 LQFP  | pin8–pin17     | pin18–pin30 | pin33–pin38 | pin41–pin54 | pin57–pin5  |  |  |  |

Table 22. I/O consumption

| ſ | Symbol                             |    | с | Parameter     | Condi                  | itions <sup>1</sup>                           |     | Value |     | Unit |

|---|------------------------------------|----|---|---------------|------------------------|-----------------------------------------------|-----|-------|-----|------|

|   | Cymbol                             |    | Ŭ | i ununeter    | Conditions             |                                               | Min | Тур   | Max | ome  |

|   | I <sub>SWTSLW</sub> ,2             | СС |   | for SLOW      | C <sub>L</sub> = 25 pF | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 | _   | —     | 20  | mA   |

|   |                                    |    |   | configuration |                        | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _   | —     | 16  |      |

|   | I <sub>SWTMED</sub> <sup>(2)</sup> | СС |   | for MEDIUM    | C <sub>L</sub> = 25 pF | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 |     | —     | 29  | mA   |

|   |                                    |    |   | configuration |                        | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |     | —     | 17  |      |

Eqn. 11

12

$$\frac{V_A}{V_{A2}} = \frac{C_{P1} + C_{P2} + C_F}{C_{P1} + C_{P2} + C_F + C_S}$$

From this formula, in the worst case (when  $V_A$  is maximum, that is for instance 5 V), assuming to accept a maximum error of half a count, a constraint is evident on  $C_F$  value:

- <sup>6</sup> 20 MHz ADC clock. Specific prescaler is programmed on MC PLL CLK to provide 20 MHz clock to the ADC.

- <sup>7</sup> See Figure 14.

# 3.15 Flash memory electrical characteristics

## 3.15.1 Program/Erase characteristics

|                          |   |                                                              | Value |                  |                             |                  |      |

|--------------------------|---|--------------------------------------------------------------|-------|------------------|-----------------------------|------------------|------|

| Symbol                   | С | Parameter                                                    | Min   | Typ <sup>1</sup> | Initial<br>Max <sup>2</sup> | Max <sup>3</sup> | Unit |

| T <sub>wprogram</sub>    | Ρ | Word Program Time for data flash memory <sup>4</sup>         | _     | 30               | 70                          | 500              | μs   |

| T <sub>dwprogram</sub>   | Ρ | Double Word Program Time for code flash memory <sup>4</sup>  | —     | 22               | 50                          | 500              | μs   |

| T <sub>BKPRG</sub>       | Ρ | Bank Program (256 KB) <sup>4,5</sup>                         | _     | 0.73             | 0.83                        | 17.5             | S    |

|                          | Ρ | Bank Program (64 KB) <sup>4,5</sup>                          | —     | 0.49             | 1.2                         | 4.1              | S    |

| T <sub>16kpperase</sub>  | Ρ | 16 KB Block Pre-program and Erase Time for code flash memory | —     | 300              | 500                         | 5000             | ms   |

|                          |   | 16 KB Block Pre-program and Erase Time for data flash memory | —     | 700              | 800                         | 5000             |      |

| T <sub>32kpperase</sub>  | Ρ | 32 KB Block Pre-program and Erase Time                       | —     | 400              | 600                         | 5000             | ms   |

| T <sub>128kpperase</sub> | Ρ | 128 KB Block Pre-program and Erase Time                      | _     | 800              | 1300                        | 7500             | ms   |

| t <sub>ESRT</sub>        | Ρ | Program and erase specifications <sup>6</sup>                |       | —                | _                           | _                | ms   |

#### Table 29. Program and erase specifications

<sup>1</sup> Typical program and erase times assume nominal supply values and operation at 25 °C. All times are subject to change pending device characterization.

<sup>2</sup> Initial factory condition: < 100 program/erase cycles, 25 °C, typical supply voltage.

<sup>3</sup> The maximum program and erase times occur after the specified number of program/erase cycles. These maximum values are characterized but not guaranteed.

<sup>4</sup> Actual hardware programming times. This does not include software overhead.

<sup>5</sup> Typical Bank programming time assumes that all cells are programmed in a single pulse. In reality some cells will require more than one pulse, adding a small overhead to total bank programming time (see "Initial Max" column).

<sup>6</sup> Time between erase suspend resume and next erase suspend request.

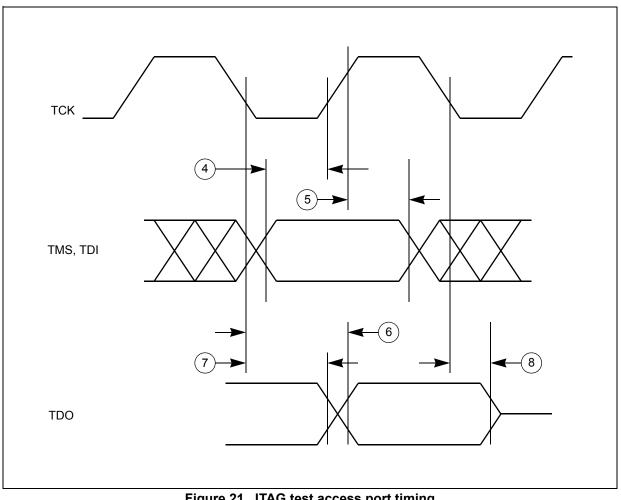

Figure 21. JTAG test access port timing

| No. | Symbol           |               | с | Parameter                   | Conditions                  | Va | Unit |    |

|-----|------------------|---------------|---|-----------------------------|-----------------------------|----|------|----|

| NO. |                  | i di difieter |   |                             | Max                         |    |      |    |

| 11  | t <sub>SUO</sub> | CC            | D | Data valid (after SCK edge) | Master (MTFE = 0)           |    | 12   | ns |

|     |                  |               |   |                             | Slave                       | _  | 36   |    |

|     |                  |               |   |                             | Master (MTFE = 1, CPHA = 0) | _  | 12   |    |

|     |                  |               |   |                             | Master (MTFE = 1, CPHA = 1) |    | 12   |    |

| 12  | t <sub>HO</sub>  | CC            | D | Data hold time for outputs  | Master (MTFE = 0)           | -2 | _    | ns |

|     |                  |               |   |                             | Slave                       | 6  | _    |    |

|     |                  |               |   |                             | Master (MTFE = 1, CPHA = 0) | 6  | _    |    |

|     |                  |               |   |                             | Master (MTFE = 1, CPHA = 1) | -2 |      |    |

Table 39. DSPI timing<sup>1</sup> (continued)

<sup>1</sup> All timing are provided with 50 pF capacitance on output, 1 ns transition time on input signal

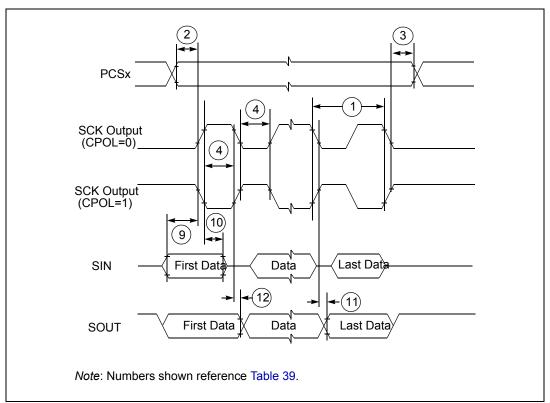

Figure 27. DSPI classic SPI timing – Master, CPHA = 0

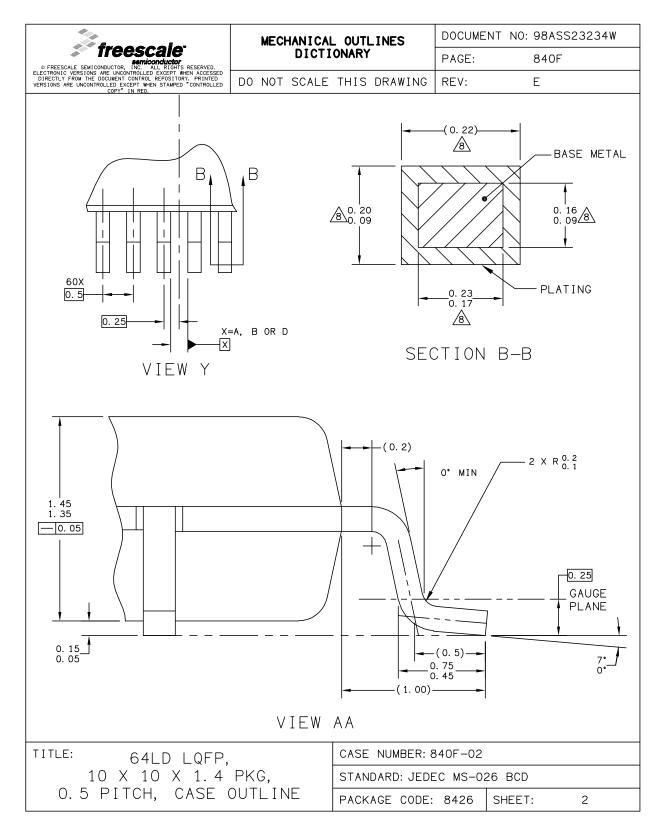

Figure 40. 64LQFP package mechanical drawing (part 2)

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.<br>LECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED                     |                                                                                                                                                                                                                                                                                                                                                      | LINES     |          | INT 1NO. 2 | 98ASS23234W |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|------------|-------------|--|--|

| ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED                                                                            | DICTIONAR                                                                                                                                                                                                                                                                                                                                            |           | PAGE:    | 8          | 340F        |  |  |

| DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED<br>VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED<br>COPY" IN RED. | DO NOT SCALE THIS                                                                                                                                                                                                                                                                                                                                    | DRAWING   | REV:     | E          | -           |  |  |

| NOTES:                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                      |           |          |            |             |  |  |

| 1. DIMENSIONS ARE IN MI                                                                                                              | IL IMETERS.                                                                                                                                                                                                                                                                                                                                          |           |          |            |             |  |  |

|                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                      | Y14.5M-19 | 994.     |            |             |  |  |

|                                                                                                                                      | DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.<br>DATUMS A, B AND D TO BE DETERMINED AT DATUM PLANE H.                                                                                                                                                                                                                                           |           |          |            |             |  |  |

| ^                                                                                                                                    | DIMENSIONS TO BE DETERMINED AT SEATING PLANE C.                                                                                                                                                                                                                                                                                                      |           |          |            |             |  |  |

| PROTRUSION SHALL NOT<br>BY MORE THAN 0.08 mr<br>LOCATED ON THE LOWEF                                                                 | THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR<br>PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE UPPER LIMIT<br>BY MORE THAN 0.08 mm AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE<br>LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN<br>PROTRUSION AND ADJACENT LEAD SHALL NOT BE LESS THAN 0.07 mm. |           |          |            |             |  |  |

| THIS DIMENSION DOES<br>IS 0.25 mm PER SIDE.<br>DIMENSION INCLUDING                                                                   | THIS DIMENSION IS                                                                                                                                                                                                                                                                                                                                    |           |          |            |             |  |  |

| $\triangle$ exact shape of each                                                                                                      | CORNER IS OPTIONAL                                                                                                                                                                                                                                                                                                                                   | -•        |          |            |             |  |  |

| A THESE DIMENSIONS APP<br>0.1 mm AND 0.25 mm F                                                                                       |                                                                                                                                                                                                                                                                                                                                                      | TION OF T | THE LEAD | D BETWE    | EN          |  |  |

|                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                      |           |          |            |             |  |  |

|                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                      |           | 340F-02  |            |             |  |  |

Figure 41. 64LQFP package mechanical drawing (part 3)