Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                    |

|--------------------------------|---------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | 1536                                                                      |

| Total RAM Bits                 | 18432                                                                     |

| Number of I/O                  | 71                                                                        |

| Number of Gates                | 60000                                                                     |

| Voltage - Supply               | 1.14V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                           |

| Package / Case                 | 100-TQFP                                                                  |

| Supplier Device Package        | 100-VQFP (14x14)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/agl060v2-vqg100 |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Flash Advantages

# Low Power

Flash-based IGLOO devices exhibit power characteristics similar to those of an ASIC, making them an ideal choice for power-sensitive applications. IGLOO devices have only a very limited power-on current surge and no high-current transition period, both of which occur on many FPGAs.

IGLOO devices also have low dynamic power consumption to further maximize power savings; power is even further reduced by the use of a 1.2 V core voltage.

Low dynamic power consumption, combined with low static power consumption and Flash\*Freeze technology, gives the IGLOO device the lowest total system power offered by any FPGA.

### Security

Nonvolatile, flash-based IGLOO devices do not require a boot PROM, so there is no vulnerable external bitstream that can be easily copied. IGLOO devices incorporate FlashLock, which provides a unique combination of reprogrammability and design security without external overhead, advantages that only an FPGA with nonvolatile flash programming can offer.

IGLOO devices utilize a 128-bit flash-based lock and a separate AES key to provide the highest level of protection in the FPGA industry for intellectual property and configuration data. In addition, all FlashROM data in IGLOO devices can be encrypted prior to loading, using the industry-leading AES-128 (FIPS192) bit block cipher encryption standard. AES was adopted by the National Institute of Standards and Technology (NIST) in 2000 and replaces the 1977 DES standard. IGLOO devices have a built-in AES decryption engine and a flash-based AES key that make them the most comprehensive programmable logic device security solution available today. IGLOO devices with AES-based security provide a high level of protection for remote field updates over public networks such as the Internet, and are designed to ensure that valuable IP remains out of the hands of system overbuilders, system cloners, and IP thieves.

Security, built into the FPGA fabric, is an inherent component of the IGLOO family. The flash cells are located beneath seven metal layers, and many device design and layout techniques have been used to make invasive attacks extremely difficult. The IGLOO family, with FlashLock and AES security, is unique in being highly resistant to both invasive and noninvasive attacks. Your valuable IP is protected with industry-standard security, making remote ISP possible. An IGLOO device provides the best available security for programmable logic designs.

# Single Chip

Flash-based FPGAs store their configuration information in on-chip flash cells. Once programmed, the configuration data is an inherent part of the FPGA structure, and no external configuration data needs to be loaded at system powerup (unlike SRAM-based FPGAs). Therefore, flash-based IGLOO FPGAs do not require system configuration components such as EEPROMs or microcontrollers to load device configuration data. This reduces bill-of-materials costs and PCB area, and increases security and system reliability.

# Instant On

Flash-based IGLOO devices support Level 0 of the Instant On classification standard. This feature helps in system component initialization, execution of critical tasks before the processor wakes up, setup and configuration of memory blocks, clock generation, and bus activity management. The Instant On feature of flash-based IGLOO devices greatly simplifies total system design and reduces total system cost, often eliminating the need for CPLDs and clock generation, and unlike SRAM-based FPGAs, the device will not have to be reloaded when system power is restored. This enables the reduction or complete removal of the configuration PROM, expensive voltage monitor, brownout detection, and clock generator devices from the PCB design. Flash-based IGLOO devices simplify total system design and reduce cost and design risk while increasing system reliability and improving system initialization time.

IGLOO flash FPGAs allow the user to quickly enter and exit Flash\*Freeze mode. This is done almost instantly (within 1 µs) and the device retains configuration and data in registers and RAM. Unlike SRAM-based FPGAs the device does not need to reload configuration and design state from external memory components; instead it retains all necessary information to resume operation immediately.

# Reduced Cost of Ownership

Advantages to the designer extend beyond low unit cost, performance, and ease of use. Unlike SRAM-based FPGAs, Flash-based IGLOO devices allow all functionality to be Instant On; no external boot PROM is required. On-board security mechanisms prevent access to all the programming information and enable secure remote updates of the FPGA logic. Designers can perform secure remote in-system reprogramming to support future design iterations and

### Figure 1-5 • I/O States During Programming Window

- 6. Click OK to return to the FlashPoint Programming File Generator window.

- Note: I/O States During programming are saved to the ADB and resulting programming files after completing programming file generation.

#### Table 2-27 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings Applicable to Standard I/O Banks

|                                                 |                   | Equivalent                                                      |              |           | VIL         | V <sub>IH</sub> |           | VOL         | V <sub>OH</sub> | I <sub>OL</sub> 1 | I <sub>OH</sub> 1 |

|-------------------------------------------------|-------------------|-----------------------------------------------------------------|--------------|-----------|-------------|-----------------|-----------|-------------|-----------------|-------------------|-------------------|

| I/O<br>Standard                                 | Drive<br>Strength | Software<br>Default<br>Drive<br>Strength<br>Option <sup>2</sup> | Slew<br>Rate | Min.<br>V | Max.<br>V   | Min.<br>V       | Max.<br>V | Max.<br>V   | Min.<br>V       | mA                | mA                |

| 3.3 V<br>LVTTL /<br>3.3 V<br>LVCMOS             | 8 mA              | 8 mA                                                            | High         | -0.3      | 0.8         | 2               | 3.6       | 0.4         | 2.4             | 8                 | 8                 |

| 3.3 V<br>LVCMOS<br>Wide<br>Range <sup>3</sup>   | 100 µA            | 8 mA                                                            | High         | -0.3      | 0.8         | 2               | 3.6       | 0.2         | VDD-0.2         | 0.1               | 0.1               |

| 2.5 V<br>LVCMOS                                 | 8 mA              | 8 mA                                                            | High         | -0.3      | 0.7         | 1.7             | 3.6       | 0.7         | 1.7             | 8                 | 8                 |

| 1.8 V<br>LVCMOS                                 | 4 mA              | 4 mA                                                            | High         | -0.3      | 0.35 * VCCI | 0.65 * VCCI     | 3.6       | 0.45        | VCCI – 0.45     | 4                 | 4                 |

| 1.5 V<br>LVCMOS                                 | 2 mA              | 2 mA                                                            | High         | -0.3      | 0.35 * VCCI | 0.65 * VCCI     | 3.6       | 0.25 * VCCI | 0.75 * VCCI     | 2                 | 2                 |

| 1.2 V<br>LVCMOS <sup>4</sup>                    | 1 mA              | 1 mA                                                            | High         | -0.3      | 0.35 * VCCI | 0.65 * VCCI     | 3.6       | 0.25 * VCCI | 0.75 * VCCI     | 1                 | 1                 |

| 1.2 V<br>LVCMOS<br>Wide<br>Range <sup>4,5</sup> | 100 µA            | 1 mA                                                            | High         | -0.3      | 0.3 * VCCI  | 0.7 * VCCI      | 3.6       | 0.1         | VCCI – 0.1      | 0.1               | 0.1               |

Notes:

1. Currents are measured at 85°C junction temperature.

2. The minimum drive strength for any LVCMOS 1.2 V or LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

3. All LVMCOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

4. Applicable to V2 Devices operating at VCCI  $\geq$  VCC.

5. All LVCMOS 1.2 V software macros support LVCMOS 1.2 V wide range as specified in the JESD8-12 specification.

# **Detailed I/O DC Characteristics**

### Table 2-37 • Input Capacitance

| Symbol          | Definition                         | Conditions           | Min. | Max. | Units |

|-----------------|------------------------------------|----------------------|------|------|-------|

| C <sub>IN</sub> | Input capacitance                  | VIN = 0, f = 1.0 MHz |      | 8    | pF    |

| CINCLK          | Input capacitance on the clock pin | VIN = 0, f = 1.0 MHz |      | 8    | pF    |

# Table 2-38 • I/O Output Buffer Maximum Resistances<sup>1</sup> Applicable to Advanced I/O Banks

| Standard                             | Drive Strength                 | R <sub>PULL-DOWN</sub><br>(Ω) <sup>2</sup> | R <sub>PULL-UP</sub><br>(Ω) <sup>3</sup> |

|--------------------------------------|--------------------------------|--------------------------------------------|------------------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS           | 2 mA                           | 100                                        | 300                                      |

|                                      | 4 mA                           | 100                                        | 300                                      |

|                                      | 6 mA                           | 50                                         | 150                                      |

|                                      | 8 mA                           | 50                                         | 150                                      |

|                                      | 12 mA                          | 25                                         | 75                                       |

|                                      | 16 mA                          | 17                                         | 50                                       |

|                                      | 24 mA                          | 11                                         | 33                                       |

| 3.3 V LVCMOS Wide Range              | 100 μA                         | Same as regular 3.3 V LVCMOS               | Same as regular 3.3 V LVCMOS             |

| 2.5 V LVCMOS                         | 2 mA                           | 100                                        | 200                                      |

|                                      | 4 mA                           | 100                                        | 200                                      |

|                                      | 6 mA                           | 50                                         | 100                                      |

|                                      | 8 mA                           | 50                                         | 100                                      |

|                                      | 12 mA                          | 25                                         | 50                                       |

|                                      | 16 mA                          | 20                                         | 40                                       |

| 1.5 V LVCMOS                         | 2 mA                           | 200                                        | 224                                      |

|                                      | 4 mA                           | 100                                        | 112                                      |

|                                      | 6 mA                           | 67                                         | 75                                       |

|                                      | 8 mA                           | 33                                         | 37                                       |

|                                      | 12 mA                          | 33                                         | 37                                       |

| 1.2 V LVCMOS <sup>4</sup>            | 2 mA                           | 158                                        | 164                                      |

| 1.2 V LVCMOS Wide Range <sup>4</sup> | 100 μA                         | Same as regular 1.2 V LVCMOS               | Same as regular 1.2 V LVCMOS             |

| 3.3 V PCI/PCI-X                      | Per PCI/PCI-X<br>specification | 25                                         | 75                                       |

Notes:

1. These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCCI, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located at http://www.microsemi.com/soc/download/ibis/default.aspx.

2. R<sub>(PULL-DOWN-MAX)</sub> = (VOLspec) / I<sub>OLspec</sub>

3. R<sub>(PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / I<sub>OHspec</sub>

4. Applicable to IGLOO V2 Devices operating at VCCI ≥ VCC

#### Table 2-54 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard Plus Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 0.97              | 2.32            | 0.18             | 0.85            | 0.66              | 2.37            | 1.90            | 1.98            | 2.13            | 5.96             | 5.49             | ns    |

| 4 mA           | Std.        | 0.97              | 2.32            | 0.18             | 0.85            | 0.66              | 2.37            | 1.90            | 1.98            | 2.13            | 5.96             | 5.49             | ns    |

| 6 mA           | Std.        | 0.97              | 1.94            | 0.18             | 0.85            | 0.66              | 1.99            | 1.57            | 2.20            | 2.53            | 5.58             | 5.16             | ns    |

| 8 mA           | Std.        | 0.97              | 1.94            | 0.18             | 0.85            | 0.66              | 1.99            | 1.57            | 2.20            | 2.53            | 5.58             | 5.16             | ns    |

| 12 mA          | Std.        | 0.97              | 1.75            | 0.18             | 0.85            | 0.66              | 1.79            | 1.40            | 2.36            | 2.79            | 5.38             | 4.99             | ns    |

| 16 mA          | Std.        | 0.97              | 1.75            | 0.18             | 0.85            | 0.66              | 1.79            | 1.40            | 2.36            | 2.79            | 5.38             | 4.99             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Table 2-55 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage<br/>Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V<br/>Applicable to Standard Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | Std.        | 0.97              | 3.80            | 0.18             | 0.83            | 0.66              | 3.88            | 3.41            | 1.74            | 1.78            | ns    |

| 4 mA           | Std.        | 0.97              | 3.80            | 0.18             | 0.83            | 0.66              | 3.88            | 3.41            | 1.74            | 1.78            | ns    |

| 6 mA           | Std.        | 0.97              | 3.15            | 0.18             | 0.83            | 0.66              | 3.21            | 2.94            | 1.96            | 2.17            | ns    |

| 8 mA           | Std.        | 0.97              | 3.15            | 0.18             | 0.83            | 0.66              | 3.21            | 2.94            | 1.96            | 2.17            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

#### Table 2-56 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

### Commercial-Case Conditions: $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | Std.        | 0.97              | 2.19            | 0.18             | 0.83            | 0.66              | 2.24            | 1.79            | 1.74            | 1.87            | ns    |

| 4 mA           | Std.        | 0.97              | 2.19            | 0.18             | 0.83            | 0.66              | 2.24            | 1.79            | 1.74            | 1.87            | ns    |

| 6 mA           | Std.        | 0.97              | 1.85            | 0.18             | 0.83            | 0.66              | 1.89            | 1.46            | 1.96            | 2.26            | ns    |

| 8 mA           | Std.        | 0.97              | 1.85            | 0.18             | 0.83            | 0.66              | 1.89            | 1.46            | 1.96            | 2.26            | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

| Parameter Name        | Parameter Definition                                            | Measuring Nodes<br>(from, to)* |  |  |

|-----------------------|-----------------------------------------------------------------|--------------------------------|--|--|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                          | HH, DOUT                       |  |  |

| tosud                 | Data Setup Time for the Output Data Register                    | FF, HH                         |  |  |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                     | FF, HH                         |  |  |

| tosue                 | Enable Setup Time for the Output Data Register                  | GG, HH                         |  |  |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                   | GG, HH                         |  |  |

| toclr2Q               | Asynchronous Clear-to-Q of the Output Data Register             | LL, DOUT                       |  |  |

| toremclr              | Asynchronous Clear Removal Time for the Output Data Register    | LL, HH                         |  |  |

| t <sub>ORECCLR</sub>  | Asynchronous Clear Recovery Time for the Output Data Register   | LL, HH                         |  |  |

| t <sub>oeclkq</sub>   | Clock-to-Q of the Output Enable Register                        | HH, EOUT                       |  |  |

| tOESUD                | Data Setup Time for the Output Enable Register                  | JJ, HH                         |  |  |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                   | JJ, HH                         |  |  |

| tOESUE                | Enable Setup Time for the Output Enable Register                | KK, HH                         |  |  |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                 | KK, HH                         |  |  |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register           | II, EOUT                       |  |  |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register  | II, HH                         |  |  |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register | II, HH                         |  |  |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                           | AA, EE                         |  |  |

| tISUD                 | Data Setup Time for the Input Data Register                     | CC, AA                         |  |  |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                      | CC, AA                         |  |  |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                   | BB, AA                         |  |  |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                    | BB, AA                         |  |  |

| t <sub>ICLR2Q</sub>   | Asynchronous Clear-to-Q of the Input Data Register              | DD, EE                         |  |  |

| t <sub>IREMCLR</sub>  | Asynchronous Clear Removal Time for the Input Data Register     | DD, AA                         |  |  |

| t <sub>IRECCLR</sub>  | Asynchronous Clear Recovery Time for the Input Data Register    | DD, AA                         |  |  |

### Table 2-156 • Parameter Definition and Measuring Nodes

Note: \*See Figure 2-17 on page 2-86 for more information.

### 1.2 V DC Core Voltage

### Table 2-165 • Input DDR Propagation Delays Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Parameter               | Description                                          | Std.   | Units |

|-------------------------|------------------------------------------------------|--------|-------|

| t <sub>DDRICLKQ1</sub>  | Clock-to-Out Out_QR for Input DDR                    | 0.76   | ns    |

| t <sub>DDRICLKQ2</sub>  | Clock-to-Out Out_QF for Input DDR                    | 0.94   | ns    |

| t <sub>DDRISUD1</sub>   | Data Setup for Input DDR (negedge)                   | 0.93   | ns    |

| t <sub>DDRISUD2</sub>   | Data Setup for Input DDR (posedge)                   | 0.84   | ns    |

| t <sub>DDRIHD1</sub>    | Data Hold for Input DDR (negedge)                    | 0.00   | ns    |

| t <sub>DDRIHD2</sub>    | Data Hold for Input DDR (posedge)                    | 0.00   | ns    |

| t <sub>DDRICLR2Q1</sub> | Asynchronous Clear-to-Out Out_QR for Input DDR       | 1.23   | ns    |

| t <sub>DDRICLR2Q2</sub> | Asynchronous Clear-to-Out Out_QF for Input DDR       | 1.42   | ns    |

| t <sub>DDRIREMCLR</sub> | Asynchronous Clear Removal Time for Input DDR        | 0.00   | ns    |

| t <sub>DDRIRECCLR</sub> | Asynchronous Clear Recovery Time for Input DDR       | 0.24   | ns    |

| t <sub>DDRIWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for Input DDR | 0.19   | ns    |

| t <sub>DDRICKMPWH</sub> | Clock Minimum Pulse Width High for Input DDR         | 0.31   | ns    |

| t <sub>DDRICKMPWL</sub> | Clock Minimum Pulse Width Low for Input DDR          | 0.28   | ns    |

| F <sub>DDRIMAX</sub>    | Maximum Frequency for Input DDR                      | 160.00 | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

### VJTAG JTAG Supply Voltage

Low power flash devices have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). Isolating the JTAG power supply in a separate I/O bank gives greater flexibility in supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned for use, the VJTAG pin together with the TRST pin could be tied to GND. It should be noted that VCC is required to be powered for JTAG operation; VJTAG alone is insufficient. If a device is in a JTAG chain of interconnected boards, the board containing the device can be powered down, provided both VJTAG and VCC to the part remain powered; otherwise, JTAG signals will not be able to transition the device, even in bypass mode.

Microsemi recommends that VPUMP and VJTAG power supplies be kept separate with independent filtering capacitors rather than supplying them from a common rail.

#### VPUMP Programming Supply Voltage

IGLOO devices support single-voltage ISP of the configuration flash and FlashROM. For programming, VPUMP should be 3.3 V nominal. During normal device operation, VPUMP can be left floating or can be tied (pulled up) to any voltage between 0 V and the VPUMP maximum. Programming power supply voltage (VPUMP) range is listed in the datasheet.

When the VPUMP pin is tied to ground, it will shut off the charge pump circuitry, resulting in no sources of oscillation from the charge pump circuitry.

For proper programming, 0.01  $\mu$ F and 0.33  $\mu$ F capacitors (both rated at 16 V) are to be connected in parallel across VPUMP and GND, and positioned as close to the FPGA pins as possible.

Microsemi recommends that VPUMP and VJTAG power supplies be kept separate with independent filtering capacitors rather than supplying them from a common rail.

# **User Pins**

#### I/O

#### User Input/Output

The I/O pin functions as an input, output, tristate, or bidirectional buffer. Input and output signal levels are compatible with the I/O standard selected.

During programming, I/Os become tristated and weakly pulled up to VCCI. With VCCI, VMV, and VCC supplies continuously powered up, when the device transitions from programming to operating mode, the I/Os are instantly configured to the desired user configuration.

Unused I/Os are configured as follows:

- Output buffer is disabled (with tristate value of high impedance)

- Input buffer is disabled (with tristate value of high impedance)

- Weak pull-up is programmed

#### GL Globals

GL I/Os have access to certain clock conditioning circuitry (and the PLL) and/or have direct access to the global network (spines). Additionally, the global I/Os can be used as regular I/Os, since they have identical capabilities. Unused GL pins are configured as inputs with pull-up resistors.

See more detailed descriptions of global I/O connectivity in the "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" chapter of the *IGLOO FPGA Fabric User Guide*. All inputs labeled GC/GF are direct inputs into the quadrant clocks. For example, if GAA0 is used for an input, GAA1 and GAA2 are no longer available for input to the quadrant globals. All inputs labeled GC/GF are direct inputs into the chip-level globals, and the rest are connected to the quadrant globals. The inputs to the global network are multiplexed, and only one input can be used as a global input.

Refer to the "I/O Structures in IGLOO and ProASIC3 Devices" chapter of the *IGLOO FPGA Fabric User Guide* for an explanation of the naming of global pins.

#### FF

#### Flash\*Freeze Mode Activation Pin

Flash\*Freeze mode is available on IGLOO devices. The FF pin is a dedicated input pin used to enter and exit Flash\*Freeze mode. The FF pin is active low, has the same characteristics as a single-ended I/O, and must meet the maximum rise and fall times. When Flash\*Freeze mode is not used in the design, the FF pin is available as a regular I/O.

When Flash\*Freeze mode is used, the FF pin must not be left floating to avoid accidentally entering Flash\*Freeze mode. While in Flash\*Freeze mode, the Flash\*Freeze pin should be constantly asserted.

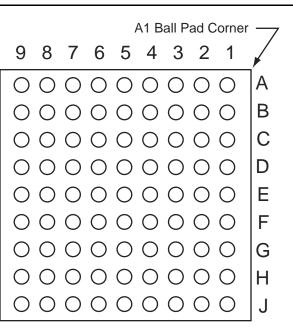

Note: This is the bottom view of the package.

# Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

|            | CS81            |            | CS81            |

|------------|-----------------|------------|-----------------|

| Pin Number | AGL030 Function | Pin Number | AGL030 Function |

| A1         | IO00RSB0        | E1         | GEB0/IO71RSE    |

| A2         | IO02RSB0        | E2         | GEA0/IO72RSE    |

| A3         | IO06RSB0        | E3         | GEC0/IO73RSE    |

| A4         | IO11RSB0        | E4         | VCCIB1          |

| A5         | IO16RSB0        | E5         | VCC             |

| A6         | IO19RSB0        | E6         | VCCIB0          |

| A7         | IO22RSB0        | E7         | GDC0/IO32RSE    |

| A8         | IO24RSB0        | E8         | GDA0/IO33RSE    |

| A9         | IO26RSB0        | E9         | GDB0/IO34RSE    |

| B1         | IO81RSB1        | F1         | IO68RSB1        |

| B2         | IO04RSB0        | F2         | IO67RSB1        |

| B3         | IO10RSB0        | F3         | IO64RSB1        |

| B4         | IO13RSB0        | F4         | GND             |

| B5         | IO15RSB0        | F5         | VCCIB1          |

| B6         | IO20RSB0        | F6         | IO47RSB1        |

| B7         | IO21RSB0        | F7         | IO36RSB0        |

| B8         | IO28RSB0        | F8         | IO38RSB0        |

| B9         | IO25RSB0        | F9         | IO40RSB0        |

| C1         | IO79RSB1        | G1         | IO65RSB1        |

| C2         | IO80RSB1        | G2         | IO66RSB1        |

| C3         | IO08RSB0        | G3         | IO57RSB1        |

| C4         | IO12RSB0        | G4         | IO53RSB1        |

| C5         | IO17RSB0        | G5         | IO49RSB1        |

| C6         | IO14RSB0        | G6         | IO44RSB1        |

| C7         | IO18RSB0        | G7         | IO46RSB1        |

| C8         | IO29RSB0        | G8         | VJTAG           |

| C9         | IO27RSB0        | G9         | TRST            |

| D1         | IO74RSB1        | H1         | IO62RSB1        |

| D2         | IO76RSB1        | H2         | FF/IO60RSB1     |

| D3         | IO77RSB1        | H3         | IO58RSB1        |

| D4         | VCC             | H4         | IO54RSB1        |

| D5         | VCCIB0          | H5         | IO48RSB1        |

| D6         | GND             | H6         | IO43RSB1        |

| D7         | IO23RSB0        | H7         | IO42RSB1        |

| D8         | IO31RSB0        | H8         | TDI             |

| D9         | IO30RSB0        | H9         | TDO             |

|            | CS81            |

|------------|-----------------|

| Pin Number | AGL030 Function |

| J1         | IO63RSB1        |

| J2         | IO61RSB1        |

| J3         | IO59RSB1        |

| J4         | IO56RSB1        |

| J5         | IO52RSB1        |

| J6         | IO45RSB1        |

| J7         | ТСК             |

| J8         | TMS             |

| J9         | VPUMP           |

Notes:

- 1. This is the bottom view of the package.

- 2. The die attach paddle center of the package is tied to ground (GND).

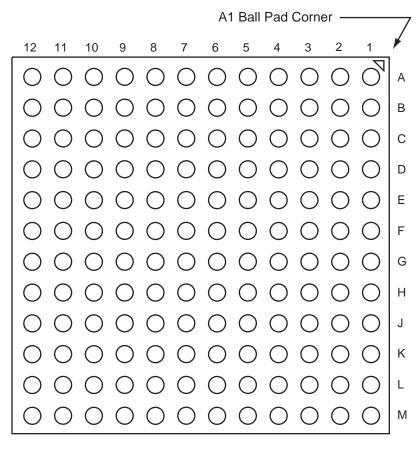

# Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

| (          | QN132           |

|------------|-----------------|

| Pin Number | AGL060 Function |

| C16        | IO60RSB1        |

| C17        | IO57RSB1        |

| C18        | NC              |

| C19        | ТСК             |

| C20        | VMV1            |

| C21        | VPUMP           |

| C22        | VJTAG           |

| C23        | VCCIB0          |

| C24        | NC              |

| C25        | NC              |

| C26        | GCA1/IO42RSB0   |

| C27        | GCC0/IO39RSB0   |

| C28        | VCCIB0          |

| C29        | IO29RSB0        |

| C30        | GNDQ            |

| C31        | GBA1/IO27RSB0   |

| C32        | GBB0/IO24RSB0   |

| C33        | VCC             |

| C34        | IO19RSB0        |

| C35        | IO16RSB0        |

| C36        | IO13RSB0        |

| C37        | GAC1/IO10RSB0   |

| C38        | NC              |

| C39        | GAA0/IO05RSB0   |

| C40        | VMV0            |

| D1         | GND             |

| D2         | GND             |

| D3         | GND             |

| D4         | GND             |

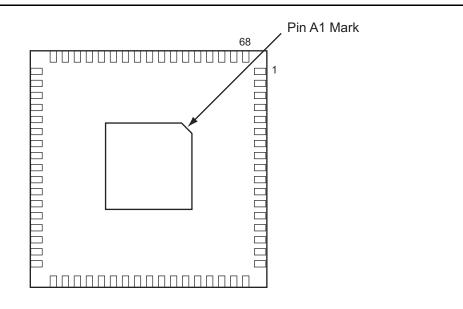

# FG144

Note: This is the bottom view of the package.

### Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

IGLOO Low Power Flash FPGAs

| FG144                      |                | FG144                      |                | FG144      |                            |  |

|----------------------------|----------------|----------------------------|----------------|------------|----------------------------|--|

| Pin Number AGL125 Function |                | Pin Number AGL125 Function |                | Pin Number | Pin Number AGL125 Function |  |

| A1                         | GNDQ           | D1                         | IO128RSB1      | G1         | GFA1/IO121RSB1             |  |

| A2                         | VMV0           | D2                         | IO129RSB1      | G2         | GND                        |  |

| A3                         | GAB0/IO02RSB0  | D3                         | IO130RSB1      | G3         | VCCPLF                     |  |

| A4                         | GAB1/IO03RSB0  | D4                         | GAA2/IO67RSB1  | G4         | GFA0/IO122RSB1             |  |

| A5                         | IO11RSB0       | D5                         | GAC0/IO04RSB0  | G5         | GND                        |  |

| A6                         | GND            | D6                         | GAC1/IO05RSB0  | G6         | GND                        |  |

| A7                         | IO18RSB0       | D7                         | GBC0/IO35RSB0  | G7         | GND                        |  |

| A8                         | VCC            | D8                         | GBC1/IO36RSB0  | G8         | GDC1/IO61RSB0              |  |

| A9                         | IO25RSB0       | D9                         | GBB2/IO43RSB0  | G9         | IO48RSB0                   |  |

| A10                        | GBA0/IO39RSB0  | D10                        | IO28RSB0       | G10        | GCC2/IO59RSB0              |  |

| A11                        | GBA1/IO40RSB0  | D11                        | IO44RSB0       | G11        | IO47RSB0                   |  |

| A12                        | GNDQ           | D12                        | GCB1/IO53RSB0  | G12        | GCB2/IO58RSB0              |  |

| B1                         | GAB2/IO69RSB1  | E1                         | VCC            | H1         | VCC                        |  |

| B2                         | GND            | E2                         | GFC0/IO125RSB1 | H2         | GFB2/IO119RSB1             |  |

| B3                         | GAA0/IO00RSB0  | E3                         | GFC1/IO126RSB1 | H3         | GFC2/IO118RSB1             |  |

| B4                         | GAA1/IO01RSB0  | E4                         | VCCIB1         | H4         | GEC1/IO112RSB1             |  |

| B5                         | IO08RSB0       | E5                         | IO68RSB1       | H5         | VCC                        |  |

| B6                         | IO14RSB0       | E6                         | VCCIB0         | H6         | IO50RSB0                   |  |

| B7                         | IO19RSB0       | E7                         | VCCIB0         | H7         | IO60RSB0                   |  |

| B8                         | IO22RSB0       | E8                         | GCC1/IO51RSB0  | H8         | GDB2/IO71RSB1              |  |

| B9                         | GBB0/IO37RSB0  | E9                         | VCCIB0         | H9         | GDC0/IO62RSB0              |  |

| B10                        | GBB1/IO38RSB0  | E10                        | VCC            | H10        | VCCIB0                     |  |

| B11                        | GND            | E11                        | GCA0/IO56RSB0  | H11        | IO49RSB0                   |  |

| B12                        | VMV0           | E12                        | IO46RSB0       | H12        | VCC                        |  |

| C1                         | IO132RSB1      | F1                         | GFB0/IO123RSB1 | J1         | GEB1/IO110RSB1             |  |

| C2                         | GFA2/IO120RSB1 | F2                         | VCOMPLF        | J2         | IO115RSB1                  |  |

| C3                         | GAC2/IO131RSB1 | F3                         | GFB1/IO124RSB1 | J3         | VCCIB1                     |  |

| C4                         | VCC            | F4                         | IO127RSB1      | J4         | GEC0/IO111RSB1             |  |

| C5                         | IO10RSB0       | F5                         | GND            | J5         | IO116RSB1                  |  |

| C6                         | IO12RSB0       | F6                         | GND            | J6         | IO117RSB1                  |  |

| C7                         | IO21RSB0       | F7                         | GND            | J7         | VCC                        |  |

| C8                         | IO24RSB0       | F8                         | GCC0/IO52RSB0  | J8         | ТСК                        |  |

| C9                         | IO27RSB0       | F9                         | GCB0/IO54RSB0  | J9         | GDA2/IO70RSB1              |  |

| C10                        | GBA2/IO41RSB0  | F10                        | GND            | J10        | TDO                        |  |

| C11                        | IO42RSB0       | F11                        | GCA1/IO55RSB0  | J11        | GDA1/IO65RSB0              |  |

| C12                        | GBC2/IO45RSB0  | F12                        | GCA2/IO57RSB0  | J12        | GDB1/IO63RSB0              |  |

| FG256                       |                | FG256                       |                | FG256      |                  |

|-----------------------------|----------------|-----------------------------|----------------|------------|------------------|

| Pin Number AGL1000 Function |                | Pin Number AGL1000 Function |                | Pin Number | AGL1000 Function |

| A1                          | GND            | C7                          | IO25RSB0       | E13        | GBC2/IO80PDB1    |

| A2                          | GAA0/IO00RSB0  | C8                          | IO36RSB0       | E14        | IO83PPB1         |

| A3                          | GAA1/IO01RSB0  | C9                          | IO42RSB0       | E15        | IO86PPB1         |

| A4                          | GAB0/IO02RSB0  | C10                         | IO49RSB0       | E16        | IO87PDB1         |

| A5                          | IO16RSB0       | C11                         | IO56RSB0       | F1         | IO217NDB3        |

| A6                          | IO22RSB0       | C12                         | GBC0/IO72RSB0  | F2         | IO218NDB3        |

| A7                          | IO28RSB0       | C13                         | IO62RSB0       | F3         | IO216PDB3        |

| A8                          | IO35RSB0       | C14                         | VMV0           | F4         | IO216NDB3        |

| A9                          | IO45RSB0       | C15                         | IO78NDB1       | F5         | VCCIB3           |

| A10                         | IO50RSB0       | C16                         | IO81NDB1       | F6         | GND              |

| A11                         | IO55RSB0       | D1                          | IO222NDB3      | F7         | VCC              |

| A12                         | IO61RSB0       | D2                          | IO222PDB3      | F8         | VCC              |

| A13                         | GBB1/IO75RSB0  | D3                          | GAC2/IO223PDB3 | F9         | VCC              |

| A14                         | GBA0/IO76RSB0  | D4                          | IO223NDB3      | F10        | VCC              |

| A15                         | GBA1/IO77RSB0  | D5                          | GNDQ           | F11        | GND              |

| A16                         | GND            | D6                          | IO23RSB0       | F12        | VCCIB1           |

| B1                          | GAB2/IO224PDB3 | D7                          | IO29RSB0       | F13        | IO83NPB1         |

| B2                          | GAA2/IO225PDB3 | D8                          | IO33RSB0       | F14        | IO86NPB1         |

| B3                          | GNDQ           | D9                          | IO46RSB0       | F15        | IO90PPB1         |

| B4                          | GAB1/IO03RSB0  | D10                         | IO52RSB0       | F16        | IO87NDB1         |

| B5                          | IO17RSB0       | D11                         | IO60RSB0       | G1         | IO210PSB3        |

| B6                          | IO21RSB0       | D12                         | GNDQ           | G2         | IO213NDB3        |

| B7                          | IO27RSB0       | D13                         | IO80NDB1       | G3         | IO213PDB3        |

| B8                          | IO34RSB0       | D14                         | GBB2/IO79PDB1  | G4         | GFC1/IO209PPB3   |

| B9                          | IO44RSB0       | D15                         | IO79NDB1       | G5         | VCCIB3           |

| B10                         | IO51RSB0       | D16                         | IO82NSB1       | G6         | VCC              |

| B11                         | IO57RSB0       | E1                          | IO217PDB3      | G7         | GND              |

| B12                         | GBC1/IO73RSB0  | E2                          | IO218PDB3      | G8         | GND              |

| B13                         | GBB0/IO74RSB0  | E3                          | IO221NDB3      | G9         | GND              |

| B14                         | IO71RSB0       | E4                          | IO221PDB3      | G10        | GND              |

| B15                         | GBA2/IO78PDB1  | E5                          | VMV0           | G11        | VCC              |

| B16                         | IO81PDB1       | E6                          | VCCIB0         | G12        | VCCIB1           |

| C1                          | IO224NDB3      | E7                          | VCCIB0         | G13        | GCC1/IO91PPB1    |

| C2                          | IO225NDB3      | E8                          | IO38RSB0       | G14        | IO90NPB1         |

| C3                          | VMV3           | E9                          | IO47RSB0       | G15        | IO88PDB1         |

| C4                          | IO11RSB0       | E10                         | VCCIB0         | G16        | IO88NDB1         |

| C5                          | GAC0/IO04RSB0  | E11                         | VCCIB0         | H1         | GFB0/IO208NPB3   |

| C6                          | GAC1/IO05RSB0  | E12                         | VMV1           | H2         | GFA0/IO207NDB3   |

| FG484                      |          |  |  |

|----------------------------|----------|--|--|

| Pin Number AGL400 Function |          |  |  |

| A1                         | GND      |  |  |

| A2                         | GND      |  |  |

| A3                         | VCCIB0   |  |  |

| A4                         | NC       |  |  |

| A5                         | NC       |  |  |

| A6                         | IO15RSB0 |  |  |

| A7                         | IO18RSB0 |  |  |

| A8                         | NC       |  |  |

| A9                         | NC       |  |  |

| A10                        | IO23RSB0 |  |  |

| A11                        | IO29RSB0 |  |  |

| A12                        | IO35RSB0 |  |  |

| A13                        | IO36RSB0 |  |  |

| A14                        | NC       |  |  |

| A15                        | NC       |  |  |

| A16                        | IO50RSB0 |  |  |

| A17                        | IO51RSB0 |  |  |

| A18                        | NC       |  |  |

| A19                        | NC       |  |  |

| A20                        | VCCIB0   |  |  |

| A21                        | GND      |  |  |

| A22                        | GND      |  |  |

| AA1                        | GND      |  |  |

| AA2                        | VCCIB3   |  |  |

| AA3                        | NC       |  |  |

| AA4                        | NC       |  |  |

| AA5                        | NC       |  |  |

| AA6                        | NC       |  |  |

| AA7                        | NC       |  |  |

| AA8                        | NC       |  |  |

| AA9                        | NC       |  |  |

| AA10                       | NC       |  |  |

| AA11                       | NC       |  |  |

| AA12                       | NC       |  |  |

| AA13                       | NC       |  |  |

| AA14                       | NC       |  |  |

| FG484      |                 |  |  |

|------------|-----------------|--|--|

| Pin Number | AGL600 Function |  |  |

| M3         | IO158NPB3       |  |  |

| M4         | GFA2/IO161PPB3  |  |  |

| M5         | GFA1/IO162PDB3  |  |  |

| M6         | VCCPLF          |  |  |

| M7         | IO160NDB3       |  |  |

| M8         | GFB2/IO160PDB3  |  |  |

| M9         | VCC             |  |  |

| M10        | GND             |  |  |

| M11        | GND             |  |  |

| M12        | GND             |  |  |

| M13        | GND             |  |  |

| M14        | VCC             |  |  |

| M15        | GCB2/IO73PPB1   |  |  |

| M16        | GCA1/IO71PPB1   |  |  |

| M17        | GCC2/IO74PPB1   |  |  |

| M18        | IO80PPB1        |  |  |

| M19        | GCA2/IO72PDB1   |  |  |

| M20        | IO79PPB1        |  |  |

| M21        | IO78PPB1        |  |  |

| M22        | NC              |  |  |

| N1         | IO154NDB3       |  |  |

| N2         | IO154PDB3       |  |  |

| N3         | NC              |  |  |

| N4         | GFC2/IO159PDB3  |  |  |

| N5         | IO161NPB3       |  |  |

| N6         | IO156PPB3       |  |  |

| N7         | IO129RSB2       |  |  |

| N8         | VCCIB3          |  |  |

| N9         | VCC             |  |  |

| N10        | GND             |  |  |

| N11        | GND             |  |  |

| N12        | GND             |  |  |

| N13        | GND             |  |  |

| N14        | VCC             |  |  |

| N15        | VCCIB1          |  |  |

| N16        | IO73NPB1        |  |  |

| FG484      |                  |  |  |

|------------|------------------|--|--|

| Pin Number | AGL1000 Function |  |  |

| K11        | GND              |  |  |

| K12        | GND              |  |  |

| K13        | GND              |  |  |

| K14        | VCC              |  |  |

| K15        | VCCIB1           |  |  |

| K16        | GCC1/IO91PPB1    |  |  |

| K17        | IO90NPB1         |  |  |

| K18        | IO88PDB1         |  |  |

| K19        | IO88NDB1         |  |  |

| K20        | IO94NPB1         |  |  |

| K21        | IO98NDB1         |  |  |

| K22        | IO98PDB1         |  |  |

| L1         | NC               |  |  |

| L2         | IO200PDB3        |  |  |

| L3         | IO210NPB3        |  |  |

| L4         | GFB0/IO208NPB3   |  |  |

| L5         | GFA0/IO207NDB3   |  |  |

| L6         | GFB1/IO208PPB3   |  |  |

| L7         | VCOMPLF          |  |  |

| L8         | GFC0/IO209NPB3   |  |  |

| L9         | VCC              |  |  |

| L10        | GND              |  |  |

| L11        | GND              |  |  |

| L12        | GND              |  |  |

| L13        | GND              |  |  |

| L14        | VCC              |  |  |

| L15        | GCC0/IO91NPB1    |  |  |

| L16        | GCB1/IO92PPB1    |  |  |

| L17        | GCA0/IO93NPB1    |  |  |

| L18        | IO96NPB1         |  |  |

| L19        | GCB0/IO92NPB1    |  |  |

| L20        | IO97PDB1         |  |  |

| L21        | IO97NDB1         |  |  |

| L22        | IO99NPB1         |  |  |

| M1         | NC               |  |  |

| M2         | IO200NDB3        |  |  |

IGLOO Low Power Flash FPGAs

| Revision                   | Changes                                                                                                                                                                                                                                                                                                                                                                                                                               | Page          |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Revision 19<br>(continued) | The following sentence was removed from the "Advanced Architecture" section:<br>"In addition, extensive on-chip programming circuitry allows for rapid, single-voltage<br>(3.3 V) programming of IGLOO devices via an IEEE 1532 JTAG interface" (SAR<br>28756).                                                                                                                                                                       | 1-3           |

|                            | The "Specifying I/O States During Programming" section is new (SAR 21281).                                                                                                                                                                                                                                                                                                                                                            | 1-8           |

|                            | Values for VCCPLL at 1.2 V –1.5 V DC core supply voltage were revised in Table 2-2 • Recommended Operating Conditions 1 (SAR 22356).                                                                                                                                                                                                                                                                                                  | 2-2           |

|                            | The value for VPUMP operation was changed from "0 to 3.45 V" to "0 to 3.6 V" (SAR 25220).                                                                                                                                                                                                                                                                                                                                             |               |

|                            | The value for VCCPLL 1.5 V DC core supply voltage was changed from "1.4 to 1.6 V" to "1.425 to 1.575 V" (SAR 26551).                                                                                                                                                                                                                                                                                                                  |               |

|                            | The notes in the table were renumbered in order of their appearance in the table (SAR 21869).                                                                                                                                                                                                                                                                                                                                         |               |

|                            | The temperature used in EQ 2 was revised from 110°C to 100°C for consistency with the limits given in Table 2-2 • Recommended Operating Conditions 1. The resulting maximum power allowed is thus 1.28 W. Formerly it was 1.71 W (SAR 26259).                                                                                                                                                                                         | 2-6           |

|                            | Values for CS196, CS281, and QN132 packages were added to Table 2-5 • Package Thermal Resistivities (SARs 26228, 32301).                                                                                                                                                                                                                                                                                                              | 2-6           |

|                            | Table 2-6 • Temperature and Voltage Derating Factors for Timing Delays (normalized to $TJ = 70^{\circ}C$ , VCC = 1.425 V) and Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays (normalized to $TJ = 70^{\circ}C$ , VCC = 1.14 V) were updated to remove the column for –20°C and shift the data over to correct columns (SAR 23041).                                                                            | 2-7           |

|                            | The tables in the "Quiescent Supply Current" section were updated with revised notes on IDD (SAR 24112). Table 2-8 • Power Supply State per Mode is new.                                                                                                                                                                                                                                                                              | 2-7           |

|                            | The formulas in the table notes for Table 2-41 • I/O Weak Pull-Up/Pull-Down Resistances were corrected (SAR 21348).                                                                                                                                                                                                                                                                                                                   | 2-37          |

|                            | The row for 110°C was removed from Table 2-45 • Duration of Short Circuit Event before Failure. The example in the associated paragraph was changed from 110°C to 100°C. Table 2-46 • I/O Input Rise Time, Fall Time, and Related I/O Reliability1 was revised to change 110° to 100°C. (SAR 26259).                                                                                                                                  | 2-40          |

|                            | The notes regarding drive strength in the "Summary of I/O Timing Characteristics –                                                                                                                                                                                                                                                                                                                                                    | 2-28,         |

|                            | Default I/O Software Settings" section, "3.3 V LVCMOS Wide Range" section and "1.2 V LVCMOS Wide Range" section tables were revised for clarification. They now state that the minimum drive strength for the default software configuration when run in wide range is $\pm 100 \ \mu$ A. The drive strength displayed in software is supported in normal range only. For a detailed I/V curve, refer to the IBIS models (SAR 25700). | 2-47,<br>2-77 |

|                            | The following sentence was deleted from the "2.5 V LVCMOS" section (SAR 24916): "It uses a 5 V-tolerant input buffer and push-pull output buffer."                                                                                                                                                                                                                                                                                    | 2-56          |

|                            | The values for $F_{DDRIMAX}$ and $F_{DDOMAX}$ were updated in the tables in the "Input DDR Module" section and "Output DDR Module" section (SAR 23919).                                                                                                                                                                                                                                                                               | 2-94,<br>2-97 |

|                            | The following notes were removed from Table 2-147 • Minimum and Maximum DC Input and Output Levels (SAR 29428): ±5%                                                                                                                                                                                                                                                                                                                   | 2-81          |

|                            | Differential input voltage = ±350 mV                                                                                                                                                                                                                                                                                                                                                                                                  |               |

|                            | Table 2-189 • IGLOO CCC/PLL Specification and Table 2-190 • IGLOO CCC/PLL Specification were updated. A note was added to both tables indicating that when the CCC/PLL core is generated by Mircosemi core generator software, not all delay values of the specified delay increments are available (SAR 25705).                                                                                                                      | 2-115         |

IGLOO Low Power Flash FPGAs

| Revision / Version                                   | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page             |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Revision 3 (Feb 2008)<br>Product Brief rev. 2        | This document was updated to include AGL015 device information. QN68 is a<br>new package offered in the AGL015. The following sections were updated:<br>"Features and Benefits"<br>"IGLOO Ordering Information"<br>"Temperature Grade Offerings"<br>"IGLOO Devices" Product Family Table<br>Table 1 • IGLOO FPGAs Package Sizes Dimensions<br>"AGL015 and AGL030" note<br>The "Temperature Grade Offerings" table was updated to include M1AGL600.<br>In the "IGLOO Ordering Information" table, the QN package measurements were<br>updated to include both 0.4 mm and 0.5 mm. | N/A<br>IV<br>III |

|                                                      | In the "General Description" section, the number of I/Os was updated from 288 to 300.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-1              |

| Packaging v1.2                                       | The "QN68" section is new.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-25             |

| <b>Revision 2 (Jan 2008)</b><br>Packaging v1.1       | The "CS196" package and pin table was added for AGL125.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-10             |

| <b>Revision 1 (Jan 2008)</b><br>Product Brief rev. 1 | The "Low Power" section was updated to change the description of low power active FPGA operation to "from 12 $\mu$ W" from "from 25 $\mu$ W." The same update was made in the "General Description" section and the "Flash*Freeze Technology" section.                                                                                                                                                                                                                                                                                                                          | l, 1-1           |

| Revision 0 (Jan 2008)                                | This document was previously in datasheet Advance v0.7. As a result of moving to the handbook format, Actel has restarted the numbering.                                                                                                                                                                                                                                                                                                                                                                                                                                        | N/A              |

| Advance v0.7<br>(December 2007)                      | Table 1 • IGLOO Product Family, the "I/Os Per Package1" table, and the Temperature Grade Offerings table were updated to reflect the following: CS196 is now supported for AGL250; device/package support for QN132 is to be determined for AGL250; the CS281 package was added for AGL600 and AGL1000.                                                                                                                                                                                                                                                                         | i, ii, iv        |

|                                                      | Table 2 • IGLOO FPGAs Package Sizes Dimensions is new, and package sizes were removed from the "I/Os Per Package1" table.                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ii               |

|                                                      | The "I/Os Per Package1"table was updated to reflect 77 instead of 79 single-<br>ended I/Os for the VG100 package for AGL030.                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ii               |

|                                                      | The "Timing Model" was updated to be consistent with the revised timing numbers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-20             |

|                                                      | In Table 2-27 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings, $T_J$ was changed to $T_A$ in notes 1 and 2.                                                                                                                                                                                                                                                                                                                                                                            | 2-26             |

|                                                      | All AC Loading figures for single-ended I/O standards were changed from Datapaths at 35 pF to 5 pF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | N/A              |

|                                                      | The "1.2 V LVCMOS (JESD8-12A)" section is new.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-74             |

|                                                      | This document was previously in datasheet Advance v0.7. As a result of moving to the handbook format, Actel has restarted the version numbers. The new version number is Advance v0.1.                                                                                                                                                                                                                                                                                                                                                                                          | N/A              |

|                                                      | Table 2-4 • IGLOO CCC/PLL Specification and Table 2-5 • IGLOO CCC/PLL         Specification were updated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-19,<br>2-20    |