# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                     |

|--------------------------------|----------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | 1536                                                                       |

| Total RAM Bits                 | 18432                                                                      |

| Number of I/O                  | 71                                                                         |

| Number of Gates                | 60000                                                                      |

| Voltage - Supply               | 1.14V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 85°C (TA)                                                          |

| Package / Case                 | 100-TQFP                                                                   |

| Supplier Device Package        | 100-VQFP (14x14)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/agl060v2-vqg100i |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Summary of I/O Timing Characteristics – Default I/O Software Settings

#### Table 2-29 • Summary of AC Measuring Points

| Standard                   | Measuring Trip Point (Vtrip) |

|----------------------------|------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 1.4 V                        |

| 3.3 V VCMOS Wide Range     | 1.4 V                        |

| 2.5 V LVCMOS               | 1.2 V                        |

| 1.8 V LVCMOS               | 0.90 V                       |

| 1.5 V LVCMOS               | 0.75 V                       |

| 1.2 V LVCMOS               | 0.60 V                       |

| 1.2 V LVCMOS Wide Range    | 0.60 V                       |

| 3.3 V PCI                  | 0.285 * VCCI (RR)            |

|                            | 0.615 * VCCI (FF)            |

| 3.3 V PCI-X                | 0.285 * VCCI (RR)            |

|                            | 0.615 * VCCI (FF)            |

#### Table 2-30 • I/O AC Parameter Definitions

| Parameter         | Parameter Definition                                                        |

|-------------------|-----------------------------------------------------------------------------|

| t <sub>DP</sub>   | Data to Pad delay through the Output Buffer                                 |

| t <sub>PY</sub>   | Pad to Data delay through the Input Buffer                                  |

| t <sub>DOUT</sub> | Data to Output Buffer delay through the I/O interface                       |

| t <sub>EOUT</sub> | Enable to Output Buffer Tristate Control delay through the I/O interface    |

| t <sub>DIN</sub>  | Input Buffer to Data delay through the I/O interface                        |

| t <sub>HZ</sub>   | Enable to Pad delay through the Output Buffer—High to Z                     |

| t <sub>ZH</sub>   | Enable to Pad delay through the Output Buffer—Z to High                     |

| t <sub>LZ</sub>   | Enable to Pad delay through the Output Buffer—Low to Z                      |

| t <sub>ZL</sub>   | Enable to Pad delay through the Output Buffer—Z to Low                      |

| t <sub>ZHS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to High |

| t <sub>ZLS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to Low  |

Table 2-34 •

Summary of I/O Timing Characteristics—Software Default Settings, Std. Speed Grade, Commercial-Case

Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI (per standard)

Applicable to Advanced I/O Banks

| I/O Standard                                  | Drive Strength     | Equivalent Software Default<br>Drive Strength Option <sup>1</sup> | Slew Rate | Capacitive Load (pF) | External Resistor ( $\Omega$ ) | t <sub>bour</sub> (ns) | t <sub>DP</sub> (ns) | t <sub>DIN</sub> (ns) | t <sub>PY</sub> (ns) | t <sub>Eour</sub> (ns) | t <sub>ZL</sub> (ns) | t <sub>ZH</sub> (ns) | t <sub>LZ</sub> (ns) | t <sub>HZ</sub> (ns) | t <sub>ZLS</sub> (ns) | t <sub>ZHS</sub> (ns) | Units |

|-----------------------------------------------|--------------------|-------------------------------------------------------------------|-----------|----------------------|--------------------------------|------------------------|----------------------|-----------------------|----------------------|------------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|-----------------------|-------|

| 3.3 V<br>LVTTL /<br>3.3 V<br>LVCMOS           | 12 mA              | 12 mA                                                             | High      | 5                    | -                              | 1.55                   | 2.67                 | 0.26                  | 0.98                 | 1.10                   | 2.71                 | 2.18                 | 3.25                 | 3.93                 | 8.50                  | 7.97                  | ns    |

| 3.3 V<br>LVCMOS<br>Wide<br>Range <sup>2</sup> | 100 µA             | 12 mA                                                             | High      | 5                    | -                              | 1.55                   | 3.73                 | 0.26                  | 1.32                 | 1.10                   | 3.73                 | 2.91                 | 4.51                 | 5.43                 | 9.52                  | 8.69                  | ns    |

| 2.5 V<br>LVCMOS                               | 12 mA              | 12 mA                                                             | High      | 5                    | —                              | 1.55                   | 2.64                 | 0.26                  | 1.20                 | 1.10                   | 2.67                 | 2.29                 | 3.30                 | 3.79                 | 8.46                  | 8.08                  | ns    |

| 1.8 V<br>LVCMOS                               | 12 mA              | 12 mA                                                             | High      | 5                    | -                              | 1.55                   | 2.72                 | 0.26                  | 1.11                 | 1.10                   | 2.76                 | 2.43                 | 3.58                 | 4.19                 | 8.55                  | 8.22                  | ns    |

| 1.5 V<br>LVCMOS                               | 12 mA              | 12 mA                                                             | High      | 5                    | _                              | 1.55                   | 2.96                 | 0.26                  | 1.27                 | 1.10                   | 3.00                 | 2.70                 | 3.75                 | 4.23                 | 8.78                  | 8.48                  | ns    |

| 1.2 V<br>LVCMOS                               | 2 mA               | 2 mA                                                              | High      | 5                    | -                              | 1.55                   | 3.60                 | 0.26                  | 1.60                 | 1.10                   | 3.47                 | 3.36                 | 3.93                 | 3.65                 | 9.26                  | 9.14                  | ns    |

| 1.2 V<br>LVCMOS<br>Wide<br>Range <sup>3</sup> | 100 µA             | 2 mA                                                              | High      | 5                    | _                              | 1.55                   | 3.60                 | 0.26                  | 1.60                 | 1.10                   | 3.47                 | 3.36                 | 3.93                 | 3.65                 | 9.26                  | 9.14                  | ns    |

| 3.3 V PCI                                     | Per PCI<br>spec    | _                                                                 | High      | 10                   | 25 <sup>2</sup>                | 1.55                   | 2.91                 | 0.26                  | 0.86                 | 1.10                   | 2.95                 | 2.29                 | 3.25                 | 3.93                 | 8.74                  | 8.08                  | ns    |

| 3.3 V<br>PCI-X                                | Per PCI-<br>X spec | Ι                                                                 | High      | 10                   | 25 <sup>2</sup>                | 1.55                   | 2.91                 | 0.25                  | 0.86                 | 1.10                   | 2.95                 | 2.29                 | 3.25                 | 3.93                 | 8.74                  | 8.08                  | ns    |

| LVDS                                          | 24 mA              | -                                                                 | High      | I                    | -                              | 1.55                   | 2.27                 | 0.25                  | 1.57                 | -                      | -                    | -                    | -                    | -                    | —                     | -                     | ns    |

| LVPECL                                        | 24 mA              | Ι                                                                 | High      | I                    | -                              | 1.55                   | 2.24                 | 0.25                  | 1.38                 | 1                      | -                    | -                    | -                    | _                    | -                     | -                     | ns    |

Notes:

The minimum drive strength for any LVCMOS 1.2 V or LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

3. All LVCMOS 1.2 V software macros support LVCMOS 1.2 V wide range as specified in the JESD8-12 specification

4. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-12 on page 2-79 for connectivity. This resistor is not required during normal operation.

5. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

## Single-Ended I/O Characteristics

### 3.3 V LVTTL / 3.3 V LVCMOS

Low-Voltage Transistor–Transistor Logic (LVTTL) is a general-purpose standard (EIA/JESD) for 3.3 V applications. It uses an LVTTL input buffer and push-pull output buffer. Furthermore, all LVCMOS 3.3 V software macros comply with LVCMOS 3.3 V wide range as specified in the JESD8a specification.

## Table 2-47 • Minimum and Maximum DC Input and Output Levels Applicable to Advanced I/O Banks

| 3.3 V LVTTL /<br>3.3 V LVCMOS | v         | IL        | VIH       |           | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL¹            | IIH <sup>2</sup> |

|-------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-----------------|------------------|

| Drive<br>Strength             | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 2 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 2   | 2  | 25                      | 27                      | 10              | 10               |

| 4 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 4   | 4  | 25                      | 27                      | 10              | 10               |

| 6 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 6   | 6  | 51                      | 54                      | 10              | 10               |

| 8 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 8   | 8  | 51                      | 54                      | 10              | 10               |

| 12 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 12  | 12 | 103                     | 109                     | 10              | 10               |

| 16 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 16  | 16 | 132                     | 127                     | 10              | 10               |

| 24 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 24  | 24 | 268                     | 181                     | 10              | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

Table 2-48 •

Minimum and Maximum DC Input and Output Levels

Applicable to Standard Plus I/O Banks

| 3.3 V LVTTL /<br>3.3 V LVCMOS | v         | ΊL        | v         | н         | V <sub>OL</sub> | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------------------|-----------|-----------|-----------|-----------|-----------------|-----------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength             | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V       | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4             | 2.4       | 2   | 2  | 25                      | 27                      | 10               | 10               |

| 4 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4             | 2.4       | 4   | 4  | 25                      | 27                      | 10               | 10               |

| 6 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4             | 2.4       | 6   | 6  | 51                      | 54                      | 10               | 10               |

| 8 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4             | 2.4       | 8   | 8  | 51                      | 54                      | 10               | 10               |

| 12 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4             | 2.4       | 12  | 12 | 103                     | 109                     | 10               | 10               |

| 16 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4             | 2.4       | 16  | 16 | 103                     | 109                     | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

#### Table 2-104 • 1.8 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V Applicable to Standard Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | Std.        | 2.62              | 0.18            | 0.98             | 0.66            | 2.67              | 2.59            | 1.67            | 1.29            | 2.62            | ns    |

| 4 mA           | Std.        | 2.18              | 0.18            | 0.98             | 0.66            | 2.22              | 1.93            | 1.97            | 2.06            | 2.18            | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

#### 1.2 V DC Core Voltage

Table 2-105 • 1.8 V LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.7 V Applicable to Advanced I/O Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 1.55              | 6.97            | 0.26             | 1.11            | 1.10              | 7.08            | 6.48            | 2.87            | 2.29            | 12.87            | 12.27            | ns    |

| 4 mA           | Std.        | 1.55              | 5.91            | 0.26             | 1.11            | 1.10              | 6.01            | 5.57            | 3.21            | 3.14            | 11.79            | 11.36            | ns    |

| 6 mA           | Std.        | 1.55              | 5.16            | 0.26             | 1.11            | 1.10              | 5.24            | 4.95            | 3.45            | 3.55            | 11.03            | 10.74            | ns    |

| 8 mA           | Std.        | 1.55              | 4.90            | 0.26             | 1.11            | 1.10              | 4.98            | 4.81            | 3.50            | 3.66            | 10.77            | 10.60            | ns    |

| 12 mA          | Std.        | 1.55              | 4.83            | 0.26             | 1.11            | 1.10              | 4.90            | 4.83            | 3.58            | 4.08            | 10.68            | 10.61            | ns    |

| 16 mA          | Std.        | 1.55              | 4.83            | 0.26             | 1.11            | 1.10              | 4.90            | 4.83            | 3.58            | 4.08            | 10.68            | 10.61            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

#### Table 2-106 • 1.8 V LVCMOS High Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.7 V Applicable to Advanced I/O Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 1.55              | 3.73            | 0.26             | 1.11            | 1.10              | 3.71            | 3.73            | 2.86            | 2.34            | 9.49             | 9.51             | ns    |

| 4 mA           | Std.        | 1.55              | 3.12            | 0.26             | 1.11            | 1.10              | 3.16            | 2.97            | 3.21            | 3.22            | 8.95             | 8.75             | ns    |

| 6 mA           | Std.        | 1.55              | 2.79            | 0.26             | 1.11            | 1.10              | 2.83            | 2.59            | 3.45            | 3.65            | 8.62             | 8.38             | ns    |

| 8 mA           | Std.        | 1.55              | 2.73            | 0.26             | 1.11            | 1.10              | 2.77            | 2.52            | 3.50            | 3.75            | 8.56             | 8.30             | ns    |

| 12 mA          | Std.        | 1.55              | 2.72            | 0.26             | 1.11            | 1.10              | 2.76            | 2.43            | 3.58            | 4.19            | 8.55             | 8.22             | ns    |

| 16 mA          | Std.        | 1.55              | 2.72            | 0.26             | 1.11            | 1.10              | 2.76            | 2.43            | 3.58            | 4.19            | 8.55             | 8.22             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

# Table 2-107 • 1.8 V LVCMOS Low Slew – Applies to 1.2 V DC Core VoltageCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.7 VApplicable to Standard Plus Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 1.55              | 6.32            | 0.26             | 1.11            | 1.10              | 6.43            | 5.81            | 2.47            | 2.16            | 12.22            | 11.60            | ns    |

| 4 mA           | Std.        | 1.55              | 5.27            | 0.26             | 1.11            | 1.10              | 5.35            | 5.01            | 2.78            | 2.92            | 11.14            | 10.79            | ns    |

| 6 mA           | Std.        | 1.55              | 4.56            | 0.26             | 1.11            | 1.10              | 4.64            | 4.44            | 3.00            | 3.30            | 10.42            | 10.22            | ns    |

| 8 mA           | Std.        | 1.55              | 4.56            | 0.26             | 1.11            | 1.10              | 4.64            | 4.44            | 3.00            | 3.30            | 10.42            | 10.22            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

#### Table 2-108 • 1.8 V LVCMOS High Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.7 V Applicable to Standard Plus Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 1.55              | 3.22            | 0.26             | 1.11            | 1.10              | 3.26            | 3.18            | 2.47            | 2.20            | 9.05             | 8.97             | ns    |

| 4 mA           | Std.        | 1.55              | 2.72            | 0.26             | 1.11            | 1.10              | 2.75            | 2.50            | 2.78            | 3.01            | 8.54             | 8.29             | ns    |

| 6 mA           | Std.        | 1.55              | 2.43            | 0.26             | 1.11            | 1.10              | 2.47            | 2.16            | 2.99            | 3.39            | 8.25             | 7.94             | ns    |

| 8 mA           | Std.        | 1.55              | 2.43            | 0.26             | 1.11            | 1.10              | 2.47            | 2.16            | 2.99            | 3.39            | 8.25             | 7.94             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

#### Table 2-109 • 1.8 V LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage

#### Commercial-Case Conditions: $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.7 V Applicable to Standard Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | Std.        | 1.55              | 6.13            | 0.26             | 1.08            | 1.10              | 6.24            | 5.79            | 2.08            | 1.78            | ns    |

| 4 mA           | Std.        | 1.55              | 5.17            | 0.26             | 1.08            | 1.10              | 5.26            | 4.98            | 2.38            | 2.54            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

#### Table 2-110 • 1.8 V LVCMOS High Slew – Applies to 1.2 V DC Core Voltage

#### Commercial-Case Conditions: $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.7 V Applicable to Standard Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | Std.        | 3.06              | 0.26            | 1.08             | 1.10            | 3.10              | 3.01            | 2.08            | 1.83            | 3.06            | ns    |

| 4 mA           | Std.        | 2.60              | 0.26            | 1.08             | 1.10            | 2.64              | 2.33            | 2.38            | 2.62            | 2.60            | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

#### 3.3 V PCI, 3.3 V PCI-X

Peripheral Component Interface for 3.3 V standard specifies support for 33 MHz and 66 MHz PCI Bus applications.

Table 2-141 • Minimum and Maximum DC Input and Output Levels

Applicable to Advanced and Standard Plus I/Os

| 3.3 V PCI/PCI-X          | v         | IL             | V         | IH        | VOL       | VOH       | IOL | ЮН | IOSH                    | IOSL                    | IIL             | IIH |

|--------------------------|-----------|----------------|-----------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-----------------|-----|

| Drive Strength           | Min.<br>V | Max.<br>V      | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA <sup>2</sup> | μA² |

| Per PCI<br>specification |           | Per PCI curves |           |           |           |           |     |    | 10                      | 10                      |                 |     |

Notes:

1. Currents are measured at 100°C junction temperature and maximum voltage.

2. Currents are measured at 85°C junction temperature.

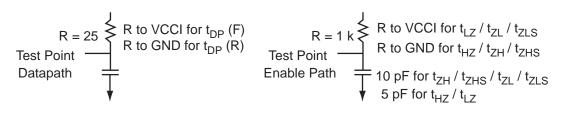

AC loadings are defined per the PCI/PCI-X specifications for the datapath; Microsemi loadings for enable path characterization are described in Figure 2-12.

#### Figure 2-12 • AC Loading

AC loadings are defined per PCI/PCI-X specifications for the datapath; Microsemi loading for tristate is described in Table 2-142.

#### Table 2-142 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V)                | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------------------|------------------------|

| 0             | 3.3            | 0.285 * VCCI for t <sub>DP(R)</sub> | 10                     |

|               |                | 0.615 * VCCI for $t_{DP(F)}$        |                        |

Note: \*Measuring point = Vtrip. See Table 2-29 on page 2-28 for a complete table of trip points.

#### **Timing Characteristics**

1.5 V DC Core Voltage

*Table 2-143* • 3.3 V PCI/PCI-X

Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Advanced I/O Banks

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 0.97              | 2.32            | 0.19             | 0.70            | 0.66              | 2.37            | 1.78            | 2.67            | 3.05            | 5.96             | 5.38             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

#### Table 2-144 • 3.3 V PCI/PCI-X

#### Commercial-Case Conditions: $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard Plus I/O Banks

| Speed Grade t | LOOUT | τ <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|---------------|-------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.          | 0.97  | 1.97            | 0.19             | 0.70            | 0.66              | 2.01            | 1.50            | 2.36            | 2.79            | 5.61             | 5.10             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

### Input Register

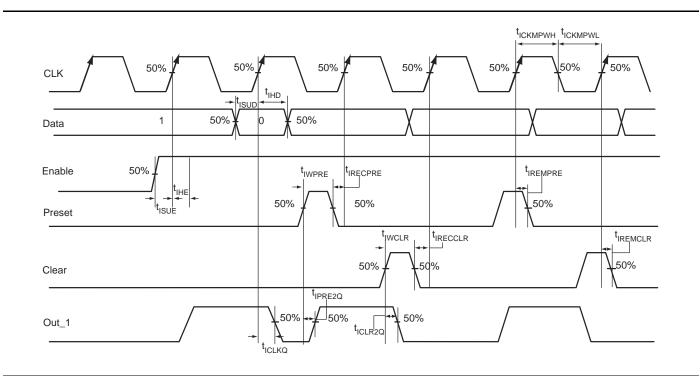

#### Figure 2-18 • Input Register Timing Diagram

#### **Timing Characteristics**

#### 1.5 V DC Core Voltage

## Table 2-157 • Input Data Register Propagation DelaysCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                         | Std. | Units |

|----------------------|---------------------------------------------------------------------|------|-------|

| t <sub>ICLKQ</sub>   | Clock-to-Q of the Input Data Register                               | 0.42 | ns    |

| t <sub>ISUD</sub>    | Data Setup Time for the Input Data Register                         | 0.47 | ns    |

| t <sub>IHD</sub>     | Data Hold Time for the Input Data Register                          | 0.00 | ns    |

| t <sub>ISUE</sub>    | Enable Setup Time for the Input Data Register                       | 0.67 | ns    |

| t <sub>IHE</sub>     | Enable Hold Time for the Input Data Register                        | 0.00 | ns    |

| t <sub>ICLR2Q</sub>  | Asynchronous Clear-to-Q of the Input Data Register                  | 0.79 | ns    |

| t <sub>IPRE2Q</sub>  | Asynchronous Preset-to-Q of the Input Data Register                 | 0.79 | ns    |

| t <sub>IREMCLR</sub> | Asynchronous Clear Removal Time for the Input Data Register         | 0.00 | ns    |

| t <sub>IRECCLR</sub> | Asynchronous Clear Recovery Time for the Input Data Register        | 0.24 | ns    |

| t <sub>IREMPRE</sub> | Asynchronous Preset Removal Time for the Input Data Register        | 0.00 | ns    |

| t <sub>IRECPRE</sub> | Asynchronous Preset Recovery Time for the Input Data Register       | 0.24 | ns    |

| t <sub>IWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Input Data Register  | 0.19 | ns    |

| t <sub>IWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Input Data Register | 0.19 | ns    |

| t <sub>ICKMPWH</sub> | Clock Minimum Pulse Width High for the Input Data Register          | 0.31 | ns    |

| t <sub>ICKMPWL</sub> | Clock Minimum Pulse Width Low for the Input Data Register           | 0.28 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

## **Global Tree Timing Characteristics**

Global clock delays include the central rib delay, the spine delay, and the row delay. Delays do not include I/O input buffer clock delays, as these are I/O standard–dependent, and the clock may be driven and conditioned internally by the CCC module. For more details on clock conditioning capabilities, refer to the "Clock Conditioning Circuits" section on page 2-115. Table 2-173 to Table 2-188 on page 2-114 present minimum and maximum global clock delays within each device. Minimum and maximum delays are measured with minimum and maximum loading.

#### **Timing Characteristics**

#### 1.5 V DC Core Voltage

#### Table 2-173 • AGL015 Global Resource

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | S                 | td.               |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.21              | 1.42              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.23              | 1.49              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.18              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.15              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.27              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

#### Table 2-174 • AGL030 Global Resource

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | S                 | Std.              |       |  |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|--|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |  |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.21              | 1.42              | ns    |  |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.23              | 1.49              | ns    |  |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.18              |                   | ns    |  |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.15              |                   | ns    |  |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.27              | ns    |  |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

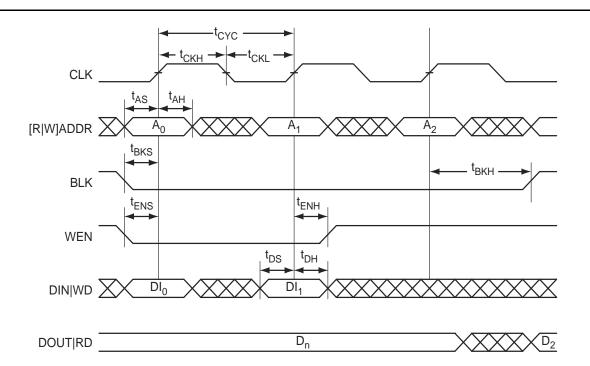

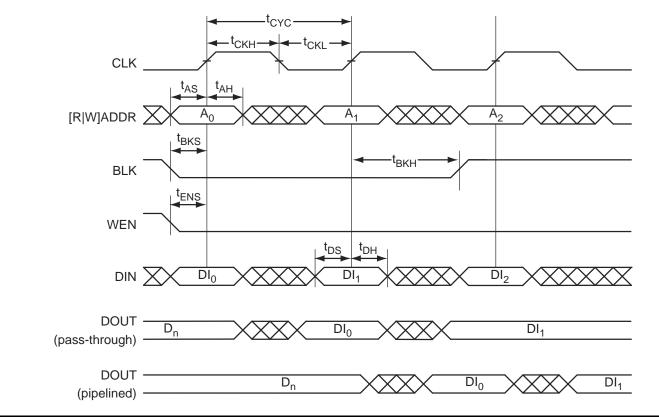

Figure 2-35 • RAM Write, Output as Write Data (WMODE = 1). Applicable to RAM4K9 only.

#### VJTAG JTAG Supply Voltage

Low power flash devices have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). Isolating the JTAG power supply in a separate I/O bank gives greater flexibility in supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned for use, the VJTAG pin together with the TRST pin could be tied to GND. It should be noted that VCC is required to be powered for JTAG operation; VJTAG alone is insufficient. If a device is in a JTAG chain of interconnected boards, the board containing the device can be powered down, provided both VJTAG and VCC to the part remain powered; otherwise, JTAG signals will not be able to transition the device, even in bypass mode.

Microsemi recommends that VPUMP and VJTAG power supplies be kept separate with independent filtering capacitors rather than supplying them from a common rail.

#### VPUMP Programming Supply Voltage

IGLOO devices support single-voltage ISP of the configuration flash and FlashROM. For programming, VPUMP should be 3.3 V nominal. During normal device operation, VPUMP can be left floating or can be tied (pulled up) to any voltage between 0 V and the VPUMP maximum. Programming power supply voltage (VPUMP) range is listed in the datasheet.

When the VPUMP pin is tied to ground, it will shut off the charge pump circuitry, resulting in no sources of oscillation from the charge pump circuitry.

For proper programming, 0.01  $\mu$ F and 0.33  $\mu$ F capacitors (both rated at 16 V) are to be connected in parallel across VPUMP and GND, and positioned as close to the FPGA pins as possible.

Microsemi recommends that VPUMP and VJTAG power supplies be kept separate with independent filtering capacitors rather than supplying them from a common rail.

## **User Pins**

#### I/O

#### User Input/Output

The I/O pin functions as an input, output, tristate, or bidirectional buffer. Input and output signal levels are compatible with the I/O standard selected.

During programming, I/Os become tristated and weakly pulled up to VCCI. With VCCI, VMV, and VCC supplies continuously powered up, when the device transitions from programming to operating mode, the I/Os are instantly configured to the desired user configuration.

Unused I/Os are configured as follows:

- Output buffer is disabled (with tristate value of high impedance)

- Input buffer is disabled (with tristate value of high impedance)

- Weak pull-up is programmed

#### GL Globals

GL I/Os have access to certain clock conditioning circuitry (and the PLL) and/or have direct access to the global network (spines). Additionally, the global I/Os can be used as regular I/Os, since they have identical capabilities. Unused GL pins are configured as inputs with pull-up resistors.

See more detailed descriptions of global I/O connectivity in the "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" chapter of the *IGLOO FPGA Fabric User Guide*. All inputs labeled GC/GF are direct inputs into the quadrant clocks. For example, if GAA0 is used for an input, GAA1 and GAA2 are no longer available for input to the quadrant globals. All inputs labeled GC/GF are direct inputs into the chip-level globals, and the rest are connected to the quadrant globals. The inputs to the global network are multiplexed, and only one input can be used as a global input.

Refer to the "I/O Structures in IGLOO and ProASIC3 Devices" chapter of the *IGLOO FPGA Fabric User Guide* for an explanation of the naming of global pins.

#### FF

#### Flash\*Freeze Mode Activation Pin

Flash\*Freeze mode is available on IGLOO devices. The FF pin is a dedicated input pin used to enter and exit Flash\*Freeze mode. The FF pin is active low, has the same characteristics as a single-ended I/O, and must meet the maximum rise and fall times. When Flash\*Freeze mode is not used in the design, the FF pin is available as a regular I/O.

When Flash\*Freeze mode is used, the FF pin must not be left floating to avoid accidentally entering Flash\*Freeze mode. While in Flash\*Freeze mode, the Flash\*Freeze pin should be constantly asserted.

Package Pin Assignments

|            | CS196           |            | CS196           |            | CS196           |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | AGL125 Function | Pin Number | AGL125 Function | Pin Number | AGL125 Function |

| A1         | GND             | C9         | IO23RSB0        | F3         | IO113RSB1       |

| A2         | GAA0/IO00RSB0   | C10        | IO29RSB0        | F4         | IO112RSB1       |

| A3         | GAC0/IO04RSB0   | C11        | VCCIB0          | F5         | IO111RSB1       |

| A4         | GAC1/IO05RSB0   | C12        | IO42RSB0        | F6         | NC              |

| A5         | IO09RSB0        | C13        | GNDQ            | F7         | VCC             |

| A6         | IO15RSB0        | C14        | IO44RSB0        | F8         | VCC             |

| A7         | IO18RSB0        | D1         | IO127RSB1       | F9         | NC              |

| A8         | IO22RSB0        | D2         | IO129RSB1       | F10        | IO07RSB0        |

| A9         | IO27RSB0        | D3         | GAA2/IO132RSB1  | F11        | IO25RSB0        |

| A10        | GBC0/IO35RSB0   | D4         | IO126RSB1       | F12        | IO10RSB0        |

| A11        | GBB0/IO37RSB0   | D5         | IO06RSB0        | F13        | IO33RSB0        |

| A12        | GBB1/IO38RSB0   | D6         | IO13RSB0        | F14        | IO47RSB0        |

| A13        | GBA1/IO40RSB0   | D7         | IO19RSB0        | G1         | GFB1/IO121RSB1  |

| A14        | GND             | D8         | IO21RSB0        | G2         | GFA0/IO119RSB1  |

| B1         | VCCIB1          | D9         | IO26RSB0        | G3         | GFA2/IO117RSB1  |

| B2         | VMV0            | D10        | IO31RSB0        | G4         | VCOMPLF         |

| B3         | GAA1/IO01RSB0   | D11        | IO30RSB0        | G5         | GFC0/IO122RSB1  |

| B4         | GAB1/IO03RSB0   | D12        | VMV0            | G6         | VCC             |

| B5         | GND             | D13        | IO46RSB0        | G7         | GND             |

| B6         | IO16RSB0        | D14        | GBC2/IO45RSB0   | G8         | GND             |

| B7         | IO20RSB0        | E1         | IO125RSB1       | G9         | VCC             |

| B8         | IO24RSB0        | E2         | GND             | G10        | GCC0/IO52RSB0   |

| B9         | IO28RSB0        | E3         | IO131RSB1       | G11        | GCB1/IO53RSB0   |

| B10        | GND             | E4         | VCCIB1          | G12        | GCA0/IO56RSB0   |

| B11        | GBC1/IO36RSB0   | E5         | NC              | G13        | IO48RSB0        |

| B12        | GBA0/IO39RSB0   | E6         | IO08RSB0        | G14        | GCC2/IO59RSB0   |

| B13        | GBA2/IO41RSB0   | E7         | IO17RSB0        | H1         | GFB0/IO120RSB1  |

| B14        | GBB2/IO43RSB0   | E8         | IO12RSB0        | H2         | GFA1/IO118RSB1  |

| C1         | GAC2/IO128RSB1  | E9         | IO11RSB0        | H3         | VCCPLF          |

| C2         | GAB2/IO130RSB1  | E10        | NC              | H4         | GFB2/IO116RSB1  |

| C3         | GNDQ            | E11        | VCCIB0          | H5         | GFC1/IO123RSB1  |

| C4         | VCCIB0          | E12        | IO32RSB0        | H6         | VCC             |

| C5         | GAB0/IO02RSB0   | E13        | GND             | H7         | GND             |

| C6         | IO14RSB0        | E14        | IO34RSB0        | H8         | GND             |

| C7         | VCCIB0          | F1         | IO124RSB1       | H9         | VCC             |

| C8         | NC              | F2         | IO114RSB1       | H10        | GCC1/IO51RSB0   |

|            | CS281           | ) [        | CS281            |

|------------|-----------------|------------|------------------|

| Pin Number | AGL600 Function | Pin Number | AGL600 Function  |

| R15        | IO94RSB2        | V10        | IO112RSB2        |

| R15        | GDA1/IO88PPB1   | V10<br>V11 | IO112R3B2        |

| R10        | GDB0/IO87NPB1   | V11<br>V12 |                  |

| _          |                 |            | IO108RSB2        |

| R19        | GDC0/IO86NPB1   | V13        | IO102RSB2        |

| T1         | IO148PPB3       | V14        | GND              |

| T2         | GEC0/IO146NPB3  | V15        | IO93RSB2         |

| T4         | GEB0/IO145NPB3  | V16        | GDA2/IO89RSB2    |

| T5         | IO132RSB2       | V17        | TDI              |

| T6         | IO136RSB2       | V18        | VCCIB2           |

| T7         | IO130RSB2       | V19        | TDO              |

| T8         | IO126RSB2       | W1         | GND              |

| Т9         | IO120RSB2       | W2         | FF/GEB2/IO142RSE |

| T10        | GND             | W3         | IO139RSB2        |

| T11        | IO113RSB2       | W4         | IO137RSB2        |

| T12        | IO104RSB2       | W5         | IO134RSB2        |

| T13        | IO101RSB2       | W6         | IO133RSB2        |

| T14        | IO98RSB2        | W7         | IO128RSB2        |

| T15        | GDC2/IO91RSB2   | W8         | IO124RSB2        |

| T16        | TMS             | W9         | IO119RSB2        |

| T18        | VJTAG           | W10        | VCCIB2           |

| T19        | GDB1/IO87PPB1   | W11        | IO109RSB2        |

| U1         | IO147PDB3       | W12        | IO107RSB2        |

| U2         | GEA1/IO144PPB3  | W13        | IO105RSB2        |

| U6         | IO131RSB2       | W14        | IO100RSB2        |

| U14        | IO99RSB2        | W15        | IO96RSB2         |

| U18        | TRST            | W16        | IO92RSB2         |

| U19        | GDA0/IO88NPB1   | W17        | GDB2/IO90RSB2    |

| V1         | IO147NDB3       | W18        | ТСК              |

| V2         | VCCIB3          | W19        | GND              |

| V3         | GEC2/IO141RSB2  |            | L                |

| V4         | IO140RSB2       | 1          |                  |

| V5         | IO135RSB2       | 1          |                  |

| V6         | GND             | 1          |                  |

| V7         | IO125RSB2       | 1          |                  |

| V8         | IO122RSB2       |            |                  |

|            |                 |            |                  |

V9

IO116RSB2

Package Pin Assignments

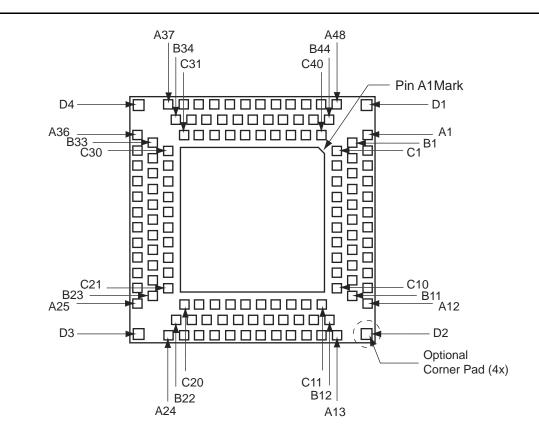

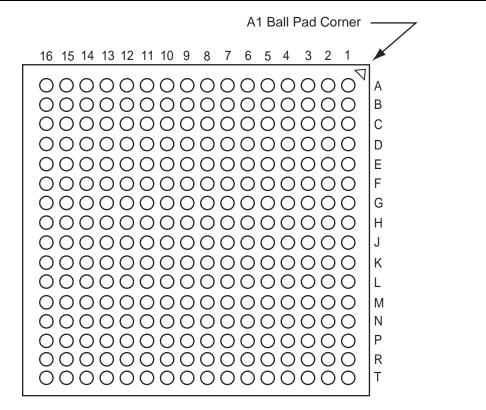

## QN132

Notes:

2. The die attach paddle center of the package is tied to ground (GND).

#### Note

QN132 package is discontinued and is not available for IGLOO devices. For more information on package drawings, see *PD3068: Package Mechanical Drawings*.

<sup>1.</sup> This is the bottom view of the package.

IGLOO Low Power Flash FPGAs

|            | QN132           |            | QN132            |            | QN132           |

|------------|-----------------|------------|------------------|------------|-----------------|

| Pin Number | AGL250 Function | Pin Number | AGL250 Function  | Pin Number | AGL250 Function |

| A1         | GAB2/IO117UPB3  | A37        | GBB1/IO38RSB0    | B25        | GND             |

| A2         | IO117VPB3       | A38        | GBC0/IO35RSB0    | B26        | IO54PDB1        |

| A3         | VCCIB3          | A39        | VCCIB0           | B27        | GCB2/IO52PDB1   |

| A4         | GFC1/IO110PDB3  | A40        | IO28RSB0         | B28        | GND             |

| A5         | GFB0/IO109NPB3  | A41        | IO22RSB0         | B29        | GCB0/IO49NDB1   |

| A6         | VCCPLF          | A42        | IO18RSB0         | B30        | GCC1/IO48PDB1   |

| A7         | GFA1/IO108PPB3  | A43        | IO14RSB0         | B31        | GND             |

| A8         | GFC2/IO105PPB3  | A44        | IO11RSB0         | B32        | GBB2/IO42PDB1   |

| A9         | IO103NDB3       | A45        | IO07RSB0         | B33        | VMV1            |

| A10        | VCC             | A46        | VCC              | B34        | GBA0/IO39RSB0   |

| A11        | GEA1/IO98PPB3   | A47        | GAC1/IO05RSB0    | B35        | GBC1/IO36RSB0   |

| A12        | GEA0/IO98NPB3   | A48        | GAB0/IO02RSB0    | B36        | GND             |

| A13        | GEC2/IO95RSB2   | B1         | IO118VDB3        | B37        | IO26RSB0        |

| A14        | IO91RSB2        | B2         | GAC2/IO116UDB3   | B38        | IO21RSB0        |

| A15        | VCC             | B3         | GND              | B39        | GND             |

| A16        | IO90RSB2        | B4         | GFC0/IO110NDB3   | B40        | IO13RSB0        |

| A17        | IO87RSB2        | B5         | VCOMPLF          | B41        | IO08RSB0        |

| A18        | IO85RSB2        | B6         | GND              | B42        | GND             |

| A19        | IO82RSB2        | B7         | GFB2/IO106PSB3   | B43        | GAC0/IO04RSB0   |

| A20        | IO76RSB2        | B8         | IO103PDB3        | B44        | GNDQ            |

| A21        | IO70RSB2        | B9         | GND              | C1         | GAA2/IO118UDB3  |

| A22        | VCC             | B10        | GEB0/IO99NDB3    | C2         | IO116VDB3       |

| A23        | GDB2/IO62RSB2   | B11        | VMV3             | C3         | VCC             |

| A24        | TDI             | B12        | FF/GEB2/IO96RSB2 | C4         | GFB1/IO109PPB3  |

| A25        | TRST            | B13        | IO92RSB2         | C5         | GFA0/IO108NPB3  |

| A26        | GDC1/IO58UDB1   | B14        | GND              | C6         | GFA2/IO107PSB3  |

| A27        | VCC             | B15        | IO89RSB2         | C7         | IO105NPB3       |

| A28        | IO54NDB1        | B16        | IO86RSB2         | C8         | VCCIB3          |

| A29        | IO52NDB1        | B17        | GND              | C9         | GEB1/IO99PDB3   |

| A30        | GCA2/IO51PPB1   | B18        | IO78RSB2         | C10        | GNDQ            |

| A31        | GCA0/IO50NPB1   | B19        | IO72RSB2         | C11        | GEA2/IO97RSB2   |

| A32        | GCB1/IO49PDB1   | B20        | GND              | C12        | IO94RSB2        |

| A33        | IO47NSB1        | B21        | GNDQ             | C13        | VCCIB2          |

| A34        | VCC             | B22        | TMS              | C14        | IO88RSB2        |

| A35        | IO41NPB1        | B23        | TDO              | C15        | IO84RSB2        |

| A36        | GBA2/IO41PPB1   | B24        | GDC0/IO58VDB1    | C16        | IO80RSB2        |

Note: This is the bottom view of the package.

#### Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

Package Pin Assignments

|            | FG256           |            | FG256           |            | FG256           |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | AGL400 Function | Pin Number | AGL400 Function | Pin Number | AGL400 Function |

| A1         | GND             | C7         | IO20RSB0        | E13        | GBC2/IO62PDB1   |

| A2         | GAA0/IO00RSB0   | C8         | IO24RSB0        | E14        | IO65RSB1        |

| A3         | GAA1/IO01RSB0   | C9         | IO33RSB0        | E15        | IO52RSB0        |

| A4         | GAB0/IO02RSB0   | C10        | IO39RSB0        | E16        | IO66PDB1        |

| A5         | IO16RSB0        | C11        | IO45RSB0        | F1         | IO150NDB3       |

| A6         | IO17RSB0        | C12        | GBC0/IO54RSB0   | F2         | IO149NPB3       |

| A7         | IO22RSB0        | C13        | IO48RSB0        | F3         | IO09RSB0        |

| A8         | IO28RSB0        | C14        | VMV0            | F4         | IO152UDB3       |

| A9         | IO34RSB0        | C15        | IO61NPB1        | F5         | VCCIB3          |

| A10        | IO37RSB0        | C16        | IO63PDB1        | F6         | GND             |

| A11        | IO41RSB0        | D1         | IO151VDB3       | F7         | VCC             |

| A12        | IO43RSB0        | D2         | IO151UDB3       | F8         | VCC             |

| A13        | GBB1/IO57RSB0   | D3         | GAC2/IO153UDB3  | F9         | VCC             |

| A14        | GBA0/IO58RSB0   | D4         | IO06RSB0        | F10        | VCC             |

| A15        | GBA1/IO59RSB0   | D5         | GNDQ            | F11        | GND             |

| A16        | GND             | D6         | IO10RSB0        | F12        | VCCIB1          |

| B1         | GAB2/IO154UDB3  | D7         | IO19RSB0        | F13        | IO62NDB1        |

| B2         | GAA2/IO155UDB3  | D8         | IO26RSB0        | F14        | IO49RSB0        |

| B3         | IO12RSB0        | D9         | IO30RSB0        | F15        | IO64PPB1        |

| B4         | GAB1/IO03RSB0   | D10        | IO40RSB0        | F16        | IO66NDB1        |

| B5         | IO13RSB0        | D11        | IO46RSB0        | G1         | IO148NDB3       |

| B6         | IO14RSB0        | D12        | GNDQ            | G2         | IO148PDB3       |

| B7         | IO21RSB0        | D13        | IO47RSB0        | G3         | IO149PPB3       |

| B8         | IO27RSB0        | D14        | GBB2/IO61PPB1   | G4         | GFC1/IO147PPB3  |

| B9         | IO32RSB0        | D15        | IO53RSB0        | G5         | VCCIB3          |

| B10        | IO38RSB0        | D16        | IO63NDB1        | G6         | VCC             |

| B11        | IO42RSB0        | E1         | IO150PDB3       | G7         | GND             |

| B12        | GBC1/IO55RSB0   | E2         | IO08RSB0        | G8         | GND             |

| B13        | GBB0/IO56RSB0   | E3         | IO153VDB3       | G9         | GND             |

| B14        | IO44RSB0        | E4         | IO152VDB3       | G10        | GND             |

| B15        | GBA2/IO60PDB1   | E5         | VMV0            | G11        | VCC             |

| B16        | IO60NDB1        | E6         | VCCIB0          | G12        | VCCIB1          |

| C1         | IO154VDB3       | E7         | VCCIB0          | G13        | GCC1/IO67PPB1   |

| C2         | IO155VDB3       | E8         | IO25RSB0        | G14        | IO64NPB1        |

| C3         | IO11RSB0        | E9         | IO31RSB0        | G15        | IO73PDB1        |

| C4         | IO07RSB0        | E10        | VCCIB0          | G16        | IO73NDB1        |

| C5         | GAC0/IO04RSB0   | E11        | VCCIB0          | H1         | GFB0/IO146NPB3  |

| C6         | GAC1/IO05RSB0   | E12        | VMV1            | H2         | GFA0/IO145NDB3  |

Package Pin Assignments

| FG256      |                   |  |

|------------|-------------------|--|

| Pin Number | AGL400 Function   |  |

| R5         | IO123RSB2         |  |

| R6         | IO118RSB2         |  |

| R7         | IO112RSB2         |  |

| R8         | IO106RSB2         |  |

| R9         | IO100RSB2         |  |

| R10        | IO96RSB2          |  |

| R11        | IO89RSB2          |  |

| R12        | IO85RSB2          |  |

| R13        | GDB2/IO81RSB2     |  |

| R14        | TDI               |  |

| R15        | NC                |  |

| R16        | TDO               |  |

| T1         | GND               |  |

| T2         | IO126RSB2         |  |

| Т3         | FF/GEB2/IO133RSB2 |  |

| T4         | IO124RSB2         |  |

| T5         | IO116RSB2         |  |

| T6         | IO113RSB2         |  |

| T7         | IO107RSB2         |  |

| T8         | IO105RSB2         |  |

| Т9         | IO102RSB2         |  |

| T10        | IO97RSB2          |  |

| T11        | IO92RSB2          |  |

| T12        | GDC2/IO82RSB2     |  |

| T13        | IO86RSB2          |  |

| T14        | GDA2/IO80RSB2     |  |

| T15        | TMS               |  |

| T16        | GND               |  |

| FG484      |                 |  |

|------------|-----------------|--|

| Pin Number | AGL400 Function |  |

| C21        | NC              |  |

| C22        | VCCIB1          |  |

| D1         | NC              |  |

| D2         | NC              |  |

| D3         | NC              |  |

| D4         | GND             |  |

| D5         | GAA0/IO00RSB0   |  |

| D6         | GAA1/IO01RSB0   |  |

| D7         | GAB0/IO02RSB0   |  |

| D8         | IO16RSB0        |  |

| D9         | IO17RSB0        |  |

| D10        | IO22RSB0        |  |

| D11        | IO28RSB0        |  |

| D12        | IO34RSB0        |  |

| D13        | IO37RSB0        |  |

| D14        | IO41RSB0        |  |

| D15        | IO43RSB0        |  |

| D16        | GBB1/IO57RSB0   |  |

| D17        | GBA0/IO58RSB0   |  |

| D18        | GBA1/IO59RSB0   |  |

| D19        | GND             |  |

| D20        | NC              |  |

| D21        | NC              |  |

| D22        | NC              |  |

| E1         | NC              |  |

| E2         | NC              |  |

| E3         | GND             |  |

| E4         | GAB2/IO154UDB3  |  |

| E5         | GAA2/IO155UDB3  |  |

| E6         | IO12RSB0        |  |

| E7         | GAB1/IO03RSB0   |  |

| E8         | IO13RSB0        |  |

| E9         | IO14RSB0        |  |

| E10        | IO21RSB0        |  |

| E11        | IO27RSB0        |  |

| E12        | IO32RSB0        |  |

IGLOO Low Power Flash FPGAs

| Revision                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page            |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| (December 2012)                 | The "IGLOO Ordering Information" section has been updated to mention "Y" as "Blank" mentioning "Device Does Not Include License to Implement IP Based on the Cryptography Research, Inc. (CRI) Patent Portfolio" (SAR 43173).                                                                                                                                                                                                                                                | III             |

|                                 | The note in Table 2-189 · IGLOO CCC/PLL Specification and Table 2-190 · IGLOO CCC/PLL Specification referring the reader to SmartGen was revised to refer instead to the online help associated with the core (SAR 42564). Additionally, note regarding SSOs was added.                                                                                                                                                                                                      | 2-115,<br>2-116 |

|                                 | Live at Power-Up (LAPU) has been replaced with 'Instant On'.                                                                                                                                                                                                                                                                                                                                                                                                                 | NA              |

| Revision 22<br>(September 2012) | The "Security" section was modified to clarify that Microsemi does not support read-<br>back of programmed data.                                                                                                                                                                                                                                                                                                                                                             | 1-2             |

|                                 | Libero Integrated Design Environment (IDE) was changed to Libero System-on-Chip (SoC) throughout the document (SAR 40271).                                                                                                                                                                                                                                                                                                                                                   | N/A             |

| Revision 21<br>(May 2012)       | Under AGL125, in the Package Pin list, CS121 was incorrectly added to the datasheet in revision 19 and has been removed (SAR 38217).                                                                                                                                                                                                                                                                                                                                         | I to IV         |

|                                 | Corrected the inadvertent error for Max Values for LVPECL VIH and revised the same to '3.6' in Table 2-151 · Minimum and Maximum DC Input and Output Levels (SAR 37685).                                                                                                                                                                                                                                                                                                     | 2-82            |

|                                 | Figure 2-38 • FIFO Read and Figure 2-39 • FIFO Write have been added (SAR 34841).                                                                                                                                                                                                                                                                                                                                                                                            | 2-127           |

|                                 | The following sentence was removed from the VMVx description in the "Pin Descriptions" section: "Within the package, the VMV plane is decoupled from the simultaneous switching noise originating from the output buffer VCCI domain" and replaced with "Within the package, the VMV plane biases the input stage of the I/Os in the I/O banks" (SAR 38317). The datasheet mentions that "VMV pins must be connected to the corresponding VCCI pins" for an ESD enhancement. | 3-1             |

Datasheet Information

| Revision / Version                                  | Changes                                                                                                                                                                                                                                                                                                                                                       | Page            |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Revision 14 (Feb 2009)<br>Product Brief v1.4        | The "Advanced I/O" section was revised to include two bullets regarding wide range power supply voltage support.                                                                                                                                                                                                                                              | Ι               |

|                                                     | 3.0 V wide range was added to the list of supported voltages in the "I/Os with Advanced I/O Standards" section. The "Wide Range I/O Support" section is new.                                                                                                                                                                                                  | 1-8             |

| Revision 13 (Jan 2009)<br>Packaging v1.8            | The "CS121" pin table was revised to add a note regarding pins F1 and G1.                                                                                                                                                                                                                                                                                     | 4-7             |

| Revision 12 (Dec 2008)                              | QN48 and QN68 were added to the AGL030 for the following tables:                                                                                                                                                                                                                                                                                              | N/A             |

| Product Brief v1.3                                  | "IGLOO Devices" Product Family Table<br>"IGLOO Ordering Information"<br>"Temperature Grade Offerings"                                                                                                                                                                                                                                                         |                 |

|                                                     | QN132 is fully supported by AGL125 so footnote 3 was removed.                                                                                                                                                                                                                                                                                                 |                 |

| Packaging v1.7                                      | The "QN48" pin diagram and pin table are new.                                                                                                                                                                                                                                                                                                                 | 4-24            |

|                                                     | The "QN68" pin table for AGL030 is new.                                                                                                                                                                                                                                                                                                                       | 4-26            |

| Revision 12 (Dec 2008)                              | The AGL600 Function for pin K15 in the "FG484" table was changed to VCCIB1.                                                                                                                                                                                                                                                                                   | 4-78            |

| Revision 11 (Oct 2008)<br>Product Brief v1.2        | This document was updated to include AGL400 device information. The following sections were updated:                                                                                                                                                                                                                                                          | N/A             |

|                                                     | "IGLOO Devices" Product Family Table<br>"IGLOO Ordering Information"<br>"Temperature Grade Offerings"                                                                                                                                                                                                                                                         |                 |

|                                                     | Figure 1-2 • IGLOO Device Architecture Overview with Four I/O Banks (AGL250, AGL600, AGL400, and AGL1000)                                                                                                                                                                                                                                                     |                 |

| DC and Switching<br>Characteristics<br>Advance v0.5 | The tables in the "Quiescent Supply Current" section were updated with values for AGL400. In addition, the title was updated to include:<br>(VCC = VJTAG = VPP = $0$ V).                                                                                                                                                                                      | 2-7             |

|                                                     | The tables in the "Power Consumption of Various Internal Resources" section were updated with values for AGL400.                                                                                                                                                                                                                                              | 2-13            |

|                                                     | Table 2-178 • AGL400 Global Resource is new.                                                                                                                                                                                                                                                                                                                  | 2-109           |

| Packaging v1.6                                      | The "CS196" table for the AGL400 device is new.                                                                                                                                                                                                                                                                                                               | 4-14            |

|                                                     | The "FG144" table for the AGL400 device is new.                                                                                                                                                                                                                                                                                                               | 4-47            |

|                                                     | The "FG256" table for the AGL400 device is new.                                                                                                                                                                                                                                                                                                               | 4-54            |

|                                                     | The "FG484" table for the AGL400 device is new.                                                                                                                                                                                                                                                                                                               | 4-64            |

| Revision 10 (Aug 2008)                              | 3.0 V LVCMOS wide range support data was added to Table 2-2 • Recommended<br>Operating Conditions 1.                                                                                                                                                                                                                                                          | 2-2             |

| DC and Switching<br>Characteristics<br>Advance v0.4 | 3.3 V LVCMOS wide range support data was added to Table 2-25 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings to Table 2-27 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings. | 2-24 to<br>2-26 |