Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Active                                                                     |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | 24576                                                                      |

| Total RAM Bits                 | 147456                                                                     |

| Number of I/O                  | 215                                                                        |

| Number of Gates                | 1000000                                                                    |

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                            |

| Package / Case                 | 281-TFBGA, CSBGA                                                           |

| Supplier Device Package        | 281-CSP (10x10)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/agl1000v5-csg281 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

field upgrades with confidence that valuable intellectual property cannot be compromised or copied. Secure ISP can be performed using the industry-standard AES algorithm. The IGLOO family device architecture mitigates the need for ASIC migration at higher user volumes. This makes the IGLOO family a cost-effective ASIC replacement solution, especially for applications in the consumer, networking/communications, computing, and avionics markets.

### Firm-Error Immunity

Firm errors occur most commonly when high-energy neutrons, generated in the upper atmosphere, strike a configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and thus change the logic, routing, or I/O behavior in an unpredictable way. These errors are impossible to prevent in SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not exist in the configuration memory of IGLOO flash-based FPGAs. Once it is programmed, the flash cell configuration element of IGLOO FPGAs cannot be altered by high-energy neutrons and is therefore immune to them. Recoverable (or soft) errors occur in the user data SRAM of all FPGA devices. These can easily be mitigated by using error detection and correction (EDAC) circuitry built into the FPGA fabric.

### Advanced Flash Technology

The IGLOO family offers many benefits, including nonvolatility and reprogrammability, through an advanced flash-based, 130-nm LVCMOS process with seven layers of metal. Standard CMOS design techniques are used to implement logic and control functions. The combination of fine granularity, enhanced flexible routing resources, and abundant flash switches allows for very high logic utilization without compromising device routability or performance. Logic functions within the device are interconnected through a four-level routing hierarchy.

IGLOO family FPGAs utilize design and process techniques to minimize power consumption in all modes of operation.

### Advanced Architecture

The proprietary IGLOO architecture provides granularity comparable to standard-cell ASICs. The IGLOO device consists of five distinct and programmable architectural features (Figure 1-1 on page 1-4 and Figure 1-2 on page 1-4):

- Flash\*Freeze technology

- FPGA VersaTiles

- · Dedicated FlashROM

- Dedicated SRAM/FIFO memory<sup>†</sup>

- Extensive CCCs and PLLs<sup>†</sup>

- Advanced I/O structure

The FPGA core consists of a sea of VersaTiles. Each VersaTile can be configured as a three-input logic function, a D-flip-flop (with or without enable), or a latch by programming the appropriate flash switch interconnections. The versatility of the IGLOO core tile as either a three-input lookup table (LUT) equivalent or a D-flip-flop/latch with enable allows for efficient use of the FPGA fabric. The VersaTile capability is unique to the ProASIC<sup>®</sup> family of third-generation-architecture flash FPGAs.

1-3 Revision 27

<sup>†</sup> The AGL015 and AGL030 do not support PLL or SRAM.

Table 2-15 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings Applicable to Standard I/O Banks

|                                      | VCCI (V) | Static Power<br>PDC6 (mW) <sup>1</sup> | Dynamic Power<br>PAC9 (μW/MHz) <sup>2</sup> |

|--------------------------------------|----------|----------------------------------------|---------------------------------------------|

| Single-Ended                         |          |                                        |                                             |

| 3.3 V LVTTL / 3.3 V LVCMOS           | 3.3      | _                                      | 17.24                                       |

| 3.3 V LVCMOS Wide Range <sup>3</sup> | 3.3      | -                                      | 17.24                                       |

| 2.5 V LVCMOS                         | 2.5      | _                                      | 5.64                                        |

| 1.8 V LVCMOS                         | 1.8      | -                                      | 2.63                                        |

| 1.5 V LVCMOS (JESD8-11)              | 1.5      | _                                      | 1.97                                        |

| 1.2 V LVCMOS <sup>4</sup>            | 1.2      | _                                      | 0.57                                        |

| 1.2 V LVCMOS Wide Range <sup>4</sup> | 1.2      | -                                      | 0.57                                        |

- 1. PDC6 is the static power (where applicable) measured on VCCI.

- 2. PAC9 is the total dynamic power measured on VCCI.

- 3. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

- 4. Applicable for IGLOO V2 devices only.

Table 2-16 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings<sup>1</sup>

Applicable to Advanced I/O Banks

| C <sub>LOAD</sub> (pF) | VCCI (V)                             | Static Power PDC7 (mW) <sup>2</sup>                           | Dynamic Power<br>PAC10 (μW/MHz) <sup>3</sup>                                                                                                                                                                                                                                                                                                                          |

|------------------------|--------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |                                      |                                                               |                                                                                                                                                                                                                                                                                                                                                                       |

| 5                      | 3.3                                  | -                                                             | 136.95                                                                                                                                                                                                                                                                                                                                                                |

| 5                      | 3.3                                  | -                                                             | 136.95                                                                                                                                                                                                                                                                                                                                                                |

| 5                      | 2.5                                  | _                                                             | 76.84                                                                                                                                                                                                                                                                                                                                                                 |

| 5                      | 1.8                                  | -                                                             | 49.31                                                                                                                                                                                                                                                                                                                                                                 |

| 5                      | 1.5                                  | -                                                             | 33.36                                                                                                                                                                                                                                                                                                                                                                 |

| 5                      | 1.2                                  | _                                                             | 16.24                                                                                                                                                                                                                                                                                                                                                                 |

| 5                      | 1.2                                  | -                                                             | 16.24                                                                                                                                                                                                                                                                                                                                                                 |

| 10                     | 3.3                                  | -                                                             | 194.05                                                                                                                                                                                                                                                                                                                                                                |

| 10                     | 3.3                                  | _                                                             | 194.05                                                                                                                                                                                                                                                                                                                                                                |

| •                      |                                      |                                                               |                                                                                                                                                                                                                                                                                                                                                                       |

| -                      | 2.5                                  | 7.74                                                          | 156.22                                                                                                                                                                                                                                                                                                                                                                |

| -                      | 3.3                                  | 19.54                                                         | 339.35                                                                                                                                                                                                                                                                                                                                                                |

|                        | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | 5 3.3<br>5 2.5<br>5 1.8<br>5 1.5<br>5 1.2<br>10 3.3<br>10 3.3 | CLOAD (pF)         VCCI (V)         PDC7 (mW)²           5         3.3         -           5         2.5         -           5         1.8         -           5         1.5         -           5         1.2         -           5         1.2         -           10         3.3         -           10         3.3         -           -         2.5         7.74 |

#### Notes:

- 1. Dynamic power consumption is given for standard load and software default drive strength and output slew.

- 2. PDC7 is the static power (where applicable) measured on VCCI.

- 3. PAC10 is the total dynamic power measured on VCCI.

- 4. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

- 5. Applicable for IGLOO V2 devices only.

2-10 Revision 27

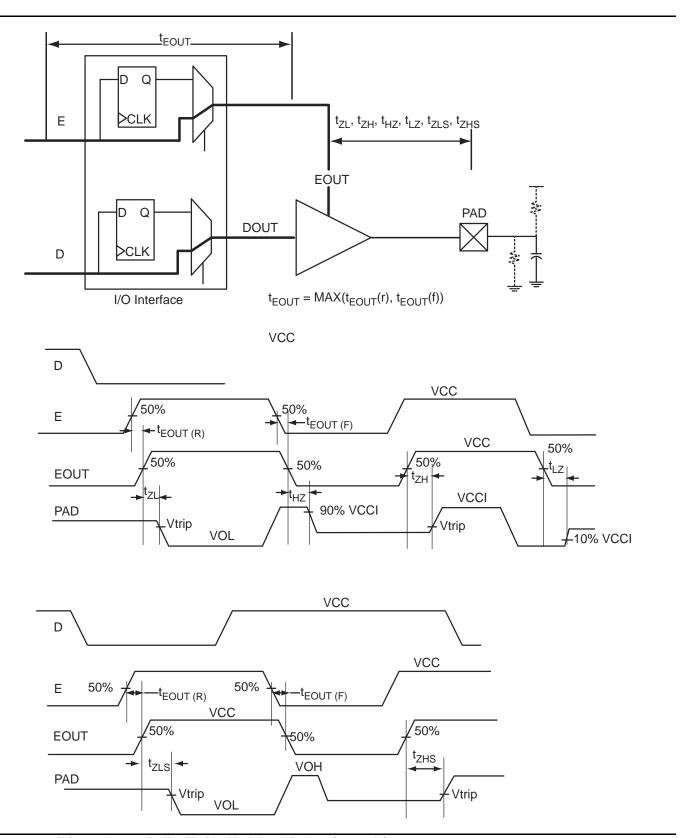

Figure 2-6 • Tristate Output Buffer Timing Model and Delays (example)

2-22 Revision 27

### **Detailed I/O DC Characteristics**

Table 2-37 • Input Capacitance

| Symbol             | Definition                         | Conditions           | Min. | Max. | Units |

|--------------------|------------------------------------|----------------------|------|------|-------|

| C <sub>IN</sub>    | Input capacitance                  | VIN = 0, f = 1.0 MHz |      | 8    | pF    |

| C <sub>INCLK</sub> | Input capacitance on the clock pin | VIN = 0, f = 1.0 MHz |      | 8    | pF    |

Table 2-38 • I/O Output Buffer Maximum Resistances<sup>1</sup>

Applicable to Advanced I/O Banks

| Standard                             | Drive Strength              | $R_{PULL-DOWN} \ \left(\Omega\right)^2$ | R <sub>PULL-UP</sub><br>(Ω) <sup>3</sup> |

|--------------------------------------|-----------------------------|-----------------------------------------|------------------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS           | 2 mA                        | 100                                     | 300                                      |

|                                      | 4 mA                        | 100                                     | 300                                      |

|                                      | 6 mA                        | 50                                      | 150                                      |

|                                      | 8 mA                        | 50                                      | 150                                      |

|                                      | 12 mA                       | 25                                      | 75                                       |

|                                      | 16 mA                       | 17                                      | 50                                       |

|                                      | 24 mA                       | 11                                      | 33                                       |

| 3.3 V LVCMOS Wide Range              | 100 μΑ                      | Same as regular 3.3 V LVCMOS            | Same as regular 3.3 V LVCMOS             |

| 2.5 V LVCMOS                         | 2 mA                        | 100                                     | 200                                      |

|                                      | 4 mA                        | 100                                     | 200                                      |

|                                      | 6 mA                        | 50                                      | 100                                      |

|                                      | 8 mA                        | 50                                      | 100                                      |

|                                      | 12 mA                       | 25                                      | 50                                       |

|                                      | 16 mA                       | 20                                      | 40                                       |

| 1.5 V LVCMOS                         | 2 mA                        | 200                                     | 224                                      |

|                                      | 4 mA                        | 100                                     | 112                                      |

|                                      | 6 mA                        | 67                                      | 75                                       |

|                                      | 8 mA                        | 33                                      | 37                                       |

|                                      | 12 mA                       | 33                                      | 37                                       |

| 1.2 V LVCMOS <sup>4</sup>            | 2 mA                        | 158                                     | 164                                      |

| 1.2 V LVCMOS Wide Range <sup>4</sup> | 100 μΑ                      | Same as regular 1.2 V LVCMOS            | Same as regular 1.2 V LVCMOS             |

| 3.3 V PCI/PCI-X                      | Per PCI/PCI-X specification | 25                                      | 75                                       |

### Notes:

2-34 Revision 27

These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCCI, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located at http://www.microsemi.com/soc/download/ibis/default.aspx.

<sup>2.</sup>  $R_{(PULL-DOWN-MAX)} = (VOLspec) / I_{OLspec}$

<sup>3.</sup>  $R_{(PULL-UP-MAX)} = (VCCImax - VOHspec) / I_{OHspec}$

<sup>4.</sup> Applicable to IGLOO V2 Devices operating at VCCI ≥ VCC

Table 2-54 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard Plus Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 0.97              | 2.32            | 0.18             | 0.85            | 0.66              | 2.37            | 1.90            | 1.98            | 2.13            | 5.96             | 5.49             | ns    |

| 4 mA           | Std.        | 0.97              | 2.32            | 0.18             | 0.85            | 0.66              | 2.37            | 1.90            | 1.98            | 2.13            | 5.96             | 5.49             | ns    |

| 6 mA           | Std.        | 0.97              | 1.94            | 0.18             | 0.85            | 0.66              | 1.99            | 1.57            | 2.20            | 2.53            | 5.58             | 5.16             | ns    |

| 8 mA           | Std.        | 0.97              | 1.94            | 0.18             | 0.85            | 0.66              | 1.99            | 1.57            | 2.20            | 2.53            | 5.58             | 5.16             | ns    |

| 12 mA          | Std.        | 0.97              | 1.75            | 0.18             | 0.85            | 0.66              | 1.79            | 1.40            | 2.36            | 2.79            | 5.38             | 4.99             | ns    |

| 16 mA          | Std.        | 0.97              | 1.75            | 0.18             | 0.85            | 0.66              | 1.79            | 1.40            | 2.36            | 2.79            | 5.38             | 4.99             | ns    |

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Table 2-55 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | Std.        | 0.97              | 3.80            | 0.18             | 0.83            | 0.66              | 3.88            | 3.41            | 1.74            | 1.78            | ns    |

| 4 mA           | Std.        | 0.97              | 3.80            | 0.18             | 0.83            | 0.66              | 3.88            | 3.41            | 1.74            | 1.78            | ns    |

| 6 mA           | Std.        | 0.97              | 3.15            | 0.18             | 0.83            | 0.66              | 3.21            | 2.94            | 1.96            | 2.17            | ns    |

| 8 mA           | Std.        | 0.97              | 3.15            | 0.18             | 0.83            | 0.66              | 3.21            | 2.94            | 1.96            | 2.17            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Table 2-56 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | Std.        | 0.97              | 2.19            | 0.18             | 0.83            | 0.66              | 2.24            | 1.79            | 1.74            | 1.87            | ns    |

| 4 mA           | Std.        | 0.97              | 2.19            | 0.18             | 0.83            | 0.66              | 2.24            | 1.79            | 1.74            | 1.87            | ns    |

| 6 mA           | Std.        | 0.97              | 1.85            | 0.18             | 0.83            | 0.66              | 1.89            | 1.46            | 1.96            | 2.26            | ns    |

| 8 mA           | Std.        | 0.97              | 1.85            | 0.18             | 0.83            | 0.66              | 1.89            | 1.46            | 1.96            | 2.26            | ns    |

### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Table 2-71 • 3.3 V LVCMOS Wide Range Low Slew – Applies to 1.5 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.7 V Applicable to Standard Banks

| Drive<br>Strength | Equivalent<br>Software<br>Default Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 100 μΑ            | 2 mA                                                                       | Std.           | 0.97              | 5.64            | 0.18             | 1.17            | 0.66              | 5.65            | 4.98            | 2.45            | 2.42            | ns    |

| 100 μΑ            | 4 mA                                                                       | Std.           | 0.97              | 5.64            | 0.18             | 1.17            | 0.66              | 5.65            | 4.98            | 2.45            | 2.42            | ns    |

| 100 μΑ            | 6 mA                                                                       | Std.           | 0.97              | 4.63            | 0.18             | 1.17            | 0.66              | 4.64            | 4.26            | 2.80            | 3.02            | ns    |

| 100 μΑ            | 8 mA                                                                       | Std.           | 0.97              | 4.63            | 0.18             | 1.17            | 0.66              | 4.64            | 4.26            | 2.80            | 3.02            | ns    |

- The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ± 100 μA. Drive strengths

displayed in software are supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Table 2-72 • 3.3 V LVCMOS Wide Range High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.7 V

Applicable to Standard Banks

| Drive<br>Strength | Equivalent<br>Software<br>Default Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 100 μΑ            | 2 mA                                                                       | 0.97           | 3.16              | 0.18            | 1.17             | 0.66            | 3.17              | 2.53            | 2.45            | 2.56            | 0.97            | ns    |

| 100 μΑ            | 4 mA                                                                       | 0.97           | 3.16              | 0.18            | 1.17             | 0.66            | 3.17              | 2.53            | 2.45            | 2.56            | 0.97            | ns    |

| 100 μΑ            | 6 mA                                                                       | 0.97           | 2.62              | 0.18            | 1.17             | 0.66            | 2.63              | 2.02            | 2.79            | 3.17            | 0.97            | ns    |

| 100 μΑ            | 8 mA                                                                       | 0.97           | 2.62              | 0.18            | 1.17             | 0.66            | 2.63              | 2.02            | 2.79            | 3.17            | 0.97            | ns    |

#### Notes:

- 1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ± 100 μA. Drive strengths displayed in software are supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

- 3. Software default selection highlighted in gray.

Table 2-100 • 1.8 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V

Applicable to Advanced I/O Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 0.97              | 3.25            | 0.18             | 1.01            | 0.66              | 3.21            | 3.25            | 2.33            | 1.61            | 6.80             | 6.85             | ns    |

| 4 mA           | Std.        | 0.97              | 2.62            | 0.18             | 1.01            | 0.66              | 2.68            | 2.51            | 2.66            | 2.46            | 6.27             | 6.11             | ns    |

| 6 mA           | Std.        | 0.97              | 2.31            | 0.18             | 1.01            | 0.66              | 2.36            | 2.15            | 2.90            | 2.87            | 5.95             | 5.75             | ns    |

| 8 mA           | Std.        | 0.97              | 2.25            | 0.18             | 1.01            | 0.66              | 2.30            | 2.08            | 2.95            | 2.98            | 5.89             | 5.68             | ns    |

| 12 mA          | Std.        | 0.97              | 2.24            | 0.18             | 1.01            | 0.66              | 2.29            | 2.00            | 3.02            | 3.40            | 5.88             | 5.60             | ns    |

| 16 mA          | Std.        | 0.97              | 2.24            | 0.18             | 1.01            | 0.66              | 2.29            | 2.00            | 3.02            | 3.40            | 5.88             | 5.60             | ns    |

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Table 2-101 • 1.8 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V

Applicable to Standard Plus Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 0.97              | 5.78            | 0.18             | 1.01            | 0.66              | 5.90            | 5.32            | 1.95            | 1.47            | 9.49             | 8.91             | ns    |

| 4 mA           | Std.        | 0.97              | 4.75            | 0.18             | 1.01            | 0.66              | 4.85            | 4.54            | 2.25            | 2.21            | 8.44             | 8.13             | ns    |

| 6 mA           | Std.        | 0.97              | 4.07            | 0.18             | 1.01            | 0.66              | 4.15            | 3.98            | 2.46            | 2.58            | 7.75             | 7.57             | ns    |

| 8 mA           | Std.        | 0.97              | 4.07            | 0.18             | 1.01            | 0.66              | 4.15            | 3.98            | 2.46            | 2.58            | 7.75             | 7.57             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Table 2-102 • 1.8 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V

Applicable to Standard Plus Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 0.97              | 2.76            | 0.18             | 1.01            | 0.66              | 2.79            | 2.76            | 1.94            | 1.51            | 6.39             | 6.35             | ns    |

| 4 mA           | Std.        | 0.97              | 2.25            | 0.18             | 1.01            | 0.66              | 2.30            | 2.09            | 2.24            | 2.29            | 5.89             | 5.69             | ns    |

| 6 mA           | Std.        | 0.97              | 1.97            | 0.18             | 1.01            | 0.66              | 2.02            | 1.76            | 2.46            | 2.66            | 5.61             | 5.36             | ns    |

| 8 mA           | Std.        | 0.97              | 1.97            | 0.18             | 1.01            | 0.66              | 2.02            | 1.76            | 2.46            | 2.66            | 5.61             | 5.36             | ns    |

### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Table 2-103 • 1.8 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V

Applicable to Standard Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | Std.        | 0.97              | 5.63            | 0.18             | 0.98            | 0.66              | 5.74            | 5.30            | 1.68            | 1.24            | ns    |

| 4 mA           | Std.        | 0.97              | 4.69            | 0.18             | 0.98            | 0.66              | 4.79            | 4.52            | 1.97            | 1.98            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

### **Timing Characteristics**

1.5 V DC Core Voltage

Table 2-115 • 1.5 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V

Applicable to Advanced I/O Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 0.97              | 6.62            | 0.18             | 1.17            | 0.66              | 6.75            | 6.06            | 2.79            | 2.31            | 10.35            | 9.66             | ns    |

| 4 mA           | Std.        | 0.97              | 5.75            | 0.18             | 1.17            | 0.66              | 5.86            | 5.34            | 3.06            | 2.78            | 9.46             | 8.93             | ns    |

| 6 mA           | Std.        | 0.97              | 5.43            | 0.18             | 1.17            | 0.66              | 5.54            | 5.19            | 3.12            | 2.90            | 9.13             | 8.78             | ns    |

| 8 mA           | Std.        | 0.97              | 5.35            | 0.18             | 1.17            | 0.66              | 5.46            | 5.20            | 2.63            | 3.36            | 9.06             | 8.79             | ns    |

| 12 mA          | Std.        | 0.97              | 5.35            | 0.18             | 1.17            | 0.66              | 5.46            | 5.20            | 2.63            | 3.36            | 9.06             | 8.79             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Table 2-116 • 1.5 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V

Applicable to Advanced I/O Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 0.97              | 2.97            | 0.18             | 1.17            | 0.66              | 3.04            | 2.90            | 2.78            | 2.40            | 6.63             | 6.50             | ns    |

| 4 mA           | Std.        | 0.97              | 2.60            | 0.18             | 1.17            | 0.66              | 2.65            | 2.45            | 3.05            | 2.88            | 6.25             | 6.05             | ns    |

| 6 mA           | Std.        | 0.97              | 2.53            | 0.18             | 1.17            | 0.66              | 2.58            | 2.37            | 3.11            | 3.00            | 6.18             | 5.96             | ns    |

| 8 mA           | Std.        | 0.97              | 2.50            | 0.18             | 1.17            | 0.66              | 2.56            | 2.27            | 3.21            | 3.48            | 6.15             | 5.86             | ns    |

| 12 mA          | Std.        | 0.97              | 2.50            | 0.18             | 1.17            | 0.66              | 2.56            | 2.27            | 3.21            | 3.48            | 6.15             | 5.86             | ns    |

### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Table 2-117 • 1.5 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V

Applicable to Standard Plus Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 0.97              | 5.93            | 0.18             | 1.18            | 0.66              | 6.04            | 5.46            | 2.30            | 2.15            | 9.64             | 9.06             | ns    |

| 4 mA           | Std.        | 0.97              | 5.11            | 0.18             | 1.18            | 0.66              | 5.21            | 4.80            | 2.54            | 2.58            | 8.80             | 8.39             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Table 2-118 • 1.5 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V

Applicable to Standard Plus Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 0.97              | 2.58            | 0.18             | 1.18            | 0.66              | 2.64            | 2.41            | 2.29            | 2.24            | 6.23             | 6.01             | ns    |

| 4 mA           | Std.        | 0.97              | 2.25            | 0.18             | 1.18            | 0.66              | 2.30            | 2.00            | 2.53            | 2.68            | 5.89             | 5.59             | ns    |

#### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

2-68 Revision 27

### 1.2 V LVCMOS (JESD8-12A)

Low-Voltage CMOS for 1.2 V complies with the LVCMOS standard JESD8-12A for general purpose 1.2 V applications. It uses a 1.2 V input buffer and a push-pull output buffer. Furthermore, all LVCMOS 1.2 V software macros comply with LVCMOS 1.2 V wide range as specified in the JESD8-12A specification.

Table 2-127 • Minimum and Maximum DC Input and Output Levels

Applicable to Advanced I/O Banks

| 1.2 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL         | VOH         | IOL | ЮН | IOSH                    | IOSL                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|-----------|-------------|-------------|-----------|-------------|-------------|-----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.26      | 0.25 * VCCI | 0.75 * VCCI | 2   | 2  | 20                      | 26                      | 10                      | 10                      |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

Table 2-128 • Minimum and Maximum DC Input and Output Levels

Applicable to Standard Plus I/O Banks

| 1.2 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL         | VOH         | I <sub>OL</sub> | ЮН | IOSH                    | IOSL                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|-----------|-------------|-------------|-----------|-------------|-------------|-----------------|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA              | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.26      | 0.25 * VCCI | 0.75 * VCCI | 2               | 2  | 20                      | 26                      | 10                      | 10                      |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

Table 2-129 • Minimum and Maximum DC Input and Output Levels

Applicable to Standard I/O Banks

| 1.2 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL         | VOH         | IOL | ЮН | IOSH                    | IOSL                    | IIL <sup>1</sup>        | IIH <sup>2</sup> |

|-------------------|-----------|-------------|-------------|-----------|-------------|-------------|-----|----|-------------------------|-------------------------|-------------------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μA <sup>4</sup>  |

| 1 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 1   | 1  | 20                      | 26                      | 10                      | 10               |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

#### 1.2 V DC Core Voltage

Table 2-145 • 3.3 V PCI/PCI-X

Commercial-Case Conditions:  $T_J = 70$ °C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V Applicable to Advanced I/O Banks

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 1.55              | 2.91            | 0.25             | 0.86            | 1.10              | 2.95            | 2.29            | 3.25            | 3.93            | 8.74             | 8.08             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

### Table 2-146 • 3.3 V PCI/PCI-X

Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V Applicable to Standard Plus I/O Banks

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 1.55              | 2.53            | 0.25             | 0.85            | 1.10              | 2.57            | 1.98            | 2.93            | 3.64            | 8.35             | 7.76             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

### **Differential I/O Characteristics**

## Physical Implementation

Configuration of the I/O modules as a differential pair is handled by Microsemi Designer software when the user instantiates a differential I/O macro in the design.

Differential I/Os can also be used in conjunction with the embedded Input Register (InReg), Output Register (OutReg), Enable Register (EnReg), and Double Data Rate (DDR). However, there is no support for bidirectional I/Os or tristates with the LVPECL standards.

### **LVDS**

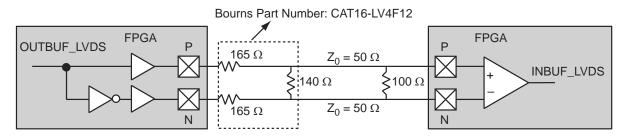

Low-Voltage Differential Signaling (ANSI/TIA/EIA-644) is a high-speed, differential I/O standard. It requires that one data bit be carried through two signal lines, so two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-13. The building blocks of the LVDS transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVPECL implementation because the output standard specifications are different.

Along with LVDS I/O, IGLOO also supports Bus LVDS structure and Multipoint LVDS (M-LVDS) configuration (up to 40 nodes).

Figure 2-13 • LVDS Circuit Diagram and Board-Level Implementation

2-76 Revision 27

Table 2-156 • Parameter Definition and Measuring Nodes

| Parameter Name       | Parameter Definition                                            | Measuring Nodes<br>(from, to)* |

|----------------------|-----------------------------------------------------------------|--------------------------------|

| t <sub>OCLKQ</sub>   | Clock-to-Q of the Output Data Register                          | HH, DOUT                       |

| t <sub>OSUD</sub>    | Data Setup Time for the Output Data Register                    | FF, HH                         |

| t <sub>OHD</sub>     | Data Hold Time for the Output Data Register                     | FF, HH                         |

| tosuE                | Enable Setup Time for the Output Data Register                  | GG, HH                         |

| t <sub>OHE</sub>     | Enable Hold Time for the Output Data Register                   | GG, HH                         |

| t <sub>OCLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Data Register             | LL, DOUT                       |

| tOREMCLR             | Asynchronous Clear Removal Time for the Output Data Register    | LL, HH                         |

| torecclr             | Asynchronous Clear Recovery Time for the Output Data Register   | LL, HH                         |

| t <sub>OECLKQ</sub>  | Clock-to-Q of the Output Enable Register                        | HH, EOUT                       |

| t <sub>OESUD</sub>   | Data Setup Time for the Output Enable Register                  | JJ, HH                         |

| t <sub>OEHD</sub>    | Data Hold Time for the Output Enable Register                   | JJ, HH                         |

| toesue               | Enable Setup Time for the Output Enable Register                | KK, HH                         |

| t <sub>OEHE</sub>    | Enable Hold Time for the Output Enable Register                 | KK, HH                         |

| t <sub>OECLR2Q</sub> | Asynchronous Clear-to-Q of the Output Enable Register           | II, EOUT                       |

| toeremclr            | Asynchronous Clear Removal Time for the Output Enable Register  | II, HH                         |

| toerecclr            | Asynchronous Clear Recovery Time for the Output Enable Register | II, HH                         |

| t <sub>ICLKQ</sub>   | Clock-to-Q of the Input Data Register                           | AA, EE                         |

| t <sub>ISUD</sub>    | Data Setup Time for the Input Data Register                     | CC, AA                         |

| t <sub>IHD</sub>     | Data Hold Time for the Input Data Register                      | CC, AA                         |

| t <sub>ISUE</sub>    | Enable Setup Time for the Input Data Register                   | BB, AA                         |

| t <sub>IHE</sub>     | Enable Hold Time for the Input Data Register                    | BB, AA                         |

| t <sub>ICLR2Q</sub>  | Asynchronous Clear-to-Q of the Input Data Register              | DD, EE                         |

| t <sub>IREMCLR</sub> | Asynchronous Clear Removal Time for the Input Data Register     | DD, AA                         |

| t <sub>IRECCLR</sub> | Asynchronous Clear Recovery Time for the Input Data Register    | DD, AA                         |

Note: \*See Figure 2-17 on page 2-86 for more information.

Table 2-185 • AGL250 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 2.11              | 2.57              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 2.19              | 2.81              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.62              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Table 2-186 • AGL400 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 2.18              | 2.64              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 2.27              | 2.89              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.62              | ns    |

### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

2-108 Revision 27

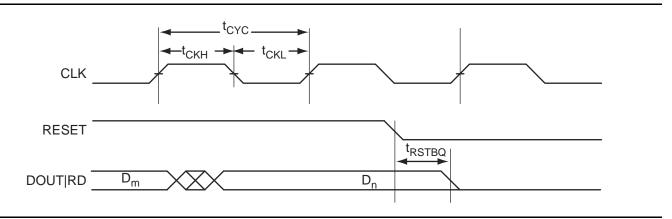

Figure 2-36 • RAM Reset. Applicable to Both RAM4K9 and RAM512x18.

2-116 Revision 27

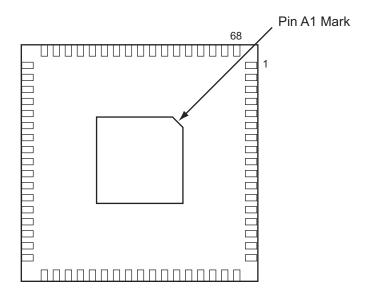

# **QN68**

### Notes:

- 1. This is the bottom view of the package.

- 2. The die attach paddle center of the package is tied to ground (GND).

### Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

# Package Pin Assignments

| FG144                        |                  |  |  |

|------------------------------|------------------|--|--|

| Pin Number   AGL250 Function |                  |  |  |

| K1                           | GEB0/IO99NDB3    |  |  |

| K2                           | GEA1/IO98PDB3    |  |  |

| K3                           | GEA0/IO98NDB3    |  |  |

| K4                           | GEA2/IO97RSB2    |  |  |

| K5                           | 02/12/100/11022  |  |  |

| _                            | IO90RSB2         |  |  |

| K6                           | IO84RSB2         |  |  |

| K7                           | GND              |  |  |

| K8                           | IO66RSB2         |  |  |

| K9                           | GDC2/IO63RSB2    |  |  |

| K10                          | GND              |  |  |

| K11                          | GDA0/IO60VDB1    |  |  |

| K12                          | GDB0/IO59VDB1    |  |  |

| L1                           | GND              |  |  |

| L2                           | VMV3             |  |  |

| L3                           | FF/GEB2/IO96RSB2 |  |  |

| L4                           | IO91RSB2         |  |  |

| L5                           | VCCIB2           |  |  |

| L6                           | IO82RSB2         |  |  |

| L7                           | IO80RSB2         |  |  |

| L8                           | IO72RSB2         |  |  |

| L9                           | TMS              |  |  |

| L10                          | VJTAG            |  |  |

| L11                          | VMV2             |  |  |

| L12                          | TRST             |  |  |

| M1                           | GNDQ             |  |  |

| M2                           | GEC2/IO95RSB2    |  |  |

| M3                           | IO92RSB2         |  |  |

| M4                           | IO89RSB2         |  |  |

| M5                           | IO87RSB2         |  |  |

| M6                           | IO85RSB2         |  |  |

| M7                           | IO78RSB2         |  |  |

| M8                           | IO76RSB2         |  |  |

| M9                           | TDI              |  |  |

| M10                          | VCCIB2           |  |  |

| M11                          | VPUMP            |  |  |

| M12                          | GNDQ             |  |  |

4-46 Revision 27

Package Pin Assignments

| FG144                        |                   |  |  |

|------------------------------|-------------------|--|--|

| Pin Number   AGL600 Function |                   |  |  |

| K1                           | GEB0/IO145NDB3    |  |  |

| K2                           | GEA1/IO144PDB3    |  |  |

| K3                           | GEA0/IO144NDB3    |  |  |

| K4                           | GEA2/IO143RSB2    |  |  |

| K5                           | IO119RSB2         |  |  |

| K6                           | IO111RSB2         |  |  |

| K7                           | GND               |  |  |

| K8                           | IO94RSB2          |  |  |

| K9                           | GDC2/IO91RSB2     |  |  |

| K10                          | GND               |  |  |

| K11                          | GDA0/IO88NDB1     |  |  |

| K12                          | GDB0/IO87NDB1     |  |  |

| L1                           | GND               |  |  |

| L2                           | VMV3              |  |  |

| L3                           | FF/GEB2/IO142RSB2 |  |  |

| L4                           | IO136RSB2         |  |  |

| L5                           | VCCIB2            |  |  |

| L6                           | IO115RSB2         |  |  |

| L7                           | IO103RSB2         |  |  |

| L8                           | IO97RSB2          |  |  |

| L9                           | TMS               |  |  |

| L10                          | VJTAG             |  |  |

| L11                          | VMV2              |  |  |

| L12                          | TRST              |  |  |

| M1                           | GNDQ              |  |  |

| M2                           | GEC2/IO141RSB2    |  |  |

| M3                           | IO138RSB2         |  |  |

| M4                           | IO123RSB2         |  |  |

| M5                           | IO126RSB2         |  |  |

| M6                           | IO134RSB2         |  |  |

| M7                           | IO108RSB2         |  |  |

| M8                           | IO99RSB2          |  |  |

| M9                           | TDI               |  |  |

| M10                          | VCCIB2            |  |  |

| M11                          | VPUMP             |  |  |

| M12                          | GNDQ              |  |  |

4-50 Revision 27

# Package Pin Assignments

| FG484      |                 |  |  |

|------------|-----------------|--|--|

| Pin Number | AGL400 Function |  |  |

| E13        | IO38RSB0        |  |  |

| E14        | IO42RSB0        |  |  |

| E15        | GBC1/IO55RSB0   |  |  |

| E16        | GBB0/IO56RSB0   |  |  |

| E17        | IO44RSB0        |  |  |

| E18        | GBA2/IO60PDB1   |  |  |

| E19        | IO60NDB1        |  |  |

| E20        | GND             |  |  |

| E21        | NC              |  |  |

| E22        | NC              |  |  |

| F1         | NC              |  |  |

| F2         | NC              |  |  |

| F3         | NC              |  |  |

| F4         | IO154VDB3       |  |  |

| F5         | IO155VDB3       |  |  |

| F6         | IO11RSB0        |  |  |

| F7         | IO07RSB0        |  |  |

| F8         | GAC0/IO04RSB0   |  |  |

| F9         | GAC1/IO05RSB0   |  |  |

| F10        | IO20RSB0        |  |  |

| F11        | IO24RSB0        |  |  |

| F12        | IO33RSB0        |  |  |

| F13        | IO39RSB0        |  |  |

| F14        | IO45RSB0        |  |  |

| F15        | GBC0/IO54RSB0   |  |  |

| F16        | IO48RSB0        |  |  |

| F17        | VMV0            |  |  |

| F18        | IO61NPB1        |  |  |

| F19        | IO63PDB1        |  |  |

| F20        | NC              |  |  |

| F21        | NC              |  |  |

| F22        | NC              |  |  |

| G1         | NC              |  |  |

| G2         | NC              |  |  |

| G3         | NC              |  |  |

| G4         | IO151VDB3       |  |  |

4-68 Revision 27

| FG484                         |           |  |  |

|-------------------------------|-----------|--|--|

| Pin Number   AGL1000 Function |           |  |  |

| AA15                          | NC        |  |  |

| AA16                          | IO122RSB2 |  |  |

| AA17                          | IO119RSB2 |  |  |

| AA18                          | IO117RSB2 |  |  |

| AA19                          | NC        |  |  |

| AA20                          | NC        |  |  |

| AA21                          | VCCIB1    |  |  |

| AA22                          | GND       |  |  |

| AB1                           | GND       |  |  |

| AB2                           | GND       |  |  |

| AB3                           | VCCIB2    |  |  |

| AB4                           | IO180RSB2 |  |  |

| AB5                           | IO176RSB2 |  |  |

| AB6                           | IO173RSB2 |  |  |

| AB7                           | IO167RSB2 |  |  |

| AB8                           | IO162RSB2 |  |  |

| AB9                           | IO156RSB2 |  |  |

| AB10                          | IO150RSB2 |  |  |

| AB11                          | IO145RSB2 |  |  |

| AB12                          | IO144RSB2 |  |  |

| AB13                          | IO132RSB2 |  |  |

| AB14                          | IO127RSB2 |  |  |

| AB15                          | IO126RSB2 |  |  |

| AB16                          | IO123RSB2 |  |  |

| AB17                          | IO121RSB2 |  |  |

| AB18                          | IO118RSB2 |  |  |

| AB19                          | NC        |  |  |

| AB20                          | VCCIB2    |  |  |

| AB21                          | GND       |  |  |

| AB22                          | GND       |  |  |

| B1                            | GND       |  |  |

| B2                            | VCCIB3    |  |  |

| В3                            | NC        |  |  |

| B4                            | IO06RSB0  |  |  |

| B5                            | IO08RSB0  |  |  |

| В6                            | IO12RSB0  |  |  |

| FG484                         |                |  |  |

|-------------------------------|----------------|--|--|

| Pin Number   AGL1000 Function |                |  |  |

| G5                            | IO222PDB3      |  |  |

| G6                            | GAC2/IO223PDB3 |  |  |

| G7                            | IO223NDB3      |  |  |

| G8                            | GNDQ           |  |  |

| G9                            | IO23RSB0       |  |  |

| G10                           | IO29RSB0       |  |  |

| G11                           | IO33RSB0       |  |  |

| G12                           | IO46RSB0       |  |  |

| G13                           | IO52RSB0       |  |  |

| G14                           | IO60RSB0       |  |  |

| G15                           | GNDQ           |  |  |

| G16                           | IO80NDB1       |  |  |

| G17                           | GBB2/IO79PDB1  |  |  |

| G18                           | IO79NDB1       |  |  |

| G19                           | IO82NPB1       |  |  |

| G20                           | IO85PDB1       |  |  |

| G21                           | IO85NDB1       |  |  |

| G22                           | NC             |  |  |

| H1                            | NC             |  |  |

| H2                            | NC             |  |  |

| H3                            | VCC            |  |  |

| H4                            | IO217PDB3      |  |  |

| H5                            | IO218PDB3      |  |  |

| H6                            | IO221NDB3      |  |  |

| H7                            | IO221PDB3      |  |  |

| H8                            | VMV0           |  |  |

| H9                            | VCCIB0         |  |  |

| H10                           | VCCIB0         |  |  |

| H11                           | IO38RSB0       |  |  |

| H12                           | IO47RSB0       |  |  |

| H13                           | VCCIB0         |  |  |

| H14                           | VCCIB0         |  |  |

| H15                           | VMV1           |  |  |

| H16                           | GBC2/IO80PDB1  |  |  |

| H17                           | IO83PPB1       |  |  |

| H18                           | IO86PPB1       |  |  |

IGLOO Low Power Flash FPGAs

| Revision / Version                                  | Changes                                                                                                                                                                                                                                                                  | Page         |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Revision 18 (Nov 2009)                              | The version changed to v2.0 for IGLOO datasheet chapters, indicating the datasheet contains information based on final characterization. Please review the datasheet carefully as most tables were updated with new data.                                                | N/A          |

| Revision 17 (Sep 2009) Product Brief v1.6           | The "Reprogrammable Flash Technology" section was modified to add "250 MHz (1.5 V systems) and 160 MHz (1.2 V systems) System Performance."                                                                                                                              | I            |

|                                                     | "IGLOO Ordering Information" was revised to note that halogen-free packages are available with RoHS-compliant packaging.                                                                                                                                                 | III          |

|                                                     | Table 1-1 • I/O Standards Supported is new.                                                                                                                                                                                                                              | 1-7          |

|                                                     | The definitions of hot-swap and cold-sparing were added to the "I/Os with Advanced I/O Standards" section.                                                                                                                                                               | 1-7          |

| Revision 16 (Apr 2009)<br>Product Brief v1.5        | M1AGL400 is no longer offered and was removed from the "IGLOO Devices" product table, "IGLOO Ordering Information", and "Temperature Grade Offerings".                                                                                                                   | I, III, IV   |

|                                                     | The -F speed grade is no longer offered for IGLOO devices. The speed grade column and note regarding -F speed grade were removed from "IGLOO Ordering Information". The "Speed Grade and Temperature Grade Matrix" section was removed.                                  | III, IV      |

|                                                     | This datasheet now has fully characterized data and has moved from being Advance to a Production version. The version number changed from Advance v0.5 to v2.0.                                                                                                          | N/A          |

|                                                     | Please review the datasheet carefully as most tables were updated with new data.                                                                                                                                                                                         |              |

| DC and Switching<br>Characteristics<br>Advance v0.6 | $3.3\ V\ LVCMOS$ and $1.2\ V\ LVCMOS$ Wide Range support was added to the datasheet. This affects all tables that contained $3.3\ V\ LVCMOS$ and $1.2\ V\ LVCMOS$ data.                                                                                                  |              |

|                                                     | $\rm I_{\rm IL}$ and $\rm I_{\rm IH}$ input leakage current information was added to all "Minimum and Maximum DC Input and Output Levels" tables.                                                                                                                        | N/A          |

|                                                     | -F was removed from the datasheet. The speed grade is no longer supported.                                                                                                                                                                                               | N/A          |

|                                                     | The notes in Table 2-2 • Recommended Operating Conditions 1 were updated.                                                                                                                                                                                                | 2-2          |

|                                                     | Table 2-4 • Overshoot and Undershoot Limits 1 was updated.                                                                                                                                                                                                               | 2-3          |

|                                                     | Table 2-5 • Package Thermal Resistivities was updated.                                                                                                                                                                                                                   | 2-6          |

|                                                     | Table 2-6 • Temperature and Voltage Derating Factors for Timing Delays (normalized to TJ = $70^{\circ}$ C, VCC = $1.425$ V) and Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays (normalized to TJ = $70^{\circ}$ C, VCC = $1.14$ V) were updated. | 2-7          |