# E·XFL

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Detans                         |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Active                                                                     |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | 3072                                                                       |

| Total RAM Bits                 | 36864                                                                      |

| Number of I/O                  | 133                                                                        |

| Number of Gates                | 125000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 85°C (TA)                                                          |

| Package / Case                 | 196-TFBGA, CSBGA                                                           |

| Supplier Device Package        | 196-CSP (8x8)                                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/agl125v5-csg196i |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                 | Core<br>Voltage  | AGL015 | AGL030 | AGL060 | AGL125 | AGL250 | AGL400 | AGL600 | AGL1000 | Units |

|-------------------------------------------------|------------------|--------|--------|--------|--------|--------|--------|--------|---------|-------|

| VCCI/VJTAG = 1.2 V<br>(per bank) Typical (25°C) | 1.2 V            | 1.7    | 1.7    | 1.7    | 1.7    | 1.7    | 1.7    | 1.7    | 1.7     | μA    |

| VCCI/VJTAG = 1.5 V<br>(per bank) Typical (25°C) | 1.2 V / 1.5<br>V | 1.8    | 1.8    | 1.8    | 1.8    | 1.8    | 1.8    | 1.8    | 1.8     | μA    |

| VCCI/VJTAG = 1.8 V<br>(per bank) Typical (25°C) | 1.2 V / 1.5<br>V | 1.9    | 1.9    | 1.9    | 1.9    | 1.9    | 1.9    | 1.9    | 1.9     | μA    |

| VCCI/VJTAG = 2.5 V<br>(per bank) Typical (25°C) | 1.2 V / 1.5<br>V | 2.2    | 2.2    | 2.2    | 2.2    | 2.2    | 2.2    | 2.2    | 2.2     | μA    |

| VCCI/VJTAG = 3.3 V<br>(per bank) Typical (25°C) | 1.2 V / 1.5<br>V | 2.5    | 2.5    | 2.5    | 2.5    | 2.5    | 2.5    | 2.5    | 2.5     | μA    |

Table 2-10 • Quiescent Supply Current (IDD) Characteristics, IGLOO Sleep Mode\*

Note:  $IDD = N_{BANKS} \times ICCI$ . Values do not include I/O static contribution, which is shown in Table 2-13 on page 2-10 through Table 2-15 on page 2-11 and Table 2-16 on page 2-11 through Table 2-18 on page 2-12 (PDC6 and PDC7).

|                | Core Voltage  | AGL015 | AGL030 | Units |

|----------------|---------------|--------|--------|-------|

| Typical (25°C) | 1.2 V / 1.5 V | 0      | 0      | μΑ    |

### Table 2-12 • Quiescent Supply Current (IDD), No IGLOO Flash\*Freeze Mode<sup>1</sup>

|                                                 | Core<br>Voltage  | AGL015 | AGL030 | AGL060 | AGL125 | AGL250 | AGL400 | AGL600 | AGL1000 | Units |  |  |  |

|-------------------------------------------------|------------------|--------|--------|--------|--------|--------|--------|--------|---------|-------|--|--|--|

| CCA Current <sup>2</sup>                        |                  |        |        |        |        |        |        |        |         |       |  |  |  |

| Typical (25°C)                                  | 1.2 V            | 5      | 6      | 10     | 13     | 18     | 25     | 28     | 42      | μA    |  |  |  |

|                                                 | 1.5 V            | 14     | 16     | 20     | 28     | 44     | 66     | 82     | 137     | μA    |  |  |  |

| ICCI or IJTAG Current <sup>3</sup>              |                  |        |        |        |        |        |        |        |         |       |  |  |  |

| VCCI/VJTAG = 1.2 V<br>(per bank) Typical (25°C) | 1.2 V            | 1.7    | 1.7    | 1.7    | 1.7    | 1.7    | 1.7    | 1.7    | 1.7     | μA    |  |  |  |

| VCCI/VJTAG = 1.5 V (per<br>bank) Typical (25°C) | 1.2 V /<br>1.5 V | 1.8    | 1.8    | 1.8    | 1.8    | 1.8    | 1.8    | 1.8    | 1.8     | μA    |  |  |  |

| VCCI/VJTAG = 1.8 V (per<br>bank) Typical (25°C) | 1.2 V /<br>1.5 V | 1.9    | 1.9    | 1.9    | 1.9    | 1.9    | 1.9    | 1.9    | 1.9     | μA    |  |  |  |

| VCCI/VJTAG = 2.5 V (per<br>bank) Typical (25°C) | 1.2 V /<br>1.5 V | 2.2    | 2.2    | 2.2    | 2.2    | 2.2    | 2.2    | 2.2    | 2.2     | μA    |  |  |  |

| VCCI/VJTAG = 3.3 V (per<br>bank) Typical (25°C) | 1.2 V /<br>1.5 V | 2.5    | 2.5    | 2.5    | 2.5    | 2.5    | 2.5    | 2.5    | 2.5     | μA    |  |  |  |

Notes:

1.  $IDD = N_{BANKS} \times ICCI + ICCA$ . JTAG counts as one bank when powered.

2. Includes VCC, VPUMP, and VCCPLL currents.

3. Values do not include I/O static contribution (PDC6 and PDC7).

# Table 2-21 • Different Components Contributing to Dynamic Power Consumption in IGLOO Devices For IGLOO V2 Devices, 1.2 V DC Core Supply Voltage

|           |                                                                      |         |           | Device     | e Specific I<br>(µW/N |             | ower        |           |        |

|-----------|----------------------------------------------------------------------|---------|-----------|------------|-----------------------|-------------|-------------|-----------|--------|

| Parameter | Definition                                                           | AGL1000 | AGL600    | AGL400     | AGL250                | AGL125      | AGL060      | AGL030    | AGL015 |

| PAC1      | Clock contribution of a<br>Global Rib                                | 4.978   | 3.982     | 3.892      | 2.854                 | 2.845       | 1.751       | 0.000     | 0.000  |

| PAC2      | Clock contribution of a<br>Global Spine                              | 2.773   | 2.248     | 1.765      | 1.740                 | 1.122       | 1.261       | 2.229     | 2.229  |

| PAC3      | Clock contribution of a<br>VersaTile row                             | 0.883   | 0.924     | 0.881      | 0.949                 | 0.939       | 0.962       | 0.942     | 0.942  |

| PAC4      | Clock contribution of a<br>VersaTile used as a<br>sequential module  | 0.096   | 0.095     | 0.096      | 0.095                 | 0.095       | 0.096       | 0.094     | 0.094  |

| PAC5      | First contribution of a<br>VersaTile used as a<br>sequential module  |         |           |            | 0.04                  | 45          |             |           |        |

| PAC6      | Second contribution of a<br>VersaTile used as a<br>sequential module |         |           |            | 0.18                  | 86          |             |           |        |

| PAC7      | Contribution of a VersaTile<br>used as a combinatorial<br>module     | 0.158   | 0.149     | 0.158      | 0.157                 | 0.160       | 0.170       | 0.160     | 0.155  |

| PAC8      | Average contribution of a routing net                                | 0.756   | 0.729     | 0.753      | 0.817                 | 0.678       | 0.692       | 0.738     | 0.721  |

| PAC9      | Contribution of an I/O input pin (standard-dependent)                |         | See Table | 2-13 on pa | ge 2-10 thr           | rough Table | e 2-15 on p | age 2-11. |        |

| PAC10     | Contribution of an I/O output pin (standard-dependent)               |         | See Table | 2-16 on pa | ge 2-11 thr           | ough Table  | e 2-18 on p | age 2-12. |        |

| PAC11     | Average contribution of a<br>RAM block during a read<br>operation    | 25.00   |           |            |                       |             |             |           |        |

| PAC12     | Average contribution of a<br>RAM block during a write<br>operation   | 30.00   |           |            |                       |             |             |           |        |

| PAC13     | Dynamic PLL contribution                                             |         |           |            | 2.1                   | 0           |             |           |        |

Note: For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi power spreadsheet calculator or SmartPower tool in Libero SoC.

# Table 2-22 • Different Components Contributing to the Static Power Consumption in IGLOO Device For IGLOO V2 Devices, 1.2 V DC Core Supply Voltage

|           |                                                  |         |                            | Device     | Specific S  | tatic Powe  | r (mW)      |           |        |  |

|-----------|--------------------------------------------------|---------|----------------------------|------------|-------------|-------------|-------------|-----------|--------|--|

| Parameter | Definition                                       | AGL1000 | AGL600                     | AGL400     | AGL250      | AGL125      | AGL060      | AGL030    | AGL015 |  |

| PDC1      | Array static power in Active mode                |         |                            | See        | Table 2-12  | 2 on page 2 | -9.         |           |        |  |

| PDC2      | Array static power in Static<br>(Idle) mode      |         |                            | See        | Table 2-11  | on page 2   | -8.         |           |        |  |

| PDC3      | Array static power in<br>Flash*Freeze mode       |         | See Table 2-9 on page 2-7. |            |             |             |             |           |        |  |

| PDC4      | Static PLL contribution                          |         |                            |            | 0.9         | 90          |             |           |        |  |

| PDC5      | Bank quiescent power<br>(VCCI-Dependent)         |         |                            | See        | Table 2-12  | 2 on page 2 | -9.         |           |        |  |

| PDC6      | I/O input pin static power (standard-dependent)  |         | See Table                  | 2-13 on pa | ge 2-10 thr | rough Table | e 2-15 on p | age 2-11. |        |  |

| PDC7      | I/O output pin static power (standard-dependent) |         | See Table                  | 2-16 on pa | ge 2-11 thr | ough Table  | e 2-18 on p | age 2-12. |        |  |

Note: For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi power spreadsheet calculator or SmartPower tool in Libero SoC.

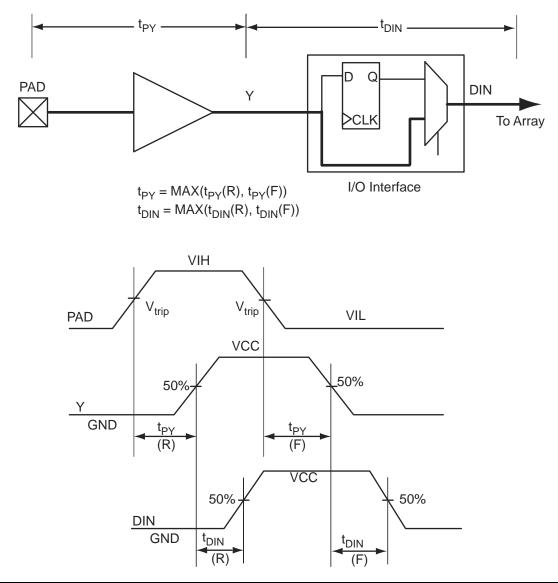

Figure 2-4 • Input Buffer Timing Model and Delays (example)

### **Overview of I/O Performance**

# Summary of I/O DC Input and Output Levels – Default I/O Software Settings

# Table 2-25 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings Applicable to Advanced I/O Banks

|                                                 |                          | Equivalent                                                      |              |       | VIL         | VIH             |       | VOL         | VOH         | IOL <sup>1</sup> | IOH <sup>1</sup> |

|-------------------------------------------------|--------------------------|-----------------------------------------------------------------|--------------|-------|-------------|-----------------|-------|-------------|-------------|------------------|------------------|

| I/O<br>Standard                                 | Drive<br>Strength        | Software<br>Default<br>Drive<br>Strength<br>Option <sup>2</sup> | Slew<br>Rate | Min.V | Max.<br>V   | Min.<br>V       | Max.V | Max.<br>V   | Min.<br>V   | mA               | mA               |

| 3.3 V<br>LVTTL /<br>3.3 V<br>LVCMOS             | 12 mA                    | 12 mA                                                           | High         | -0.3  | 0.8         | 2               | 3.6   | 0.4         | 2.4         | 12               | 12               |

| 3.3 V<br>LVCMOS<br>Wide<br>Range <sup>3</sup>   | 100 µA                   | 12 mA                                                           | High         | -0.3  | 0.8         | 2               | 3.6   | 0.2         | VCCI – 0.2  | 0.1              | 0.1              |

| 2.5 V<br>LVCMOS                                 | 12 mA                    | 12 mA                                                           | High         | -0.3  | 0.7         | 1.7             | 2.7   | 0.7         | 1.7         | 12               | 12               |

| 1.8 V<br>LVCMOS                                 | 12 mA                    | 12 mA                                                           | High         | -0.3  | 0.35 * VCCI | 0.65 * VCCI     | 1.9   | 0.45        | VCCI – 0.45 | 12               | 12               |

| 1.5 V<br>LVCMOS                                 | 12 mA                    | 12 mA                                                           | High         | -0.3  | 0.35 * VCCI | 0.65 * VCCI     | 1.575 | 0.25 * VCCI | 0.75 * VCCI | 12               | 12               |

| 1.2 V<br>LVCMOS <sup>4</sup>                    | 2 mA                     | 2 mA                                                            | High         | -0.3  | 0.35 * VCCI | 0.65 * VCCI     | 1.26  | 0.25 * VCCI | 0.75 * VCCI | 2                | 2                |

| 1.2 V<br>LVCMOS<br>Wide<br>Range <sup>4,5</sup> | 100 µA                   | 2 mA                                                            | High         | -0.3  | 0.3 * VCCI  | 0.7 * VCCI      | 1.575 | 0.1         | VCCI – 0.1  | 0.1              | 0.1              |

| 3.3 V PCI                                       |                          |                                                                 | -            | •     | Per P       | CI specificatio | ns    |             |             | •                |                  |

| 3.3 V<br>PCI-X                                  | Per PCI-X specifications |                                                                 |              |       |             |                 |       |             |             |                  |                  |

Notes:

1. Currents are measured at 85°C junction temperature.

2. The minimum drive strength for any LVCMOS 1.2 V or LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

3. All LVMCOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

4. Applicable to V2 Devices operating at VCCI  $\geq$  VCC.

5. All LVCMOS 1.2 V software macros support LVCMOS 1.2 V wide range as specified in the JESD8-12 specification.

Table 2-31 •

Summary of I/O Timing Characteristics—Software Default Settings, Std. Speed Grade, Commercial-Case

Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI (per standard)

Applicable to Advanced I/O Banks

| //O Standard                                  | Drive Strength     | Equivalent Software Default<br>Drive Strength Option <sup>1</sup> (mA) | Slew Rate | , Capacitive Load (pF) | External Resistor (Ω) | toour (ns) | t <sub>DP</sub> (ns) | t <sub>DIN</sub> (ns) | t <sub>PY</sub> (ns) | teour (ns) | t <sub>zL</sub> (ns) | t <sub>zH</sub> (ns) | t <sub>LZ</sub> (ns) | t <sub>Hz</sub> (ns) | tzLS (ns) | t <sub>zHS</sub> (ns) | Units |

|-----------------------------------------------|--------------------|------------------------------------------------------------------------|-----------|------------------------|-----------------------|------------|----------------------|-----------------------|----------------------|------------|----------------------|----------------------|----------------------|----------------------|-----------|-----------------------|-------|

| 3.3 V<br>LVTTL /<br>3.3 V<br>LVCMOS           | 12 mA              | 12                                                                     | High      | 5                      | Ι                     | 0.97       | 2.09                 | 0.18                  | 0.85                 | 0.66       | 2.14                 | 1.68                 | 2.67                 | 3.05                 | 5.73      | 5.27                  | ns    |

| 3.3 V<br>LVCMOS<br>Wide<br>Range <sup>2</sup> | 100 µA             | 12                                                                     | High      | 5                      | _                     | 0.97       | 2.93                 | 0.18                  | 1.19                 | 0.66       | 2.95                 | 2.27                 | 3.81                 | 4.30                 | 6.54      | 5.87                  | ns    |

| 2.5 V<br>LVCMOS                               | 12 mA              | 12                                                                     | High      | 5                      | -                     | 0.97       | 2.09                 | 0.18                  | 1.08                 | 0.66       | 2.14                 | 1.83                 | 2.73                 | 2.93                 | 5.73      | 5.43                  | ns    |

| 1.8 V<br>LVCMOS                               | 12 mA              | 12                                                                     | High      | 5                      | -                     | 0.97       | 2.24                 | 0.18                  | 1.01                 | 0.66       | 2.29                 | 2.00                 | 3.02                 | 3.40                 | 5.88      | 5.60                  | ns    |

| 1.5 V<br>LVCMOS                               | 12 mA              | 12                                                                     | High      | 5                      | -                     | 0.97       | 2.50                 | 0.18                  | 1.17                 | 0.66       | 2.56                 | 2.27                 | 3.21                 | 3.48                 | 6.15      | 5.86                  | ns    |

| 3.3 V PCI                                     | Per PCI<br>spec    | Ι                                                                      | High      | 10                     | 25 <sup>2</sup>       | 0.97       | 2.32                 | 0.18                  | 0.74                 | 0.66       | 2.37                 | 1.78                 | 2.67                 | 3.05                 | 5.96      | 5.38                  | ns    |

| 3.3 V<br>PCI-X                                | Per PCI-<br>X spec | Ι                                                                      | High      | 10                     | 25 <sup>2</sup>       | 0.97       | 2.32                 | 0.19                  | 0.70                 | 0.66       | 2.37                 | 1.78                 | 2.67                 | 3.05                 | 5.96      | 5.38                  | ns    |

| LVDS                                          | 24 mA              | -                                                                      | High      | Ι                      | -                     | 0.97       | 1.74                 | 0.19                  | 1.35                 | -          | -                    | -                    | -                    | -                    | -         | -                     | ns    |

| LVPECL                                        | 24 mA              | -                                                                      | High      | _                      | -                     | 0.97       | 1.68                 | 0.19                  | 1.16                 | _          | _                    | -                    | -                    | _                    | -         | -                     | ns    |

Notes:

1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

3. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-12 on page 2-79 for connectivity. This resistor is not required during normal operation.

4. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

| Table 2-97 • | Minimum and Maximum DC Input and Output Levels |

|--------------|------------------------------------------------|

|              | Applicable to Standard I/O Banks               |

| 1.8 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL       | VOH         | IOL | ЮН | IOSH                    | IOSL                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|-----------|-------------|-------------|-----------|-----------|-------------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.45      | VCCI - 0.45 | 2   | 2  | 9                       | 11                      | 10               | 10               |

| 4 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.45      | VCCI – 0.45 | 4   | 4  | 17                      | 22                      | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

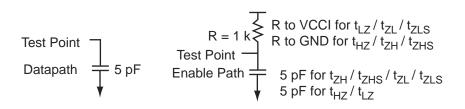

### Figure 2-9 • AC Loading

Table 2-98 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 1.8            | 0.9                  | 5                      |

Note: \*Measuring point = Vtrip. See Table 2-29 on page 2-28 for a complete table of trip points.

### Timing Characteristics

### 1.5 V DC Core Voltage

Table 2-99 • 1.8 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V Applicable to Advanced I/O Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 0.97              | 6.38            | 0.18             | 1.01            | 0.66              | 6.51            | 5.93            | 2.33            | 1.56            | 10.10            | 9.53             | ns    |

| 4 mA           | Std.        | 0.97              | 5.35            | 0.18             | 1.01            | 0.66              | 5.46            | 5.04            | 2.67            | 2.38            | 9.05             | 8.64             | ns    |

| 6 mA           | Std.        | 0.97              | 4.62            | 0.18             | 1.01            | 0.66              | 4.71            | 4.44            | 2.90            | 2.79            | 8.31             | 8.04             | ns    |

| 8 mA           | Std.        | 0.97              | 4.37            | 0.18             | 1.01            | 0.66              | 4.46            | 4.31            | 2.95            | 2.89            | 8.05             | 7.90             | ns    |

| 12 mA          | Std.        | 0.97              | 4.32            | 0.18             | 1.01            | 0.66              | 4.37            | 4.32            | 3.03            | 3.30            | 7.97             | 7.92             | ns    |

| 16 mA          | Std.        | 0.97              | 4.32            | 0.18             | 1.01            | 0.66              | 4.37            | 4.32            | 3.03            | 3.30            | 7.97             | 7.92             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

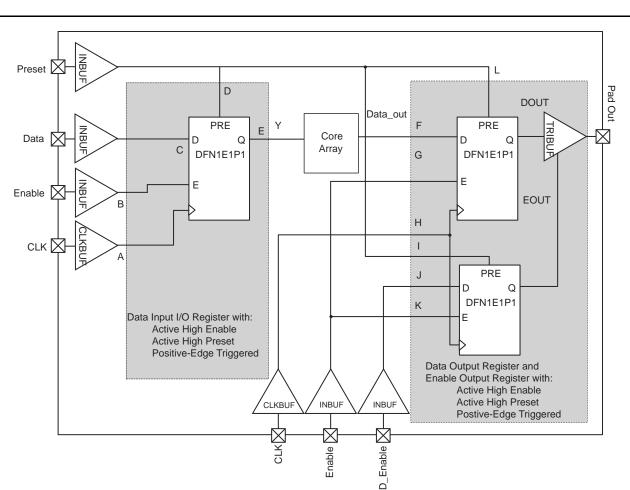

### I/O Register Specifications

# Fully Registered I/O Buffers with Synchronous Enable and Asynchronous Preset

Figure 2-16 • Timing Model of Registered I/O Buffers with Synchronous Enable and Asynchronous Preset

| Parameter Name        | Parameter Definition                                             | Measuring Nodes<br>(from, to)* |

|-----------------------|------------------------------------------------------------------|--------------------------------|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                           | H, DOUT                        |

| tosud                 | Data Setup Time for the Output Data Register                     | F, H                           |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                      | F, H                           |

| tosue                 | Enable Setup Time for the Output Data Register                   | G, H                           |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                    | G, H                           |

| t <sub>OPRE2Q</sub>   | Asynchronous Preset-to-Q of the Output Data Register             | L, DOUT                        |

| t <sub>OREMPRE</sub>  | Asynchronous Preset Removal Time for the Output Data Register    | L, H                           |

| t <sub>ORECPRE</sub>  | Asynchronous Preset Recovery Time for the Output Data Register   | L, H                           |

| t <sub>oeclkq</sub>   | Clock-to-Q of the Output Enable Register                         | H, EOUT                        |

| tOESUD                | Data Setup Time for the Output Enable Register                   | J, H                           |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                    | J, H                           |

| tOESUE                | Enable Setup Time for the Output Enable Register                 | К, Н                           |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                  | К, Н                           |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register           | I, EOUT                        |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register  | I, H                           |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register | I, H                           |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                            | A, E                           |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                      | C, A                           |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                       | C, A                           |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                    | B, A                           |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                     | B, A                           |

| t <sub>IPRE2Q</sub>   | Asynchronous Preset-to-Q of the Input Data Register              | D, E                           |

| t <sub>IREMPRE</sub>  | Asynchronous Preset Removal Time for the Input Data Register     | D, A                           |

| t <sub>IRECPRE</sub>  | Asynchronous Preset Recovery Time for the Input Data Register    | D, A                           |

### Table 2-155 • Parameter Definition and Measuring Nodes

Note: \*See Figure 2-16 on page 2-84 for more information.

### 1.2 V DC Core Voltage

### Table 2-165 • Input DDR Propagation Delays Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Parameter               | Description                                          | Std.   | Units |

|-------------------------|------------------------------------------------------|--------|-------|

| t <sub>DDRICLKQ1</sub>  | Clock-to-Out Out_QR for Input DDR                    | 0.76   | ns    |

| t <sub>DDRICLKQ2</sub>  | Clock-to-Out Out_QF for Input DDR                    | 0.94   | ns    |

| t <sub>DDRISUD1</sub>   | Data Setup for Input DDR (negedge)                   | 0.93   | ns    |

| t <sub>DDRISUD2</sub>   | Data Setup for Input DDR (posedge)                   | 0.84   | ns    |

| t <sub>DDRIHD1</sub>    | Data Hold for Input DDR (negedge)                    | 0.00   | ns    |

| t <sub>DDRIHD2</sub>    | Data Hold for Input DDR (posedge)                    | 0.00   | ns    |

| t <sub>DDRICLR2Q1</sub> | Asynchronous Clear-to-Out Out_QR for Input DDR       | 1.23   | ns    |

| t <sub>DDRICLR2Q2</sub> | Asynchronous Clear-to-Out Out_QF for Input DDR       | 1.42   | ns    |

| t <sub>DDRIREMCLR</sub> | Asynchronous Clear Removal Time for Input DDR        | 0.00   | ns    |

| t <sub>DDRIRECCLR</sub> | Asynchronous Clear Recovery Time for Input DDR       | 0.24   | ns    |

| t <sub>DDRIWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for Input DDR | 0.19   | ns    |

| t <sub>DDRICKMPWH</sub> | Clock Minimum Pulse Width High for Input DDR         | 0.31   | ns    |

| t <sub>DDRICKMPWL</sub> | Clock Minimum Pulse Width Low for Input DDR          | 0.28   | ns    |

| F <sub>DDRIMAX</sub>    | Maximum Frequency for Input DDR                      | 160.00 | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

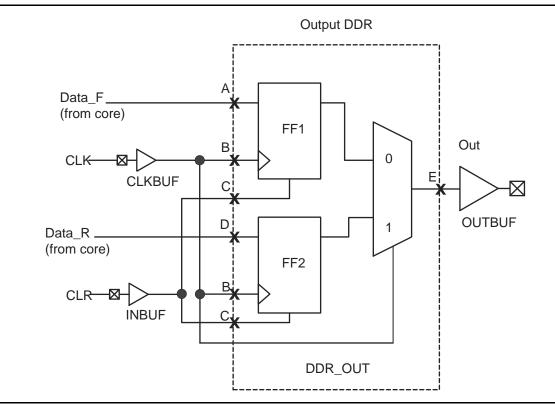

### **Output DDR Module**

### Figure 2-23 • Output DDR Timing Model

### Table 2-166 • Parameter Definitions

| Parameter Name          | Parameter Definition      | Measuring Nodes (from, to) |

|-------------------------|---------------------------|----------------------------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out              | B, E                       |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out | C, E                       |

| t <sub>DDROREMCLR</sub> | Clear Removal             | С, В                       |

| t <sub>DDRORECCLR</sub> | Clear Recovery            | С, В                       |

| tDDROSUD1               | Data Setup Data_F         | А, В                       |

| tDDROSUD2               | Data Setup Data_R         | D, B                       |

| t <sub>DDROHD1</sub>    | Data Hold Data_F          | A, B                       |

| t <sub>DDROHD2</sub>    | Data Hold Data_R          | D, B                       |

### 1.2 V DC Core Voltage

### Table 2-193 • RAM4K9

### Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Parameter             | Description                                                                                                          | Std.  | Units |

|-----------------------|----------------------------------------------------------------------------------------------------------------------|-------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                   | 1.53  | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                    | 0.29  | ns    |

| t <sub>ENS</sub>      | REN WEN setup time                                                                                                   | 1.50  | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                   | 0.29  | ns    |

| t <sub>BKS</sub>      | BLK setup time                                                                                                       | 3.05  | ns    |

| t <sub>BKH</sub>      | BLK hold time                                                                                                        | 0.29  | ns    |

| t <sub>DS</sub>       | Input data (DIN) setup time                                                                                          | 1.33  | ns    |

| t <sub>DH</sub>       | Input data (DIN) hold time                                                                                           | 0.66  | ns    |

| t <sub>CKQ1</sub>     | Clock High to new data valid on DOUT (output retained, WMODE = 0)                                                    | 6.61  | ns    |

|                       | Clock High to new data valid on DOUT (flow-through, WMODE = 1)                                                       | 5.72  | ns    |

| t <sub>CKQ2</sub>     | Clock High to new data valid on DOUT (pipelined)                                                                     | 3.38  | ns    |

| t <sub>C2CWWL</sub> 1 | Address collision clk-to-clk delay for reliable write after write on same address – Applicable to Closing Edge       | 0.30  | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address – Applicable to Opening Edge | 0.89  | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address – Applicable to Opening Edge | 1.01  | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to data out Low on DOUT (flow-through)                                                                     | 3.86  | ns    |

|                       | RESET Low to data out Low on DOUT (pipelined)                                                                        | 3.86  | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                        | 1.12  | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                       | 5.93  | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                            | 1.18  | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                     | 10.90 | ns    |

| F <sub>MAX</sub>      | Maximum frequency                                                                                                    | 92    | MHz   |

Notes:

1. For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Package Pin Assignments

| CS121      |                 |  |  |

|------------|-----------------|--|--|

| Pin Number | AGL060 Function |  |  |

| K10        | VPUMP           |  |  |

| K11        | GDB1/IO47RSB0   |  |  |

| L1         | VMV1            |  |  |

| L2         | GNDQ            |  |  |

| L3         | IO65RSB1        |  |  |

| L4         | IO63RSB1        |  |  |

| L5         | IO61RSB1        |  |  |

| L6         | IO58RSB1        |  |  |

| L7         | IO57RSB1        |  |  |

| L8         | IO55RSB1        |  |  |

| L9         | GNDQ            |  |  |

| L10        | GDA0/IO50RSB0   |  |  |

| L11        | VMV1            |  |  |

## Microsemi

Package Pin Assignments

| FG144      |                   |  |  |

|------------|-------------------|--|--|

| Pin Number | AGL600 Function   |  |  |

| K1         | GEB0/IO145NDB3    |  |  |

| K2         | GEA1/IO144PDB3    |  |  |

| K3         | GEA0/IO144NDB3    |  |  |

| K4         | GEA2/IO143RSB2    |  |  |

| K5         | IO119RSB2         |  |  |

| K6         | IO111RSB2         |  |  |

| K7         | GND               |  |  |

| K8         | IO94RSB2          |  |  |

| K9         | GDC2/IO91RSB2     |  |  |

| K10        | GND               |  |  |

| K11        | GDA0/IO88NDB1     |  |  |

| K12        | GDB0/IO87NDB1     |  |  |

| L1         | GND               |  |  |

| L2         | VMV3              |  |  |

| L3         | FF/GEB2/IO142RSB2 |  |  |

| L4         | IO136RSB2         |  |  |

| L5         | VCCIB2            |  |  |

| L6         | IO115RSB2         |  |  |

| L7         | IO103RSB2         |  |  |

| L8         | IO97RSB2          |  |  |

| L9         | TMS               |  |  |

| L10        | VJTAG             |  |  |

| L11        | VMV2              |  |  |

| L12        | TRST              |  |  |

| M1         | GNDQ              |  |  |

| M2         | GEC2/IO141RSB2    |  |  |

| M3         | IO138RSB2         |  |  |

| M4         | IO123RSB2         |  |  |

| M5         | IO126RSB2         |  |  |

| M6         | IO134RSB2         |  |  |

| M7         | IO108RSB2         |  |  |

| M8         | IO99RSB2          |  |  |

| M9         | TDI               |  |  |

| M10        | VCCIB2            |  |  |

| M11        | VPUMP             |  |  |

| M12        | GNDQ              |  |  |

## Microsemi

Package Pin Assignments

| FG256      |                   |  |  |

|------------|-------------------|--|--|

| Pin Number | AGL400 Function   |  |  |

| R5         | IO123RSB2         |  |  |

| R6         | IO118RSB2         |  |  |

| R7         | IO112RSB2         |  |  |

| R8         | IO106RSB2         |  |  |

| R9         | IO100RSB2         |  |  |

| R10        | IO96RSB2          |  |  |

| R11        | IO89RSB2          |  |  |

| R12        | IO85RSB2          |  |  |

| R13        | GDB2/IO81RSB2     |  |  |

| R14        | TDI               |  |  |

| R15        | NC                |  |  |

| R16        | TDO               |  |  |

| T1         | GND               |  |  |

| T2         | IO126RSB2         |  |  |

| Т3         | FF/GEB2/IO133RSB2 |  |  |

| T4         | IO124RSB2         |  |  |

| T5         | IO116RSB2         |  |  |

| T6         | IO113RSB2         |  |  |

| T7         | IO107RSB2         |  |  |

| T8         | IO105RSB2         |  |  |

| Т9         | IO102RSB2         |  |  |

| T10        | IO97RSB2          |  |  |

| T11        | IO92RSB2          |  |  |

| T12        | GDC2/IO82RSB2     |  |  |

| T13        | IO86RSB2          |  |  |

| T14        | GDA2/IO80RSB2     |  |  |

| T15        | TMS               |  |  |

| T16        | GND               |  |  |

|            | FG484           |  |  |  |

|------------|-----------------|--|--|--|

| Pin Number | AGL400 Function |  |  |  |

| N17        | IO74RSB1        |  |  |  |

| N18        | IO72NPB1        |  |  |  |

| N19        | IO70NDB1        |  |  |  |

| N20        | NC              |  |  |  |

| N21        | NC              |  |  |  |

| N22        | NC              |  |  |  |

| P1         | NC              |  |  |  |

| P2         | NC              |  |  |  |

| P3         | NC              |  |  |  |

| P4         | IO142NDB3       |  |  |  |

| P5         | IO141NPB3       |  |  |  |

| P6         | IO125RSB2       |  |  |  |

| P7         | IO139RSB3       |  |  |  |

| P8         | VCCIB3          |  |  |  |

| P9         | GND             |  |  |  |

| P10        | VCC             |  |  |  |

| P11        | VCC             |  |  |  |

| P12        | VCC             |  |  |  |

| P13        | VCC             |  |  |  |

| P14        | GND             |  |  |  |

| P15        | VCCIB1          |  |  |  |

| P16        | GDB0/IO78VPB1   |  |  |  |

| P17        | IO76VDB1        |  |  |  |

| P18        | IO76UDB1        |  |  |  |

| P19        | IO75PDB1        |  |  |  |

| P20        | NC              |  |  |  |

| P21        | NC              |  |  |  |

| P22        | NC              |  |  |  |

| R1         | NC              |  |  |  |

| R2         | NC              |  |  |  |

| R3         | VCC             |  |  |  |

| R4         | IO140PDB3       |  |  |  |

| R5         | IO130RSB2       |  |  |  |

| R6         | IO138NPB3       |  |  |  |

| R7         | GEC0/IO137NPB3  |  |  |  |

| R8         | VMV3            |  |  |  |

| FG484      |                 |  |  |

|------------|-----------------|--|--|

| Pin Number | AGL600 Function |  |  |

| G5         | IO171PDB3       |  |  |

| G6         | GAC2/IO172PDB3  |  |  |

| G7         | IO06RSB0        |  |  |

| G8         | GNDQ            |  |  |

| G9         | IO10RSB0        |  |  |

| G10        | IO19RSB0        |  |  |

| G11        | IO26RSB0        |  |  |

| G12        | IO30RSB0        |  |  |

| G13        | IO40RSB0        |  |  |

| G14        | IO45RSB0        |  |  |

| G15        | GNDQ            |  |  |

| G16        | IO50RSB0        |  |  |

| G17        | GBB2/IO61PPB1   |  |  |

| G18        | IO53RSB0        |  |  |

| G19        | IO63NDB1        |  |  |

| G20        | NC              |  |  |

| G21        | NC              |  |  |

| G22        | NC              |  |  |

| H1         | NC              |  |  |

| H2         | NC              |  |  |

| H3         | VCC             |  |  |

| H4         | IO166PDB3       |  |  |

| H5         | IO167NPB3       |  |  |

| H6         | IO172NDB3       |  |  |

| H7         | IO169NDB3       |  |  |

| H8         | VMV0            |  |  |

| H9         | VCCIB0          |  |  |

| H10        | VCCIB0          |  |  |

| H11        | IO25RSB0        |  |  |

| H12        | IO31RSB0        |  |  |

| H13        | VCCIB0          |  |  |

| H14        | VCCIB0          |  |  |

| H15        | VMV1            |  |  |

| H16        | GBC2/IO62PDB1   |  |  |

| H17        | IO67PPB1        |  |  |

| H18        | IO64PPB1        |  |  |

|            | FG484             |  |  |  |

|------------|-------------------|--|--|--|

| Pin Number | AGL1000 Function  |  |  |  |

| V15        | IO125RSB2         |  |  |  |

| V16        | GDB2/IO115RSB2    |  |  |  |

| V17        | TDI               |  |  |  |

| V18        | GNDQ              |  |  |  |

| V19        | TDO               |  |  |  |

| V20        | GND               |  |  |  |

| V21        | NC                |  |  |  |

| V22        | IO109NDB1         |  |  |  |

| W1         | NC                |  |  |  |

| W2         | IO191PDB3         |  |  |  |

| W3         | NC                |  |  |  |

| W4         | GND               |  |  |  |

| W5         | IO183RSB2         |  |  |  |

| W6         | FF/GEB2/IO186RSB2 |  |  |  |

| W7         | IO172RSB2         |  |  |  |

| W8         | IO170RSB2         |  |  |  |

| W9         | IO164RSB2         |  |  |  |

| W10        | IO158RSB2         |  |  |  |

| W11        | IO153RSB2         |  |  |  |

| W12        | IO142RSB2         |  |  |  |

| W13        | IO135RSB2         |  |  |  |

| W14        | IO130RSB2         |  |  |  |

| W15        | GDC2/IO116RSB2    |  |  |  |

| W16        | IO120RSB2         |  |  |  |

| W17        | GDA2/IO114RSB2    |  |  |  |

| W18        | TMS               |  |  |  |

| W19        | GND               |  |  |  |

| W20        | NC                |  |  |  |

| W21        | NC                |  |  |  |

| W22        | NC                |  |  |  |

| Y1         | VCCIB3            |  |  |  |

| Y2         | IO191NDB3         |  |  |  |

| Y3         | NC                |  |  |  |

| Y4         | IO182RSB2         |  |  |  |

| Y5         | GND               |  |  |  |

| Y6         | IO177RSB2         |  |  |  |

Datasheet Information

| Revision                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                            |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Revision 21<br>(continued)      | Pin description table for AGL125 CS121 was removed as it was incorrectly added to the datasheet in revision 19 (SAR 38217).                                                                                                                                                                                                                                                                                                                   | -                                               |

| Revision 20<br>(March 2012)     | Notes indicating that AGL015 is not recommended for new designs have been added.<br>The "Devices Not Recommended For New Designs" section is new (SAR 35015).                                                                                                                                                                                                                                                                                 | I to IV                                         |

|                                 | Notes indicating that device/package support is TBD for AGL250-QN132 and AGL060-FG144 have been reinserted (SAR 33689).                                                                                                                                                                                                                                                                                                                       | I to IV                                         |

|                                 | Values for the power data for PAC1, PAC2, PAC3, PAC4, PAC7, and PAC8 were revised in Table 2-19 • Different Components Contributing to Dynamic Power Consumption in IGLOO Devices and Table 2-21 • Different Components Contributing to Dynamic Power Consumption in IGLOO Devices to match the SmartPower tool in Libero software version 9.0 SP1 and Power Calculator spreadsheet v7a released on 08/10/2010 (SAR 33768).                   | 2-15                                            |

|                                 | The reference to guidelines for global spines and VersaTile rows, given in the "Global Clock Contribution—PCLOCK" section, was corrected to the "Spine Architecture" section of the Global Resources chapter in the <i>IGLOO FPGA Fabric User Guide</i> (SAR 34730).                                                                                                                                                                          |                                                 |

|                                 | Figure 2-4 • Input Buffer Timing Model and Delays (example) has been modified for the DIN waveform; the Rise and Fall time label has been changed to t <sub>DIN</sub> (SAR 37104).                                                                                                                                                                                                                                                            | 2-21                                            |

|                                 | <ul> <li>Added missing characteristics for 3.3 V LVCMOS, 3.3 V LVCMOS Wide range, 1.2 V LVCMOS, and 1.2 V LVCMOS Wide range to the following tables:</li> <li>Table 2-38, Table 2-39, Table 2-40, Table 2-42, Table 2-43, and Table 2-44 (SARs 33854 and 36891)</li> <li>Table 2-63, Table 2-64, and Table 2-65 (SAR 33854)</li> <li>Table 2-127, Table 2-128, Table 2-129, Table 2-137, Table 2-138, and Table 2-139 (SAR 36891).</li> </ul> | 2-40,<br>2-47 to<br>2-49,<br>2-74,<br>2-77, and |

|                                 | AC Loading figures in the "Single-Ended I/O Characteristics" section were updated to match Table 2-50 · AC Waveforms, Measuring Points, and Capacitive Loads (SAR 34878).                                                                                                                                                                                                                                                                     |                                                 |

|                                 | Added values for minimum pulse width and removed the FRMAX row from Table 2-173 through Table 2-188 in the "Global Tree Timing Characteristics" section. Use the software to determine the FRMAX for the device you are using (SAR 29271).                                                                                                                                                                                                    |                                                 |

| Revision 19<br>(September 2011) | CS121 was added to the product tables in the "IGLOO Low Power Flash FPGAs" section for AGL125 (SAR 22737). CS81 was added for AGL250 (SAR 22737).                                                                                                                                                                                                                                                                                             | I                                               |

|                                 | Notes indicating that device/package support is TBD for AGL250-QN132 and AGL060-FG144 have been removed (SAR 33689).                                                                                                                                                                                                                                                                                                                          | I to IV                                         |

|                                 | M1AGL400 was removed from the "I/Os Per Package1" table. This device was discontinued in April 2009 (SAR 32450).                                                                                                                                                                                                                                                                                                                              | II                                              |

|                                 | Dimensions for the QN48 package were added to Table 1 • IGLOO FPGAs Package Sizes Dimensions (SAR 30537).                                                                                                                                                                                                                                                                                                                                     | II                                              |

|                                 | The Y security option and Licensed DPA Logo were added to the "IGLOO Ordering<br>Information" section. The trademarked Licensed DPA Logo identifies that a product is<br>covered by a DPA counter-measures license from Cryptography Research (SAR<br>32151).                                                                                                                                                                                 |                                                 |

|                                 | The "In-System Programming (ISP) and Security" section and "Security" section were revised to clarify that although no existing security measures can give an absolute guarantee, Microsemi FPGAs implement the best security available in the industry (SAR 32865).                                                                                                                                                                          |                                                 |

IGLOO Low Power Flash FPGAs

| Revision                   | Changes                                                                                                                                                                                                                                                                                                                                                                                                                               | Page          |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Revision 19<br>(continued) | The following sentence was removed from the "Advanced Architecture" section:<br>"In addition, extensive on-chip programming circuitry allows for rapid, single-voltage<br>(3.3 V) programming of IGLOO devices via an IEEE 1532 JTAG interface" (SAR<br>28756).                                                                                                                                                                       | 1-3           |

|                            | The "Specifying I/O States During Programming" section is new (SAR 21281).                                                                                                                                                                                                                                                                                                                                                            | 1-8           |

|                            | Values for VCCPLL at 1.2 V –1.5 V DC core supply voltage were revised in Table 2-2 • Recommended Operating Conditions 1 (SAR 22356).                                                                                                                                                                                                                                                                                                  | 2-2           |

|                            | The value for VPUMP operation was changed from "0 to 3.45 V" to "0 to 3.6 V" (SAR 25220).                                                                                                                                                                                                                                                                                                                                             |               |

|                            | The value for VCCPLL 1.5 V DC core supply voltage was changed from "1.4 to 1.6 V" to "1.425 to 1.575 V" (SAR 26551).                                                                                                                                                                                                                                                                                                                  |               |

|                            | The notes in the table were renumbered in order of their appearance in the table (SAR 21869).                                                                                                                                                                                                                                                                                                                                         |               |

|                            | The temperature used in EQ 2 was revised from 110°C to 100°C for consistency with the limits given in Table 2-2 • Recommended Operating Conditions 1. The resulting maximum power allowed is thus 1.28 W. Formerly it was 1.71 W (SAR 26259).                                                                                                                                                                                         | 2-6           |

|                            | Values for CS196, CS281, and QN132 packages were added to Table 2-5 • Package Thermal Resistivities (SARs 26228, 32301).                                                                                                                                                                                                                                                                                                              | 2-6           |

|                            | Table 2-6 • Temperature and Voltage Derating Factors for Timing Delays (normalized to $TJ = 70^{\circ}C$ , VCC = 1.425 V) and Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays (normalized to $TJ = 70^{\circ}C$ , VCC = 1.14 V) were updated to remove the column for –20°C and shift the data over to correct columns (SAR 23041).                                                                            | 2-7           |

|                            | The tables in the "Quiescent Supply Current" section were updated with revised notes on IDD (SAR 24112). Table 2-8 • Power Supply State per Mode is new.                                                                                                                                                                                                                                                                              | 2-7           |

|                            | The formulas in the table notes for Table 2-41 • I/O Weak Pull-Up/Pull-Down Resistances were corrected (SAR 21348).                                                                                                                                                                                                                                                                                                                   | 2-37          |

|                            | The row for 110°C was removed from Table 2-45 • Duration of Short Circuit Event before Failure. The example in the associated paragraph was changed from 110°C to 100°C. Table 2-46 • I/O Input Rise Time, Fall Time, and Related I/O Reliability1 was revised to change 110° to 100°C. (SAR 26259).                                                                                                                                  | 2-40          |

|                            | The notes regarding drive strength in the "Summary of I/O Timing Characteristics –                                                                                                                                                                                                                                                                                                                                                    | 2-28,         |

|                            | Default I/O Software Settings" section, "3.3 V LVCMOS Wide Range" section and "1.2 V LVCMOS Wide Range" section tables were revised for clarification. They now state that the minimum drive strength for the default software configuration when run in wide range is $\pm 100 \ \mu$ A. The drive strength displayed in software is supported in normal range only. For a detailed I/V curve, refer to the IBIS models (SAR 25700). | 2-47,<br>2-77 |

|                            | The following sentence was deleted from the "2.5 V LVCMOS" section (SAR 24916): "It uses a 5 V-tolerant input buffer and push-pull output buffer."                                                                                                                                                                                                                                                                                    | 2-56          |

|                            | The values for $F_{DDRIMAX}$ and $F_{DDOMAX}$ were updated in the tables in the "Input DDR Module" section and "Output DDR Module" section (SAR 23919).                                                                                                                                                                                                                                                                               | 2-94,<br>2-97 |

|                            | The following notes were removed from Table 2-147 • Minimum and Maximum DC Input and Output Levels (SAR 29428): ±5%                                                                                                                                                                                                                                                                                                                   | 2-81          |

|                            | Differential input voltage = ±350 mV                                                                                                                                                                                                                                                                                                                                                                                                  |               |

|                            | Table 2-189 • IGLOO CCC/PLL Specification and Table 2-190 • IGLOO CCC/PLL Specification were updated. A note was added to both tables indicating that when the CCC/PLL core is generated by Mircosemi core generator software, not all delay values of the specified delay increments are available (SAR 25705).                                                                                                                      | 2-115         |