# E·XFL

Welcome to E-XFL.COM

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Active                                                                    |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | 6144                                                                      |

| Total RAM Bits                 | 36864                                                                     |

| Number of I/O                  | 143                                                                       |

| Number of Gates                | 250000                                                                    |

| Voltage - Supply               | 1.14V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                           |

| Package / Case                 | 196-TFBGA, CSBGA                                                          |

| Supplier Device Package        | 196-CSP (8x8)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/agl250v2-csg196 |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Product Grade | Programming Cycles | Program Retention<br>(biased/unbiased) | Maximum Storage<br>Temperature T <sub>STG</sub> (°C) <sup>2</sup> | Maximum Operating Junction<br>Temperature T <sub>J</sub> (°C) <sup>2</sup> |  |  |  |

|---------------|--------------------|----------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|

| Commercial    | 500                | 20 years                               | 110                                                               | 100                                                                        |  |  |  |

| Industrial    | 500                | 20 years                               | 110                                                               | 100                                                                        |  |  |  |

Table 2-3 • Flash Programming Limits – Retention, Storage, and Operating Temperature<sup>1</sup>

1. This is a stress rating only; functional operation at any condition other than those indicated is not implied.

2. These limits apply for program/data retention only. Refer to Table 2-1 on page 2-1 and Table 2-2 on page 2-2 for device operating conditions and absolute limits.

## Table 2-4 • Overshoot and Undershoot Limits<sup>1</sup>

| VCCI          | Average VCCI–GND Overshoot or Undershoot Duration<br>as a Percentage of Clock Cycle <sup>2</sup> | Maximum Overshoot/<br>Undershoot <sup>2</sup> |

|---------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2.7 V or less | 10%                                                                                              | 1.4 V                                         |

| F             | 5%                                                                                               | 1.49 V                                        |

| 3 V           | 10%                                                                                              | 1.1 V                                         |

| F             | 5%                                                                                               | 1.19 V                                        |

| 3.3 V         | 10%                                                                                              | 0.79 V                                        |

| F             | 5%                                                                                               | 0.88 V                                        |

| 3.6 V         | 10%                                                                                              | 0.45 V                                        |

| F             | 5%                                                                                               | 0.54 V                                        |

Notes:

1. Based on reliability requirements at junction temperature at 85°C.

2. The duration is allowed at one out of six clock cycles. If the overshoot/undershoot occurs at one out of two cycles, the maximum overshoot/undershoot has to be reduced by 0.15 V.

3. This table does not provide PCI overshoot/undershoot limits.

# I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)

Sophisticated power-up management circuitry is designed into every IGLOO device. These circuits ensure easy transition from the powered-off state to the powered-up state of the device. The many different supplies can power up in any sequence with minimized current spikes or surges. In addition, the I/O will be in a known state through the power-up sequence. The basic principle is shown in Figure 2-1 on page 2-4 and Figure 2-2 on page 2-5.

There are five regions to consider during power-up.

IGLOO I/Os are activated only if ALL of the following three conditions are met:

- 1. VCC and VCCI are above the minimum specified trip points (Figure 2-1 on page 2-4 and Figure 2-2 on page 2-5).

- 2. VCCI > VCC 0.75 V (typical)

- 3. Chip is in the operating mode.

## VCCI Trip Point:

Ramping up (V5 devices): 0.6 V < trip\_point\_up < 1.2 V Ramping down (V5 Devices): 0.5 V < trip\_point\_down < 1.1 V Ramping up (V2 devices): 0.75 V < trip\_point\_up < 1.05 V Ramping down (V2 devices): 0.65 V < trip\_point\_down < 0.95 V

## VCC Trip Point:

Ramping up (V5 devices): 0.6 V < trip\_point\_up < 1.1 V Ramping down (V5 devices): 0.5 V < trip\_point\_down < 1.0 V

# Guidelines

# **Toggle Rate Definition**

A toggle rate defines the frequency of a net or logic element relative to a clock. It is a percentage. If the toggle rate of a net is 100%, this means that this net switches at half the clock frequency. Below are some examples:

- The average toggle rate of a shift register is 100% because all flip-flop outputs toggle at half of the clock frequency.

- The average toggle rate of an 8-bit counter is 25%:

- Bit 0 (LSB) = 100%

- Bit 1 = 50%

- Bit 2 = 25%

- ...

- Bit 7 (MSB) = 0.78125%

- Average toggle rate = (100% + 50% + 25% + 12.5% + . . . + 0.78125%) / 8

# Enable Rate Definition

Output enable rate is the average percentage of time during which tristate outputs are enabled. When nontristate output buffers are used, the enable rate should be 100%.

### Table 2-23 • Toggle Rate Guidelines Recommended for Power Calculation

| Component  | Definition                       | Guideline |

|------------|----------------------------------|-----------|

| $\alpha_1$ | Toggle rate of VersaTile outputs | 10%       |

| $\alpha_2$ | I/O buffer toggle rate           | 10%       |

### Table 2-24 • Enable Rate Guidelines Recommended for Power Calculation

| Component      | Definition                           | Guideline |

|----------------|--------------------------------------|-----------|

| β <sub>1</sub> | I/O output buffer enable rate        | 100%      |

| β <sub>2</sub> | RAM enable rate for read operations  | 12.5%     |

| β <sub>3</sub> | RAM enable rate for write operations | 12.5%     |

# **User I/O Characteristics**

# **Timing Model**

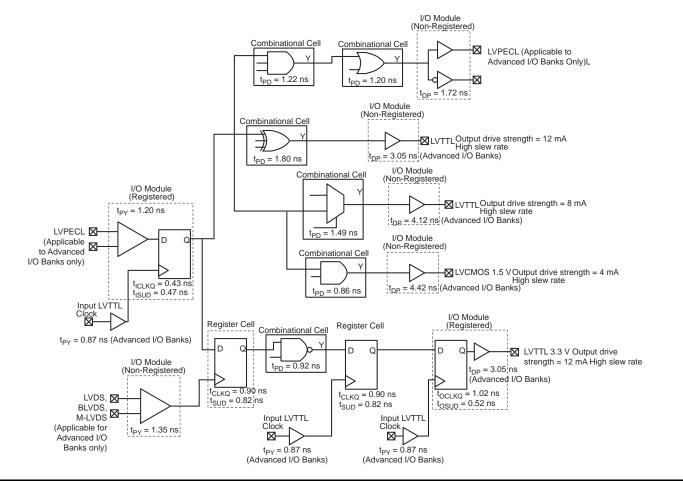

# Figure 2-3 • Timing Model

Operating Conditions: Std. Speed, Commercial Temperature Range ( $T_J = 70^{\circ}$ C), Worst-Case VCC = 1.425 V, for DC 1.5 V Core Voltage, Applicable to V2 and V5 Devices

# Table 2-26 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings Applicable to Standard Plus I/O Banks

|                                               |                   | Equivalent                                                      |              |           | VIL         | VIH              |                 | VOL         | VOH         | I <sub>OL</sub> | I <sub>ОН</sub> |

|-----------------------------------------------|-------------------|-----------------------------------------------------------------|--------------|-----------|-------------|------------------|-----------------|-------------|-------------|-----------------|-----------------|

| I/O<br>Standard                               | Drive<br>Strength | Software<br>Default<br>Drive<br>Strength<br>Option <sup>2</sup> | Slew<br>Rate | Min.<br>V | Max.<br>V   | Min.<br>V        | Max. V          | Max.<br>V   | Min.<br>V   | mA              | mA              |

| 3.3 V<br>LVTTL /<br>3.3 V<br>LVCMOS           | 12 mA             | 12 mA                                                           | High         | -0.3      | 0.8         | 2                | 3.6             | 0.4         | 2.4         | 12              | 12              |

| 3.3 V<br>LVCMOS<br>Wide<br>Range <sup>3</sup> | 100 µA            | 12 mA                                                           | High         | -0.3      | 0.8         | 2                | 3.6             | 0.2         | VDD-0.2     | 0.1             | 0.1             |

| 2.5 V<br>LVCMOS                               | 12 mA             | 12 mA                                                           | High         | -0.3      | 0.7         | 1.7              | 2.7             | 0.7         | 1.7         | 12              | 12              |

| 1.8 V<br>LVCMOS                               | 8 mA              | 8 mA                                                            | High         | -0.3      | 0.35 * VCCI | 0.65 * VCCI      | 0.65 * VCCI 1.9 |             | VCCI – 0.45 | 8               | 8               |

| 1.5 V<br>LVCMOS                               | 4 mA              | 4 mA                                                            | High         | -0.3      | 0.35 * VCCI | 0.65 * VCCI      | 1.575           | 0.25 * VCCI | 0.75 * VCCI | 4               | 4               |

| 1.2 V<br>LVCMOS <sup>4</sup>                  | 2 mA              | 2 mA                                                            | High         | -0.3      | 0.35 * VCCI | 0.65 * VCCI      | 1.26            | 0.25 * VCCI | 0.75 * VCCI | 2               | 2               |

| 1.2 V<br>LVCMOS<br>Wide<br>Range <sup>4</sup> | 100 µA            | 2 mA                                                            | High         | -0.3      | 0.3 * VCCI  | 0.7 * VCCI       | 1.575           | 0.1         | VCCI - 0.1  | 0.1             | 0.1             |

| 3.3 V PCI                                     |                   | •                                                               |              |           | Per F       | CI specification | ons             |             | •           |                 |                 |

| 3.3 V<br>PCI-X                                |                   |                                                                 |              |           | Per P(      | CI-X specificat  | ions            |             |             |                 |                 |

Notes:

1. Currents are measured at 85°C junction temperature.

The minimum drive strength for any LVCMOS 1.2 V or LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

3. All LVMCOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

4. Applicable to V2 Devices operating at VCCI  $\geq$  VCC.

5. All LVCMOS 1.2 V software macros support LVCMOS 1.2 V wide range as specified in the JESD8-12 specification.

Table 2-31 •

Summary of I/O Timing Characteristics—Software Default Settings, Std. Speed Grade, Commercial-Case

Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI (per standard)

Applicable to Advanced I/O Banks

| //O Standard                                  | Drive Strength     | Equivalent Software Default<br>Drive Strength Option <sup>1</sup> (mA) | Slew Rate | , Capacitive Load (pF) | External Resistor (Ω) | toour (ns) | t <sub>DP</sub> (ns) | t <sub>DIN</sub> (ns) | t <sub>PY</sub> (ns) | teour (ns) | t <sub>zL</sub> (ns) | t <sub>zH</sub> (ns) | t <sub>LZ</sub> (ns) | t <sub>Hz</sub> (ns) | tzLS (ns) | t <sub>zHS</sub> (ns) | Units |

|-----------------------------------------------|--------------------|------------------------------------------------------------------------|-----------|------------------------|-----------------------|------------|----------------------|-----------------------|----------------------|------------|----------------------|----------------------|----------------------|----------------------|-----------|-----------------------|-------|

| 3.3 V<br>LVTTL /<br>3.3 V<br>LVCMOS           | 12 mA              | 12                                                                     | High      | 5                      | Ι                     | 0.97       | 2.09                 | 0.18                  | 0.85                 | 0.66       | 2.14                 | 1.68                 | 2.67                 | 3.05                 | 5.73      | 5.27                  | ns    |

| 3.3 V<br>LVCMOS<br>Wide<br>Range <sup>2</sup> | 100 µA             | 12                                                                     | High      | 5                      | _                     | 0.97       | 2.93                 | 0.18                  | 1.19                 | 0.66       | 2.95                 | 2.27                 | 3.81                 | 4.30                 | 6.54      | 5.87                  | ns    |

| 2.5 V<br>LVCMOS                               | 12 mA              | 12                                                                     | High      | 5                      | -                     | 0.97       | 2.09                 | 0.18                  | 1.08                 | 0.66       | 2.14                 | 1.83                 | 2.73                 | 2.93                 | 5.73      | 5.43                  | ns    |

| 1.8 V<br>LVCMOS                               | 12 mA              | 12                                                                     | High      | 5                      | -                     | 0.97       | 2.24                 | 0.18                  | 1.01                 | 0.66       | 2.29                 | 2.00                 | 3.02                 | 3.40                 | 5.88      | 5.60                  | ns    |

| 1.5 V<br>LVCMOS                               | 12 mA              | 12                                                                     | High      | 5                      | -                     | 0.97       | 2.50                 | 0.18                  | 1.17                 | 0.66       | 2.56                 | 2.27                 | 3.21                 | 3.48                 | 6.15      | 5.86                  | ns    |

| 3.3 V PCI                                     | Per PCI<br>spec    | Ι                                                                      | High      | 10                     | 25 <sup>2</sup>       | 0.97       | 2.32                 | 0.18                  | 0.74                 | 0.66       | 2.37                 | 1.78                 | 2.67                 | 3.05                 | 5.96      | 5.38                  | ns    |

| 3.3 V<br>PCI-X                                | Per PCI-<br>X spec | Ι                                                                      | High      | 10                     | 25 <sup>2</sup>       | 0.97       | 2.32                 | 0.19                  | 0.70                 | 0.66       | 2.37                 | 1.78                 | 2.67                 | 3.05                 | 5.96      | 5.38                  | ns    |

| LVDS                                          | 24 mA              | -                                                                      | High      | Ι                      | -                     | 0.97       | 1.74                 | 0.19                  | 1.35                 | -          | -                    | -                    | -                    | -                    | -         | -                     | ns    |

| LVPECL                                        | 24 mA              | -                                                                      | High      | _                      | -                     | 0.97       | 1.68                 | 0.19                  | 1.16                 | _          | _                    | -                    | -                    | _                    | -         | -                     | ns    |

1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

3. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-12 on page 2-79 for connectivity. This resistor is not required during normal operation.

4. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Table 2-35 • Summary of I/O Timing Characteristics—Software Default Settings, Std. Speed Grade, Commercial-CaseConditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI (per standard)Applicable to Standard Plus I/O Banks

| I/O Standard                                  | Drive Strength       | Equivalent Software Default<br>Drive Strength Option <sup>1</sup> (mA) | Slew Rate | Capacitive Load (pF) | External Resistor ( $\Omega$ ) | t <sub>bour</sub> (ns) | t <sub>DP</sub> (ns) | t <sub>DIN</sub> (ns) | t <sub>PY</sub> (ns) | t <sub>EOUT</sub> (ns) | t <sub>ZL</sub> (ns) | tzt) (su) | t <sub>LZ</sub> (ns) | t <sub>HZ</sub> (ns) | t <sub>ZLS</sub> (ns) | t <sub>ZHS</sub> (ns) | Units |

|-----------------------------------------------|----------------------|------------------------------------------------------------------------|-----------|----------------------|--------------------------------|------------------------|----------------------|-----------------------|----------------------|------------------------|----------------------|-----------|----------------------|----------------------|-----------------------|-----------------------|-------|

| 3.3 V<br>LVTTL /<br>3.3 V<br>LVCMOS           | 12 mA                | 12                                                                     | High      | 5                    | _                              | 1.55                   | 2.31                 | 0.26                  | 0.97                 | 1.10                   | 2.34                 | 1.86      | 2.93                 | 3.64                 | 8.12                  | 7.65                  | ns    |

| 3.3 V<br>LVCMOS<br>Wide<br>Range <sup>2</sup> | 100 µA               | 12                                                                     | High      | 5                    | _                              | 1.55                   | 3.20                 | 0.26                  | 1.32                 | 1.10                   | 3.20                 | 2.52      | 4.01                 | 4.97                 | 8.99                  | 8.31                  | ns    |

| 2.5 V<br>LVCMOS                               | 12 mA                | 12                                                                     | High      | 5                    | —                              | 1.55                   | 2.29                 | 0.26                  | 1.19                 | 1.10                   | 2.32                 | 1.94      | 2.94                 | 3.52                 | 8.10                  | 7.73                  | ns    |

| 1.8 V<br>LVCMOS                               | 8 mA                 | 8                                                                      | High      | 5                    | _                              | 1.55                   | 2.43                 | 0.26                  | 1.11                 | 1.10                   | 2.47                 | 2.16      | 2.99                 | 3.39                 | 8.25                  | 7.94                  | ns    |

| 1.5 V<br>LVCMOS                               | 4 mA                 | 4                                                                      | High      | 5                    | _                              | 1.55                   | 2.68                 | 0.26                  | 1.27                 | 1.10                   | 2.72                 | 2.39      | 3.07                 | 3.37                 | 8.50                  | 8.18                  | ns    |

| 1.2 V<br>LVCMOS                               | 2 mA                 | 2                                                                      | High      | 5                    | _                              | 1.55                   | 3.22                 | 0.26                  | 1.59                 | 1.10                   | 3.11                 | 2.78      | 3.29                 | 3.48                 | 8.90                  | 8.57                  | ns    |

| 1.2 V<br>LVCMOS<br>Wide<br>Range <sup>3</sup> | 100 µA               | 2                                                                      | High      | 5                    | -                              | 1.55                   | 3.22                 | 0.26                  | 1.59                 | 1.10                   | 3.11                 | 2.78      | 3.29                 | 3.48                 | 8.90                  | 8.57                  | ns    |

| 3.3 V PCI                                     | Per PCI<br>spec      | -                                                                      | High      | 10                   | 25 <sup>2</sup>                | 1.55                   | 2.53                 | 0.26                  | 0.84                 | 1.10                   | 2.57                 | 1.98      | 2.93                 | 3.64                 | 8.35                  | 7.76                  | ns    |

| 3.3 V<br>PCI-X                                | Per<br>PCI-X<br>spec | -                                                                      | High      | 10                   | 25 <sup>2</sup>                | 1.55                   | 2.53                 | 0.25                  | 0.85                 | 1.10                   | 2.57                 | 1.98      | 2.93                 | 3.64                 | 8.35                  | 7.76                  | ns    |

The minimum drive strength for any LVCMOS 1.2 V or LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

3. All LVCMOS 1.2 V software macros support LVCMOS 1.2 V wide range as specified in the JESD8-12 specification

4. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-12 on page 2-79 for connectivity. This resistor is not required during normal operation.

5. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

# Table 2-44 • I/O Short Currents IOSH/IOSL Applicable to Standard I/O Banks

|                            | Drive Strength | IOSL (mA)*                   | IOSH (mA)*                   |

|----------------------------|----------------|------------------------------|------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 2 mA           | 25                           | 27                           |

|                            | 4 mA           | 25                           | 27                           |

|                            | 6 mA           | 51                           | 54                           |

|                            | 8 mA           | 51                           | 54                           |

| 3.3 V LVCMOS Wide Range    | 100 μA         | Same as regular 3.3 V LVCMOS | Same as regular 3.3 V LVCMOS |

| 2.5 V LVCMOS               | 2 mA           | 16                           | 18                           |

|                            | 4 mA           | 16                           | 18                           |

|                            | 6 mA           | 32                           | 37                           |

|                            | 8 mA           | 32                           | 37                           |

| 1.8 V LVCMOS               | 2 mA           | 9                            | 11                           |

|                            | 4 mA           | 17                           | 22                           |

| 1.5 V LVCMOS               | 2 mA           | 13                           | 16                           |

| 1.2 V LVCMOS               | 1 mA           | 20                           | 26                           |

| 1.2 V LVCMOS Wide Range    | 100 μA         | 20                           | 26                           |

*Note:*  $^{*}T_{J} = 100^{\circ}C$

The length of time an I/O can withstand  $I_{OSH}/I_{OSL}$  events depends on the junction temperature. The reliability data below is based on a 3.3 V, 12 mA I/O setting, which is the worst case for this type of analysis.

For example, at 100°C, the short current condition would have to be sustained for more than six months to cause a reliability concern. The I/O design does not contain any short circuit protection, but such protection would only be needed in extremely prolonged stress conditions.

Table 2-45 • Duration of Short Circuit Event before Failure

| Temperature | Time before Failure |

|-------------|---------------------|

| -40°C       | > 20 years          |

| –20°C       | > 20 years          |

| 0°C         | > 20 years          |

| 25°C        | > 20 years          |

| 70°C        | 5 years             |

| 85°C        | 2 years             |

| 100°C       | 6 months            |

Table 2-46 • I/O Input Rise Time, Fall Time, and Related I/O Reliability1

| Input Buffer                  | Input Rise/Fall Time (min.) | Input Rise/Fall Time (max.) | Reliability      |

|-------------------------------|-----------------------------|-----------------------------|------------------|

| LVTTL/LVCMOS                  | No requirement              | 10 ns *                     | 20 years (100°C) |

| LVDS/B-LVDS/M-LVDS/<br>LVPECL | No requirement              | 10 ns *                     | 10 years (100°C) |

Note: The maximum input rise/fall time is related to the noise induced into the input buffer trace. If the noise is low, then the rise time and fall time of input buffers can be increased beyond the maximum value. The longer the rise/fall times, the more susceptible the input signal is to the board noise. Microsemi recommends signal integrity evaluation/characterization of the system to ensure that there is no excessive noise coupling into input signals.

Table 2-75 • 3.3 V LVCMOS Wide Range Low Slew – Applies to 1.2 V DC Core Voltage<br/>Commercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.7<br/>Applicable to Standard Plus Banks

| Drive<br>Strength | Equivalent<br>Software<br>Default Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>dout</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>eout</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 100 µA            | 2 mA                                                                       | Std.           | 1.55              | 6.69            | 0.26             | 1.32            | 1.10              | 6.69            | 5.73            | 3.41            | 3.72            | 12.48            | 11.52            | ns    |

| 100 µA            | 4 mA                                                                       | Std.           | 1.55              | 6.69            | 0.26             | 1.32            | 1.10              | 6.69            | 5.73            | 3.41            | 3.72            | 12.48            | 11.52            | ns    |

| 100 µA            | 6 mA                                                                       | Std.           | 1.55              | 5.58            | 0.26             | 1.32            | 1.10              | 5.58            | 5.01            | 3.77            | 4.35            | 11.36            | 10.79            | ns    |

| 100 µA            | 8 mA                                                                       | Std.           | 1.55              | 5.58            | 0.26             | 1.32            | 1.10              | 5.58            | 5.01            | 3.77            | 4.35            | 11.36            | 10.79            | ns    |

| 100 µA            | 12 mA                                                                      | Std.           | 1.55              | 4.82            | 0.26             | 1.32            | 1.10              | 4.82            | 4.44            | 4.02            | 4.76            | 10.61            | 10.23            | ns    |

| 100 µA            | 16 mA                                                                      | Std.           | 1.55              | 4.82            | 0.26             | 1.32            | 1.10              | 4.82            | 4.44            | 4.02            | 4.76            | 10.61            | 10.23            | ns    |

1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ± 100 μA. Drive strengths displayed in software are supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

# Table 2-76 • 3.3 V LVCMOS Wide Range High Slew – Applies to 1.2 V DC Core Voltage<br/>Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.7<br/>Applicable to Standard Plus Banks

| Drive<br>Strength | Equivalent<br>Software<br>Default Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|-------------------|----------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 100 µA            | 2 mA                                                                       | Std.           | 1.55              | 4.10            | 0.26             | 1.32            | 1.10              | 4.10            | 3.30            | 3.40            | 3.92            | 9.89             | 9.09             | ns    |

| 100 µA            | 4 mA                                                                       | Std.           | 1.55              | 4.10            | 0.26             | 1.32            | 1.10              | 4.10            | 3.30            | 3.40            | 3.92            | 9.89             | 9.09             | ns    |

| 100 µA            | 6 mA                                                                       | Std.           | 1.55              | 3.51            | 0.26             | 1.32            | 1.10              | 3.51            | 2.79            | 3.76            | 4.56            | 9.30             | 8.57             | ns    |

| 100 µA            | 8 mA                                                                       | Std.           | 1.55              | 3.51            | 0.26             | 1.32            | 1.10              | 3.51            | 2.79            | 3.76            | 4.56            | 9.30             | 8.57             | ns    |

| 100 µA            | 12 mA                                                                      | Std.           | 1.55              | 3.20            | 0.26             | 1.32            | 1.10              | 3.20            | 2.52            | 4.01            | 4.97            | 8.99             | 8.31             | ns    |

| 100 µA            | 16 mA                                                                      | Std.           | 1.55              | 3.20            | 0.26             | 1.32            | 1.10              | 3.20            | 2.52            | 4.01            | 4.97            | 8.99             | 8.31             | ns    |

Notes:

1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ± 100 μA. Drive strengths displayed in software are supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

3. Software default selection highlighted in gray.

# 1.8 V LVCMOS

Low-voltage CMOS for 1.8 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 1.8 V applications. It uses a 1.8 V input buffer and a push-pull output buffer.

| 1.8 V<br>LVCMOS   | VIL       |             | VIH         |           | VOL       | VOH         | IOL | ЮН | IOSH                    | IOSL                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|-----------|-------------|-------------|-----------|-----------|-------------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 2   | 2  | 9                       | 11                      | 10               | 10               |

| 4 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 4   | 4  | 17                      | 22                      | 10               | 10               |

| 6 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 6   | 6  | 35                      | 44                      | 10               | 10               |

| 8 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 8   | 8  | 45                      | 51                      | 10               | 10               |

| 12 mA             | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 12  | 12 | 91                      | 74                      | 10               | 10               |

| 16 mA             | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 16  | 16 | 91                      | 74                      | 10               | 10               |

# Table 2-95 • Minimum and Maximum DC Input and Output Levels Applicable to Advanced I/O Banks

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

3. Currents are measured at 100°C junction temperature and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

# Table 2-96 • Minimum and Maximum DC Input and Output Levels Applicable to Standard Plus I/O Banks

| 1.8 V<br>LVCMOS   | VIL       |             | VIH         |           | VOL       | VOH         | IOL | ЮН | IOSH                    | IOSL                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|-----------|-------------|-------------|-----------|-----------|-------------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 2   | 2  | 9                       | 11                      | 10               | 10               |

| 4 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 4   | 4  | 17                      | 22                      | 10               | 10               |

| 6 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 6   | 6  | 35                      | 44                      | 10               | 10               |

| 8 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 8   | 8  | 35                      | 44                      | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

3. Currents are measured at 100°C junction temperature and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

## 1.2 V DC Core Voltage

### Table 2-145 • 3.3 V PCI/PCI-X

```

Commercial-Case Conditions: T_J = 70^{\circ}C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V

Applicable to Advanced I/O Banks

```

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 1.55              | 2.91            | 0.25             | 0.86            | 1.10              | 2.95            | 2.29            | 3.25            | 3.93            | 8.74             | 8.08             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

#### Table 2-146 • 3.3 V PCI/PCI-X

### Commercial-Case Conditions: $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V Applicable to Standard Plus I/O Banks

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 1.55              | 2.53            | 0.25             | 0.85            | 1.10              | 2.57            | 1.98            | 2.93            | 3.64            | 8.35             | 7.76             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

# **Differential I/O Characteristics**

## **Physical Implementation**

Configuration of the I/O modules as a differential pair is handled by Microsemi Designer software when the user instantiates a differential I/O macro in the design.

Differential I/Os can also be used in conjunction with the embedded Input Register (InReg), Output Register (OutReg), Enable Register (EnReg), and Double Data Rate (DDR). However, there is no support for bidirectional I/Os or tristates with the LVPECL standards.

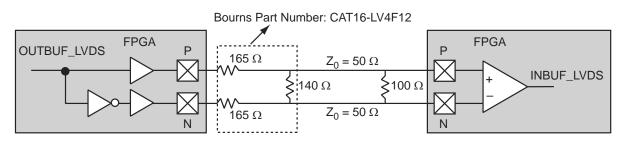

## LVDS

Low-Voltage Differential Signaling (ANSI/TIA/EIA-644) is a high-speed, differential I/O standard. It requires that one data bit be carried through two signal lines, so two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-13. The building blocks of the LVDS transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVPECL implementation because the output standard specifications are different.

Along with LVDS I/O, IGLOO also supports Bus LVDS structure and Multipoint LVDS (M-LVDS) configuration (up to 40 nodes).

Figure 2-13 • LVDS Circuit Diagram and Board-Level Implementation

# 1.2 V DC Core Voltage

# Table 2-165 • Input DDR Propagation Delays Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Parameter               | Description                                          | Std.   | Units |

|-------------------------|------------------------------------------------------|--------|-------|

| t <sub>DDRICLKQ1</sub>  | Clock-to-Out Out_QR for Input DDR                    | 0.76   | ns    |

| t <sub>DDRICLKQ2</sub>  | Clock-to-Out Out_QF for Input DDR                    | 0.94   | ns    |

| t <sub>DDRISUD1</sub>   | Data Setup for Input DDR (negedge)                   | 0.93   | ns    |

| t <sub>DDRISUD2</sub>   | Data Setup for Input DDR (posedge)                   | 0.84   | ns    |

| t <sub>DDRIHD1</sub>    | Data Hold for Input DDR (negedge)                    | 0.00   | ns    |

| t <sub>DDRIHD2</sub>    | Data Hold for Input DDR (posedge)                    | 0.00   | ns    |

| t <sub>DDRICLR2Q1</sub> | Asynchronous Clear-to-Out Out_QR for Input DDR       | 1.23   | ns    |

| t <sub>DDRICLR2Q2</sub> | Asynchronous Clear-to-Out Out_QF for Input DDR       | 1.42   | ns    |

| t <sub>DDRIREMCLR</sub> | Asynchronous Clear Removal Time for Input DDR        | 0.00   | ns    |

| t <sub>DDRIRECCLR</sub> | Asynchronous Clear Recovery Time for Input DDR       | 0.24   | ns    |

| t <sub>DDRIWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for Input DDR | 0.19   | ns    |

| t <sub>DDRICKMPWH</sub> | Clock Minimum Pulse Width High for Input DDR         | 0.31   | ns    |

| t <sub>DDRICKMPWL</sub> | Clock Minimum Pulse Width Low for Input DDR          | 0.28   | ns    |

| F <sub>DDRIMAX</sub>    | Maximum Frequency for Input DDR                      | 160.00 | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

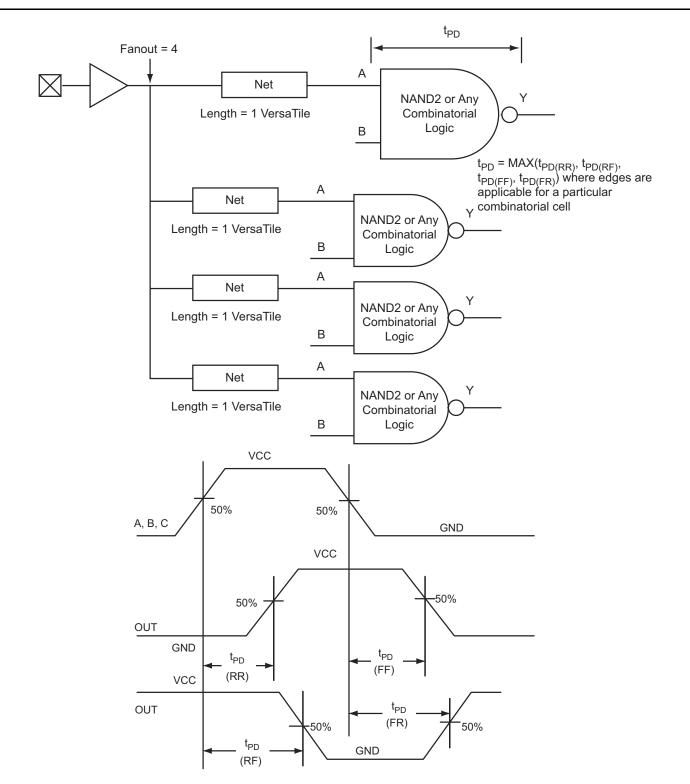

Figure 2-26 • Timing Model and Waveforms

# **Global Resource Characteristics**

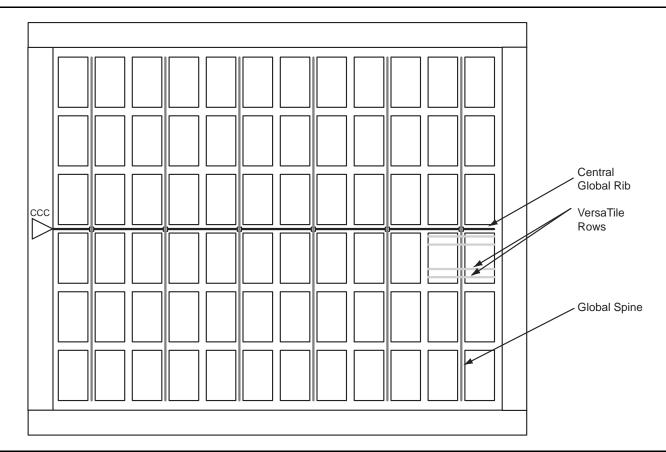

# AGL250 Clock Tree Topology

Clock delays are device-specific. Figure 2-29 is an example of a global tree used for clock routing. The global tree presented in Figure 2-29 is driven by a CCC located on the west side of the AGL250 device. It is used to drive all D-flip-flops in the device.

Figure 2-29 • Example of Global Tree Use in an AGL250 Device for Clock Routing

# Microsemi

Package Pin Assignments

|            | CS196           |            | CS196           |            | CS196           |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | AGL250 Function | Pin Number | AGL250 Function | Pin Number | AGL250 Function |

| A1         | GND             | C9         | IO30RSB0        | F3         | IO111PDB3       |

| A2         | GAA0/IO00RSB0   | C10        | IO33RSB0        | F4         | IO111NDB3       |

| A3         | GAC0/IO04RSB0   | C11        | VCCIB0          | F5         | IO113NPB3       |

| A4         | GAC1/IO05RSB0   | C12        | IO41NPB1        | F6         | IO06RSB0        |

| A5         | IO10RSB0        | C13        | GNDQ            | F7         | VCC             |

| A6         | IO13RSB0        | C14        | IO42NDB1        | F8         | VCC             |

| A7         | IO17RSB0        | D1         | IO116VDB3       | F9         | IO28RSB0        |

| A8         | IO19RSB0        | D2         | IO117VDB3       | F10        | IO54PDB1        |

| A9         | IO23RSB0        | D3         | GAA2/IO118UDB3  | F11        | IO54NDB1        |

| A10        | GBC0/IO35RSB0   | D4         | IO113PPB3       | F12        | IO47NDB1        |

| A11        | GBB0/IO37RSB0   | D5         | IO08RSB0        | F13        | IO47PDB1        |

| A12        | GBB1/IO38RSB0   | D6         | IO14RSB0        | F14        | IO45NDB1        |

| A13        | GBA1/IO40RSB0   | D7         | IO15RSB0        | G1         | GFB1/IO109PDB3  |

| A14        | GND             | D8         | IO18RSB0        | G2         | GFA0/IO108NDB3  |

| B1         | VCCIB3          | D9         | IO25RSB0        | G3         | GFA2/IO107PPB3  |

| B2         | VMV0            | D10        | IO32RSB0        | G4         | VCOMPLF         |

| B3         | GAA1/IO01RSB0   | D11        | IO44PPB1        | G5         | GFC0/IO110NDB3  |

| B4         | GAB1/IO03RSB0   | D12        | VMV1            | G6         | VCC             |

| B5         | GND             | D13        | IO43NDB1        | G7         | GND             |

| B6         | IO12RSB0        | D14        | GBC2/IO43PDB1   | G8         | GND             |

| B7         | IO16RSB0        | E1         | IO112PDB3       | G9         | VCC             |

| B8         | IO22RSB0        | E2         | GND             | G10        | GCC0/IO48NDB1   |

| B9         | IO24RSB0        | E3         | IO118VDB3       | G11        | GCB1/IO49PDB1   |

| B10        | GND             | E4         | VCCIB3          | G12        | GCA0/IO50NDB1   |

| B11        | GBC1/IO36RSB0   | E5         | IO114USB3       | G13        | IO53NDB1        |

| B12        | GBA0/IO39RSB0   | E6         | IO07RSB0        | G14        | GCC2/IO53PDB1   |

| B13        | GBA2/IO41PPB1   | E7         | IO09RSB0        | H1         | GFB0/IO109NDB3  |

| B14        | GBB2/IO42PDB1   | E8         | IO21RSB0        | H2         | GFA1/IO108PDB3  |

| C1         | GAC2/IO116UDB3  | E9         | IO31RSB0        | H3         | VCCPLF          |

| C2         | GAB2/IO117UDB3  | E10        | IO34RSB0        | H4         | GFB2/IO106PPB3  |

| C3         | GNDQ            | E11        | VCCIB1          | H5         | GFC1/IO110PDB3  |

| C4         | VCCIB0          | E12        | IO44NPB1        | H6         | VCC             |

| C5         | GAB0/IO02RSB0   | E13        | GND             | H7         | GND             |

| C6         | IO11RSB0        | E14        | IO45PDB1        | H8         | GND             |

| C7         | VCCIB0          | F1         | IO112NDB3       | H9         | VCC             |

| C8         | IO20RSB0        | F2         | IO107NPB3       | H10        | GCC1/IO48PDB1   |

Package Pin Assignments

|            | QN132           |

|------------|-----------------|

| Pin Number | AGL250 Function |

| C17        | IO74RSB2        |

| C18        | VCCIB2          |

| C19        | ТСК             |

| C20        | VMV2            |

| C21        | VPUMP           |

| C22        | VJTAG           |

| C23        | VCCIB1          |

| C24        | IO53NSB1        |

| C25        | IO51NPB1        |

| C26        | GCA1/IO50PPB1   |

| C27        | GCC0/IO48NDB1   |

| C28        | VCCIB1          |

| C29        | IO42NDB1        |

| C30        | GNDQ            |

| C31        | GBA1/IO40RSB0   |

| C32        | GBB0/IO37RSB0   |

| C33        | VCC             |

| C34        | IO24RSB0        |

| C35        | IO19RSB0        |

| C36        | IO16RSB0        |

| C37        | IO10RSB0        |

| C38        | VCCIB0          |

| C39        | GAB1/IO03RSB0   |

| C40        | VMV0            |

| D1         | GND             |

| D2         | GND             |

| D3         | GND             |

| D4         | GND             |

|            | FG484           |

|------------|-----------------|

| Pin Number | AGL400 Function |

| G5         | IO151UDB3       |

| G6         | GAC2/IO153UDB3  |

| G7         | IO06RSB0        |

| G8         | GNDQ            |

| G9         | IO10RSB0        |

| G10        | IO19RSB0        |

| G11        | IO26RSB0        |

| G12        | IO30RSB0        |

| G13        | IO40RSB0        |

| G14        | IO46RSB0        |

| G15        | GNDQ            |

| G16        | IO47RSB0        |

| G17        | GBB2/IO61PPB1   |

| G18        | IO53RSB0        |

| G19        | IO63NDB1        |

| G20        | NC              |

| G21        | NC              |

| G22        | NC              |

| H1         | NC              |

| H2         | NC              |

| H3         | VCC             |

| H4         | IO150PDB3       |

| H5         | IO08RSB0        |

| H6         | IO153VDB3       |

| H7         | IO152VDB3       |

| H8         | VMV0            |

| H9         | VCCIB0          |

| H10        | VCCIB0          |

| H11        | IO25RSB0        |

| H12        | IO31RSB0        |

| H13        | VCCIB0          |

| H14        | VCCIB0          |

| H15        | VMV1            |

| H16        | GBC2/IO62PDB1   |

| H17        | IO65RSB1        |

| H18        | IO52RSB0        |

|            | FG484            |

|------------|------------------|

| Pin Number | AGL1000 Function |

| E13        | IO51RSB0         |

| E14        | IO57RSB0         |

| E15        | GBC1/IO73RSB0    |

| E16        | GBB0/IO74RSB0    |

| E17        | IO71RSB0         |

| E18        | GBA2/IO78PDB1    |

| E19        | IO81PDB1         |

| E20        | GND              |

| E21        | NC               |

| E22        | IO84PDB1         |

| F1         | NC               |

| F2         | IO215PDB3        |

| F3         | IO215NDB3        |

| F4         | IO224NDB3        |

| F5         | IO225NDB3        |

| F6         | VMV3             |

| F7         | IO11RSB0         |

| F8         | GAC0/IO04RSB0    |

| F9         | GAC1/IO05RSB0    |

| F10        | IO25RSB0         |

| F11        | IO36RSB0         |

| F12        | IO42RSB0         |

| F13        | IO49RSB0         |

| F14        | IO56RSB0         |

| F15        | GBC0/IO72RSB0    |

| F16        | IO62RSB0         |

| F17        | VMV0             |

| F18        | IO78NDB1         |

| F19        | IO81NDB1         |

| F20        | IO82PPB1         |

| F21        | NC               |

| F22        | IO84NDB1         |

| G1         | IO214NDB3        |

| G2         | IO214PDB3        |

| G3         | NC               |

| G4         | IO222NDB3        |

|            | FG484             |

|------------|-------------------|

| Pin Number | AGL1000 Function  |

| V15        | IO125RSB2         |

| V16        | GDB2/IO115RSB2    |

| V17        | TDI               |

| V18        | GNDQ              |

| V19        | TDO               |

| V20        | GND               |

| V21        | NC                |

| V22        | IO109NDB1         |

| W1         | NC                |

| W2         | IO191PDB3         |

| W3         | NC                |

| W4         | GND               |

| W5         | IO183RSB2         |

| W6         | FF/GEB2/IO186RSB2 |

| W7         | IO172RSB2         |

| W8         | IO170RSB2         |

| W9         | IO164RSB2         |

| W10        | IO158RSB2         |

| W11        | IO153RSB2         |

| W12        | IO142RSB2         |

| W13        | IO135RSB2         |

| W14        | IO130RSB2         |

| W15        | GDC2/IO116RSB2    |

| W16        | IO120RSB2         |

| W17        | GDA2/IO114RSB2    |

| W18        | TMS               |

| W19        | GND               |

| W20        | NC                |

| W21        | NC                |

| W22        | NC                |

| Y1         | VCCIB3            |

| Y2         | IO191NDB3         |

| Y3         | NC                |

| Y4         | IO182RSB2         |

| Y5         | GND               |

| Y6         | IO177RSB2         |

Microsemi

IGLOO Low Power Flash FPGAs

| Revision / Version                                   | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page             |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Revision 3 (Feb 2008)<br>Product Brief rev. 2        | This document was updated to include AGL015 device information. QN68 is a<br>new package offered in the AGL015. The following sections were updated:<br>"Features and Benefits"<br>"IGLOO Ordering Information"<br>"Temperature Grade Offerings"<br>"IGLOO Devices" Product Family Table<br>Table 1 • IGLOO FPGAs Package Sizes Dimensions<br>"AGL015 and AGL030" note<br>The "Temperature Grade Offerings" table was updated to include M1AGL600.<br>In the "IGLOO Ordering Information" table, the QN package measurements were<br>updated to include both 0.4 mm and 0.5 mm. | N/A<br>IV<br>III |

|                                                      | In the "General Description" section, the number of I/Os was updated from 288 to 300.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-1              |

| Packaging v1.2                                       | The "QN68" section is new.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-25             |

| <b>Revision 2 (Jan 2008)</b><br>Packaging v1.1       | The "CS196" package and pin table was added for AGL125.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-10             |

| <b>Revision 1 (Jan 2008)</b><br>Product Brief rev. 1 | The "Low Power" section was updated to change the description of low power active FPGA operation to "from 12 $\mu$ W" from "from 25 $\mu$ W." The same update was made in the "General Description" section and the "Flash*Freeze Technology" section.                                                                                                                                                                                                                                                                                                                          | l, 1-1           |

| Revision 0 (Jan 2008)                                | This document was previously in datasheet Advance v0.7. As a result of moving to the handbook format, Actel has restarted the numbering.                                                                                                                                                                                                                                                                                                                                                                                                                                        | N/A              |

| Advance v0.7<br>(December 2007)                      | Table 1 • IGLOO Product Family, the "I/Os Per Package1" table, and the Temperature Grade Offerings table were updated to reflect the following: CS196 is now supported for AGL250; device/package support for QN132 is to be determined for AGL250; the CS281 package was added for AGL600 and AGL1000.                                                                                                                                                                                                                                                                         | i, ii, iv        |

|                                                      | Table 2 • IGLOO FPGAs Package Sizes Dimensions is new, and package sizes         were removed from the "I/Os Per Package1" table.                                                                                                                                                                                                                                                                                                                                                                                                                                               | ii               |

|                                                      | The "I/Os Per Package1"table was updated to reflect 77 instead of 79 single-<br>ended I/Os for the VG100 package for AGL030.                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ii               |

|                                                      | The "Timing Model" was updated to be consistent with the revised timing numbers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-20             |

|                                                      | In Table 2-27 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings, $T_J$ was changed to $T_A$ in notes 1 and 2.                                                                                                                                                                                                                                                                                                                                                                            | 2-26             |

|                                                      | All AC Loading figures for single-ended I/O standards were changed from Datapaths at 35 pF to 5 pF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | N/A              |

|                                                      | The "1.2 V LVCMOS (JESD8-12A)" section is new.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-74             |

|                                                      | This document was previously in datasheet Advance v0.7. As a result of moving to the handbook format, Actel has restarted the version numbers. The new version number is Advance v0.1.                                                                                                                                                                                                                                                                                                                                                                                          | N/A              |

|                                                      | Table 2-4 • IGLOO CCC/PLL Specification and Table 2-5 • IGLOO CCC/PLL         Specification were updated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-19,<br>2-20    |

| Revision / Version               | Changes                                                                                                                                                                                                                                                         | Page           |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Advance v0.4<br>(September 2007) | Cortex-M1 device information was added to Table 1 • IGLOO Product Family, the "I/Os Per Package1" table, "IGLOO Ordering Information", and Temperature Grade Offerings.                                                                                         | i, ii, iii, iv |

|                                  | The number of single-ended I/Os for the CS81 package for AGL030 was updated to 66 in the "I/Os Per Package1" table.                                                                                                                                             | ii             |

|                                  | The "Power Conservation Techniques" section was updated to recommend that unused I/O signals be left floating.                                                                                                                                                  | 2-51           |

| Advance v0.3<br>(August 2007)    | In Table 1 • IGLOO Product Family, the CS81 package was added for AGL030. The CS196 was replaced by the CS121 for AGL060. Table note 3 was moved to the specific packages to which it applies for AGL060: QN132 and FG144.                                      | i              |

|                                  | The CS81 and CS121 packages were added to the "I/Os Per Package1" table.<br>The number of single-ended I/Os was removed for the CS196 package in<br>AGL060. Table note 6 was moved to the specific packages to which it applies for<br>AGL060: QN132 and FG144. | ii             |

|                                  | The CS81 and CS121 packages were added to the Temperature Grade Offerings table. The temperature grade offerings were removed for the CS196 package in AGL060. Table note 3 was moved to the specific packages to which it applies for AGL060: QN132 and FG144. | iv             |

|                                  | The CS81 and CS121 packages were added to Table 2-31 • Flash*Freeze Pin Location in IGLOO Family Packages (device-independent).                                                                                                                                 | 2-61           |

| Advance v0.2                     | The words "ambient temperature" were added to the temperature range in the "IGLOO Ordering Information", Temperature Grade Offerings, and "Speed Grade and Temperature Grade Matrix" sections.                                                                  | iii, iv        |

|                                  | The $T_J$ parameter in Table 3-2 • Recommended Operating Conditions was changed to $T_A$ , ambient temperature, and table notes 4–6 were added.                                                                                                                 | 3-2            |