## E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                    |

|--------------------------------|---------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | 6144                                                                      |

| Total RAM Bits                 | 36864                                                                     |

| Number of I/O                  | 68                                                                        |

| Number of Gates                | 250000                                                                    |

| Voltage - Supply               | 1.14V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -40°C ~ 85°C (TA)                                                         |

| Package / Case                 | 100-TQFP                                                                  |

| Supplier Device Package        | 100-VQFP (14x14)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/agl250v2-vq100i |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Flash\*Freeze Technology

The IGLOO device has an ultra-low power static mode, called Flash\*Freeze mode, which retains all SRAM and register information and can still quickly return to normal operation. Flash\*Freeze technology enables the user to quickly (within 1 µs) enter and exit Flash\*Freeze mode by activating the Flash\*Freeze pin while all power supplies are kept at their original values. In addition, I/Os and global I/Os can still be driven and can be toggling without impact on power consumption, clocks can still be driven or can be toggling without impact on power consumption, and the device retains all core registers, SRAM information, and states. I/O states are tristated during Flash\*Freeze mode or can be set to a certain state using weak pull-up or pull-down I/O attribute configuration. No power is consumed by the I/O banks, clocks, JTAG pins, or PLL, and the device consumes as little as 5 µW in this mode.

Flash\*Freeze technology allows the user to switch to active mode on demand, thus simplifying the power management of the device.

The Flash\*Freeze pin (active low) can be routed internally to the core to allow the user's logic to decide when it is safe to transition to this mode. It is also possible to use the Flash\*Freeze pin as a regular I/O if Flash\*Freeze mode usage is not planned, which is advantageous because of the inherent low power static (as low as 12  $\mu$ W) and dynamic capabilities of the IGLOO device. Refer to Figure 1-3 for an illustration of entering/exiting Flash\*Freeze mode.

#### Figure 1-3 • IGLOO Flash\*Freeze Mode

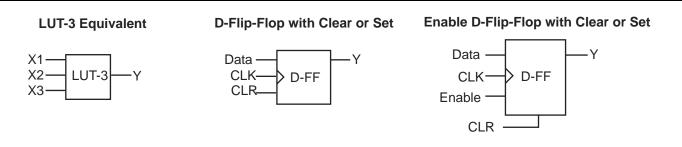

#### VersaTiles

The IGLOO core consists of VersaTiles, which have been enhanced beyond the ProASIC<sup>PLUS®</sup> core tiles. The IGLOO VersaTile supports the following:

- All 3-input logic functions—LUT-3 equivalent

- Latch with clear or set

- D-flip-flop with clear or set

- Enable D-flip-flop with clear or set

Refer to Figure 1-4 for VersaTile configurations.

## Table 2-20 • Different Components Contributing to the Static Power Consumption in IGLOO Devices For IGLOO V2 or V5 Devices, 1.5 V DC Core Supply Voltage

|           |                                                       |         | Device-Specific Static Power (mW) |            |              |             |             |           |        |  |  |  |  |  |

|-----------|-------------------------------------------------------|---------|-----------------------------------|------------|--------------|-------------|-------------|-----------|--------|--|--|--|--|--|

| Parameter | Definition                                            | AGL1000 | AGL600                            | AGL400     | AGL250       | AGL125      | AGL060      | AGL030    | AGL015 |  |  |  |  |  |

| PDC1      | Array static power in Active mode                     |         |                                   | See        | Table 2-12   | 2 on page 2 | 2-9.        |           |        |  |  |  |  |  |

| PDC2      | Array static power in Static (Idle) mode              |         |                                   | See        | Table 2-11   | on page 2   | 2-8.        |           |        |  |  |  |  |  |

| PDC3      | Array static power in<br>Flash*Freeze mode            |         |                                   | See        | e Table 2-9  | on page 2   | -7.         |           |        |  |  |  |  |  |

| PDC4      | Static PLL contribution                               |         |                                   |            | 1.8          | 34          |             |           |        |  |  |  |  |  |

| PDC5      | Bank quiescent power<br>(V <sub>CCI</sub> -dependent) |         |                                   | See        | Table 2-12   | 2 on page 2 | 2-9.        |           |        |  |  |  |  |  |

| PDC6      | I/O input pin static power (standard-dependent)       |         | See Table                         | 2-13 on pa | ige 2-10 thi | rough Table | e 2-15 on p | age 2-11. |        |  |  |  |  |  |

| PDC7      | I/O output pin static power (standard-dependent)      |         | See Table                         | 2-16 on pa | ige 2-11 thr | ough Table  | e 2-18 on p | age 2-12. |        |  |  |  |  |  |

Note: \*For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi power spreadsheet calculator or SmartPower tool in Libero SoC.

## **Power Calculation Methodology**

This section describes a simplified method to estimate power consumption of an application. For more accurate and detailed power estimations, use the SmartPower tool in Microsemi Libero SoC software.

The power calculation methodology described below uses the following variables:

- The number of PLLs as well as the number and the frequency of each output clock generated

- The number of combinatorial and sequential cells used in the design

- The internal clock frequencies

- The number and the standard of I/O pins used in the design

- The number of RAM blocks used in the design

- Toggle rates of I/O pins as well as VersaTiles—guidelines are provided in Table 2-23 on page 2-19.

- Enable rates of output buffers—guidelines are provided for typical applications in Table 2-24 on page 2-19.

- Read rate and write rate to the memory—guidelines are provided for typical applications in Table 2-24 on page 2-19. The calculation should be repeated for each clock domain defined in the design.

## Methodology

## Total Power Consumption—P<sub>TOTAL</sub>

$P_{TOTAL} = P_{STAT} + P_{DYN}$

$\mathsf{P}_{\mathsf{STAT}}$  is the total static power consumption.

P<sub>DYN</sub> is the total dynamic power consumption.

## Total Static Power Consumption—PSTAT

P<sub>STAT</sub> = (P<sub>DC1</sub> or P<sub>DC2</sub> or P<sub>DC3</sub>) + N<sub>BANKS</sub> \* P<sub>DC5</sub> + N<sub>INPUTS</sub> \* P<sub>DC6</sub> + N<sub>OUTPUTS</sub> \* P<sub>DC7</sub>

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

N<sub>OUTPUTS</sub> is the number of I/O output buffers used in the design.

N<sub>BANKS</sub> is the number of I/O banks powered in the design.

## Total Dynamic Power Consumption—PDYN

$P_{DYN} = P_{CLOCK} + P_{S-CELL} + P_{C-CELL} + P_{NET} + P_{INPUTS} + P_{OUTPUTS} + P_{MEMORY} + P_{PLL}$

## Global Clock Contribution—P<sub>CLOCK</sub>

$\mathsf{P}_{\mathsf{CLOCK}} = (\mathsf{P}_{\mathsf{AC1}} + \mathsf{N}_{\mathsf{SPINE}} * \mathsf{P}_{\mathsf{AC2}} + \mathsf{N}_{\mathsf{ROW}} * \mathsf{P}_{\mathsf{AC3}} + \mathsf{N}_{\mathsf{S}\text{-}\mathsf{CELL}} * \mathsf{P}_{\mathsf{AC4}}) * \mathsf{F}_{\mathsf{CLK}}$

N<sub>SPINE</sub> is the number of global spines used in the user design—guidelines are provided in the "Spine Architecture" section of the *IGLOO FPGA Fabric User Guide.*

N<sub>ROW</sub> is the number of VersaTile rows used in the design—guidelines are provided in the "Spine Architecture" section of the *IGLOO FPGA Fabric User Guide*.

$\mathsf{F}_{\mathsf{CLK}}$  is the global clock signal frequency.

N<sub>S-CELL</sub> is the number of VersaTiles used as sequential modules in the design.

P<sub>AC1</sub>, P<sub>AC2</sub>, P<sub>AC3</sub>, and P<sub>AC4</sub> are device-dependent.

## Sequential Cells Contribution—P<sub>S-CELL</sub>

$\mathsf{P}_{\text{S-CELL}} = \mathsf{N}_{\text{S-CELL}} * (\mathsf{P}_{\text{AC5}} + \alpha_1 / 2 * \mathsf{P}_{\text{AC6}}) * \mathsf{F}_{\text{CLK}}$

$N_{S-CELL}$  is the number of VersaTiles used as sequential modules in the design. When a multi-tile sequential cell is used, it should be accounted for as 1.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-23 on page 2-19.

$F_{CLK}$  is the global clock signal frequency.

## **User I/O Characteristics**

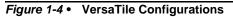

## **Timing Model**

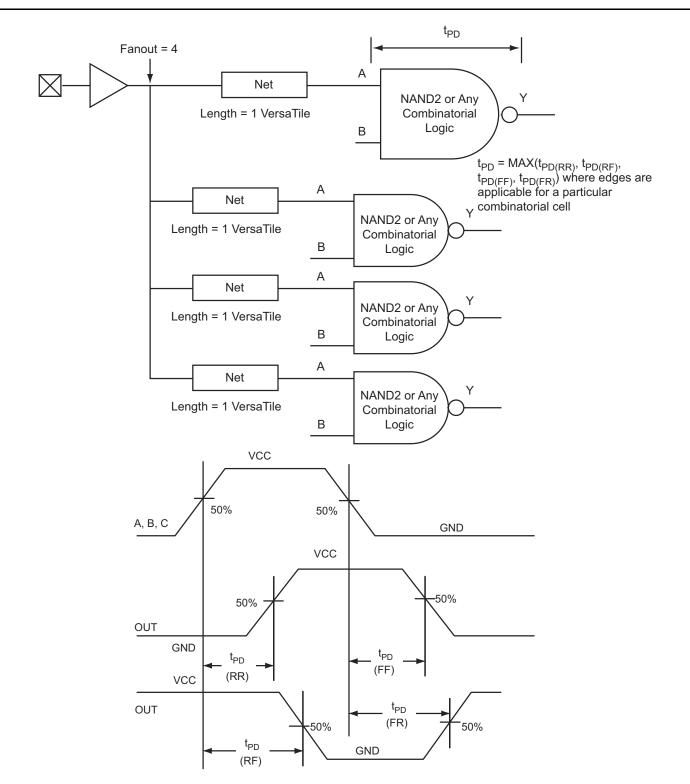

### Figure 2-3 • Timing Model

Operating Conditions: Std. Speed, Commercial Temperature Range ( $T_J = 70^{\circ}$ C), Worst-Case VCC = 1.425 V, for DC 1.5 V Core Voltage, Applicable to V2 and V5 Devices

## Summary of I/O Timing Characteristics – Default I/O Software Settings

## Table 2-29 • Summary of AC Measuring Points

| Standard                   | Measuring Trip Point (Vtrip) |

|----------------------------|------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 1.4 V                        |

| 3.3 V VCMOS Wide Range     | 1.4 V                        |

| 2.5 V LVCMOS               | 1.2 V                        |

| 1.8 V LVCMOS               | 0.90 V                       |

| 1.5 V LVCMOS               | 0.75 V                       |

| 1.2 V LVCMOS               | 0.60 V                       |

| 1.2 V LVCMOS Wide Range    | 0.60 V                       |

| 3.3 V PCI                  | 0.285 * VCCI (RR)            |

|                            | 0.615 * VCCI (FF)            |

| 3.3 V PCI-X                | 0.285 * VCCI (RR)            |

|                            | 0.615 * VCCI (FF)            |

### Table 2-30 • I/O AC Parameter Definitions

| Parameter         | Parameter Definition                                                        |

|-------------------|-----------------------------------------------------------------------------|

| t <sub>DP</sub>   | Data to Pad delay through the Output Buffer                                 |

| t <sub>PY</sub>   | Pad to Data delay through the Input Buffer                                  |

| t <sub>DOUT</sub> | Data to Output Buffer delay through the I/O interface                       |

| t <sub>EOUT</sub> | Enable to Output Buffer Tristate Control delay through the I/O interface    |

| t <sub>DIN</sub>  | Input Buffer to Data delay through the I/O interface                        |

| t <sub>HZ</sub>   | Enable to Pad delay through the Output Buffer—High to Z                     |

| t <sub>ZH</sub>   | Enable to Pad delay through the Output Buffer—Z to High                     |

| t <sub>LZ</sub>   | Enable to Pad delay through the Output Buffer—Low to Z                      |

| t <sub>ZL</sub>   | Enable to Pad delay through the Output Buffer—Z to Low                      |

| t <sub>ZHS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to High |

| t <sub>ZLS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to Low  |

## **Detailed I/O DC Characteristics**

## Table 2-37 • Input Capacitance

| Symbol          | Definition                         | Conditions           | Min. | Max. | Units |

|-----------------|------------------------------------|----------------------|------|------|-------|

| C <sub>IN</sub> | Input capacitance                  | VIN = 0, f = 1.0 MHz |      | 8    | pF    |

| CINCLK          | Input capacitance on the clock pin | VIN = 0, f = 1.0 MHz |      | 8    | pF    |

## Table 2-38 • I/O Output Buffer Maximum Resistances<sup>1</sup> Applicable to Advanced I/O Banks

| Standard                             | Drive Strength                 | R <sub>PULL-DOWN</sub><br>(Ω) <sup>2</sup> | R <sub>PULL-UP</sub><br>(Ω) <sup>3</sup> |

|--------------------------------------|--------------------------------|--------------------------------------------|------------------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS           | 2 mA                           | 100                                        | 300                                      |

|                                      | 4 mA                           | 100                                        | 300                                      |

|                                      | 6 mA                           | 50                                         | 150                                      |

|                                      | 8 mA                           | 50                                         | 150                                      |

|                                      | 12 mA                          | 25                                         | 75                                       |

|                                      | 16 mA                          | 17                                         | 50                                       |

|                                      | 24 mA                          | 11                                         | 33                                       |

| 3.3 V LVCMOS Wide Range              | 100 μA                         | Same as regular 3.3 V LVCMOS               | Same as regular 3.3 V LVCMOS             |

| 2.5 V LVCMOS                         | 2 mA                           | 100                                        | 200                                      |

|                                      | 4 mA                           | 100                                        | 200                                      |

|                                      | 6 mA                           | 50                                         | 100                                      |

|                                      | 8 mA                           | 50                                         | 100                                      |

|                                      | 12 mA                          | 25                                         | 50                                       |

|                                      | 16 mA                          | 20                                         | 40                                       |

| 1.5 V LVCMOS                         | 2 mA                           | 200                                        | 224                                      |

|                                      | 4 mA                           | 100                                        | 112                                      |

|                                      | 6 mA                           | 67                                         | 75                                       |

|                                      | 8 mA                           | 33                                         | 37                                       |

|                                      | 12 mA                          | 33                                         | 37                                       |

| 1.2 V LVCMOS <sup>4</sup>            | 2 mA                           | 158                                        | 164                                      |

| 1.2 V LVCMOS Wide Range <sup>4</sup> | 100 μA                         | Same as regular 1.2 V LVCMOS               | Same as regular 1.2 V LVCMOS             |

| 3.3 V PCI/PCI-X                      | Per PCI/PCI-X<br>specification | 25                                         | 75                                       |

Notes:

1. These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCCI, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located at http://www.microsemi.com/soc/download/ibis/default.aspx.

2. R<sub>(PULL-DOWN-MAX)</sub> = (VOLspec) / I<sub>OLspec</sub>

3. R<sub>(PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / I<sub>OHspec</sub>

4. Applicable to IGLOO V2 Devices operating at VCCI ≥ VCC

# Table 2-60 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew – Applies to 1.2 V DC Core VoltageCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 VApplicable to Standard Plus Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 1.55              | 2.89            | 0.26             | 0.97            | 1.10              | 2.93            | 2.38            | 2.53            | 2.96            | 8.72             | 8.17             | ns    |

| 4 mA           | Std.        | 1.55              | 2.89            | 0.26             | 0.97            | 1.10              | 2.93            | 2.38            | 2.53            | 2.96            | 8.72             | 8.17             | ns    |

| 6 mA           | Std.        | 1.55              | 2.50            | 0.26             | 0.97            | 1.10              | 2.54            | 2.04            | 2.77            | 3.37            | 8.33             | 7.82             | ns    |

| 8 mA           | Std.        | 1.55              | 2.50            | 0.26             | 0.97            | 1.10              | 2.54            | 2.04            | 2.77            | 3.37            | 8.33             | 7.82             | ns    |

| 12 mA          | Std.        | 1.55              | 2.31            | 0.26             | 0.97            | 1.10              | 2.34            | 1.86            | 2.93            | 3.64            | 8.12             | 7.65             | ns    |

| 16 mA          | Std.        | 1.55              | 2.31            | 0.26             | 0.97            | 1.10              | 2.34            | 1.86            | 2.93            | 3.64            | 8.12             | 7.65             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

#### Table 2-61 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V Applicable to Standard Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | Std.        | 1.55              | 4.39            | 0.26             | 0.94            | 1.10              | 4.46            | 3.91            | 2.17            | 2.44            | ns    |

| 4 mA           | Std.        | 1.55              | 4.39            | 0.26             | 0.94            | 1.10              | 4.46            | 3.91            | 2.17            | 2.44            | ns    |

| 6 mA           | Std.        | 1.55              | 3.72            | 0.26             | 0.94            | 1.10              | 3.78            | 3.43            | 2.40            | 2.85            | ns    |

| 8 mA           | Std.        | 1.55              | 3.72            | 0.26             | 0.94            | 1.10              | 3.78            | 3.43            | 2.40            | 2.85            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

## Table 2-62 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew – Applies to 1.2 V DC Core Voltage

### Commercial-Case Conditions: $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V Applicable to Standard Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | Std.        | 1.55              | 2.74            | 0.26             | 0.94            | 1.10              | 2.78            | 2.26            | 2.17            | 2.55            | ns    |

| 4 mA           | Std.        | 1.55              | 2.74            | 0.26             | 0.94            | 1.10              | 2.78            | 2.26            | 2.17            | 2.55            | ns    |

| 6 mA           | Std.        | 1.55              | 2.38            | 0.26             | 0.94            | 1.10              | 2.41            | 1.92            | 2.40            | 2.96            | ns    |

| 8 mA           | Std.        | 1.55              | 2.38            | 0.26             | 0.94            | 1.10              | 2.41            | 1.92            | 2.40            | 2.96            | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

## **Timing Characteristics**

#### Applies to 1.5 V DC Core Voltage

# Table 2-83 •2.5 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage<br/>Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V<br/>Applicable to Advanced I/O Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 0.97              | 4.96            | 0.18             | 1.08            | 0.66              | 5.06            | 4.59            | 2.26            | 2.00            | 8.66             | 8.19             | ns    |

| 4 mA           | Std.        | 0.97              | 4.96            | 0.18             | 1.08            | 0.66              | 5.06            | 4.59            | 2.26            | 2.00            | 8.66             | 8.19             | ns    |

| 6 mA           | Std.        | 0.97              | 4.15            | 0.18             | 1.08            | 0.66              | 4.24            | 3.94            | 2.54            | 2.51            | 7.83             | 7.53             | ns    |

| 8 mA           | Std.        | 0.97              | 4.15            | 0.18             | 1.08            | 0.66              | 4.24            | 3.94            | 2.54            | 2.51            | 7.83             | 7.53             | ns    |

| 12 mA          | Std.        | 0.97              | 3.57            | 0.18             | 1.08            | 0.66              | 3.65            | 3.47            | 2.73            | 2.84            | 7.24             | 7.06             | ns    |

| 16 mA          | Std.        | 0.97              | 3.39            | 0.18             | 1.08            | 0.66              | 3.46            | 3.36            | 2.78            | 2.92            | 7.06             | 6.95             | ns    |

| 24 mA          | Std.        | 0.97              | 3.38            | 0.18             | 1.08            | 0.66              | 3.38            | 3.38            | 2.83            | 3.25            | 6.98             | 6.98             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

#### Table 2-84 • 2.5 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V Applicable to Advanced I/O Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 0.97              | 2.77            | 0.18             | 1.08            | 0.66              | 2.83            | 2.60            | 2.26            | 2.08            | 6.42             | 6.19             | ns    |

| 4 mA           | Std.        | 0.97              | 2.77            | 0.18             | 1.08            | 0.66              | 2.83            | 2.60            | 2.26            | 2.08            | 6.42             | 6.19             | ns    |

| 6 mA           | Std.        | 0.97              | 2.34            | 0.18             | 1.08            | 0.66              | 2.39            | 2.08            | 2.54            | 2.60            | 5.99             | 5.68             | ns    |

| 8 mA           | Std.        | 0.97              | 2.34            | 0.18             | 1.08            | 0.66              | 2.39            | 2.08            | 2.54            | 2.60            | 5.99             | 5.68             | ns    |

| 12 mA          | Std.        | 0.97              | 2.09            | 0.18             | 1.08            | 0.66              | 2.14            | 1.83            | 2.73            | 2.93            | 5.73             | 5.43             | ns    |

| 16 mA          | Std.        | 0.97              | 2.05            | 0.18             | 1.08            | 0.66              | 2.09            | 1.78            | 2.78            | 3.02            | 5.69             | 5.38             | ns    |

| 24 mA          | Std.        | 0.97              | 2.06            | 0.18             | 1.08            | 0.66              | 2.10            | 1.72            | 2.83            | 3.35            | 5.70             | 5.32             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

# Table 2-85 •2.5 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage<br/>Commercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V<br/>Applicable to Standard Plus Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 0.97              | 4.42            | 0.18             | 1.08            | 0.66              | 4.51            | 4.10            | 1.96            | 1.85            | 8.10             | 7.69             | ns    |

| 4 mA           | Std.        | 0.97              | 4.42            | 0.18             | 1.08            | 0.66              | 4.51            | 4.10            | 1.96            | 1.85            | 8.10             | 7.69             | ns    |

| 6 mA           | Std.        | 0.97              | 3.62            | 0.18             | 1.08            | 0.66              | 3.70            | 3.52            | 2.21            | 2.32            | 7.29             | 7.11             | ns    |

| 8 mA           | Std.        | 0.97              | 3.62            | 0.18             | 1.08            | 0.66              | 3.70            | 3.52            | 2.21            | 2.32            | 7.29             | 7.11             | ns    |

| 12 mA          | Std.        | 0.97              | 3.09            | 0.18             | 1.08            | 0.66              | 3.15            | 3.09            | 2.39            | 2.61            | 6.74             | 6.68             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

## 1.2 V LVCMOS (JESD8-12A)

Low-Voltage CMOS for 1.2 V complies with the LVCMOS standard JESD8-12A for general purpose 1.2 V applications. It uses a 1.2 V input buffer and a push-pull output buffer. Furthermore, all LVCMOS 1.2 V software macros comply with LVCMOS 1.2 V wide range as specified in the JESD8-12A specification.

Table 2-127 • Minimum and Maximum DC Input and Output Levels Applicable to Advanced I/O Banks

| 1.2 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL         | VOH         | IOL | юн | IOSH                    | IOSL                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|-----------|-------------|-------------|-----------|-------------|-------------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.26      | 0.25 * VCCI | 0.75 * VCCI | 2   | 2  | 20                      | 26                      | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

## Table 2-128 • Minimum and Maximum DC Input and Output Levels Applicable to Standard Plus I/O Banks

| 1.2 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL         | VOH         | I <sub>OL</sub> | юн | IOSH                    | IOSL                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|-----------|-------------|-------------|-----------|-------------|-------------|-----------------|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA              | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.26      | 0.25 * VCCI | 0.75 * VCCI | 2               | 2  | 20                      | 26                      | 10               | 10               |

Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

#### Table 2-129 • Minimum and Maximum DC Input and Output Levels Applicable to Standard I/O Banks

| 1.2 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL         | VOH         | IOL | юн | IOSH                    | IOSL                    | IIL¹            | IIH <sup>2</sup> |

|-------------------|-----------|-------------|-------------|-----------|-------------|-------------|-----|----|-------------------------|-------------------------|-----------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 1 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 1   | 1  | 20                      | 26                      | 10              | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

3. Currents are measured at 100°C junction temperature and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

## **DDR Module Specifications**

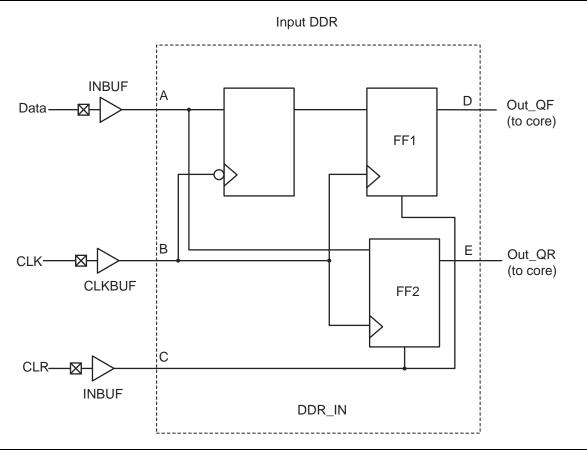

## Input DDR Module

## Figure 2-21 • Input DDR Timing Model

| Table 2-163 • F | Parameter | Definitions |

|-----------------|-----------|-------------|

|-----------------|-----------|-------------|

| Parameter Name          | Parameter Definition         | Measuring Nodes (from, to) |

|-------------------------|------------------------------|----------------------------|

| t <sub>DDRICLKQ1</sub>  | Clock-to-Out Out_QR          | B, D                       |

| tDDRICLKQ2              | Clock-to-Out Out_QF          | B, E                       |

| tDDRISUD                | Data Setup Time of DDR input | А, В                       |

|                         | Data Hold Time of DDR input  | A, B                       |

| t <sub>DDRICLR2Q1</sub> | Clear-to-Out Out_QR          | C, D                       |

| t <sub>DDRICLR2Q2</sub> | Clear-to-Out Out_QF          | C, E                       |

| t <sub>DDRIREMCLR</sub> | Clear Removal                | С, В                       |

| t <sub>DDRIRECCLR</sub> | Clear Recovery               | С, В                       |

Figure 2-26 • Timing Model and Waveforms

Package Pin Assignments

|            | CS121           |

|------------|-----------------|

| Pin Number | AGL060 Function |

| K10        | VPUMP           |

| K11        | GDB1/IO47RSB0   |

| L1         | VMV1            |

| L2         | GNDQ            |

| L3         | IO65RSB1        |

| L4         | IO63RSB1        |

| L5         | IO61RSB1        |

| L6         | IO58RSB1        |

| L7         | IO57RSB1        |

| L8         | IO55RSB1        |

| L9         | GNDQ            |

| L10        | GDA0/IO50RSB0   |

| L11        | VMV1            |

## Microsemi

Package Pin Assignments

|            | FG256           |            | FG256           |            | FG256           |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | AGL400 Function | Pin Number | AGL400 Function | Pin Number | AGL400 Function |

| A1         | GND             | C7         | IO20RSB0        | E13        | GBC2/IO62PDB1   |

| A2         | GAA0/IO00RSB0   | C8         | IO24RSB0        | E14        | IO65RSB1        |

| A3         | GAA1/IO01RSB0   | C9         | IO33RSB0        | E15        | IO52RSB0        |

| A4         | GAB0/IO02RSB0   | C10        | IO39RSB0        | E16        | IO66PDB1        |

| A5         | IO16RSB0        | C11        | IO45RSB0        | F1         | IO150NDB3       |

| A6         | IO17RSB0        | C12        | GBC0/IO54RSB0   | F2         | IO149NPB3       |

| A7         | IO22RSB0        | C13        | IO48RSB0        | F3         | IO09RSB0        |

| A8         | IO28RSB0        | C14        | VMV0            | F4         | IO152UDB3       |

| A9         | IO34RSB0        | C15        | IO61NPB1        | F5         | VCCIB3          |

| A10        | IO37RSB0        | C16        | IO63PDB1        | F6         | GND             |

| A11        | IO41RSB0        | D1         | IO151VDB3       | F7         | VCC             |

| A12        | IO43RSB0        | D2         | IO151UDB3       | F8         | VCC             |

| A13        | GBB1/IO57RSB0   | D3         | GAC2/IO153UDB3  | F9         | VCC             |

| A14        | GBA0/IO58RSB0   | D4         | IO06RSB0        | F10        | VCC             |

| A15        | GBA1/IO59RSB0   | D5         | GNDQ            | F11        | GND             |

| A16        | GND             | D6         | IO10RSB0        | F12        | VCCIB1          |

| B1         | GAB2/IO154UDB3  | D7         | IO19RSB0        | F13        | IO62NDB1        |

| B2         | GAA2/IO155UDB3  | D8         | IO26RSB0        | F14        | IO49RSB0        |

| B3         | IO12RSB0        | D9         | IO30RSB0        | F15        | IO64PPB1        |

| B4         | GAB1/IO03RSB0   | D10        | IO40RSB0        | F16        | IO66NDB1        |

| B5         | IO13RSB0        | D11        | IO46RSB0        | G1         | IO148NDB3       |

| B6         | IO14RSB0        | D12        | GNDQ            | G2         | IO148PDB3       |

| B7         | IO21RSB0        | D13        | IO47RSB0        | G3         | IO149PPB3       |

| B8         | IO27RSB0        | D14        | GBB2/IO61PPB1   | G4         | GFC1/IO147PPB3  |

| B9         | IO32RSB0        | D15        | IO53RSB0        | G5         | VCCIB3          |

| B10        | IO38RSB0        | D16        | IO63NDB1        | G6         | VCC             |

| B11        | IO42RSB0        | E1         | IO150PDB3       | G7         | GND             |

| B12        | GBC1/IO55RSB0   | E2         | IO08RSB0        | G8         | GND             |

| B13        | GBB0/IO56RSB0   | E3         | IO153VDB3       | G9         | GND             |

| B14        | IO44RSB0        | E4         | IO152VDB3       | G10        | GND             |

| B15        | GBA2/IO60PDB1   | E5         | VMV0            | G11        | VCC             |

| B16        | IO60NDB1        | E6         | VCCIB0          | G12        | VCCIB1          |

| C1         | IO154VDB3       | E7         | VCCIB0          | G13        | GCC1/IO67PPB1   |

| C2         | IO155VDB3       | E8         | IO25RSB0        | G14        | IO64NPB1        |

| C3         | IO11RSB0        | E9         | IO31RSB0        | G15        | IO73PDB1        |

| C4         | IO07RSB0        | E10        | VCCIB0          | G16        | IO73NDB1        |

| C5         | GAC0/IO04RSB0   | E11        | VCCIB0          | H1         | GFB0/IO146NPB3  |

| C6         | GAC1/IO05RSB0   | E12        | VMV1            | H2         | GFA0/IO145NDB3  |

| Pin NumberAGL400 FunctionAA15NCAA16NCAA17NCAA18NCAA19NCAA20NCAA21VCCIB1AA22GNDAB1GND | _ |

|--------------------------------------------------------------------------------------|---|

| AA16NCAA17NCAA18NCAA19NCAA20NCAA21VCCIB1AA22GNDAB1GND                                |   |

| AA17NCAA18NCAA19NCAA20NCAA21VCCIB1AA22GNDAB1GND                                      |   |

| AA18NCAA19NCAA20NCAA21VCCIB1AA22GNDAB1GND                                            |   |

| AA19NCAA20NCAA21VCCIB1AA22GNDAB1GND                                                  |   |

| AA20NCAA21VCCIB1AA22GNDAB1GND                                                        |   |

| AA21 VCCIB1<br>AA22 GND<br>AB1 GND                                                   |   |

| AA22 GND<br>AB1 GND                                                                  |   |

| AB1 GND                                                                              |   |

|                                                                                      |   |

| AB2 GND                                                                              |   |

|                                                                                      |   |

| AB3 VCCIB2                                                                           |   |

| AB4 NC                                                                               |   |

| AB5 NC                                                                               |   |

| AB6 IO121RSB2                                                                        |   |

| AB7 IO119RSB2                                                                        |   |

| AB8 IO114RSB2                                                                        |   |

| AB9 IO109RSB2                                                                        |   |

| AB10 NC                                                                              |   |

| AB11 NC                                                                              |   |

| AB12 IO104RSB2                                                                       |   |

| AB13 IO103RSB2                                                                       |   |

| AB14 NC                                                                              |   |

| AB15 NC                                                                              |   |

| AB16 IO91RSB2                                                                        |   |

| AB17 IO90RSB2                                                                        |   |

| AB18 NC                                                                              |   |

| AB19 NC                                                                              |   |

| AB20 VCCIB2                                                                          |   |

| AB21 GND                                                                             |   |

| AB22 GND                                                                             |   |

| B1 GND                                                                               |   |

| B2 VCCIB3                                                                            |   |

| B3 NC                                                                                |   |

| B4 NC                                                                                |   |

| B5 NC                                                                                |   |

| B6 NC                                                                                |   |

Package Pin Assignments

| FG484      |                 |  |  |  |

|------------|-----------------|--|--|--|

| Pin Number | AGL400 Function |  |  |  |

| H19        | IO66PDB1        |  |  |  |

| H20        | VCC             |  |  |  |

| H21        | NC              |  |  |  |

| H22        | NC              |  |  |  |

| J1         | NC              |  |  |  |

| J2         | NC              |  |  |  |

| J3         | NC              |  |  |  |

| J4         | IO150NDB3       |  |  |  |

| J5         | IO149NPB3       |  |  |  |

| J6         | IO09RSB0        |  |  |  |

| J7         | IO152UDB3       |  |  |  |

| J8         | VCCIB3          |  |  |  |

| J9         | GND             |  |  |  |

| J10        | VCC             |  |  |  |

| J11        | VCC             |  |  |  |

| J12        | VCC             |  |  |  |

| J13        | VCC             |  |  |  |

| J14        | GND             |  |  |  |

| J15        | VCCIB1          |  |  |  |

| J16        | IO62NDB1        |  |  |  |

| J17        | IO49RSB0        |  |  |  |

| J18        | IO64PPB1        |  |  |  |

| J19        | IO66NDB1        |  |  |  |

| J20        | NC              |  |  |  |

| J21        | NC              |  |  |  |

| J22        | NC              |  |  |  |

| K1         | NC              |  |  |  |

| K2         | NC              |  |  |  |

| K3         | NC              |  |  |  |

| K4         | IO148NDB3       |  |  |  |

| K5         | IO148PDB3       |  |  |  |

| K6         | IO149PPB3       |  |  |  |

| K7         | GFC1/IO147PPB3  |  |  |  |

| K8         | VCCIB3          |  |  |  |

| K9         | VCC             |  |  |  |

| K10        | GND             |  |  |  |

| FG484      |                 |  |  |  |

|------------|-----------------|--|--|--|

| Pin Number | AGL600 Function |  |  |  |

| H19        | IO66PDB1        |  |  |  |

| H20        | VCC             |  |  |  |

| H21        | NC              |  |  |  |

| H22        | NC              |  |  |  |

| J1         | NC              |  |  |  |

| J2         | NC              |  |  |  |

| J3         | NC              |  |  |  |

| J4         | IO166NDB3       |  |  |  |

| J5         | IO168NPB3       |  |  |  |

| J6         | IO167PPB3       |  |  |  |

| J7         | IO169PDB3       |  |  |  |

| J8         | VCCIB3          |  |  |  |

| J9         | GND             |  |  |  |

| J10        | VCC             |  |  |  |

| J11        | VCC             |  |  |  |

| J12        | VCC             |  |  |  |

| J13        | VCC             |  |  |  |

| J14        | GND             |  |  |  |

| J15        | VCCIB1          |  |  |  |

| J16        | IO62NDB1        |  |  |  |

| J17        | IO64NPB1        |  |  |  |

| J18        | IO65PPB1        |  |  |  |

| J19        | IO66NDB1        |  |  |  |

| J20        | NC              |  |  |  |

| J21        | IO68PDB1        |  |  |  |

| J22        | IO68NDB1        |  |  |  |

| K1         | IO157PDB3       |  |  |  |

| K2         | IO157NDB3       |  |  |  |

| K3         | NC              |  |  |  |

| K4         | IO165NDB3       |  |  |  |

| K5         | IO165PDB3       |  |  |  |

| K6         | IO168PPB3       |  |  |  |

| K7         | GFC1/IO164PPB3  |  |  |  |

| K8         | VCCIB3          |  |  |  |

| K9         | VCC             |  |  |  |

| K10        | GND             |  |  |  |

| FG484      |                  |  |  |  |

|------------|------------------|--|--|--|

| Pin Number | AGL1000 Function |  |  |  |

| G5         | IO222PDB3        |  |  |  |

| G6         | GAC2/IO223PDB3   |  |  |  |

| G7         | IO223NDB3        |  |  |  |

| G8         | GNDQ             |  |  |  |

| G9         | IO23RSB0         |  |  |  |

| G10        | IO29RSB0         |  |  |  |

| G11        | IO33RSB0         |  |  |  |

| G12        | IO46RSB0         |  |  |  |

| G13        | IO52RSB0         |  |  |  |

| G14        | IO60RSB0         |  |  |  |

| G15        | GNDQ             |  |  |  |

| G16        | IO80NDB1         |  |  |  |

| G17        | GBB2/IO79PDB1    |  |  |  |

| G18        | IO79NDB1         |  |  |  |

| G19        | IO82NPB1         |  |  |  |

| G20        | IO85PDB1         |  |  |  |

| G21        | IO85NDB1         |  |  |  |

| G22        | NC               |  |  |  |

| H1         | NC               |  |  |  |

| H2         | NC               |  |  |  |

| H3         | VCC              |  |  |  |

| H4         | IO217PDB3        |  |  |  |

| H5         | IO218PDB3        |  |  |  |

| H6         | IO221NDB3        |  |  |  |

| H7         | IO221PDB3        |  |  |  |

| H8         | VMV0             |  |  |  |

| H9         | VCCIB0           |  |  |  |

| H10        | VCCIB0           |  |  |  |

| H11        | IO38RSB0         |  |  |  |

| H12        | IO47RSB0         |  |  |  |

| H13        | VCCIB0           |  |  |  |

| H14        | VCCIB0           |  |  |  |

| H15        | VMV1             |  |  |  |

| H16        | GBC2/IO80PDB1    |  |  |  |

| H17        | IO83PPB1         |  |  |  |

| H18        | IO86PPB1         |  |  |  |

| FG484      |                  |  |  |  |

|------------|------------------|--|--|--|

| Pin Number | AGL1000 Function |  |  |  |

| K11        | GND              |  |  |  |

| K12        | GND              |  |  |  |

| K13        | GND              |  |  |  |

| K14        | VCC              |  |  |  |

| K15        | VCCIB1           |  |  |  |

| K16        | GCC1/IO91PPB1    |  |  |  |

| K17        | IO90NPB1         |  |  |  |

| K18        | IO88PDB1         |  |  |  |

| K19        | IO88NDB1         |  |  |  |

| K20        | IO94NPB1         |  |  |  |

| K21        | IO98NDB1         |  |  |  |

| K22        | IO98PDB1         |  |  |  |

| L1         | NC               |  |  |  |

| L2         | IO200PDB3        |  |  |  |

| L3         | IO210NPB3        |  |  |  |

| L4         | GFB0/IO208NPB3   |  |  |  |

| L5         | GFA0/IO207NDB3   |  |  |  |

| L6         | GFB1/IO208PPB3   |  |  |  |

| L7         | VCOMPLF          |  |  |  |

| L8         | GFC0/IO209NPB3   |  |  |  |

| L9         | VCC              |  |  |  |

| L10        | GND              |  |  |  |

| L11        | GND              |  |  |  |

| L12        | GND              |  |  |  |

| L13        | GND              |  |  |  |

| L14        | VCC              |  |  |  |

| L15        | GCC0/IO91NPB1    |  |  |  |

| L16        | GCB1/IO92PPB1    |  |  |  |

| L17        | GCA0/IO93NPB1    |  |  |  |

| L18        | IO96NPB1         |  |  |  |

| L19        | GCB0/IO92NPB1    |  |  |  |

| L20        | IO97PDB1         |  |  |  |

| L21        | IO97NDB1         |  |  |  |

| L22        | IO99NPB1         |  |  |  |

| M1         | NC               |  |  |  |

| M2         | IO200NDB3        |  |  |  |

| FG484      |                  |  |

|------------|------------------|--|

| Pin Number | AGL1000 Function |  |

| M3         | IO206NDB3        |  |

| M4         | GFA2/IO206PDB3   |  |

| M5         | GFA1/IO207PDB3   |  |

| M6         | VCCPLF           |  |

| M7         | IO205NDB3        |  |

| M8         | GFB2/IO205PDB3   |  |

| M9         | VCC              |  |

| M10        | GND              |  |

| M11        | GND              |  |

| M12        | GND              |  |

| M13        | GND              |  |

| M14        | VCC              |  |

| M15        | GCB2/IO95PPB1    |  |

| M16        | GCA1/IO93PPB1    |  |

| M17        | GCC2/IO96PPB1    |  |

| M18        | IO100PPB1        |  |

| M19        | GCA2/IO94PPB1    |  |

| M20        | IO101PPB1        |  |

| M21        | IO99PPB1         |  |

| M22        | NC               |  |

| N1         | IO201NDB3        |  |

| N2         | IO201PDB3        |  |

| N3         | NC               |  |

| N4         | GFC2/IO204PDB3   |  |

| N5         | IO204NDB3        |  |

| N6         | IO203NDB3        |  |

| N7         | IO203PDB3        |  |

| N8         | VCCIB3           |  |

| N9         | VCC              |  |

| N10        | GND              |  |

| N11        | GND              |  |

| N12        | GND              |  |

| N13        | GND              |  |

| N14        | VCC              |  |

| N15        | VCCIB1           |  |

| N16        | IO95NPB1         |  |

Microsemi

IGLOO Low Power Flash FPGAs

| Revision / Version                                   | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page             |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Revision 3 (Feb 2008)<br>Product Brief rev. 2        | This document was updated to include AGL015 device information. QN68 is a<br>new package offered in the AGL015. The following sections were updated:<br>"Features and Benefits"<br>"IGLOO Ordering Information"<br>"Temperature Grade Offerings"<br>"IGLOO Devices" Product Family Table<br>Table 1 • IGLOO FPGAs Package Sizes Dimensions<br>"AGL015 and AGL030" note<br>The "Temperature Grade Offerings" table was updated to include M1AGL600.<br>In the "IGLOO Ordering Information" table, the QN package measurements were<br>updated to include both 0.4 mm and 0.5 mm. | N/A<br>IV<br>III |

|                                                      | In the "General Description" section, the number of I/Os was updated from 288 to 300.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-1              |

| Packaging v1.2                                       | The "QN68" section is new.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-25             |

| <b>Revision 2 (Jan 2008)</b><br>Packaging v1.1       | The "CS196" package and pin table was added for AGL125.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-10             |

| <b>Revision 1 (Jan 2008)</b><br>Product Brief rev. 1 | The "Low Power" section was updated to change the description of low power active FPGA operation to "from 12 $\mu$ W" from "from 25 $\mu$ W." The same update was made in the "General Description" section and the "Flash*Freeze Technology" section.                                                                                                                                                                                                                                                                                                                          | l, 1-1           |

| Revision 0 (Jan 2008)                                | This document was previously in datasheet Advance v0.7. As a result of moving to the handbook format, Actel has restarted the numbering.                                                                                                                                                                                                                                                                                                                                                                                                                                        | N/A              |

| Advance v0.7<br>(December 2007)                      | Table 1 • IGLOO Product Family, the "I/Os Per Package1" table, and the Temperature Grade Offerings table were updated to reflect the following: CS196 is now supported for AGL250; device/package support for QN132 is to be determined for AGL250; the CS281 package was added for AGL600 and AGL1000.                                                                                                                                                                                                                                                                         | i, ii, iv        |

|                                                      | Table 2 • IGLOO FPGAs Package Sizes Dimensions is new, and package sizes were removed from the "I/Os Per Package1" table.                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ii               |

|                                                      | The "I/Os Per Package1"table was updated to reflect 77 instead of 79 single-<br>ended I/Os for the VG100 package for AGL030.                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ii               |

|                                                      | The "Timing Model" was updated to be consistent with the revised timing numbers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-20             |

|                                                      | In Table 2-27 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings, $T_J$ was changed to $T_A$ in notes 1 and 2.                                                                                                                                                                                                                                                                                                                                                                            | 2-26             |

|                                                      | All AC Loading figures for single-ended I/O standards were changed from Datapaths at 35 pF to 5 pF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | N/A              |

|                                                      | The "1.2 V LVCMOS (JESD8-12A)" section is new.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-74             |

|                                                      | This document was previously in datasheet Advance v0.7. As a result of moving to the handbook format, Actel has restarted the version numbers. The new version number is Advance v0.1.                                                                                                                                                                                                                                                                                                                                                                                          | N/A              |

|                                                      | Table 2-4 • IGLOO CCC/PLL Specification and Table 2-5 • IGLOO CCC/PLL         Specification were updated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-19,<br>2-20    |