Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Product Status                 | Active                                                                   |

|--------------------------------|--------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells | 13824                                                                    |

| Total RAM Bits                 | 110592                                                                   |

| Number of I/O                  | 177                                                                      |

| Number of Gates                | 600000                                                                   |

| Voltage - Supply               | 1.14V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                          |

| Package / Case                 | 256-LBGA                                                                 |

| Supplier Device Package        | 256-FPBGA (17x17)                                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/agl600v2-fg256 |

|                                |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

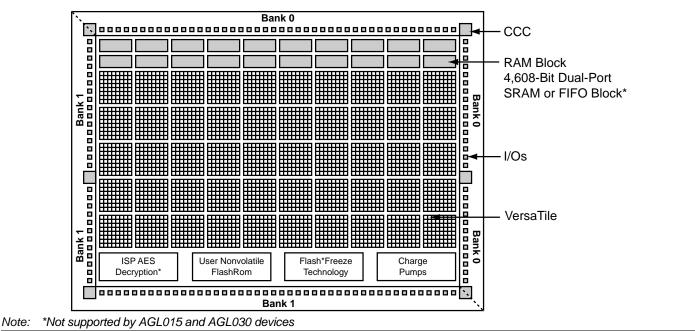

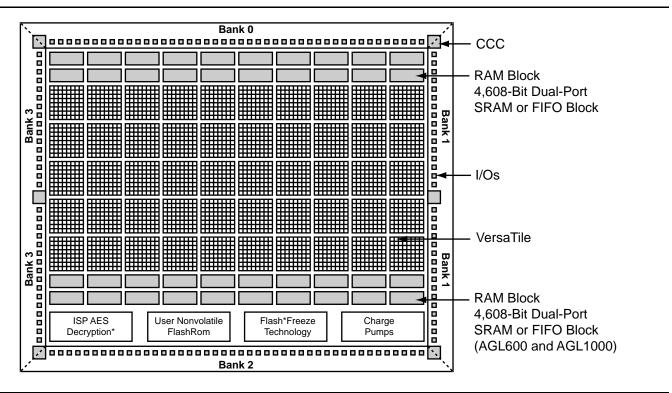

VersaTiles are connected with any of the four levels of routing hierarchy. Flash switches are distributed throughout the device to provide nonvolatile, reconfigurable interconnect programming. Maximum core utilization is possible for virtually any design.

Figure 1-1 • IGLOO Device Architecture Overview with Two I/O Banks (AGL015, AGL030, AGL060, and AGL125)

Figure 1-2 • IGLOO Device Architecture Overview with Four I/O Banks (AGL250, AGL600, AGL400, and AGL1000)

| Table 2-2 • | Recommended Ope | erating Conditions <sup>1</sup> |

|-------------|-----------------|---------------------------------|

|-------------|-----------------|---------------------------------|

| Symbol              | Para                                                         | ameter                                              | Commercial     | Industrial     | Units |

|---------------------|--------------------------------------------------------------|-----------------------------------------------------|----------------|----------------|-------|

| TJ                  | Junction Temperature <sup>2</sup>                            |                                                     | 0 to +85       | -40 to +100    | °C    |

| VCC <sup>3</sup>    | 1.5 V DC core supply voltage <sup>5</sup>                    |                                                     | 1.425 to 1.575 | 1.425 to 1.575 | V     |

|                     | 1.2 V–1.5 V wide range DC core supply voltage <sup>4,6</sup> |                                                     | 1.14 to 1.575  | 1.14 to 1.575  | V     |

| VJTAG               | JTAG DC voltage                                              |                                                     | 1.4 to 3.6     | 1.4 to 3.6     | V     |

| VPUMP               | Programming voltage                                          | Programming Mode                                    | 3.15 to 3.45   | 3.15 to 3.45   | V     |

|                     |                                                              | Operation <sup>7</sup>                              | 0 to 3.6       | 0 to 3.6       | V     |

| VCCPLL <sup>8</sup> | Analog power supply (PLL)                                    | 1.5 V DC core supply voltage <sup>5</sup>           | 1.425 to 1.575 | 1.425 to 1.575 | V     |

|                     |                                                              | 1.2 V - 1.5 V DC core supply voltage <sup>4,6</sup> | 1.14 to 1.575  | 1.14 to 1.575  | V     |

| VCCI and            | 1.2 V DC core supply voltage <sup>6</sup>                    |                                                     | 1.14 to 1.26   | 1.14 to 1.26   | V     |

| VMV <sup>9</sup>    | 1.2 V DC wide range DC supply voltage <sup>6</sup>           |                                                     | 1.14 to 1.575  | 1.14 to 1.575  | V     |

|                     | 1.5 V DC supply voltage                                      |                                                     | 1.425 to 1.575 | 1.425 to 1.575 | V     |

|                     | 1.8 V DC supply voltage                                      |                                                     | 1.7 to 1.9     | 1.7 to 1.9     | V     |

|                     | 2.5 V DC supply voltage                                      |                                                     | 2.3 to 2.7     | 2.3 to 2.7     | V     |

|                     | 3.0 V DC supply voltage <sup>10</sup>                        |                                                     | 2.7 to 3.6     | 2.7 to 3.6     | V     |

|                     | 3.3 V DC supply voltage                                      |                                                     | 3.0 to 3.6     | 3.0 to 3.6     | V     |

|                     | LVDS differential I/O                                        |                                                     | 2.375 to 2.625 | 2.375 to 2.625 | V     |

|                     | LVPECL differential I/O                                      |                                                     | 3.0 to 3.6     | 3.0 to 3.6     | V     |

Notes:

1. All parameters representing voltages are measured with respect to GND unless otherwise specified.

- 2. Software Default Junction Temperature Range in the Libero SoC software is set to 0°C to +70°C for commercial, and -40°C to +85°C for industrial. To ensure targeted reliability standards are met across the full range of junction temperatures, Microsemi recommends using custom settings for temperature range before running timing and power analysis tools. For more information on custom settings, refer to the New Project Dialog Box in the Libero SoC Online Help.

- 3. The ranges given here are for power supplies only. The recommended input voltage ranges specific to each I/O standard are given in Table 2-25 on page 2-24. VCCI should be at the same voltage within a given I/O bank.

- 4. All IGLOO devices (V5 and V2) must be programmed with the VCC core voltage at 1.5 V. Applications using the V2 devices powered by 1.2 V supply must switch the core supply to 1.5 V for in-system programming.

- 5. For  $IGLOO^{\mathbb{R}}$  V5 devices

- 6. For IGLOO V2 devices only, operating at VCCI  $\geq$  VCC.

- 7. VPUMP can be left floating during operation (not programming mode).

- 8. VCCPLL pins should be tied to VCC pins. See the "Pin Descriptions" chapter of the IGLOO FPGA Fabric User Guide for further information.

- 9. VMV and VCCI must be at the same voltage within a given I/O bank. VMV pins must be connected to the corresponding VCCI pins. See the "VMVx I/O Supply Voltage (quiet)" on page 3-1 for further information.

- 10. 3.3 V wide range is compliant to the JESD-8B specification and supports 3.0 V VCCI operation.

# **Power Consumption of Various Internal Resources**

Table 2-19 • Different Components Contributing to Dynamic Power Consumption in IGLOO Devices

For IGLOO V2 or V5 Devices, 1.5 V DC Core Supply Voltage

|           |                                                                      |         |           | Devic      | e Specific<br>(μW/l |             | ower        |           |        |

|-----------|----------------------------------------------------------------------|---------|-----------|------------|---------------------|-------------|-------------|-----------|--------|

| Parameter | Definition                                                           | AGL1000 | AGL600    | AGL400     | AGL250              | AGL125      | AGL060      | AGL030    | AGL015 |

| PAC1      | Clock contribution of a<br>Global Rib                                | 7.778   | 6.221     | 6.082      | 4.460               | 4.446       | 2.736       | 0.000     | 0.000  |

| PAC2      | Clock contribution of a<br>Global Spine                              | 4.334   | 3.512     | 2.759      | 2.718               | 1.753       | 1.971       | 3.483     | 3.483  |

| PAC3      | Clock contribution of a<br>VersaTile row                             | 1.379   | 1.445     | 1.377      | 1.483               | 1.467       | 1.503       | 1.472     | 1.472  |

| PAC4      | Clock contribution of a<br>VersaTile used as a<br>sequential module  | 0.151   | 0.149     | 0.151      | 0.149               | 0.149       | 0.151       | 0.146     | 0.146  |

| PAC5      | First contribution of a<br>VersaTile used as a<br>sequential module  | 0.057   |           |            |                     |             |             |           |        |

| PAC6      | Second contribution of a<br>VersaTile used as a<br>sequential module | 0.207   |           |            |                     |             |             |           |        |

| PAC7      | Contribution of a VersaTile<br>used as a combinatorial<br>module     | 0.276   | 0.262     | 0.279      | 0.277               | 0.280       | 0.300       | 0.281     | 0.273  |

| PAC8      | Average contribution of a routing net                                | 1.161   | 1.147     | 1.193      | 1.273               | 1.076       | 1.088       | 1.134     | 1.153  |

| PAC9      | Contribution of an I/O input pin (standard-dependent)                |         | See Table | 2-13 on pa | age 2-10 th         | rough Table | e 2-15 on p | age 2-11. |        |

| PAC10     | Contribution of an I/O output pin (standard-dependent)               |         | See Table | 2-16 on pa | age 2-11 th         | rough Table | e 2-18 on p | age 2-12. |        |

| PAC11     | Average contribution of a<br>RAM block during a read<br>operation    |         |           |            | 25.                 | 00          |             |           |        |

| PAC12     | Average contribution of a<br>RAM block during a write<br>operation   |         |           |            | 30.                 | 00          |             |           |        |

| PAC13     | Dynamic PLL contribution                                             |         |           |            | 2.7                 | 70          |             |           |        |

Note: For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi power spreadsheet calculator or SmartPower tool in Libero SoC.

#### Table 2-27 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings Applicable to Standard I/O Banks

|                                                 |                   | Equivalent                                                      |              |           | VIL         | V <sub>IH</sub> |           | VOL         | V <sub>OH</sub> | I <sub>OL</sub> 1 | I <sub>OH</sub> 1 |

|-------------------------------------------------|-------------------|-----------------------------------------------------------------|--------------|-----------|-------------|-----------------|-----------|-------------|-----------------|-------------------|-------------------|

| I/O<br>Standard                                 | Drive<br>Strength | Software<br>Default<br>Drive<br>Strength<br>Option <sup>2</sup> | Slew<br>Rate | Min.<br>V | Max.<br>V   | Min.<br>V       | Max.<br>V | Max.<br>V   | Min.<br>V       | mA                | mA                |

| 3.3 V<br>LVTTL /<br>3.3 V<br>LVCMOS             | 8 mA              | 8 mA                                                            | High         | -0.3      | 0.8         | 2               | 3.6       | 0.4         | 2.4             | 8                 | 8                 |

| 3.3 V<br>LVCMOS<br>Wide<br>Range <sup>3</sup>   | 100 µA            | 8 mA                                                            | High         | -0.3      | 0.8         | 2               | 3.6       | 0.2         | VDD-0.2         | 0.1               | 0.1               |

| 2.5 V<br>LVCMOS                                 | 8 mA              | 8 mA                                                            | High         | -0.3      | 0.7         | 1.7             | 3.6       | 0.7         | 1.7             | 8                 | 8                 |

| 1.8 V<br>LVCMOS                                 | 4 mA              | 4 mA                                                            | High         | -0.3      | 0.35 * VCCI | 0.65 * VCCI     | 3.6       | 0.45        | VCCI – 0.45     | 4                 | 4                 |

| 1.5 V<br>LVCMOS                                 | 2 mA              | 2 mA                                                            | High         | -0.3      | 0.35 * VCCI | 0.65 * VCCI     | 3.6       | 0.25 * VCCI | 0.75 * VCCI     | 2                 | 2                 |

| 1.2 V<br>LVCMOS <sup>4</sup>                    | 1 mA              | 1 mA                                                            | High         | -0.3      | 0.35 * VCCI | 0.65 * VCCI     | 3.6       | 0.25 * VCCI | 0.75 * VCCI     | 1                 | 1                 |

| 1.2 V<br>LVCMOS<br>Wide<br>Range <sup>4,5</sup> | 100 µA            | 1 mA                                                            | High         | -0.3      | 0.3 * VCCI  | 0.7 * VCCI      | 3.6       | 0.1         | VCCI – 0.1      | 0.1               | 0.1               |

Notes:

1. Currents are measured at 85°C junction temperature.

2. The minimum drive strength for any LVCMOS 1.2 V or LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

3. All LVMCOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

4. Applicable to V2 Devices operating at VCCI  $\geq$  VCC.

5. All LVCMOS 1.2 V software macros support LVCMOS 1.2 V wide range as specified in the JESD8-12 specification.

# 1.8 V LVCMOS

Low-voltage CMOS for 1.8 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 1.8 V applications. It uses a 1.8 V input buffer and a push-pull output buffer.

| 1.8 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL       | VOH         | IOL | ЮН | IOSH                    | IOSL                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|-----------|-------------|-------------|-----------|-----------|-------------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 2   | 2  | 9                       | 11                      | 10               | 10               |

| 4 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 4   | 4  | 17                      | 22                      | 10               | 10               |

| 6 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 6   | 6  | 35                      | 44                      | 10               | 10               |

| 8 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 8   | 8  | 45                      | 51                      | 10               | 10               |

| 12 mA             | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 12  | 12 | 91                      | 74                      | 10               | 10               |

| 16 mA             | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 16  | 16 | 91                      | 74                      | 10               | 10               |

# Table 2-95 • Minimum and Maximum DC Input and Output Levels Applicable to Advanced I/O Banks

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

3. Currents are measured at 100°C junction temperature and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

# Table 2-96 • Minimum and Maximum DC Input and Output Levels Applicable to Standard Plus I/O Banks

| 1.8 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL       | VOH         | IOL | ЮН | IOSH                    | IOSL                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|-----------|-------------|-------------|-----------|-----------|-------------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 2   | 2  | 9                       | 11                      | 10               | 10               |

| 4 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 4   | 4  | 17                      | 22                      | 10               | 10               |

| 6 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 6   | 6  | 35                      | 44                      | 10               | 10               |

| 8 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 8   | 8  | 35                      | 44                      | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

3. Currents are measured at 100°C junction temperature and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

## **Timing Characteristics**

## 1.5 V DC Core Voltage

## Table 2-115 • 1.5 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Advanced I/O Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 0.97              | 6.62            | 0.18             | 1.17            | 0.66              | 6.75            | 6.06            | 2.79            | 2.31            | 10.35            | 9.66             | ns    |

| 4 mA           | Std.        | 0.97              | 5.75            | 0.18             | 1.17            | 0.66              | 5.86            | 5.34            | 3.06            | 2.78            | 9.46             | 8.93             | ns    |

| 6 mA           | Std.        | 0.97              | 5.43            | 0.18             | 1.17            | 0.66              | 5.54            | 5.19            | 3.12            | 2.90            | 9.13             | 8.78             | ns    |

| 8 mA           | Std.        | 0.97              | 5.35            | 0.18             | 1.17            | 0.66              | 5.46            | 5.20            | 2.63            | 3.36            | 9.06             | 8.79             | ns    |

| 12 mA          | Std.        | 0.97              | 5.35            | 0.18             | 1.17            | 0.66              | 5.46            | 5.20            | 2.63            | 3.36            | 9.06             | 8.79             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

### Table 2-116 • 1.5 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Advanced I/O Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 0.97              | 2.97            | 0.18             | 1.17            | 0.66              | 3.04            | 2.90            | 2.78            | 2.40            | 6.63             | 6.50             | ns    |

| 4 mA           | Std.        | 0.97              | 2.60            | 0.18             | 1.17            | 0.66              | 2.65            | 2.45            | 3.05            | 2.88            | 6.25             | 6.05             | ns    |

| 6 mA           | Std.        | 0.97              | 2.53            | 0.18             | 1.17            | 0.66              | 2.58            | 2.37            | 3.11            | 3.00            | 6.18             | 5.96             | ns    |

| 8 mA           | Std.        | 0.97              | 2.50            | 0.18             | 1.17            | 0.66              | 2.56            | 2.27            | 3.21            | 3.48            | 6.15             | 5.86             | ns    |

| 12 mA          | Std.        | 0.97              | 2.50            | 0.18             | 1.17            | 0.66              | 2.56            | 2.27            | 3.21            | 3.48            | 6.15             | 5.86             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

### Table 2-117 • 1.5 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage

### Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Standard Plus Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 0.97              | 5.93            | 0.18             | 1.18            | 0.66              | 6.04            | 5.46            | 2.30            | 2.15            | 9.64             | 9.06             | ns    |

| 4 mA           | Std.        | 0.97              | 5.11            | 0.18             | 1.18            | 0.66              | 5.21            | 4.80            | 2.54            | 2.58            | 8.80             | 8.39             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

### Table 2-118 • 1.5 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Standard Plus Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 0.97              | 2.58            | 0.18             | 1.18            | 0.66              | 2.64            | 2.41            | 2.29            | 2.24            | 6.23             | 6.01             | ns    |

| 4 mA           | Std.        | 0.97              | 2.25            | 0.18             | 1.18            | 0.66              | 2.30            | 2.00            | 2.53            | 2.68            | 5.89             | 5.59             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

| Parameter Name        | Parameter Definition                                             | Measuring Nodes<br>(from, to)* |

|-----------------------|------------------------------------------------------------------|--------------------------------|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                           | H, DOUT                        |

| tosud                 | Data Setup Time for the Output Data Register                     | F, H                           |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                      | F, H                           |

| tosue                 | Enable Setup Time for the Output Data Register                   | G, H                           |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                    | G, H                           |

| t <sub>OPRE2Q</sub>   | Asynchronous Preset-to-Q of the Output Data Register             | L, DOUT                        |

| t <sub>OREMPRE</sub>  | Asynchronous Preset Removal Time for the Output Data Register    | L, H                           |

| t <sub>ORECPRE</sub>  | Asynchronous Preset Recovery Time for the Output Data Register   | L, H                           |

| t <sub>oeclkq</sub>   | Clock-to-Q of the Output Enable Register                         | H, EOUT                        |

| tOESUD                | Data Setup Time for the Output Enable Register                   | J, H                           |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                    | J, H                           |

| tOESUE                | Enable Setup Time for the Output Enable Register                 | К, Н                           |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                  | K, H                           |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register           | I, EOUT                        |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register  | I, H                           |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register | I, H                           |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                            | A, E                           |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                      | C, A                           |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                       | C, A                           |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                    | B, A                           |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                     | B, A                           |

| t <sub>IPRE2Q</sub>   | Asynchronous Preset-to-Q of the Input Data Register              | D, E                           |

| t <sub>IREMPRE</sub>  | Asynchronous Preset Removal Time for the Input Data Register     | D, A                           |

| t <sub>IRECPRE</sub>  | Asynchronous Preset Recovery Time for the Input Data Register    | D, A                           |

### Table 2-155 • Parameter Definition and Measuring Nodes

Note: \*See Figure 2-16 on page 2-84 for more information.

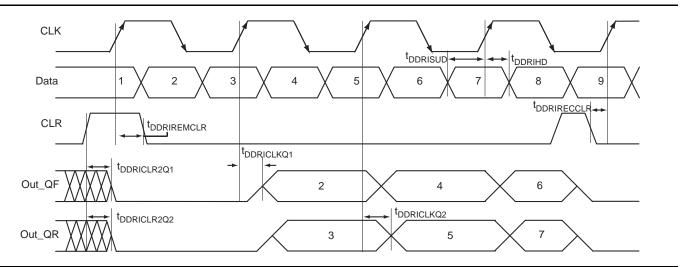

# Figure 2-22 • Input DDR Timing Diagram

### Timing Characteristics

1.5 V DC Core Voltage

# Table 2-164 • Input DDR Propagation DelaysCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter               | Description                                          | Std.   | Units |

|-------------------------|------------------------------------------------------|--------|-------|

| t <sub>DDRICLKQ1</sub>  | Clock-to-Out Out_QR for Input DDR                    | 0.48   | ns    |

| t <sub>DDRICLKQ2</sub>  | Clock-to-Out Out_QF for Input DDR                    | 0.65   | ns    |

| t <sub>DDRISUD1</sub>   | Data Setup for Input DDR (negedge)                   | 0.50   | ns    |

| t <sub>DDRISUD2</sub>   | Data Setup for Input DDR (posedge)                   | 0.40   | ns    |

| t <sub>DDRIHD1</sub>    | Data Hold for Input DDR (negedge)                    | 0.00   | ns    |

| t <sub>DDRIHD2</sub>    | Data Hold for Input DDR (posedge)                    | 0.00   | ns    |

| t <sub>DDRICLR2Q1</sub> | Asynchronous Clear-to-Out Out_QR for Input DDR       | 0.82   | ns    |

| t <sub>DDRICLR2Q2</sub> | Asynchronous Clear-to-Out Out_QF for Input DDR       | 0.98   | ns    |

| t <sub>DDRIREMCLR</sub> | Asynchronous Clear Removal Time for Input DDR        | 0.00   | ns    |

| t <sub>DDRIRECCLR</sub> | Asynchronous Clear Recovery Time for Input DDR       | 0.23   | ns    |

| t <sub>DDRIWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for Input DDR | 0.19   | ns    |

| t <sub>DDRICKMPWH</sub> | Clock Minimum Pulse Width High for Input DDR         | 0.31   | ns    |

| t <sub>DDRICKMPWL</sub> | Clock Minimum Pulse Width Low for Input DDR          | 0.28   | ns    |

| F <sub>DDRIMAX</sub>    | Maximum Frequency for Input DDR                      | 250.00 | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

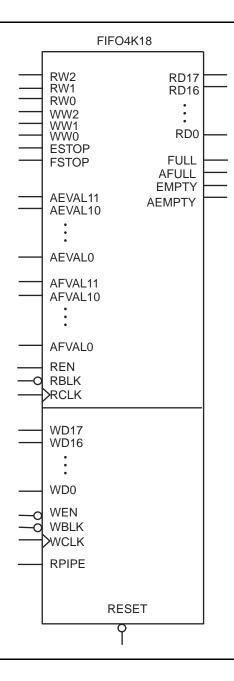

# **FIFO**

Figure 2-37 • FIFO Model

# **JTAG 1532 Characteristics**

JTAG timing delays do not include JTAG I/Os. To obtain complete JTAG timing, add I/O buffer delays to the corresponding standard selected; refer to the I/O timing characteristics in the "User I/O Characteristics" section on page 2-20 for more details.

# Timing Characteristics

### *Table 2-199* • JTAG 1532

### Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                 | Std.  | Units |

|----------------------|-----------------------------|-------|-------|

| t <sub>DISU</sub>    | Test Data Input Setup Time  | 1.00  | ns    |

| t <sub>DIHD</sub>    | Test Data Input Hold Time   | 2.00  | ns    |

| t <sub>TMSSU</sub>   | Test Mode Select Setup Time | 1.00  | ns    |

| t <sub>TMDHD</sub>   | Test Mode Select Hold Time  | 2.00  | ns    |

| t <sub>TCK2Q</sub>   | Clock to Q (data out)       | 8.00  | ns    |

| t <sub>RSTB2Q</sub>  | Reset to Q (data out)       | 25.00 | ns    |

| F <sub>TCKMAX</sub>  | TCK Maximum Frequency       | 15    | MHz   |

| t <sub>TRSTREM</sub> | ResetB Removal Time         | 0.58  | ns    |

| t <sub>TRSTREC</sub> | ResetB Recovery Time        | 0.00  | ns    |

| t <sub>TRSTMPW</sub> | ResetB Minimum Pulse        | TBD   | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

### *Table 2-200* • JTAG 1532

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Parameter            | Description                 | Std.  | Units |

|----------------------|-----------------------------|-------|-------|

| t <sub>DISU</sub>    | Test Data Input Setup Time  | 1.50  | ns    |

| t <sub>DIHD</sub>    | Test Data Input Hold Time   | 3.00  | ns    |

| t <sub>TMSSU</sub>   | Test Mode Select Setup Time | 1.50  | ns    |

| t <sub>TMDHD</sub>   | Test Mode Select Hold Time  | 3.00  | ns    |

| t <sub>TCK2Q</sub>   | Clock to Q (data out)       | 11.00 | ns    |

| t <sub>RSTB2Q</sub>  | Reset to Q (data out)       | 30.00 | ns    |

| F <sub>TCKMAX</sub>  | TCK Maximum Frequency       | 9.00  | MHz   |

| t <sub>TRSTREM</sub> | ResetB Removal Time         | 1.18  | ns    |

| t <sub>TRSTREC</sub> | ResetB Recovery Time        | 0.00  | ns    |

| t <sub>TRSTMPW</sub> | ResetB Minimum Pulse        | TBD   | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

| QN68       |                 | QN68       |                 |  |

|------------|-----------------|------------|-----------------|--|

| Pin Number | AGL030 Function | Pin Number | AGL030 Function |  |

| 1          | IO82RSB1        | 37         | TRST            |  |

| 2          | IO80RSB1        | 38         | VJTAG           |  |

| 3          | IO78RSB1        | 39         | IO40RSB0        |  |

| 4          | IO76RSB1        | 40         | IO37RSBO        |  |

| 5          | GECO/IO73RSB1   | 41         | GDBO/IO34RSBO   |  |

| 6          | GEAO/IO72RSB1   | 42         | GDAO/IO33RSBO   |  |

| 7          | GEBO/IO71RSB1   | 43         | GDCO/IO32RSBO   |  |

| 8          | VCC             | 44         | VCCIBO          |  |

| 9          | GND             | 45         | GND             |  |

| 10         | VCCIB1          | 46         | VCC             |  |

| 11         | IO68RSB1        | 47         | IO31RSB0        |  |

| 12         | IO67RSB1        | 48         | IO29RSBO        |  |

| 13         | IO66RSB1        | 49         | IO28RSBO        |  |

| 14         | IO65RSB1        | 50         | IO27RSBO        |  |

| 15         | IO64RSB1        | 51         | IO25RSB0        |  |

| 16         | IO63RSB1        | 52         | IO24RSBO        |  |

| 17         | IO62RSB1        | 53         | IO22RSB0        |  |

| 18         | FF/IO60RSB1     | 54         | IO21RSBO        |  |

| 19         | IO58RSB1        | 55         | IO19RSBO        |  |

| 20         | IO56RSB1        | 56         | IO17RSBO        |  |

| 21         | IO54RSB1        | 57         | IO15RSB0        |  |

| 22         | IO52RSB1        | 58         | IO14RSBO        |  |

| 23         | IO51RSB1        | 59         | VCCIBO          |  |

| 24         | VCC             | 60         | GND             |  |

| 25         | GND             | 61         | VCC             |  |

| 26         | VCCIB1          | 62         | IO12RSBO        |  |

| 27         | IO50RSB1        | 63         | IO10RSB0        |  |

| 28         | IO48RSB1        | 64         | IOO8RSBO        |  |

| 29         | IO46RSB1        | 65         | IOO6RSB0        |  |

| 30         | IO44RSB1        | 66         | IOO4RSBO        |  |

| 31         | IO42RSB1        | 67         | IO02RSB0        |  |

| 32         | ТСК             | 68         | IOOORSBO        |  |

| 33         | TDI             |            |                 |  |

| 34         | TMS             |            |                 |  |

| 35         | VPUMP           |            |                 |  |

| 36         | TDO             |            |                 |  |

|            |                 |            |                 |  |

| 8 | IO14RSBO |

|---|----------|

| 9 | VCCIBO   |

| 0 | GND      |

| 1 | VCC      |

| 2 | IO12RSBO |

| 3 | IO10RSB0 |

| 4 | IO08RSB0 |

| 5 | IO06RSB0 |

| 6 | IOO4RSBO |

| 7 | IO02RSB0 |

| 8 | IOOORSBO |

|   |          |

|   |          |

|   |          |

|   |          |

|   |          |

Package Pin Assignments

| FG484      |                 |  |

|------------|-----------------|--|

| Pin Number | AGL400 Function |  |

| B7         | NC              |  |

| B8         | NC              |  |

| B9         | NC              |  |

| B10        | NC              |  |

| B11        | NC              |  |

| B12        | NC              |  |

| B13        | NC              |  |

| B14        | NC              |  |

| B15        | NC              |  |

| B16        | NC              |  |

| B17        | NC              |  |

| B18        | NC              |  |

| B19        | NC              |  |

| B20        | NC              |  |

| B21        | VCCIB1          |  |

| B22        | GND             |  |

| C1         | VCCIB3          |  |

| C2         | NC              |  |

| C3         | NC              |  |

| C4         | NC              |  |

| C5         | GND             |  |

| C6         | NC              |  |

| C7         | NC              |  |

| C8         | VCC             |  |

| C9         | VCC             |  |

| C10        | NC              |  |

| C11        | NC              |  |

| C12        | NC              |  |

| C13        | NC              |  |

| C14        | VCC             |  |

| C15        | VCC             |  |

| C16        | NC              |  |

| C17        | NC              |  |

| C18        | GND             |  |

| C19        | NC              |  |

| C20        | NC              |  |

Datasheet Information

# **Datasheet Categories**

# Categories

In order to provide the latest information to designers, some datasheet parameters are published before data has been fully characterized from silicon devices. The data provided for a given device, as highlighted in the "IGLOO Device Status" table, is designated as either "Product Brief," "Advance," "Preliminary," or "Production." The definitions of these categories are as follows:

# **Product Brief**

The product brief is a summarized version of a datasheet (advance or production) and contains general product information. This document gives an overview of specific device and family information.

# Advance

This version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production. This label only applies to the DC and Switching Characteristics chapter of the datasheet and will only be used when the data has not been fully characterized.

# Preliminary

The datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible.

# Unmarked (production)

This version contains information that is considered to be final.

# **Export Administration Regulations (EAR)**

The products described in this document are subject to the Export Administration Regulations (EAR). They could require an approved export license prior to export from the United States. An export includes release of product or disclosure of technology to a foreign national inside or outside the United States.

# Safety Critical, Life Support, and High-Reliability Applications Policy

The Microsemi products described in this advance status document may not have completed Microsemi's qualification process. Microsemi may amend or enhance products during the product introduction and qualification process, resulting in changes in device functionality or performance. It is the responsibility of each customer to ensure the fitness of any Microsemi product (but especially a new product) for a particular purpose, including appropriateness for safety-critical, life-support, and other high-reliability applications. Consult Microsemi's Terms and Conditions for specific liability exclusions relating to life-support applications. A reliability report covering all of the Microsemi SoC Products Group's products is available at http://www.microsemi.com/soc/documents/ORT\_Report.pdf. Microsemi also offers a variety of enhanced qualification and lot acceptance screening procedures. Contact your local Microsemi sales office for additional reliability information.