Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

E·XFI

| Product Status                 | Active                                                                       |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                            |

| Number of Logic Elements/Cells | 24576                                                                        |

| Total RAM Bits                 | 147456                                                                       |

| Number of I/O                  | 177                                                                          |

| Number of Gates                | 1000000                                                                      |

| Voltage - Supply               | 1.14V ~ 1.575V                                                               |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 85°C (TA)                                                            |

| Package / Case                 | 256-LBGA                                                                     |

| Supplier Device Package        | 256-FPBGA (17x17)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1agl1000v2-fg256i |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Wide Range I/O Support

IGLOO devices support JEDEC-defined wide range I/O operation. IGLOO devices support both the JESD8-B specification, covering 3 V and 3.3 V supplies, for an effective operating range of 2.7 V to 3.6 V, and JESD8-12 with its 1.2 V nominal, supporting an effective operating range of 1.14 V to 1.575 V.

Wider I/O range means designers can eliminate power supplies or power conditioning components from the board or move to less costly components with greater tolerances. Wide range eases I/O bank management and provides enhanced protection from system voltage spikes, while providing the flexibility to easily run custom voltage applications.

## **Specifying I/O States During Programming**

You can modify the I/O states during programming in FlashPro. In FlashPro, this feature is supported for PDB files generated from Designer v8.5 or greater. See the *FlashPro User Guide* for more information.

- Note: PDB files generated from Designer v8.1 to Designer v8.4 (including all service packs) have limited display of Pin Numbers only.

- 1. Load a PDB from the FlashPro GUI. You must have a PDB loaded to modify the I/O states during programming.

- 2. From the FlashPro GUI, click PDB Configuration. A FlashPoint Programming File Generator window appears.

- 3. Click the Specify I/O States During Programming button to display the Specify I/O States During Programming dialog box.

- 4. Sort the pins as desired by clicking any of the column headers to sort the entries by that header. Select the I/Os you wish to modify (Figure 1-5 on page 1-9).

- 5. Set the I/O Output State. You can set Basic I/O settings if you want to use the default I/O settings for your pins, or use Custom I/O settings to customize the settings for each pin. Basic I/O state settings:

- 1 I/O is set to drive out logic High

- 0 I/O is set to drive out logic Low

Last Known State – I/O is set to the last value that was driven out prior to entering the programming mode, and then held at that value during programming

Z -Tri-State: I/O is tristated

## **Power Consumption of Various Internal Resources**

Table 2-19 • Different Components Contributing to Dynamic Power Consumption in IGLOO Devices

For IGLOO V2 or V5 Devices, 1.5 V DC Core Supply Voltage

|           |                                                                      |         |           | Devic      | e Specific<br>(μW/l |             | ower        |           |        |

|-----------|----------------------------------------------------------------------|---------|-----------|------------|---------------------|-------------|-------------|-----------|--------|

| Parameter | Definition                                                           | AGL1000 | AGL600    | AGL400     | AGL250              | AGL125      | AGL060      | AGL030    | AGL015 |

| PAC1      | Clock contribution of a<br>Global Rib                                | 7.778   | 6.221     | 6.082      | 4.460               | 4.446       | 2.736       | 0.000     | 0.000  |

| PAC2      | Clock contribution of a<br>Global Spine                              | 4.334   | 3.512     | 2.759      | 2.718               | 1.753       | 1.971       | 3.483     | 3.483  |

| PAC3      | Clock contribution of a<br>VersaTile row                             | 1.379   | 1.445     | 1.377      | 1.483               | 1.467       | 1.503       | 1.472     | 1.472  |

| PAC4      | Clock contribution of a<br>VersaTile used as a<br>sequential module  | 0.151   | 0.149     | 0.151      | 0.149               | 0.149       | 0.151       | 0.146     | 0.146  |

| PAC5      | First contribution of a<br>VersaTile used as a<br>sequential module  | 0.057   |           |            |                     |             |             |           |        |

| PAC6      | Second contribution of a<br>VersaTile used as a<br>sequential module | 0.207   |           |            |                     |             |             |           |        |

| PAC7      | Contribution of a VersaTile<br>used as a combinatorial<br>module     | 0.276   | 0.262     | 0.279      | 0.277               | 0.280       | 0.300       | 0.281     | 0.273  |

| PAC8      | Average contribution of a routing net                                | 1.161   | 1.147     | 1.193      | 1.273               | 1.076       | 1.088       | 1.134     | 1.153  |

| PAC9      | Contribution of an I/O input pin (standard-dependent)                |         | See Table | 2-13 on pa | age 2-10 th         | rough Table | e 2-15 on p | age 2-11. |        |

| PAC10     | Contribution of an I/O output pin (standard-dependent)               |         | See Table | 2-16 on pa | age 2-11 th         | rough Table | e 2-18 on p | age 2-12. |        |

| PAC11     | Average contribution of a<br>RAM block during a read<br>operation    |         |           |            | 25.                 | 00          |             |           |        |

| PAC12     | Average contribution of a<br>RAM block during a write<br>operation   |         |           |            | 30.                 | 00          |             |           |        |

| PAC13     | Dynamic PLL contribution                                             |         |           |            | 2.7                 | 70          |             |           |        |

Note: For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi power spreadsheet calculator or SmartPower tool in Libero SoC.

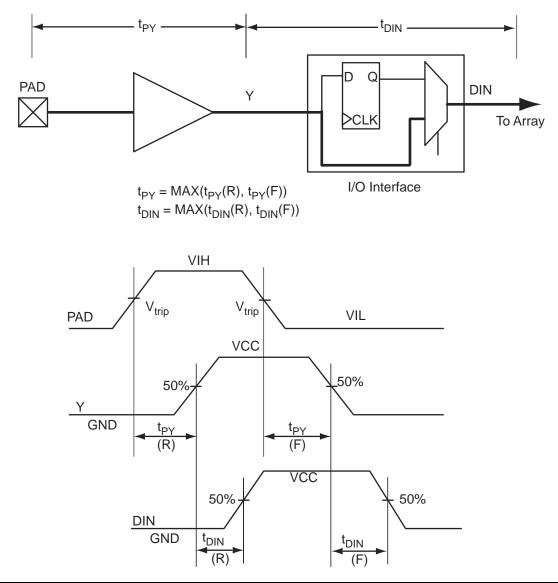

Figure 2-4 • Input Buffer Timing Model and Delays (example)

### Applies to 1.2 V DC Core Voltage

# Table 2-73 • 3.3 V LVCMOS Wide Range Low Slew – Applies to 1.2 V DC Core Voltage<br/>Commercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.7 V<br/>Applicable to Advanced Banks

| Drive<br>Strength | Equivalent<br>Software<br>Default Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>dout</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>eout</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|-------------------|----------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 100 µA            | 2 mA                                                                       | Std.           | 1.55              | 7.52            | 0.26             | 1.32            | 1.10              | 7.52            | 6.38            | 3.84            | 4.02            | 13.31            | 12.16            | ns    |

| 100 µA            | 4 mA                                                                       | Std.           | 1.55              | 7.52            | 0.26             | 1.32            | 1.10              | 7.52            | 6.38            | 3.84            | 4.02            | 13.31            | 12.16            | ns    |

| 100 µA            | 6 mA                                                                       | Std.           | 1.55              | 6.37            | 0.26             | 1.32            | 1.10              | 6.37            | 5.57            | 4.23            | 4.73            | 12.16            | 11.35            | ns    |

| 100 µA            | 8 mA                                                                       | Std.           | 1.55              | 6.37            | 0.26             | 1.32            | 1.10              | 6.37            | 5.57            | 4.23            | 4.73            | 12.16            | 11.35            | ns    |

| 100 µA            | 12 mA                                                                      | Std.           | 1.55              | 5.55            | 0.26             | 1.32            | 1.10              | 5.55            | 4.96            | 4.50            | 5.18            | 11.34            | 10.75            | ns    |

| 100 µA            | 16 mA                                                                      | Std.           | 1.55              | 5.32            | 0.26             | 1.32            | 1.10              | 5.32            | 4.82            | 4.56            | 5.29            | 11.10            | 10.61            | ns    |

| 100 µA            | 24 mA                                                                      | Std.           | 1.55              | 5.19            | 0.26             | 1.32            | 1.10              | 5.19            | 4.85            | 4.63            | 5.74            | 10.98            | 10.63            | ns    |

Notes:

1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ± 100 μA. Drive strengths displayed in software are supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

# Table 2-74 • 3.3 V LVCMOS Wide Range High Slew – Applies to 1.2 V DC Core VoltageCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.7Applicable to Advanced Banks

| Drive<br>Strength | Equivalent<br>Software<br>Default Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>eout</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|-------------------|----------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 100 µA            | 2 mA                                                                       | Std.           | 1.55              | 4.75            | 0.26             | 1.32            | 1.10              | 4.75            | 3.77            | 3.84            | 4.27            | 10.54            | 9.56             | ns    |

| 100 µA            | 4 mA                                                                       | Std.           | 1.55              | 4.75            | 0.26             | 1.32            | 1.10              | 4.75            | 3.77            | 3.84            | 4.27            | 10.54            | 9.56             | ns    |

| 100 µA            | 6 mA                                                                       | Std.           | 1.55              | 4.10            | 0.26             | 1.32            | 1.10              | 4.10            | 3.19            | 4.24            | 4.98            | 9.88             | 8.98             | ns    |

| 100 µA            | 8 mA                                                                       | Std.           | 1.55              | 4.10            | 0.26             | 1.32            | 1.10              | 4.10            | 3.19            | 4.24            | 4.98            | 9.88             | 8.98             | ns    |

| 100 µA            | 12 mA                                                                      | Std.           | 1.55              | 3.73            | 0.26             | 1.32            | 1.10              | 3.73            | 2.91            | 4.51            | 5.43            | 9.52             | 8.69             | ns    |

| 100 µA            | 16 mA                                                                      | Std.           | 1.55              | 3.67            | 0.26             | 1.32            | 1.10              | 3.67            | 2.85            | 4.57            | 5.55            | 9.46             | 8.64             | ns    |

| 100 µA            | 24 mA                                                                      | Std.           | 1.55              | 3.70            | 0.26             | 1.32            | 1.10              | 3.70            | 2.79            | 4.65            | 6.01            | 9.49             | 8.58             | ns    |

Notes:

1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ± 100 μA. Drive strengths displayed in software are supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

3. Software default selection highlighted in gray.

### Applies to 1.2 V Core Voltage

# Table 2-89 • 2.5 V LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage<br/>Commercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.3 V<br/>Applicable to Advanced I/O Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 1.55              | 5.59            | 0.26             | 1.20            | 1.10              | 5.68            | 5.14            | 2.82            | 2.80            | 11.47            | 10.93            | ns    |

| 4 mA           | Std.        | 1.55              | 5.59            | 0.26             | 1.20            | 1.10              | 5.68            | 5.14            | 2.82            | 2.80            | 11.47            | 10.93            | ns    |

| 6 mA           | Std.        | 1.55              | 4.76            | 0.26             | 1.20            | 1.10              | 4.84            | 4.47            | 3.10            | 3.33            | 10.62            | 10.26            | ns    |

| 8 mA           | Std.        | 1.55              | 4.76            | 0.26             | 1.20            | 1.10              | 4.84            | 4.47            | 3.10            | 3.33            | 10.62            | 10.26            | ns    |

| 12 mA          | Std.        | 1.55              | 4.17            | 0.26             | 1.20            | 1.10              | 4.23            | 3.99            | 3.30            | 3.67            | 10.02            | 9.77             | ns    |

| 16 mA          | Std.        | 1.55              | 3.98            | 0.26             | 1.20            | 1.10              | 4.04            | 3.88            | 3.34            | 3.76            | 9.83             | 9.66             | ns    |

| 24 mA          | Std.        | 1.55              | 3.90            | 0.26             | 1.20            | 1.10              | 3.96            | 3.90            | 3.40            | 4.09            | 9.75             | 9.68             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

### Table 2-90 • 2.5 V LVCMOS High Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.3 V Applicable to Advanced I/O Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 1.55              | 3.33            | 0.26             | 1.20            | 1.10              | 3.38            | 3.09            | 2.82            | 2.91            | 9.17             | 8.88             | ns    |

| 4 mA           | Std.        | 1.55              | 3.33            | 0.26             | 1.20            | 1.10              | 3.38            | 3.09            | 2.82            | 2.91            | 9.17             | 8.88             | ns    |

| 6 mA           | Std.        | 1.55              | 2.89            | 0.26             | 1.20            | 1.10              | 2.93            | 2.56            | 3.10            | 3.45            | 8.72             | 8.34             | ns    |

| 8 mA           | Std.        | 1.55              | 2.89            | 0.26             | 1.20            | 1.10              | 2.93            | 2.56            | 3.10            | 3.45            | 8.72             | 8.34             | ns    |

| 12 mA          | Std.        | 1.55              | 2.64            | 0.26             | 1.20            | 1.10              | 2.67            | 2.29            | 3.30            | 3.79            | 8.46             | 8.08             | ns    |

| 16 mA          | Std.        | 1.55              | 2.59            | 0.26             | 1.20            | 1.10              | 2.63            | 2.24            | 3.34            | 3.88            | 8.41             | 8.03             | ns    |

| 24 mA          | Std.        | 1.55              | 2.60            | 0.26             | 1.20            | 1.10              | 2.64            | 2.18            | 3.40            | 4.22            | 8.42             | 7.97             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

Table 2-91 • 2.5 V LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.3 V Applicable to Standard Plus Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 1.55              | 5.02            | 0.26             | 1.19            | 1.10              | 5.11            | 4.60            | 2.50            | 2.62            | 10.89            | 10.38            | ns    |

| 4 mA           | Std.        | 1.55              | 5.02            | 0.26             | 1.19            | 1.10              | 5.11            | 4.60            | 2.50            | 2.62            | 10.89            | 10.38            | ns    |

| 6 mA           | Std.        | 1.55              | 4.21            | 0.26             | 1.19            | 1.10              | 4.27            | 4.00            | 2.76            | 3.10            | 10.06            | 9.79             | ns    |

| 8 mA           | Std.        | 1.55              | 4.21            | 0.26             | 1.19            | 1.10              | 4.27            | 4.00            | 2.76            | 3.10            | 10.06            | 9.79             | ns    |

| 12 mA          | Std.        | 1.55              | 3.66            | 0.26             | 1.19            | 1.10              | 3.71            | 3.55            | 2.94            | 3.41            | 9.50             | 9.34             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

| Table 2-138 • Minimum and Maximum DC Input and Output Levels for LVCMOS 1.2 V Wide Range |  |

|------------------------------------------------------------------------------------------|--|

| Applicable to Standard Plus I/O Banks                                                    |  |

| 1.2 V LVCI<br>Wide Rang |                                                                               |           | VIL         | VIH         |           | VOL         | VOH         | IOL | юн  | IOSL                    | IOSH                    | IIL <sup>2</sup> | IIH <sup>3</sup> |

|-------------------------|-------------------------------------------------------------------------------|-----------|-------------|-------------|-----------|-------------|-------------|-----|-----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength       | Equivalent<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA  | Max.<br>mA <sup>4</sup> | Max.<br>mA <sup>4</sup> | μA <sup>5</sup>  | μA <sup>5</sup>  |

| 100 µA                  | 2mA                                                                           | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.26      | 0.25 * VCCI | 0.75 * VCCI | 100 | 100 | 20                      | 26                      | 10               | 10               |

Notes:

1. The minimum drive strength for the default LVCMOS 1.2 V software configuration when run in wide range is ± 100 μA. The drive strength displayed in software is supported in normal range only. For a detailed I/V curve, refer to the IBIS models.

2. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

3. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

4. Currents are measured at 100°C junction temperature and maximum voltage.

5. Currents are measured at 85°C junction temperature.

6. Software default selection highlighted in gray.

### Table 2-139 • Minimum and Maximum DC Input and Output Levels for LVCMOS 1.2 V Wide Range Applicable to Standard I/O Banks

| 1.2 V LVCI<br>Wide Rang |                                                                               |           | VIL         | VIH         |           | VOL         | VOH         | IOL | юн  | IOSL                    | IOSH                    | IIL <sup>2</sup> | IIH <sup>3</sup> |

|-------------------------|-------------------------------------------------------------------------------|-----------|-------------|-------------|-----------|-------------|-------------|-----|-----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength       | Equivalent<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA  | Max.<br>mA <sup>4</sup> | Max.<br>mA <sup>4</sup> | μA <sup>5</sup>  | μA <sup>5</sup>  |

| 100 µA                  | 1 mA                                                                          | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 100 | 100 | 20                      | 26                      | 10               | 10               |

Notes:

The minimum drive strength for the default LVCMOS 1.2 V software configuration when run in wide range is ± 100 μA. The drive strength displayed in software is supported in normal range only. For a detailed I/V curve, refer to the IBIS models.

2. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

3. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

4. Currents are measured at 100°C junction temperature and maximum voltage.

5. Currents are measured at 85°C junction temperature.

6. Software default selection highlighted in gray.

#### Table 2-140 • 1.2 V LVCMOS Wide Range AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 1.2            | 0.6                  | 5                      |

Note: \*Measuring point = Vtrip. See Table 2-29 on page 2-28 for a complete table of trip points.

### **Timing Characteristics**

Refer to LVCMOS 1.2 V (normal range) "Timing Characteristics" on page 2-75 for worst-case timing.

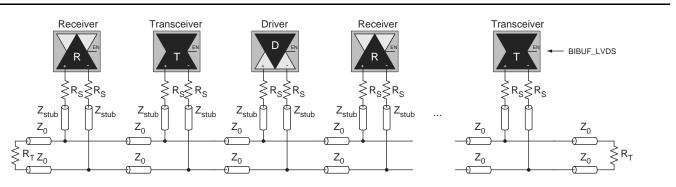

### B-LVDS/M-LVDS

Bus LVDS (B-LVDS) and Multipoint LVDS (M-LVDS) specifications extend the existing LVDS standard to highperformance multipoint bus applications. Multidrop and multipoint bus configurations may contain any combination of drivers, receivers, and transceivers. Microsemi LVDS drivers provide the higher drive current required by B-LVDS and M-LVDS to accommodate the loading. The drivers require series terminations for better signal quality and to control voltage swing. Termination is also required at both ends of the bus since the driver can be located anywhere on the bus. These configurations can be implemented using the TRIBUF\_LVDS and BIBUF\_LVDS macros along with appropriate terminations. Multipoint designs using Microsemi LVDS macros can achieve up to 200 MHz with a maximum of 20 loads. A sample application is given in Figure 2-14. The input and output buffer delays are available in the LVDS section in Table 2-149 on page 2-81 and Table 2-150 on page 2-81.

Example: For a bus consisting of 20 equidistant loads, the following terminations provide the required differential voltage, in worst-case Industrial operating conditions, at the farthest receiver:  $R_S = 60 \Omega$  and  $R_T = 70 \Omega$ , given  $Z_0 = 50 \Omega$  (2") and  $Z_{stub} = 50 \Omega$  (~1.5").

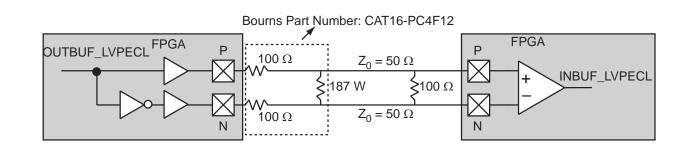

### LVPECL

Low-Voltage Positive Emitter-Coupled Logic (LVPECL) is another differential I/O standard. It requires that one data bit be carried through two signal lines. Like LVDS, two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-15. The building blocks of the LVPECL transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVDS implementation because the output standard specifications are different.

Figure 2-15 • LVPECL Circuit Diagram and Board-Level Implementation

# **VersaTile Characteristics**

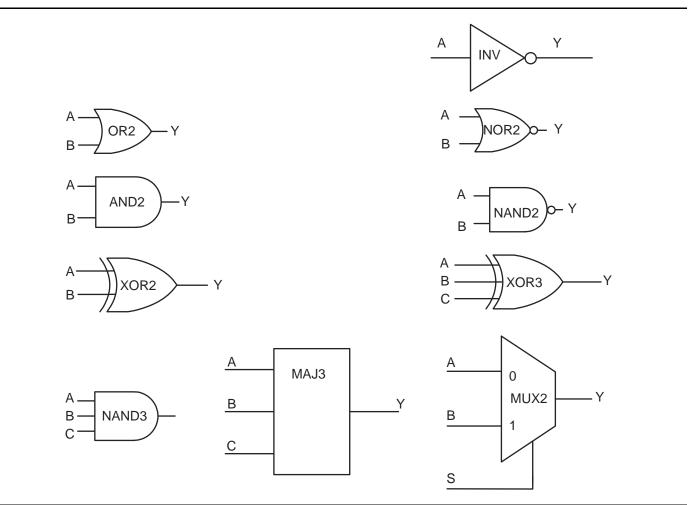

### VersaTile Specifications as a Combinatorial Module

The IGLOO library offers all combinations of LUT-3 combinatorial functions. In this section, timing characteristics are presented for a sample of the library. For more details, refer to the *IGLOO, Fusion, and ProASIC3 Macro Library Guide*.

Figure 2-25 • Sample of Combinatorial Cells

# **Clock Conditioning Circuits**

### **CCC Electrical Specifications**

### **Timing Characteristics**

### Table 2-189 • IGLOO CCC/PLL Specification

For IGLOO V2 or V5 Devices, 1.5 V DC Core Supply Voltage

| Parameter                                                          | Min.           | Тур.             | Max.            | Units           |

|--------------------------------------------------------------------|----------------|------------------|-----------------|-----------------|

| Clock Conditioning Circuitry Input Frequency fIN_CCC               | 1.5            |                  | 250             | MHz             |

| Clock Conditioning Circuitry Output Frequency f <sub>OUT_CCC</sub> | 0.75           |                  | 250             | MHz             |

| Delay Increments in Programmable Delay Blocks <sup>1, 2</sup>      |                | 360 <sup>3</sup> |                 | ps              |

| Number of Programmable Values in Each Programmable Delay Block     |                |                  | 32              |                 |

| Serial Clock (SCLK) for Dynamic PLL <sup>4, 5</sup>                |                |                  | 100             | ns              |

| Input Cycle-to-Cycle Jitter (peak magnitude)                       |                |                  | 1               | ns              |

| Acquisition Time                                                   |                |                  |                 |                 |

| LockControl = 0                                                    |                |                  | 300             | μs              |

| LockControl = 1                                                    |                |                  | 6.0             | ms              |

| Tracking Jitter <sup>6</sup>                                       |                |                  |                 |                 |

| LockControl = 0                                                    |                |                  | 2.5             | ns              |

| LockControl = 1                                                    |                |                  | 1.5             | ns              |

| Output Duty Cycle                                                  | 48.5           |                  | 51.5            | %               |

| Delay Range in Block: Programmable Delay 1 <sup>1, 2</sup>         | 1.25           |                  | 15.65           | ns              |

| Delay Range in Block: Programmable Delay 2 <sup>1, 2</sup>         | 0.469          |                  | 15.65           | ns              |

| Delay Range in Block: Fixed Delay <sup>1, 2</sup>                  |                | 3.5              |                 | ns              |

| CCC Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub>         | Maxim          | um Peak-to-      | Peak Jitter Da  | ta <sup>7</sup> |

|                                                                    | $SSO \geq 4^8$ | $SSO \geq 8^8$   | $SSO \geq 16^8$ |                 |

| 0.75 MHz to 50 MHz                                                 | 0.60%          | 0.80%            | 1.20%           |                 |

| 50 MHz to 160 MHz                                                  | 4.00%          | 6.00%            | 12.00%          |                 |

Notes:

1. This delay is a function of voltage and temperature. See Table 2-6 on page 2-7 and Table 2-7 on page 2-7 for deratings.

2.  $T_J = 25^{\circ}C, V_{CC} = 1.5 V$

3. When the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available. Refer to the Libero SoC Online Help associated with the core for more information.

4. The AGL030 device does not support a PLL.

5. Maximum value obtained for a Std. speed grade device in Worst-Case Commercial Conditions. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

6. Tracking jitter is defined as the variation in clock edge position of PLL outputs with reference to the PLL input clock edge. Tracking jitter does not measure the variation in PLL output period, which is covered by the period jitter parameter.

7. Measurements done with LVTTL 3.3 V, 8 mA I/O drive strength, and high slew Rate. VCC/VCCPLL = 1.14 V, VQ/PQ/TQ type of packages, 20 pF load.

8. Simultaneously Switching Outputs (SSOs) are outputs that are synchronous to a single clock domain and have clock-to-out times that are within ±200 ps of each other. Switching I/Os are placed outside of the PLL bank. Refer to the "Simultaneously Switching Outputs (SSOs) and Printed Circuit Board Layout" section in the IGLOO FPGA Fabric User Guide.

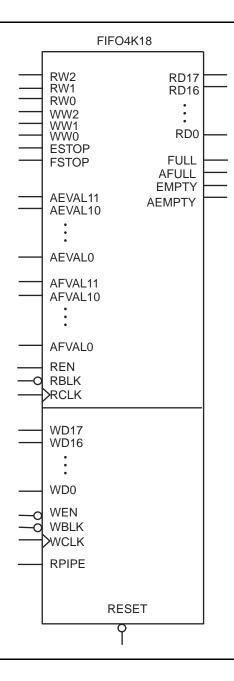

### **FIFO**

Figure 2-37 • FIFO Model

The Flash\*Freeze pin can be used with any single-ended I/O standard supported by the I/O bank in which the pin is located, and input signal levels compatible with the I/O standard selected. The FF pin should be treated as a sensitive asynchronous signal. When defining pin placement and board layout, simultaneously switching outputs (SSOs) and their effects on sensitive asynchronous pins must be considered.

Unused FF or I/O pins are tristated with weak pull-up. This default configuration applies to both Flash\*Freeze mode and normal operation mode. No user intervention is required.

Table 3-1 shows the Flash\*Freeze pin location on the available packages for IGLOO a devices. The Flash\*Freeze pin location is independent of device, allowing migration to larger or smaller IGLOO devices while maintaining the same pin location on the board. Refer to the "Flash\*Freeze Technology and Low Power Modes" chapter of the *IGLOO FPGA Fabric User Guide* for more information on I/O states during Flash\*Freeze mode.

### Table 3-1 • Flash\*Freeze Pin Location in IGLOO Family Packages (device-independent)

| IGLOO Packages | Flash*Freeze Pin |

|----------------|------------------|

| CS81/UC81      | H2               |

| CS121          | J5               |

| CS196          | P3               |

| CS281          | W2               |

| QN48           | 14               |

| QN68           | 18               |

| QN132          | B12              |

| VQ100          | 27               |

| FG144          | L3               |

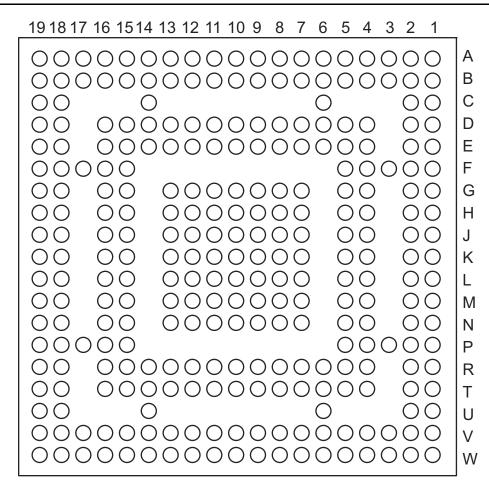

| FG256          | Т3               |

| FG484          | W6               |

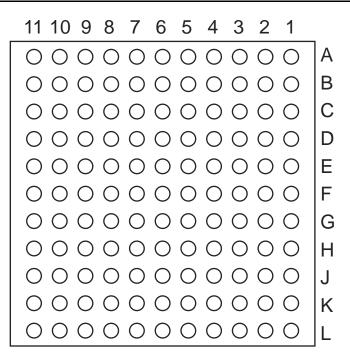

Package Pin Assignments

# CS121

Note: This is the bottom view of the package.

### Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

Package Pin Assignments

# **CS281**

Note: This is the bottom view of the package.

### Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

|            | QN132           | QN132      |                 | QN132      |                 |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | AGL060 Function | Pin Number | AGL060 Function | Pin Number | AGL060 Function |

| A1         | GAB2/IO00RSB1   | A37        | GBB1/IO25RSB0   | B24        | GDC0/IO49RSB0   |

| A2         | IO93RSB1        | A38        | GBC0/IO22RSB0   | B25        | GND             |

| A3         | VCCIB1          | A39        | VCCIB0          | B26        | NC              |

| A4         | GFC1/IO89RSB1   | A40        | IO21RSB0        | B27        | GCB2/IO45RSB0   |

| A5         | GFB0/IO86RSB1   | A41        | IO18RSB0        | B28        | GND             |

| A6         | VCCPLF          | A42        | IO15RSB0        | B29        | GCB0/IO41RSB0   |

| A7         | GFA1/IO84RSB1   | A43        | IO14RSB0        | B30        | GCC1/IO38RSB0   |

| A8         | GFC2/IO81RSB1   | A44        | IO11RSB0        | B31        | GND             |

| A9         | IO78RSB1        | A45        | GAB1/IO08RSB0   | B32        | GBB2/IO30RSB0   |

| A10        | VCC             | A46        | NC              | B33        | VMV0            |

| A11        | GEB1/IO75RSB1   | A47        | GAB0/IO07RSB0   | B34        | GBA0/IO26RSB0   |

| A12        | GEA0/IO72RSB1   | A48        | IO04RSB0        | B35        | GBC1/IO23RSB0   |

| A13        | GEC2/IO69RSB1   | B1         | IO01RSB1        | B36        | GND             |

| A14        | IO65RSB1        | B2         | GAC2/IO94RSB1   | B37        | IO20RSB0        |

| A15        | VCC             | B3         | GND             | B38        | IO17RSB0        |

| A16        | IO64RSB1        | B4         | GFC0/IO88RSB1   | B39        | GND             |

| A17        | IO63RSB1        | B5         | VCOMPLF         | B40        | IO12RSB0        |

| A18        | IO62RSB1        | B6         | GND             | B41        | GAC0/IO09RSB0   |

| A19        | IO61RSB1        | B7         | GFB2/IO82RSB1   | B42        | GND             |

| A20        | IO58RSB1        | B8         | IO79RSB1        | B43        | GAA1/IO06RSB0   |

| A21        | GDB2/IO55RSB1   | B9         | GND             | B44        | GNDQ            |

| A22        | NC              | B10        | GEB0/IO74RSB1   | C1         | GAA2/IO02RSB1   |

| A23        | GDA2/IO54RSB1   | B11        | VMV1            | C2         | IO95RSB1        |

| A24        | TDI             | B12        | FF/GEB2/IO70RSB | C3         | VCC             |

| A25        | TRST            |            | 1               | C4         | GFB1/IO87RSB1   |

| A26        | GDC1/IO48RSB0   | B13        | IO67RSB1        | C5         | GFA0/IO85RSB1   |

| A27        | VCC             | B14        | GND             | C6         | GFA2/IO83RSB1   |

| A28        | IO47RSB0        | B15        | NC              | C7         | IO80RSB1        |

| A29        | GCC2/IO46RSB0   | B16        | NC              | C8         | VCCIB1          |

| A30        | GCA2/IO44RSB0   | B17        | GND             | C9         | GEA1/IO73RSB1   |

| A31        | GCA0/IO43RSB0   | B18        | IO59RSB1        | C10        | GNDQ            |

| A32        | GCB1/IO40RSB0   | B19        | GDC2/IO56RSB1   | C11        | GEA2/IO71RSB1   |

| A33        | IO36RSB0        | B20        | GND             | C12        | IO68RSB1        |

| A34        | VCC             | B21        | GNDQ            | C13        | VCCIB1          |

| A35        | IO31RSB0        | B22        | TMS             | C14        | NC              |

| A36        | GBA2/IO28RSB0   | B23        | TDO             | C15        | NC              |

|            | FG144           | FG144      |                 | FG144      |                 |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | AGL250 Function | Pin Number | AGL250 Function | Pin Number | AGL250 Function |

| A1         | GNDQ            | D1         | IO112NDB3       | G1         | GFA1/IO108PPB3  |

| A2         | VMV0            | D2         | IO112PDB3       | G2         | GND             |

| A3         | GAB0/IO02RSB0   | D3         | IO116VDB3       | G3         | VCCPLF          |

| A4         | GAB1/IO03RSB0   | D4         | GAA2/IO118UPB3  | G4         | GFA0/IO108NPB3  |

| A5         | IO16RSB0        | D5         | GAC0/IO04RSB0   | G5         | GND             |

| A6         | GND             | D6         | GAC1/IO05RSB0   | G6         | GND             |

| A7         | IO29RSB0        | D7         | GBC0/IO35RSB0   | G7         | GND             |

| A8         | VCC             | D8         | GBC1/IO36RSB0   | G8         | GDC1/IO58UPB1   |

| A9         | IO33RSB0        | D9         | GBB2/IO42PDB1   | G9         | IO53NDB1        |

| A10        | GBA0/IO39RSB0   | D10        | IO42NDB1        | G10        | GCC2/IO53PDB1   |

| A11        | GBA1/IO40RSB0   | D11        | IO43NPB1        | G11        | IO52NDB1        |

| A12        | GNDQ            | D12        | GCB1/IO49PPB1   | G12        | GCB2/IO52PDB1   |

| B1         | GAB2/IO117UDB3  | E1         | VCC             | H1         | VCC             |

| B2         | GND             | E2         | GFC0/IO110NDB3  | H2         | GFB2/IO106PDB3  |

| B3         | GAA0/IO00RSB0   | E3         | GFC1/IO110PDB3  | H3         | GFC2/IO105PSB3  |

| B4         | GAA1/IO01RSB0   | E4         | VCCIB3          | H4         | GEC1/IO100PDB3  |

| B5         | IO14RSB0        | E5         | IO118VPB3       | H5         | VCC             |

| B6         | IO19RSB0        | E6         | VCCIB0          | H6         | IO79RSB2        |

| B7         | IO22RSB0        | E7         | VCCIB0          | H7         | IO65RSB2        |

| B8         | IO30RSB0        | E8         | GCC1/IO48PDB1   | H8         | GDB2/IO62RSB2   |

| B9         | GBB0/IO37RSB0   | E9         | VCCIB1          | H9         | GDC0/IO58VPB1   |

| B10        | GBB1/IO38RSB0   | E10        | VCC             | H10        | VCCIB1          |

| B11        | GND             | E11        | GCA0/IO50NDB1   | H11        | IO54PSB1        |

| B12        | VMV1            | E12        | IO51NDB1        | H12        | VCC             |

| C1         | IO117VDB3       | F1         | GFB0/IO109NPB3  | J1         | GEB1/IO99PDB3   |

| C2         | GFA2/IO107PPB3  | F2         | VCOMPLF         | J2         | IO106NDB3       |

| C3         | GAC2/IO116UDB3  | F3         | GFB1/IO109PPB3  | J3         | VCCIB3          |

| C4         | VCC             | F4         | IO107NPB3       | J4         | GEC0/IO100NDB3  |

| C5         | IO12RSB0        | F5         | GND             | J5         | IO88RSB2        |

| C6         | IO17RSB0        | F6         | GND             | J6         | IO81RSB2        |

| C7         | IO24RSB0        | F7         | GND             | J7         | VCC             |

| C8         | IO31RSB0        | F8         | GCC0/IO48NDB1   | J8         | ТСК             |

| C9         | IO34RSB0        | F9         | GCB0/IO49NPB1   | J9         | GDA2/IO61RSB2   |

| C10        | GBA2/IO41PDB1   | F10        | GND             | J10        | TDO             |

| C11        | IO41NDB1        | F11        | GCA1/IO50PDB1   | J11        | GDA1/IO60UDB1   |

| C12        | GBC2/IO43PPB1   | F12        | GCA2/IO51PDB1   | J12        | GDB1/IO59UDB1   |

| FG484                      |        |  |

|----------------------------|--------|--|

| Pin Number AGL400 Function |        |  |

| Y7                         | NC     |  |

| Y8                         | VCC    |  |

| Y9                         | VCC    |  |

| Y10                        | NC     |  |

| Y11                        | NC     |  |

| Y12                        | NC     |  |

| Y13                        | NC     |  |

| Y14                        | VCC    |  |

| Y15                        | VCC    |  |

| Y16                        | NC     |  |

| Y17                        | NC     |  |

| Y18                        | GND    |  |

| Y19                        | NC     |  |

| Y20                        | NC     |  |

| Y21                        | NC     |  |

| Y22                        | VCCIB1 |  |

|            | FG484           |            |

|------------|-----------------|------------|

| Pin Number | AGL600 Function | Pin Number |

| A1         | GND             | AA15       |

| A2         | GND             | AA16       |

| A3         | VCCIB0          | AA17       |

| A4         | NC              | AA18       |

| A5         | NC              | AA19       |

| A6         | IO09RSB0        | AA20       |

| A7         | IO15RSB0        | AA21       |

| A8         | NC              | AA22       |

| A9         | NC              | AB1        |

| A10        | IO22RSB0        | AB2        |

| A11        | IO23RSB0        | AB3        |

| A12        | IO29RSB0        | AB4        |

| A13        | IO35RSB0        | AB5        |

| A14        | NC              | AB6        |

| A15        | NC              | AB7        |

| A16        | IO46RSB0        | AB8        |

| A17        | IO48RSB0        | AB9        |

| A18        | NC              | AB10       |

| A19        | NC              | AB11       |

| A20        | VCCIB0          | AB12       |

| A21        | GND             | AB13       |

| A22        | GND             | AB14       |

| AA1        | GND             | AB15       |

| AA2        | VCCIB3          | AB16       |

| AA3        | NC              | AB17       |

| AA4        | NC              | AB18       |

| AA5        | NC              | AB19       |

| AA6        | IO135RSB2       | AB20       |

| AA7        | IO133RSB2       | AB21       |

| AA8        | NC              | AB22       |

| AA9        | NC              | B1         |

| AA10       | NC              | B2         |

| AA11       | NC              | B3         |

| AA12       | NC              | B4         |

| AA13       | NC              | B5         |

| AA14       | NC              | B6         |

|          | FG484           |     |

|----------|-----------------|-----|

| n Number | AGL600 Function | Pin |

| AA15     | NC              |     |

| AA16     | IO101RSB2       |     |

| AA17     | NC              |     |

| AA18     | NC              |     |

| AA19     | NC              |     |

| AA20     | NC              |     |

| AA21     | VCCIB1          |     |

| AA22     | GND             |     |

| AB1      | GND             |     |

| AB2      | GND             |     |

| AB3      | VCCIB2          |     |

| AB4      | NC              |     |

| AB5      | NC              |     |

| AB6      | IO130RSB2       |     |

| AB7      | IO128RSB2       |     |

| AB8      | IO122RSB2       |     |

| AB9      | IO116RSB2       |     |

| AB10     | NC              |     |

| AB11     | NC              |     |

| AB12     | IO113RSB2       |     |

| AB13     | IO112RSB2       |     |

| AB14     | NC              |     |

| AB15     | NC              |     |

| AB16     | IO100RSB2       |     |

| AB17     | IO95RSB2        |     |

| AB18     | NC              |     |

| AB19     | NC              |     |

| AB20     | VCCIB2          |     |

| AB21     | GND             |     |

| AB22     | GND             |     |

| B1       | GND             |     |

| B2       | VCCIB3          |     |

| B3       | NC              |     |

| B4       | NC              |     |

| B5       | NC              |     |

| B6       | IO08RSB0        |     |

| FG484      |                 |  |

|------------|-----------------|--|

| Pin Number | AGL600 Function |  |

| B7         | IO12RSB0        |  |

| B8         | NC              |  |

| B9         | NC              |  |

| B10        | IO17RSB0        |  |

| B11        | NC              |  |

| B12        | NC              |  |

| B13        | IO36RSB0        |  |

| B14        | NC              |  |

| B15        | NC              |  |

| B16        | IO47RSB0        |  |

| B17        | IO49RSB0        |  |

| B18        | NC              |  |

| B19        | NC              |  |

| B20        | NC              |  |

| B21        | VCCIB1          |  |

| B22        | GND             |  |

| C1         | VCCIB3          |  |

| C2         | NC              |  |

| C3         | NC              |  |

| C4         | NC              |  |

| C5         | GND             |  |

| C6         | NC              |  |

| C7         | NC              |  |

| C8         | VCC             |  |

| C9         | VCC             |  |

| C10        | NC              |  |

| C11        | NC              |  |

| C12        | NC              |  |

| C13        | NC              |  |

| C14        | VCC             |  |

| C15        | VCC             |  |

| C16        | NC              |  |

| C17        | NC              |  |

| C18        | GND             |  |

| C19        | NC              |  |

| C20        | NC              |  |

| FG484                       |                |  |

|-----------------------------|----------------|--|

| Pin Number AGL1000 Function |                |  |

| G5                          | IO222PDB3      |  |

| G6                          | GAC2/IO223PDB3 |  |

| G7                          | IO223NDB3      |  |

| G8                          | GNDQ           |  |

| G9                          | IO23RSB0       |  |

| G10                         | IO29RSB0       |  |

| G11                         | IO33RSB0       |  |

| G12                         | IO46RSB0       |  |

| G13                         | IO52RSB0       |  |

| G14                         | IO60RSB0       |  |

| G15                         | GNDQ           |  |

| G16                         | IO80NDB1       |  |

| G17                         | GBB2/IO79PDB1  |  |

| G18                         | IO79NDB1       |  |

| G19                         | IO82NPB1       |  |

| G20                         | IO85PDB1       |  |

| G21                         | IO85NDB1       |  |

| G22                         | NC             |  |

| H1                          | NC             |  |

| H2                          | NC             |  |

| H3                          | VCC            |  |

| H4                          | IO217PDB3      |  |

| H5                          | IO218PDB3      |  |

| H6                          | IO221NDB3      |  |

| H7                          | IO221PDB3      |  |

| H8                          | VMV0           |  |

| H9                          | VCCIB0         |  |

| H10                         | VCCIB0         |  |

| H11                         | IO38RSB0       |  |

| H12                         | IO47RSB0       |  |

| H13                         | VCCIB0         |  |

| H14                         | VCCIB0         |  |

| H15                         | VMV1           |  |

| H16                         | GBC2/IO80PDB1  |  |

| H17                         | IO83PPB1       |  |

| H18                         | IO86PPB1       |  |

Datasheet Information

| Revision    | Changes                                                                                                                                                                                                                                         | Page     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Revision 19 | The following figures were deleted (SAR 29991). Reference was made to a new application note, <i>Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs</i> , which covers these cases in detail (SAR 21770).     | N/A      |

|             | Figure 2-36 • Write Access after Write onto Same Address                                                                                                                                                                                        |          |

|             | Figure 2-37 • Read Access after Write onto Same Address                                                                                                                                                                                         |          |

|             | Figure 2-38 • Write Access after Read onto Same Address                                                                                                                                                                                         | 2-119 to |

|             | The port names in the SRAM "Timing Waveforms", SRAM "Timing Characteristics" tables, Figure 2-40 • FIFO Reset, and the FIFO "Timing Characteristics" tables were revised to ensure consistency with the software names (SARs 29991, 30510).     | 2-130    |

|             | The "Pin Descriptions" chapter has been added (SAR 21642).                                                                                                                                                                                      | 3-1      |

|             | Package names used in the "Package Pin Assignments" section were revised to match standards given in <i>Package Mechanical Drawings</i> (SAR 27395).                                                                                            | 4-1      |

|             | The "CS81" pin table for AGL250 is new (SAR 22737).                                                                                                                                                                                             | 4-5      |

|             | The CS121 pin table for AGL125 is new (SAR 22737).                                                                                                                                                                                              |          |

|             | The P3 function was revised in the "CS196" pin table for AGL250 (SAR 24800).                                                                                                                                                                    | 4-12     |

|             | The "QN132" pin table for AGL250 was added.                                                                                                                                                                                                     | 4-35,    |

|             | The "FG144" pin table for AGL060 was added (SAR 33689)                                                                                                                                                                                          | 4-42     |

| July 2010   | The versioning system for datasheets has been changed. Datasheets are assigned a revision number that increments each time the datasheet is revised. The "IGLOO Device Status" table indicates the status for each device in the device family. | N/A      |

| Revision / Version                                   | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page             |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Revision 3 (Feb 2008)<br>Product Brief rev. 2        | This document was updated to include AGL015 device information. QN68 is a<br>new package offered in the AGL015. The following sections were updated:<br>"Features and Benefits"<br>"IGLOO Ordering Information"<br>"Temperature Grade Offerings"<br>"IGLOO Devices" Product Family Table<br>Table 1 • IGLOO FPGAs Package Sizes Dimensions<br>"AGL015 and AGL030" note<br>The "Temperature Grade Offerings" table was updated to include M1AGL600.<br>In the "IGLOO Ordering Information" table, the QN package measurements were<br>updated to include both 0.4 mm and 0.5 mm. | N/A<br>IV<br>III |

|                                                      | In the "General Description" section, the number of I/Os was updated from 288 to 300.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-1              |

| Packaging v1.2                                       | The "QN68" section is new.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-25             |

| <b>Revision 2 (Jan 2008)</b><br>Packaging v1.1       | The "CS196" package and pin table was added for AGL125.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-10             |

| <b>Revision 1 (Jan 2008)</b><br>Product Brief rev. 1 | The "Low Power" section was updated to change the description of low power active FPGA operation to "from 12 $\mu$ W" from "from 25 $\mu$ W." The same update was made in the "General Description" section and the "Flash*Freeze Technology" section.                                                                                                                                                                                                                                                                                                                          | l, 1-1           |

| Revision 0 (Jan 2008)                                | This document was previously in datasheet Advance v0.7. As a result of moving to the handbook format, Actel has restarted the numbering.                                                                                                                                                                                                                                                                                                                                                                                                                                        | N/A              |

| Advance v0.7<br>(December 2007)                      | Table 1 • IGLOO Product Family, the "I/Os Per Package1" table, and the Temperature Grade Offerings table were updated to reflect the following: CS196 is now supported for AGL250; device/package support for QN132 is to be determined for AGL250; the CS281 package was added for AGL600 and AGL1000.                                                                                                                                                                                                                                                                         | i, ii, iv        |

|                                                      | Table 2 • IGLOO FPGAs Package Sizes Dimensions is new, and package sizes were removed from the "I/Os Per Package1" table.                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ii               |

|                                                      | The "I/Os Per Package1"table was updated to reflect 77 instead of 79 single-<br>ended I/Os for the VG100 package for AGL030.                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ii               |

|                                                      | The "Timing Model" was updated to be consistent with the revised timing numbers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-20             |

|                                                      | In Table 2-27 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings, $T_J$ was changed to $T_A$ in notes 1 and 2.                                                                                                                                                                                                                                                                                                                                                                            | 2-26             |

|                                                      | All AC Loading figures for single-ended I/O standards were changed from Datapaths at 35 pF to 5 pF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | N/A              |

|                                                      | The "1.2 V LVCMOS (JESD8-12A)" section is new.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-74             |

|                                                      | This document was previously in datasheet Advance v0.7. As a result of moving to the handbook format, Actel has restarted the version numbers. The new version number is Advance v0.1.                                                                                                                                                                                                                                                                                                                                                                                          | N/A              |

|                                                      | Table 2-4 • IGLOO CCC/PLL Specification and Table 2-5 • IGLOO CCC/PLL         Specification were updated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-19,<br>2-20    |