Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

E·XFI

| Product Status                 | Active                                                                       |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                            |

| Number of Logic Elements/Cells | 24576                                                                        |

| Total RAM Bits                 | 147456                                                                       |

| Number of I/O                  | 177                                                                          |

| Number of Gates                | 1000000                                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                                              |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 85°C (TA)                                                            |

| Package / Case                 | 256-LBGA                                                                     |

| Supplier Device Package        | 256-FPBGA (17x17)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1agl1000v5-fg256i |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Product Grade | Programming Cycles | Program RetentionMaximum Storage(biased/unbiased)Temperature T <sub>STG</sub> (°C) |     | Maximum Operating Junction<br>Temperature T <sub>J</sub> (°C) <sup>2</sup> |  |

|---------------|--------------------|------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------|--|

| Commercial    | 500                | 20 years                                                                           | 110 | 100                                                                        |  |

| Industrial    | 500                | 20 years                                                                           | 110 | 100                                                                        |  |

Table 2-3 • Flash Programming Limits – Retention, Storage, and Operating Temperature<sup>1</sup>

Notes:

1. This is a stress rating only; functional operation at any condition other than those indicated is not implied.

2. These limits apply for program/data retention only. Refer to Table 2-1 on page 2-1 and Table 2-2 on page 2-2 for device operating conditions and absolute limits.

### Table 2-4 • Overshoot and Undershoot Limits<sup>1</sup>

| VCCI          | Average VCCI–GND Overshoot or Undershoot Duration<br>as a Percentage of Clock Cycle <sup>2</sup> | Maximum Overshoot/<br>Undershoot <sup>2</sup> |

|---------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2.7 V or less | 10%                                                                                              | 1.4 V                                         |

| F             | 5%                                                                                               | 1.49 V                                        |

| 3 V           | 10%                                                                                              | 1.1 V                                         |

| F             | 5%                                                                                               | 1.19 V                                        |

| 3.3 V         | 10%                                                                                              | 0.79 V                                        |

| F             | 5%                                                                                               | 0.88 V                                        |

| 3.6 V         | 10%                                                                                              | 0.45 V                                        |

| F             | 5%                                                                                               | 0.54 V                                        |

Notes:

1. Based on reliability requirements at junction temperature at 85°C.

2. The duration is allowed at one out of six clock cycles. If the overshoot/undershoot occurs at one out of two cycles, the maximum overshoot/undershoot has to be reduced by 0.15 V.

3. This table does not provide PCI overshoot/undershoot limits.

# I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)

Sophisticated power-up management circuitry is designed into every IGLOO device. These circuits ensure easy transition from the powered-off state to the powered-up state of the device. The many different supplies can power up in any sequence with minimized current spikes or surges. In addition, the I/O will be in a known state through the power-up sequence. The basic principle is shown in Figure 2-1 on page 2-4 and Figure 2-2 on page 2-5.

There are five regions to consider during power-up.

IGLOO I/Os are activated only if ALL of the following three conditions are met:

- 1. VCC and VCCI are above the minimum specified trip points (Figure 2-1 on page 2-4 and Figure 2-2 on page 2-5).

- 2. VCCI > VCC 0.75 V (typical)

- 3. Chip is in the operating mode.

### VCCI Trip Point:

Ramping up (V5 devices): 0.6 V < trip\_point\_up < 1.2 V Ramping down (V5 Devices): 0.5 V < trip\_point\_down < 1.1 V Ramping up (V2 devices): 0.75 V < trip\_point\_up < 1.05 V Ramping down (V2 devices): 0.65 V < trip\_point\_down < 0.95 V

### VCC Trip Point:

Ramping up (V5 devices): 0.6 V < trip\_point\_up < 1.1 V Ramping down (V5 devices): 0.5 V < trip\_point\_down < 1.0 V

## Table 2-65 • Minimum and Maximum DC Input and Output Levels for LVCMOS 3.3 V Wide Range Applicable to Standard I/O Banks

| 3.3 V LVCMO       | S Wide Range                                                               | V         | IL        | V         | /IH       | VOL       | VOH       | IOL | IOH | IOSL                    | IOSH                    | IIL <sup>2</sup>        | IIH <sup>3</sup>        |

|-------------------|----------------------------------------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----|-----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Equivalent<br>Software<br>Default Drive<br>Strength<br>Option <sup>1</sup> | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | μΑ  | μΑ  | Max.<br>mA <sup>4</sup> | Max.<br>mA <sup>4</sup> | μ <b>Α</b> <sup>5</sup> | μ <b>Α</b> <sup>5</sup> |

| 100 µA            | 2 mA                                                                       | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD - 0.2 | 100 | 100 | 25                      | 27                      | 10                      | 10                      |

| 100 µA            | 4 mA                                                                       | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD - 0.2 | 100 | 100 | 25                      | 27                      | 10                      | 10                      |

| 100 µA            | 6 mA                                                                       | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 51                      | 54                      | 10                      | 10                      |

| 100 µA            | 8 mA                                                                       | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD - 0.2 | 100 | 100 | 51                      | 54                      | 10                      | 10                      |

Notes:

1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ± 100 μA. Drive strengths displayed in software are supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

3. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

4. Currents are measured at 100°C junction temperature and maximum voltage.

5. Currents are measured at 85°C junction temperature.

6. Software default selection highlighted in gray.

### Table 2-66 • 3.3 V LVCMOS Wide Range AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 3.3            | 1.4                  | 5                      |

Note: \*Measuring point = Vtrip. See Table 2-29 on page 2-28 for a complete table of trip points.

| DC Parameter        | Description                 | Min.  | Тур.  | Max.  | Units |

|---------------------|-----------------------------|-------|-------|-------|-------|

| VCCI                | Supply Voltage              | 2.375 | 2.5   | 2.625 | V     |

| VOL                 | Output Low Voltage          | 0.9   | 1.075 | 1.25  | V     |

| VOH                 | Output High Voltage         | 1.25  | 1.425 | 1.6   | V     |

| IOL <sup>1</sup>    | Output Lower Current        | 0.65  | 0.91  | 1.16  | mA    |

| IOH <sup>1</sup>    | Output High Current         | 0.65  | 0.91  | 1.16  | mA    |

| VI                  | Input Voltage               | 0     |       | 2.925 | V     |

| IIH <sup>2</sup>    | Input High Leakage Current  |       |       | 10    | μA    |

| IIL <sup>2</sup>    | Input Low Leakage Current   |       |       | 10    | μA    |

| VODIFF              | Differential Output Voltage | 250   | 350   | 450   | mV    |

| VOCM                | Output Common-Mode Voltage  | 1.125 | 1.25  | 1.375 | V     |

| VICM                | Input Common-Mode Voltage   | 0.05  | 1.25  | 2.35  | V     |

| VIDIFF <sup>4</sup> | Input Differential Voltage  | 100   | 350   |       | mV    |

### Table 2-147 • Minimum and Maximum DC Input and Output Levels

Notes:

1. IOL/IOH is defined by VODIFF/(resistor network)

2. Currents are measured at 85°C junction temperature.

### Table 2-148 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) |

|---------------|----------------|----------------------|

| 1.075         | 1.325          | Cross point          |

*Note:* \**Measuring point = Vtrip. See Table 2-29 on page 2-28 for a complete table of trip points.*

### **Timing Characteristics**

### 1.5 V DC Core Voltage

### Table 2-149 • LVDS – Applies to 1.5 V DC Core Voltage

### Commercial-Case Conditions: $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V Applicable to Standard Banks

| Speed Grade | <sup>t</sup> dout | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.97              | 1.67            | 0.19             | 1.31            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 and Table 2-7 on page 2-7 for derating values.

### 1.2 V DC Core Voltage

### Table 2-150 • LVDS – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.3 V Applicable to Standard Banks

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 1.55              | 2.19            | 0.25             | 1.52            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 and Table 2-7 on page 2-7 for derating values.

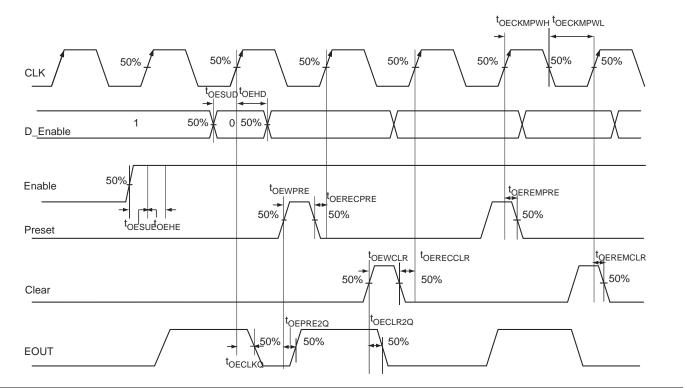

### **Output Enable Register**

### Figure 2-20 • Output Enable Register Timing Diagram

### **Timing Characteristics**

### 1.5 V DC Core Voltage

## Table 2-161 • Output Enable Register Propagation DelaysCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                            | Std. | Units |

|-----------------------|------------------------------------------------------------------------|------|-------|

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                               | 0.75 | ns    |

| tOESUD                | Data Setup Time for the Output Enable Register                         | 0.51 | ns    |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                          | 0.00 | ns    |

| tOESUE                | Enable Setup Time for the Output Enable Register                       | 0.73 | ns    |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                        | 0.00 | ns    |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register                  | 1.13 | ns    |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register                 | 1.13 | ns    |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register         | 0.00 | ns    |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register        | 0.24 | ns    |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register        | 0.00 | ns    |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register       | 0.24 | ns    |

| t <sub>OEWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Output Enable Register  | 0.19 | ns    |

| t <sub>OEWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Enable Register | 0.19 | ns    |

| t <sub>OECKMPWH</sub> | Clock Minimum Pulse Width High for the Output Enable Register          | 0.31 | ns    |

| t <sub>OECKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Enable Register           | 0.28 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

### **Timing Characteristics**

### 1.5 V DC Core Voltage

## Table 2-169 • Combinatorial Cell Propagation Delays Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Combinatorial Cell | Equation                  | Parameter       | Std. | Units |

|--------------------|---------------------------|-----------------|------|-------|

| INV                | Y =!A                     | t <sub>PD</sub> | 0.80 | ns    |

| AND2               | $Y=A\cdotB$               | t <sub>PD</sub> | 0.84 | ns    |

| NAND2              | Y =!(A · B)               | t <sub>PD</sub> | 0.90 | ns    |

| OR2                | Y = A + B                 | t <sub>PD</sub> | 1.19 | ns    |

| NOR2               | Y = !(A + B)              | t <sub>PD</sub> | 1.10 | ns    |

| XOR2               | Y = A ⊕ B                 | t <sub>PD</sub> | 1.37 | ns    |

| MAJ3               | Y = MAJ(A, B, C)          | t <sub>PD</sub> | 1.33 | ns    |

| XOR3               | $Y = A \oplus B \oplus C$ | t <sub>PD</sub> | 1.79 | ns    |

| MUX2               | Y = A !S + B S            | t <sub>PD</sub> | 1.48 | ns    |

| AND3               | $Y = A \cdot B \cdot C$   | t <sub>PD</sub> | 1.21 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

### 1.2 V DC Core Voltage

### Table 2-170 • Combinatorial Cell Propagation Delays Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Combinatorial Cell | Equation                  | Parameter       | Std. | Units |

|--------------------|---------------------------|-----------------|------|-------|

| INV                | Y = !A                    | t <sub>PD</sub> | 1.34 | ns    |

| AND2               | $Y = A \cdot B$           | t <sub>PD</sub> | 1.43 | ns    |

| NAND2              | $Y = !(A \cdot B)$        | t <sub>PD</sub> | 1.59 | ns    |

| OR2                | Y = A + B                 | t <sub>PD</sub> | 2.30 | ns    |

| NOR2               | Y = !(A + B)              | t <sub>PD</sub> | 2.07 | ns    |

| XOR2               | Y = A ⊕ B                 | t <sub>PD</sub> | 2.46 | ns    |

| MAJ3               | Y = MAJ(A, B, C)          | t <sub>PD</sub> | 2.46 | ns    |

| XOR3               | $Y = A \oplus B \oplus C$ | t <sub>PD</sub> | 3.12 | ns    |

| MUX2               | Y = A !S + B S            | t <sub>PD</sub> | 2.83 | ns    |

| AND3               | $Y = A \cdot B \cdot C$   | t <sub>PD</sub> | 2.28 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

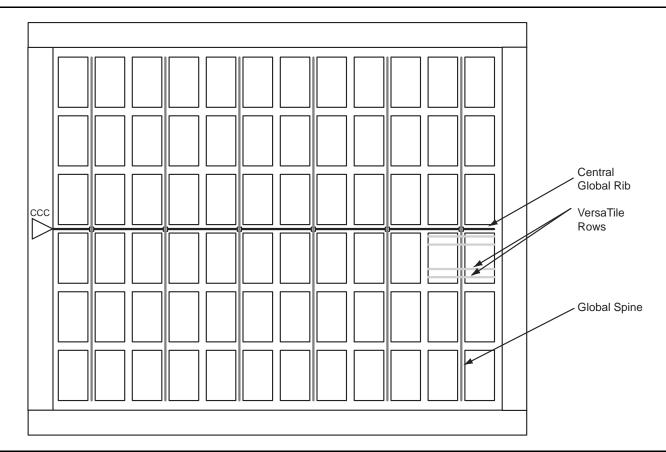

## **Global Resource Characteristics**

## AGL250 Clock Tree Topology

Clock delays are device-specific. Figure 2-29 is an example of a global tree used for clock routing. The global tree presented in Figure 2-29 is driven by a CCC located on the west side of the AGL250 device. It is used to drive all D-flip-flops in the device.

Figure 2-29 • Example of Global Tree Use in an AGL250 Device for Clock Routing

### Table 2-175 • AGL060 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | Si                | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.33              | 1.55              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.35              | 1.62              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.18              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.15              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.27              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

### Table 2-176 • AGL125 Global Resource

### Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.36              | 1.71              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.39              | 1.82              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.18              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.15              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.43              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

The Flash\*Freeze pin can be used with any single-ended I/O standard supported by the I/O bank in which the pin is located, and input signal levels compatible with the I/O standard selected. The FF pin should be treated as a sensitive asynchronous signal. When defining pin placement and board layout, simultaneously switching outputs (SSOs) and their effects on sensitive asynchronous pins must be considered.

Unused FF or I/O pins are tristated with weak pull-up. This default configuration applies to both Flash\*Freeze mode and normal operation mode. No user intervention is required.

Table 3-1 shows the Flash\*Freeze pin location on the available packages for IGLOO a devices. The Flash\*Freeze pin location is independent of device, allowing migration to larger or smaller IGLOO devices while maintaining the same pin location on the board. Refer to the "Flash\*Freeze Technology and Low Power Modes" chapter of the *IGLOO FPGA Fabric User Guide* for more information on I/O states during Flash\*Freeze mode.

#### Table 3-1 • Flash\*Freeze Pin Location in IGLOO Family Packages (device-independent)

| IGLOO Packages | Flash*Freeze Pin |

|----------------|------------------|

| CS81/UC81      | H2               |

| CS121          | J5               |

| CS196          | P3               |

| CS281          | W2               |

| QN48           | 14               |

| QN68           | 18               |

| QN132          | B12              |

| VQ100          | 27               |

| FG144          | L3               |

| FG256          | Т3               |

| FG484          | W6               |

IGLOO Low Power Flash FPGAs

|            | CS121           |            | CS121           |            | CS121           |  |  |

|------------|-----------------|------------|-----------------|------------|-----------------|--|--|

| Pin Number | AGL060 Function | Pin Number | AGL060 Function | Pin Number | AGL060 Function |  |  |

| A1         | GNDQ            | D4         | IO10RSB0        | G7         | VCC             |  |  |

| A2         | IO01RSB0        | D5         | IO11RSB0        | G8         | GDC0/IO46RSB0   |  |  |

| A3         | GAA1/IO03RSB0   | D6         | IO18RSB0        | G9         | GDA1/IO49RSB0   |  |  |

| A4         | GAC1/IO07RSB0   | D7         | IO32RSB0        | G10        | GDB0/IO48RSB0   |  |  |

| A5         | IO15RSB0        | D8         | IO31RSB0        | G11        | GCA0/IO40RSB0   |  |  |

| A6         | IO13RSB0        | D9         | GCA2/IO41RSB0   | H1         | IO75RSB1        |  |  |

| A7         | IO17RSB0        | D10        | IO30RSB0        | H2         | IO76RSB1        |  |  |

| A8         | GBB1/IO22RSB0   | D11        | IO33RSB0        | H3         | GFC2/IO78RSB1   |  |  |

| A9         | GBA1/IO24RSB0   | E1         | IO87RSB1        | H4         | GFA2/IO80RSB1   |  |  |

| A10        | GNDQ            | E2         | GFC0/IO85RSB1   | H5         | IO77RSB1        |  |  |

| A11        | VMV0            | E3         | IO92RSB1        | H6         | GEC2/IO66RSB1   |  |  |

| B1         | GAA2/IO95RSB1   | E4         | IO94RSB1        | H7         | IO54RSB1        |  |  |

| B2         | IO00RSB0        | E5         | VCC             | H8         | GDC2/IO53RSB1   |  |  |

| B3         | GAA0/IO02RSB0   | E6         | VCCIB0          | H9         | VJTAG           |  |  |

| B4         | GAC0/IO06RSB0   | E7         | GND             | H10        | TRST            |  |  |

| B5         | IO08RSB0        | E8         | GCC0/IO36RSB0   | H11        | IO44RSB0        |  |  |

| B6         | IO12RSB0        | E9         | IO34RSB0        | J1         | GEC1/IO74RSB1   |  |  |

| B7         | IO16RSB0        | E10        | GCB1/IO37RSB0   | J2         | GEC0/IO73RSB1   |  |  |

| B8         | GBC1/IO20RSB0   | E11        | GCC1/IO35RSB0   | J3         | GEB1/IO72RSB1   |  |  |

| B9         | GBB0/IO21RSB0   | F1*        | VCOMPLF         | J4         | GEA0/IO69RSB1   |  |  |

| B10        | GBB2/IO27RSB0   | F2         | GFB0/IO83RSB1   | J5         | FF/GEB2/IO67RSB |  |  |

| B11        | GBA2/IO25RSB0   | F3         | GFA0/IO82RSB1   | J6         | IO62RSB1        |  |  |

| C1         | IO89RSB1        | F4         | GFC1/IO86RSB1   | J7         | GDA2/IO51RSB1   |  |  |

| C2         | GAC2/IO91RSB1   | F5         | VCCIB1          | J8         | GDB2/IO52RSB1   |  |  |

| C3         | GAB1/IO05RSB0   | F6         | VCC             | J9         | TDI             |  |  |

| C4         | GAB0/IO04RSB0   | F7         | VCCIB0          | J10        | TDO             |  |  |

| C5         | IO09RSB0        | F8         | GCB2/IO42RSB0   | J11        | GDC1/IO45RSB0   |  |  |

| C6         | IO14RSB0        | F9         | GCC2/IO43RSB0   | K1         | GEB0/IO71RSB1   |  |  |

| C7         | GBA0/IO23RSB0   | F10        | GCB0/IO38RSB0   | K2         | GEA1/IO70RSB1   |  |  |

| C8         | GBC0/IO19RSB0   | F11        | GCA1/IO39RSB0   | K3         | GEA2/IO68RSB1   |  |  |

| C9         | IO26RSB0        | G1*        | VCCPLF          | K4         | IO64RSB1        |  |  |

| C10        | IO28RSB0        | G2         | GFB2/IO79RSB1   | K5         | IO60RSB1        |  |  |

| C11        | GBC2/IO29RSB0   | G3         | GFA1/IO81RSB1   | K6         | IO59RSB1        |  |  |

| D1         | IO88RSB1        | G4         | GFB1/IO84RSB1   | K7         | IO56RSB1        |  |  |

| D2         | IO90RSB1        | G5         | GND             | K8         | ТСК             |  |  |

| D3         | GAB2/IO93RSB1   | G6         | VCCIB1          | К9         | TMS             |  |  |

Note: \*Pin numbers F1 and G1 must be connected to ground because a PLL is not supported for AGL060-CS/G121.

Package Pin Assignments

|            | CS281            | CS281      |                  |  |

|------------|------------------|------------|------------------|--|

| Pin Number | AGL1000 Function | Pin Number | AGL1000 Function |  |

| R15        | IO122RSB2        | V10        | IO145RSB2        |  |

| R16        | GDA1/IO113PPB1   | V11        | IO144RSB2        |  |

| R18        | GDB0/IO112NPB1   | V12        | IO134RSB2        |  |

| R19        | GDC0/IO111NPB1   | V13        | IO133RSB2        |  |

| T1         | IO197PPB3        | V14        | GND              |  |

| T2         | GEC0/IO190NPB3   | V15        | IO119RSB2        |  |

| T4         | GEB0/IO189NPB3   | V16        | GDA2/IO114RSB    |  |

| T5         | IO181RSB2        | V17        | TDI              |  |

| T6         | IO172RSB2        | V18        | VCCIB2           |  |

| T7         | IO171RSB2        | V19        | TDO              |  |

| T8         | IO156RSB2        | W1         | GND              |  |

| Т9         | IO159RSB2        | W2         | FF/GEB2/IO186RS  |  |

| T10        | GND              | W3         | IO183RSB2        |  |

| T11        | IO139RSB2        | W4         | IO176RSB2        |  |

| T12        | IO138RSB2        | W5         | IO170RSB2        |  |

| T13        | IO129RSB2        | W6         | IO162RSB2        |  |

| T14        | IO123RSB2        | W7         | IO157RSB2        |  |

| T15        | GDC2/IO116RSB2   | W8         | IO152RSB2        |  |

| T16        | TMS              | W9         | IO149RSB2        |  |

| T18        | VJTAG            | W10        | VCCIB2           |  |

| T19        | GDB1/IO112PPB1   | W11        | IO140RSB2        |  |

| U1         | IO193PDB3        | W12        | IO135RSB2        |  |

| U2         | GEA1/IO188PPB3   | W13        | IO130RSB2        |  |

| U6         | IO167RSB2        | W14        | IO125RSB2        |  |

| U14        | IO128RSB2        | W15        | IO120RSB2        |  |

| U18        | TRST             | W16        | IO118RSB2        |  |

| U19        | GDA0/IO113NPB1   | W17        | GDB2/IO115RSB    |  |

| V1         | IO193NDB3        | W18        | ТСК              |  |

| V2         | VCCIB3           | W19        | GND              |  |

| V3         | GEC2/IO185RSB2   |            |                  |  |

| V4         | IO182RSB2        |            |                  |  |

| V5         | IO175RSB2        |            |                  |  |

| V6         | GND              |            |                  |  |

| V7         | IO161RSB2        |            |                  |  |

| V8         | IO143RSB2        |            |                  |  |

|            |                  |            |                  |  |

V9

IO146RSB2

Package Pin Assignments

| QN48       |                 |  |  |  |

|------------|-----------------|--|--|--|

| Pin Number | AGL030 Function |  |  |  |

| 1          | IO82RSB1        |  |  |  |

| 2          | GEC0/IO73RSB1   |  |  |  |

| 3          | GEA0/IO72RSB1   |  |  |  |

| 4          | GEB0/IO71RSB1   |  |  |  |

| 5          | GND             |  |  |  |

| 6          | VCCIB1          |  |  |  |

| 7          | IO68RSB1        |  |  |  |

| 8          | IO67RSB1        |  |  |  |

| 9          | IO66RSB1        |  |  |  |

| 10         | IO65RSB1        |  |  |  |

| 11         | IO64RSB1        |  |  |  |

| 12         | IO62RSB1        |  |  |  |

| 13         | IO61RSB1        |  |  |  |

| 14         | FF/IO60RSB1     |  |  |  |

| 15         | IO57RSB1        |  |  |  |

| 16         | IO55RSB1        |  |  |  |

| 17         | IO53RSB1        |  |  |  |

| 18         | VCC             |  |  |  |

| 19         | VCCIB1          |  |  |  |

| 20         | IO46RSB1        |  |  |  |

| 21         | IO42RSB1        |  |  |  |

| 22         | ТСК             |  |  |  |

| 23         | TDI             |  |  |  |

| 24         | TMS             |  |  |  |

| 25         | VPUMP           |  |  |  |

| 26         | TDO             |  |  |  |

| 27         | TRST            |  |  |  |

| 28         | VJTAG           |  |  |  |

| 29         | IO38RSB0        |  |  |  |

| 30         | GDB0/IO34RSB0   |  |  |  |

| 31         | GDA0/IO33RSB0   |  |  |  |

| 32         | GDC0/IO32RSB0   |  |  |  |

| 33         | VCCIB0          |  |  |  |

| 34         | GND             |  |  |  |

| 35         | VCC             |  |  |  |

| 36         | IO25RSB0        |  |  |  |

| QN48       |                 |  |  |  |

|------------|-----------------|--|--|--|

| Pin Number | AGL030 Function |  |  |  |

| 37         | IO24RSB0        |  |  |  |

| 38         | IO22RSB0        |  |  |  |

| 39         | IO20RSB0        |  |  |  |

| 40         | IO18RSB0        |  |  |  |

| 41         | IO16RSB0        |  |  |  |

| 42         | IO14RSB0        |  |  |  |

| 43         | IO10RSB0        |  |  |  |

| 44         | IO08RSB0        |  |  |  |

| 45         | IO06RSB0        |  |  |  |

| 46         | IO04RSB0        |  |  |  |

| 47         | IO02RSB0        |  |  |  |

| 48         | IO00RSB0        |  |  |  |

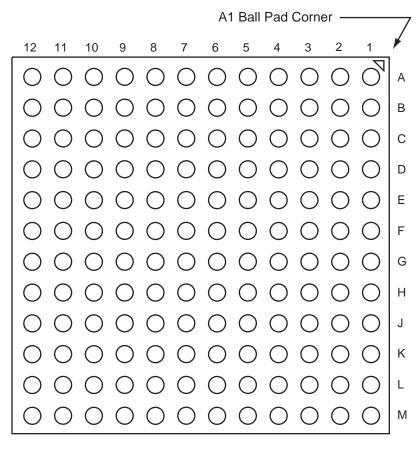

## FG144

Note: This is the bottom view of the package.

### Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

IGLOO Low Power Flash FPGAs

| FG144      |                 | FG144      |                 | FG144      |                 |  |

|------------|-----------------|------------|-----------------|------------|-----------------|--|

| Pin Number | AGL250 Function | Pin Number | AGL250 Function | Pin Number | AGL250 Function |  |

| A1         | GNDQ            | D1         | IO112NDB3       | G1         | GFA1/IO108PPB3  |  |

| A2         | VMV0            | D2         | IO112PDB3       | G2         | GND             |  |

| A3         | GAB0/IO02RSB0   | D3         | IO116VDB3       | G3         | VCCPLF          |  |

| A4         | GAB1/IO03RSB0   | D4         | GAA2/IO118UPB3  | G4         | GFA0/IO108NPB3  |  |

| A5         | IO16RSB0        | D5         | GAC0/IO04RSB0   | G5         | GND             |  |

| A6         | GND             | D6         | GAC1/IO05RSB0   | G6         | GND             |  |

| A7         | IO29RSB0        | D7         | GBC0/IO35RSB0   | G7         | GND             |  |

| A8         | VCC             | D8         | GBC1/IO36RSB0   | G8         | GDC1/IO58UPB1   |  |

| A9         | IO33RSB0        | D9         | GBB2/IO42PDB1   | G9         | IO53NDB1        |  |

| A10        | GBA0/IO39RSB0   | D10        | IO42NDB1        | G10        | GCC2/IO53PDB1   |  |

| A11        | GBA1/IO40RSB0   | D11        | IO43NPB1        | G11        | IO52NDB1        |  |

| A12        | GNDQ            | D12        | GCB1/IO49PPB1   | G12        | GCB2/IO52PDB1   |  |

| B1         | GAB2/IO117UDB3  | E1         | VCC             | H1         | VCC             |  |

| B2         | GND             | E2         | GFC0/IO110NDB3  | H2         | GFB2/IO106PDB3  |  |

| B3         | GAA0/IO00RSB0   | E3         | GFC1/IO110PDB3  | H3         | GFC2/IO105PSB3  |  |

| B4         | GAA1/IO01RSB0   | E4         | VCCIB3          | H4         | GEC1/IO100PDB3  |  |

| B5         | IO14RSB0        | E5         | IO118VPB3       | H5         | VCC             |  |

| B6         | IO19RSB0        | E6         | VCCIB0          | H6         | IO79RSB2        |  |

| B7         | IO22RSB0        | E7         | VCCIB0          | H7         | IO65RSB2        |  |

| B8         | IO30RSB0        | E8         | GCC1/IO48PDB1   | H8         | GDB2/IO62RSB2   |  |

| B9         | GBB0/IO37RSB0   | E9         | VCCIB1          | H9         | GDC0/IO58VPB1   |  |

| B10        | GBB1/IO38RSB0   | E10        | VCC             | H10        | VCCIB1          |  |

| B11        | GND             | E11        | GCA0/IO50NDB1   | H11        | IO54PSB1        |  |

| B12        | VMV1            | E12        | IO51NDB1        | H12        | VCC             |  |

| C1         | IO117VDB3       | F1         | GFB0/IO109NPB3  | J1         | GEB1/IO99PDB3   |  |

| C2         | GFA2/IO107PPB3  | F2         | VCOMPLF         | J2         | IO106NDB3       |  |

| C3         | GAC2/IO116UDB3  | F3         | GFB1/IO109PPB3  | J3         | VCCIB3          |  |

| C4         | VCC             | F4         | IO107NPB3       | J4         | GEC0/IO100NDB3  |  |

| C5         | IO12RSB0        | F5         | GND             | J5         | IO88RSB2        |  |

| C6         | IO17RSB0        | F6         | GND             | J6         | IO81RSB2        |  |

| C7         | IO24RSB0        | F7         | GND             | J7         | VCC             |  |

| C8         | IO31RSB0        | F8         | GCC0/IO48NDB1   | J8         | ТСК             |  |

| C9         | IO34RSB0        | F9         | GCB0/IO49NPB1   | J9         | GDA2/IO61RSB2   |  |

| C10        | GBA2/IO41PDB1   | F10        | GND             | J10        | TDO             |  |

| C11        | IO41NDB1        | F11        | GCA1/IO50PDB1   | J11        | GDA1/IO60UDB1   |  |

| C12        | GBC2/IO43PPB1   | F12        | GCA2/IO51PDB1   | J12        | GDB1/IO59UDB1   |  |

| Pin NumberAGL400 FunctionAA15NCAA16NCAA17NCAA18NCAA19NCAA20NCAA21VCCIB1AA22GNDAB1GND | _ |

|--------------------------------------------------------------------------------------|---|

| AA16NCAA17NCAA18NCAA19NCAA20NCAA21VCCIB1AA22GNDAB1GND                                |   |

| AA17NCAA18NCAA19NCAA20NCAA21VCCIB1AA22GNDAB1GND                                      |   |

| AA18NCAA19NCAA20NCAA21VCCIB1AA22GNDAB1GND                                            |   |

| AA19NCAA20NCAA21VCCIB1AA22GNDAB1GND                                                  |   |

| AA20 NC<br>AA21 VCCIB1<br>AA22 GND<br>AB1 GND                                        |   |

| AA21 VCCIB1<br>AA22 GND<br>AB1 GND                                                   |   |

| AA22 GND<br>AB1 GND                                                                  |   |

| AB1 GND                                                                              |   |

|                                                                                      |   |

| AB2 GND                                                                              |   |

|                                                                                      |   |

| AB3 VCCIB2                                                                           |   |

| AB4 NC                                                                               |   |

| AB5 NC                                                                               |   |

| AB6 IO121RSB2                                                                        |   |

| AB7 IO119RSB2                                                                        |   |

| AB8 IO114RSB2                                                                        |   |

| AB9 IO109RSB2                                                                        |   |

| AB10 NC                                                                              |   |

| AB11 NC                                                                              |   |

| AB12 IO104RSB2                                                                       |   |

| AB13 IO103RSB2                                                                       |   |

| AB14 NC                                                                              |   |

| AB15 NC                                                                              |   |

| AB16 IO91RSB2                                                                        |   |

| AB17 IO90RSB2                                                                        |   |

| AB18 NC                                                                              |   |

| AB19 NC                                                                              |   |

| AB20 VCCIB2                                                                          |   |

| AB21 GND                                                                             |   |

| AB22 GND                                                                             |   |

| B1 GND                                                                               |   |

| B2 VCCIB3                                                                            |   |

| B3 NC                                                                                |   |

| B4 NC                                                                                |   |

| B5 NC                                                                                |   |

| B6 NC                                                                                |   |

| FG484      |                 |  |  |

|------------|-----------------|--|--|

| Pin Number | AGL600 Function |  |  |

| N17        | IO80NPB1        |  |  |

| N18        | IO74NPB1        |  |  |

| N19        | IO72NDB1        |  |  |

| N20        | NC              |  |  |

| N21        | IO79NPB1        |  |  |

| N22        | NC              |  |  |

| P1         | NC              |  |  |

| P2         | IO153PDB3       |  |  |

| P3         | IO153NDB3       |  |  |

| P4         | IO159NDB3       |  |  |

| P5         | IO156NPB3       |  |  |

| P6         | IO151PPB3       |  |  |

| P7         | IO158PPB3       |  |  |

| P8         | VCCIB3          |  |  |

| P9         | GND             |  |  |

| P10        | VCC             |  |  |

| P11        | VCC             |  |  |

| P12        | VCC             |  |  |

| P13        | VCC             |  |  |

| P14        | GND             |  |  |

| P15        | VCCIB1          |  |  |

| P16        | GDB0/IO87NPB1   |  |  |

| P17        | IO85NDB1        |  |  |

| P18        | IO85PDB1        |  |  |

| P19        | IO84PDB1        |  |  |

| P20        | NC              |  |  |

| P21        | IO81PDB1        |  |  |

| P22        | NC              |  |  |

| R1         | NC              |  |  |

| R2         | NC              |  |  |

| R3         | VCC             |  |  |

| R4         | IO150PDB3       |  |  |

| R5         | IO151NPB3       |  |  |

| R6         | IO147NPB3       |  |  |

| R7         | GEC0/IO146NPB3  |  |  |

|            |                 |  |  |

| FG484      |                  |  |  |  |

|------------|------------------|--|--|--|

| Pin Number | AGL1000 Function |  |  |  |

| A1         | GND              |  |  |  |

| A2         | GND              |  |  |  |

| A3         | VCCIB0           |  |  |  |

| A4         | IO07RSB0         |  |  |  |

| A5         | IO09RSB0         |  |  |  |

| A6         | IO13RSB0         |  |  |  |

| A7         | IO18RSB0         |  |  |  |

| A8         | IO20RSB0         |  |  |  |

| A9         | IO26RSB0         |  |  |  |

| A10        | IO32RSB0         |  |  |  |

| A11        | IO40RSB0         |  |  |  |

| A12        | IO41RSB0         |  |  |  |

| A13        | IO53RSB0         |  |  |  |

| A14        | IO59RSB0         |  |  |  |

| A15        | IO64RSB0         |  |  |  |

| A16        | IO65RSB0         |  |  |  |

| A17        | IO67RSB0         |  |  |  |

| A18        | IO69RSB0         |  |  |  |

| A19        | NC               |  |  |  |

| A20        | VCCIB0           |  |  |  |

| A21        | GND              |  |  |  |

| A22        | GND              |  |  |  |

| AA1        | GND              |  |  |  |

| AA2        | VCCIB3           |  |  |  |

| AA3        | NC               |  |  |  |

| AA4        | IO181RSB2        |  |  |  |

| AA5        | IO178RSB2        |  |  |  |

| AA6        | IO175RSB2        |  |  |  |

| AA7        | IO169RSB2        |  |  |  |

| AA8        | IO166RSB2        |  |  |  |

| AA9        | IO160RSB2        |  |  |  |

| AA10       | IO152RSB2        |  |  |  |

| AA11       | IO146RSB2        |  |  |  |

| AA12       | IO139RSB2        |  |  |  |

| AA13       | IO133RSB2        |  |  |  |

| AA14       | NC               |  |  |  |

Datasheet Information

| Revision                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                            |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Revision 21<br>(continued)      | Pin description table for AGL125 CS121 was removed as it was incorrectly added to the datasheet in revision 19 (SAR 38217).                                                                                                                                                                                                                                                                                                                   | -                                               |

| Revision 20<br>(March 2012)     | Notes indicating that AGL015 is not recommended for new designs have been added.<br>The "Devices Not Recommended For New Designs" section is new (SAR 35015).                                                                                                                                                                                                                                                                                 | I to IV                                         |

|                                 | Notes indicating that device/package support is TBD for AGL250-QN132 and AGL060-FG144 have been reinserted (SAR 33689).                                                                                                                                                                                                                                                                                                                       | I to IV                                         |

|                                 | Values for the power data for PAC1, PAC2, PAC3, PAC4, PAC7, and PAC8 were revised in Table 2-19 • Different Components Contributing to Dynamic Power Consumption in IGLOO Devices and Table 2-21 • Different Components Contributing to Dynamic Power Consumption in IGLOO Devices to match the SmartPower tool in Libero software version 9.0 SP1 and Power Calculator spreadsheet v7a released on 08/10/2010 (SAR 33768).                   | 2-15                                            |

|                                 | The reference to guidelines for global spines and VersaTile rows, given in the "Global Clock Contribution—PCLOCK" section, was corrected to the "Spine Architecture" section of the Global Resources chapter in the <i>IGLOO FPGA Fabric User Guide</i> (SAR 34730).                                                                                                                                                                          |                                                 |

|                                 | Figure 2-4 • Input Buffer Timing Model and Delays (example) has been modified for the DIN waveform; the Rise and Fall time label has been changed to t <sub>DIN</sub> (SAR 37104).                                                                                                                                                                                                                                                            | 2-21                                            |

|                                 | <ul> <li>Added missing characteristics for 3.3 V LVCMOS, 3.3 V LVCMOS Wide range, 1.2 V LVCMOS, and 1.2 V LVCMOS Wide range to the following tables:</li> <li>Table 2-38, Table 2-39, Table 2-40, Table 2-42, Table 2-43, and Table 2-44 (SARs 33854 and 36891)</li> <li>Table 2-63, Table 2-64, and Table 2-65 (SAR 33854)</li> <li>Table 2-127, Table 2-128, Table 2-129, Table 2-137, Table 2-138, and Table 2-139 (SAR 36891).</li> </ul> | 2-40,<br>2-47 to<br>2-49,<br>2-74,<br>2-77, and |

|                                 | AC Loading figures in the "Single-Ended I/O Characteristics" section were updated to match Table 2-50 · AC Waveforms, Measuring Points, and Capacitive Loads (SAR 34878).                                                                                                                                                                                                                                                                     |                                                 |

|                                 | Added values for minimum pulse width and removed the FRMAX row from Table 2-173 through Table 2-188 in the "Global Tree Timing Characteristics" section. Use the software to determine the FRMAX for the device you are using (SAR 29271).                                                                                                                                                                                                    |                                                 |

| Revision 19<br>(September 2011) | CS121 was added to the product tables in the "IGLOO Low Power Flash FPGAs" section for AGL125 (SAR 22737). CS81 was added for AGL250 (SAR 22737).                                                                                                                                                                                                                                                                                             | I                                               |

|                                 | Notes indicating that device/package support is TBD for AGL250-QN132 and AGL060-FG144 have been removed (SAR 33689).                                                                                                                                                                                                                                                                                                                          | I to IV                                         |

|                                 | M1AGL400 was removed from the "I/Os Per Package1" table. This device was discontinued in April 2009 (SAR 32450).                                                                                                                                                                                                                                                                                                                              | II                                              |

|                                 | Dimensions for the QN48 package were added to Table 1 • IGLOO FPGAs Package Sizes Dimensions (SAR 30537).                                                                                                                                                                                                                                                                                                                                     | II                                              |

|                                 | The Y security option and Licensed DPA Logo were added to the "IGLOO Ordering<br>Information" section. The trademarked Licensed DPA Logo identifies that a product is<br>covered by a DPA counter-measures license from Cryptography Research (SAR<br>32151).                                                                                                                                                                                 |                                                 |

|                                 | The "In-System Programming (ISP) and Security" section and "Security" section were revised to clarify that although no existing security measures can give an absolute guarantee, Microsemi FPGAs implement the best security available in the industry (SAR 32865).                                                                                                                                                                          |                                                 |

Datasheet Information

| Revision / Version                                  | Changes                                                                                                                                                                                                                                                                                                                                                       | Page            |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| <b>Revision 14 (Feb 2009)</b><br>Product Brief v1.4 | The "Advanced I/O" section was revised to include two bullets regarding wide range power supply voltage support.                                                                                                                                                                                                                                              | Ι               |

|                                                     | 3.0 V wide range was added to the list of supported voltages in the "I/Os with Advanced I/O Standards" section. The "Wide Range I/O Support" section is new.                                                                                                                                                                                                  | 1-8             |

| Revision 13 (Jan 2009)<br>Packaging v1.8            | The "CS121" pin table was revised to add a note regarding pins F1 and G1.                                                                                                                                                                                                                                                                                     | 4-7             |

| Revision 12 (Dec 2008)                              | QN48 and QN68 were added to the AGL030 for the following tables:                                                                                                                                                                                                                                                                                              | N/A             |

| Product Brief v1.3                                  | "IGLOO Devices" Product Family Table<br>"IGLOO Ordering Information"<br>"Temperature Grade Offerings"                                                                                                                                                                                                                                                         |                 |

|                                                     | QN132 is fully supported by AGL125 so footnote 3 was removed.                                                                                                                                                                                                                                                                                                 |                 |

| Packaging v1.7                                      | The "QN48" pin diagram and pin table are new.                                                                                                                                                                                                                                                                                                                 | 4-24            |

|                                                     | The "QN68" pin table for AGL030 is new.                                                                                                                                                                                                                                                                                                                       | 4-26            |

| Revision 12 (Dec 2008)                              | The AGL600 Function for pin K15 in the "FG484" table was changed to VCCIB1.                                                                                                                                                                                                                                                                                   | 4-78            |

| Revision 11 (Oct 2008)<br>Product Brief v1.2        | This document was updated to include AGL400 device information. The following sections were updated:                                                                                                                                                                                                                                                          | N/A             |

|                                                     | "IGLOO Devices" Product Family Table<br>"IGLOO Ordering Information"<br>"Temperature Grade Offerings"                                                                                                                                                                                                                                                         |                 |

|                                                     | Figure 1-2 • IGLOO Device Architecture Overview with Four I/O Banks (AGL250, AGL600, AGL400, and AGL1000)                                                                                                                                                                                                                                                     |                 |

| DC and Switching<br>Characteristics<br>Advance v0.5 | The tables in the "Quiescent Supply Current" section were updated with values for AGL400. In addition, the title was updated to include:<br>(VCC = VJTAG = VPP = $0$ V).                                                                                                                                                                                      | 2-7             |

|                                                     | The tables in the "Power Consumption of Various Internal Resources" section were updated with values for AGL400.                                                                                                                                                                                                                                              | 2-13            |

|                                                     | Table 2-178 • AGL400 Global Resource is new.                                                                                                                                                                                                                                                                                                                  | 2-109           |

| Packaging v1.6                                      | The "CS196" table for the AGL400 device is new.                                                                                                                                                                                                                                                                                                               | 4-14            |

|                                                     | The "FG144" table for the AGL400 device is new.                                                                                                                                                                                                                                                                                                               | 4-47            |

|                                                     | The "FG256" table for the AGL400 device is new.                                                                                                                                                                                                                                                                                                               | 4-54            |

|                                                     | The "FG484" table for the AGL400 device is new.                                                                                                                                                                                                                                                                                                               | 4-64            |

| Revision 10 (Aug 2008)                              | 3.0 V LVCMOS wide range support data was added to Table 2-2 • Recommended<br>Operating Conditions 1.                                                                                                                                                                                                                                                          | 2-2             |

| DC and Switching<br>Characteristics<br>Advance v0.4 | 3.3 V LVCMOS wide range support data was added to Table 2-25 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings to Table 2-27 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings. | 2-24 to<br>2-26 |

|                                                     | 3.3 V LVCMOS wide range support data was added to Table 2-28 • Summary of Maximum and Minimum DC Input Levels.                                                                                                                                                                                                                                                | 2-27            |

|                                                     | 3.3 V LVCMOS wide range support text was added to Table 2-49 · Minimum and Maximum DC Input and Output Levels for LVCMOS 3.3 V Wide Range.                                                                                                                                                                                                                    | 2-39            |

Datasheet Information

| Revision / Version               | Changes                                                                                                                                                                                    | Page           |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Advance v0.7<br>(continued)      | The former Table 2-16 • Maximum I/O Frequency for Single-Ended and Differential I/Os in All Banks in IGLOO Devices (maximum drive strength and high slew selected) was removed.            | N/A            |

|                                  | The "During Flash*Freeze Mode" section was updated to include information about the output of the I/O to the FPGA core.                                                                    | 2-57           |

|                                  | Table 2-31 • Flash*Freeze Pin Location in IGLOO Family Packages (device-<br>independent) was updated to add UC81 and CS281. Flash*Freeze pins were<br>assigned for CS81, CS121, and CS196. | 2-61           |

|                                  | Figure 2-40 • Flash*Freeze Mode Type 2 – Timing Diagram was updated to modify the LSICC Signal.                                                                                            | 2-55           |

|                                  | Information regarding calculation of the quiescent supply current was added to the "Quiescent Supply Current" section.                                                                     | 3-6            |

|                                  | Table3-8 • QuiescentSupplyCurrent(IDD)Characteristics,IGLOOFlash*FreezeMode <sup>†</sup> was updated.                                                                                      | 3-6            |

|                                  | Table 3-9 • Quiescent Supply Current ( $I_{DD}$ ) Characteristics, IGLOO Sleep Mode (VCC = 0 V) <sup>†</sup> was updated.                                                                  | 3-6            |

|                                  | Table 3-11 • Quiescent Supply Current (I <sub>DD</sub> ), No IGLOO Flash*Freeze Mode1 was updated.                                                                                         | 3-7            |

|                                  | Table 3-115         Minimum and Maximum DC Input and Output Levels was updated.                                                                                                            | 3-58           |

|                                  | Table 3-156 • JTAG 1532 was updated and Table 3-155 • JTAG 1532 is new.                                                                                                                    | 3-104          |

|                                  | The "121-Pin CSP" and "281-Pin CSP" packages are new.                                                                                                                                      | 4-5, 4-7       |

|                                  | The "81-Pin CSP" table for the AGL030 device was updated to change the G6 pin function to IO44RSB1 and the JG pin function to IO45RSB1.                                                    | 4-4            |

|                                  | The "121-Pin CSP" table for the AGL060 device is new.                                                                                                                                      | 4-6            |

|                                  | The "256-Pin FBGA" table for the AGL1000 device is new.                                                                                                                                    | 4-34           |

|                                  | The "281-Pin CSP" table for the AGL 600 device is new.                                                                                                                                     | 4-8            |

|                                  | The "100-Pin VQFP" table for the AGL060 device is new.                                                                                                                                     | 4-18           |

|                                  | The "144-Pin FBGA" table for the AGL250 device is new.                                                                                                                                     | 4-24           |

|                                  | The "144-Pin FBGA" table for the AGL1000 device is new.                                                                                                                                    | 4-28           |

|                                  | The "484-Pin FBGA" table for the AGL600 device is new.                                                                                                                                     | 4-38           |

|                                  | The "484-Pin FBGA" table for the AGL1000 device is new.                                                                                                                                    | 4-43           |

| Advance v0.6<br>(November 2007)  | Table 1 • IGLOO Product Family, the "I/Os Per Package1" table, and the "IGLOO Ordering Information", and the Temperature Grade Offerings table were updated to add the UC81 package.       | i, ii, iii, iv |

|                                  | The "81-Pin $\mu$ CSP" table for the AGL030 device is new.                                                                                                                                 | 4-3            |

|                                  | The "81-Pin CSP" table for the AGL030 device is new.                                                                                                                                       | 4-1            |

| Advance v0.5<br>(September 2007) | Table 1 • IGLOO Product Family was updated for AGL030 in the Package Pins section to change CS181 to CS81.                                                                                 | i              |

| Revision / Version               | Changes                                                                                                                                                                                                                                                         | Page           |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Advance v0.4<br>(September 2007) | Cortex-M1 device information was added to Table 1 • IGLOO Product Family, the "I/Os Per Package1" table, "IGLOO Ordering Information", and Temperature Grade Offerings.                                                                                         | i, ii, iii, iv |

|                                  | The number of single-ended I/Os for the CS81 package for AGL030 was updated to 66 in the "I/Os Per Package1" table.                                                                                                                                             | ii             |

|                                  | The "Power Conservation Techniques" section was updated to recommend that unused I/O signals be left floating.                                                                                                                                                  | 2-51           |

| Advance v0.3<br>(August 2007)    | In Table 1 • IGLOO Product Family, the CS81 package was added for AGL030. The CS196 was replaced by the CS121 for AGL060. Table note 3 was moved to the specific packages to which it applies for AGL060: QN132 and FG144.                                      | i              |

|                                  | The CS81 and CS121 packages were added to the "I/Os Per Package1" table.<br>The number of single-ended I/Os was removed for the CS196 package in<br>AGL060. Table note 6 was moved to the specific packages to which it applies for<br>AGL060: QN132 and FG144. | ii             |

|                                  | The CS81 and CS121 packages were added to the Temperature Grade Offerings table. The temperature grade offerings were removed for the CS196 package in AGL060. Table note 3 was moved to the specific packages to which it applies for AGL060: QN132 and FG144. | iv             |

|                                  | The CS81 and CS121 packages were added to Table 2-31 • Flash*Freeze Pin Location in IGLOO Family Packages (device-independent).                                                                                                                                 | 2-61           |

| Advance v0.2                     | The words "ambient temperature" were added to the temperature range in the "IGLOO Ordering Information", Temperature Grade Offerings, and "Speed Grade and Temperature Grade Matrix" sections.                                                                  | iii, iv        |

|                                  | The $T_J$ parameter in Table 3-2 • Recommended Operating Conditions was changed to $T_A$ , ambient temperature, and table notes 4–6 were added.                                                                                                                 | 3-2            |