Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

E·XFI

| Product Status                 | Active                                                                       |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                            |

| Number of Logic Elements/Cells | 13824                                                                        |

| Total RAM Bits                 | 110592                                                                       |

| Number of I/O                  | 177                                                                          |

| Number of Gates                | 600000                                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                                              |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 85°C (TA)                                                            |

| Package / Case                 | 256-LBGA                                                                     |

| Supplier Device Package        | 256-FPBGA (17x17)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1agl600v5-fgg256i |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Temperature and Voltage Derating Factors

Table 2-6 •Temperature and Voltage Derating Factors for Timing Delays (normalized to T<sub>J</sub> = 70°C, VCC = 1.425 V)For IGLOO V2 or V5 devices, 1.5 V DC Core Supply Voltage

| Array Voltage VCC<br>(V) | Junction Temperature (°C) |       |       |       |       |       |  |  |  |

|--------------------------|---------------------------|-------|-------|-------|-------|-------|--|--|--|

|                          | –40°C                     | 0°C   | 25°C  | 70°C  | 85°C  | 100°C |  |  |  |

| 1.425                    | 0.934                     | 0.953 | 0.971 | 1.000 | 1.007 | 1.013 |  |  |  |

| 1.500                    | 0.855                     | 0.874 | 0.891 | 0.917 | 0.924 | 0.929 |  |  |  |

| 1.575                    | 0.799                     | 0.816 | 0.832 | 0.857 | 0.864 | 0.868 |  |  |  |

Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays (normalized to T<sub>J</sub> = 70°C, VCC = 1.14 V) For IGLOO V2, 1.2 V DC Core Supply Voltage

| Array Voltage VCC<br>(V) | Junction Temperature (°C) |       |       |       |       |       |  |  |  |  |

|--------------------------|---------------------------|-------|-------|-------|-------|-------|--|--|--|--|

|                          | –40°C                     | 0°C   | 25°C  | 70°C  | 85°C  | 100°C |  |  |  |  |

| 1.14                     | 0.967                     | 0.978 | 0.991 | 1.000 | 1.006 | 1.010 |  |  |  |  |

| 1.20                     | 0.864                     | 0.874 | 0.885 | 0.894 | 0.899 | 0.902 |  |  |  |  |

| 1.26                     | 0.794                     | 0.803 | 0.814 | 0.821 | 0.827 | 0.830 |  |  |  |  |

## **Calculating Power Dissipation**

### **Quiescent Supply Current**

Quiescent supply current (IDD) calculation depends on multiple factors, including operating voltages (VCC, VCCI, and VJTAG), operating temperature, system clock frequency, and power modes usage. Microsemi recommends using the PowerCalculator and SmartPower software estimation tools to evaluate the projected static and active power based on the user design, power mode usage, operating voltage, and temperature.

#### Table 2-8 • Power Supply State per Mode

| Power Supply Configurations |     |        |      |       |                 |  |

|-----------------------------|-----|--------|------|-------|-----------------|--|

| Modes/power supplies        | VCC | VCCPLL | VCCI | VJTAG | VPUMP           |  |

| Flash*Freeze                | On  | On     | On   | On    | On/off/floating |  |

| Sleep                       | Off | Off    | On   | Off   | Off             |  |

| Shutdown                    | Off | Off    | Off  | Off   | Off             |  |

| No Flash*Freeze             | On  | On     | On   | On    | On/off/floating |  |

Note: Off: Power supply level = 0 V

|         | Core<br>Voltage | AGL015 | AGL030 | AGL060 | AGL125 | AGL250 | AGL400 | AGL600 | AGL1000 | Units |

|---------|-----------------|--------|--------|--------|--------|--------|--------|--------|---------|-------|

| Typical | 1.2 V           | 4      | 4      | 8      | 13     | 20     | 27     | 30     | 44      | μΑ    |

| (25°C)  | 1.5 V           | 6      | 6      | 10     | 18     | 34     | 51     | 72     | 127     | μΑ    |

Note: \*IDD includes VCC, VPUMP, VCCI, VCCPLL, and VMV currents. Values do not include I/O static contribution, which is shown in Table 2-13 on page 2-10 through Table 2-15 on page 2-11 and Table 2-16 on page 2-11 through Table 2-18 on page 2-12 (PDC6 and PDC7).

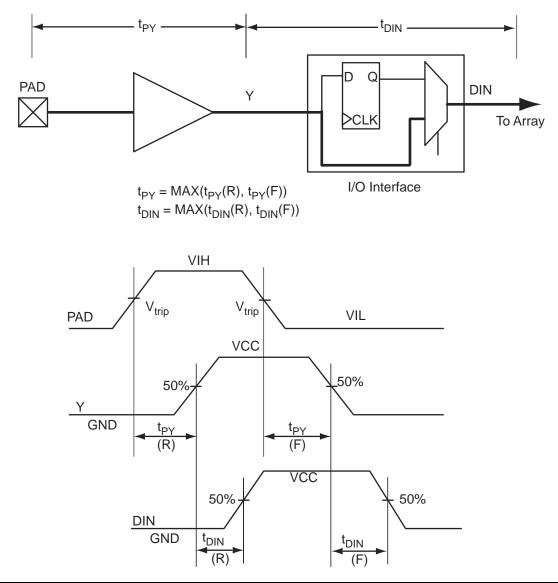

Figure 2-4 • Input Buffer Timing Model and Delays (example)

### Single-Ended I/O Characteristics

### 3.3 V LVTTL / 3.3 V LVCMOS

Low-Voltage Transistor–Transistor Logic (LVTTL) is a general-purpose standard (EIA/JESD) for 3.3 V applications. It uses an LVTTL input buffer and push-pull output buffer. Furthermore, all LVCMOS 3.3 V software macros comply with LVCMOS 3.3 V wide range as specified in the JESD8a specification.

# Table 2-47 • Minimum and Maximum DC Input and Output Levels Applicable to Advanced I/O Banks

| 3.3 V LVTTL /<br>3.3 V LVCMOS | v         | IL        | v         | н         | VOL       | VOH       | IOL | юн | IOSL                    | IOSH                    | IIL¹            | IIH <sup>2</sup> |

|-------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-----------------|------------------|

| Drive<br>Strength             | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 2 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 2   | 2  | 25                      | 27                      | 10              | 10               |

| 4 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 4   | 4  | 25                      | 27                      | 10              | 10               |

| 6 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 6   | 6  | 51                      | 54                      | 10              | 10               |

| 8 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 8   | 8  | 51                      | 54                      | 10              | 10               |

| 12 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 12  | 12 | 103                     | 109                     | 10              | 10               |

| 16 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 16  | 16 | 132                     | 127                     | 10              | 10               |

| 24 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 24  | 24 | 268                     | 181                     | 10              | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

Table 2-48 •

Minimum and Maximum DC Input and Output Levels

Applicable to Standard Plus I/O Banks

| 3.3 V LVTTL /<br>3.3 V LVCMOS | v         | ΊL        | v         | н         | V <sub>OL</sub> | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------------------|-----------|-----------|-----------|-----------|-----------------|-----------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength             | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V       | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4             | 2.4       | 2   | 2  | 25                      | 27                      | 10               | 10               |

| 4 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4             | 2.4       | 4   | 4  | 25                      | 27                      | 10               | 10               |

| 6 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4             | 2.4       | 6   | 6  | 51                      | 54                      | 10               | 10               |

| 8 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4             | 2.4       | 8   | 8  | 51                      | 54                      | 10               | 10               |

| 12 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4             | 2.4       | 12  | 12 | 103                     | 109                     | 10               | 10               |

| 16 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4             | 2.4       | 16  | 16 | 103                     | 109                     | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

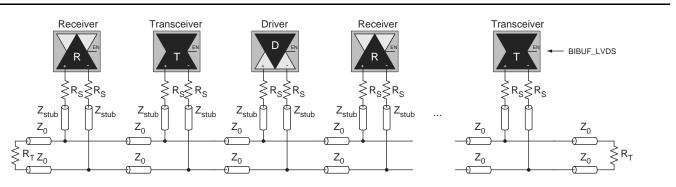

### B-LVDS/M-LVDS

Bus LVDS (B-LVDS) and Multipoint LVDS (M-LVDS) specifications extend the existing LVDS standard to highperformance multipoint bus applications. Multidrop and multipoint bus configurations may contain any combination of drivers, receivers, and transceivers. Microsemi LVDS drivers provide the higher drive current required by B-LVDS and M-LVDS to accommodate the loading. The drivers require series terminations for better signal quality and to control voltage swing. Termination is also required at both ends of the bus since the driver can be located anywhere on the bus. These configurations can be implemented using the TRIBUF\_LVDS and BIBUF\_LVDS macros along with appropriate terminations. Multipoint designs using Microsemi LVDS macros can achieve up to 200 MHz with a maximum of 20 loads. A sample application is given in Figure 2-14. The input and output buffer delays are available in the LVDS section in Table 2-149 on page 2-81 and Table 2-150 on page 2-81.

Example: For a bus consisting of 20 equidistant loads, the following terminations provide the required differential voltage, in worst-case Industrial operating conditions, at the farthest receiver:  $R_S = 60 \Omega$  and  $R_T = 70 \Omega$ , given  $Z_0 = 50 \Omega$  (2") and  $Z_{stub} = 50 \Omega$  (~1.5").

### LVPECL

Low-Voltage Positive Emitter-Coupled Logic (LVPECL) is another differential I/O standard. It requires that one data bit be carried through two signal lines. Like LVDS, two pins are needed. It also requires external resistor termination.

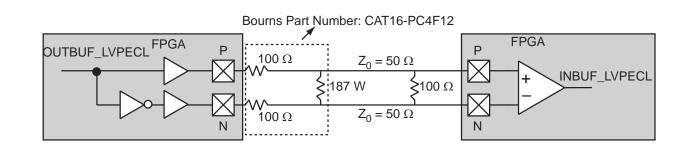

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-15. The building blocks of the LVPECL transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVDS implementation because the output standard specifications are different.

Figure 2-15 • LVPECL Circuit Diagram and Board-Level Implementation

| Parameter Name        | Parameter Definition                                             | Measuring Nodes<br>(from, to)* |

|-----------------------|------------------------------------------------------------------|--------------------------------|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                           | H, DOUT                        |

| tosud                 | Data Setup Time for the Output Data Register                     | F, H                           |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                      | F, H                           |

| tosue                 | Enable Setup Time for the Output Data Register                   | G, H                           |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                    | G, H                           |

| t <sub>OPRE2Q</sub>   | Asynchronous Preset-to-Q of the Output Data Register             | L, DOUT                        |

| t <sub>OREMPRE</sub>  | Asynchronous Preset Removal Time for the Output Data Register    | L, H                           |

| t <sub>ORECPRE</sub>  | Asynchronous Preset Recovery Time for the Output Data Register   | L, H                           |

| t <sub>oeclkq</sub>   | Clock-to-Q of the Output Enable Register                         | H, EOUT                        |

| tOESUD                | Data Setup Time for the Output Enable Register                   | J, H                           |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                    | J, H                           |

| tOESUE                | Enable Setup Time for the Output Enable Register                 | К, Н                           |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                  | К, Н                           |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register           | I, EOUT                        |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register  | I, H                           |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register | I, H                           |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                            | A, E                           |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                      | C, A                           |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                       | C, A                           |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                    | B, A                           |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                     | B, A                           |

| t <sub>IPRE2Q</sub>   | Asynchronous Preset-to-Q of the Input Data Register              | D, E                           |

| t <sub>IREMPRE</sub>  | Asynchronous Preset Removal Time for the Input Data Register     | D, A                           |

| t <sub>IRECPRE</sub>  | Asynchronous Preset Recovery Time for the Input Data Register    | D, A                           |

#### Table 2-155 • Parameter Definition and Measuring Nodes

Note: \*See Figure 2-16 on page 2-84 for more information.

## **VersaTile Characteristics**

### VersaTile Specifications as a Combinatorial Module

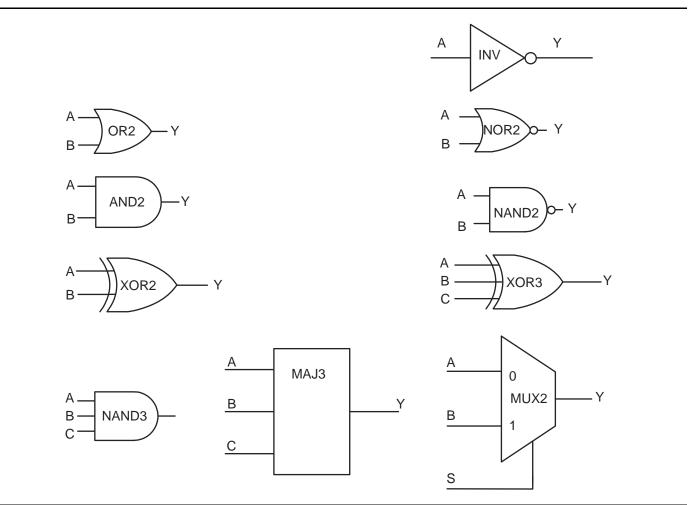

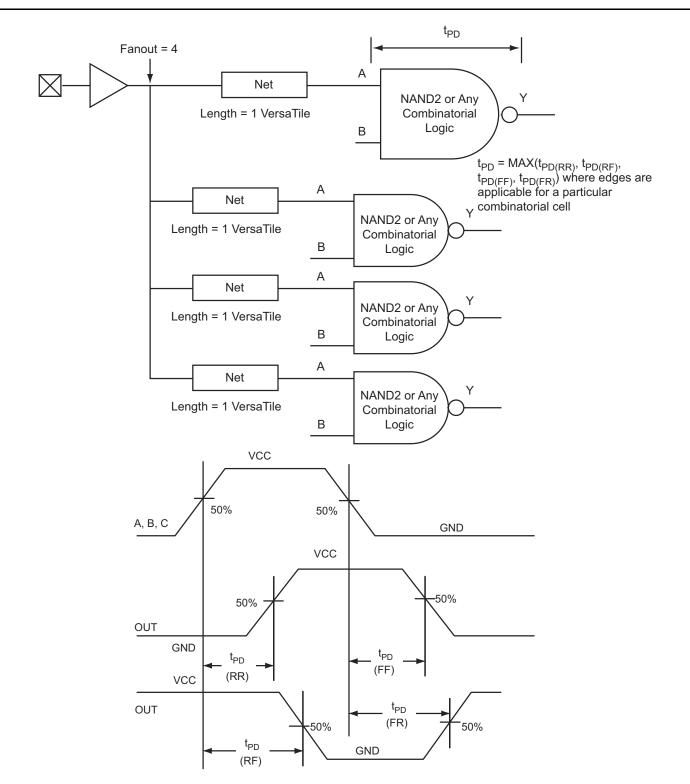

The IGLOO library offers all combinations of LUT-3 combinatorial functions. In this section, timing characteristics are presented for a sample of the library. For more details, refer to the *IGLOO, Fusion, and ProASIC3 Macro Library Guide*.

Figure 2-25 • Sample of Combinatorial Cells

Figure 2-26 • Timing Model and Waveforms

#### 1.2 V DC Core Voltage

# Table 2-181 • AGL015 Global ResourceCommercial-Case Conditions: TJ = 70°C, VCC = 1.14 V

|                      |                                           | S                 | td.               |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.79              | 2.09              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.87              | 2.26              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.39              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

### Table 2-182 • AGL030 Global Resource

#### Commercial-Case Conditions: $T_J = 70^{\circ}C$ , VCC = 1.14 V

|                      |                                           | S                 | td.               |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.80              | 2.09              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.88              | 2.27              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.39              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

#### Table 2-190 • IGLOO CCC/PLL Specification For IGLOO V2 Devices, 1.2 V DC Core Supply Voltage

| Parameter                                                          | Min.           | Тур.             | Max.            | Units             |

|--------------------------------------------------------------------|----------------|------------------|-----------------|-------------------|

| Clock Conditioning Circuitry Input Frequency fIN_CCC               | 1.5            |                  | 160             | MHz               |

| Clock Conditioning Circuitry Output Frequency f <sub>OUT_CCC</sub> | 0.75           |                  | 160             | MHz               |

| Delay Increments in Programmable Delay Blocks <sup>1, 2</sup>      |                | 580 <sup>3</sup> |                 | ps                |

| Number of Programmable Values in Each Programmable Delay Block     |                |                  | 32              |                   |

| Serial Clock (SCLK) for Dynamic PLL <sup>4,5</sup>                 |                |                  | 60              | ns                |

| Input Cycle-to-Cycle Jitter (peak magnitude)                       |                |                  | 0.25            | ns                |

| Acquisition Time                                                   |                |                  |                 |                   |

| LockControl = 0                                                    |                |                  | 300             | μs                |

| LockControl = 1                                                    |                |                  | 6.0             | ms                |

| Tracking Jitter <sup>6</sup>                                       |                |                  |                 |                   |

| LockControl = 0                                                    |                |                  | 4               | ns                |

| LockControl = 1                                                    |                |                  | 3               | ns                |

| Output Duty Cycle                                                  | 48.5           |                  | 51.5            | %                 |

| Delay Range in Block: Programmable Delay 1 <sup>1,2</sup>          | 2.3            |                  | 20.86           | ns                |

| Delay Range in Block: Programmable Delay 2 <sup>1,2</sup>          | 0.863          |                  | 20.86           | ns                |

| Delay Range in Block: Fixed Delay <sup>1, 2, 5</sup>               |                | 5.7              |                 | ns                |

| CCC Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub>         | Maxim          | um Peak-to-I     | Peak Jitter Dat | ta <sup>7,8</sup> |

|                                                                    | $SSO \geq 4^9$ | $SSO \geq 8^9$   | $SSO \geq 16^9$ |                   |

| 0.75 MHz to 50 MHz                                                 | 1.20%          | 2.00%            | 3.00%           |                   |

| 50 MHz to 160 MHz                                                  | 5.00%          | 7.00%            | 15.00%          |                   |

Notes:

1. This delay is a function of voltage and temperature. See Table 2-6 on page 2-7 and Table 2-7 on page 2-7 for deratings.

2.  $T_J = 25^{\circ}C$ ,  $V_{CC} = 1.2 V$

3. When the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available. Refer to the Libero SoC Online Help associated with the core for more information.

4. Maximum value obtained for a Std. speed grade device in Worst-Case Commercial Conditions. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

5. The AGL030 device does not support a PLL.

6. Tracking jitter is defined as the variation in clock edge position of PLL outputs with reference to the PLL input clock edge. Tracking jitter does not measure the variation in PLL output period, which is covered by the period jitter parameter.

7. VCO output jitter is calculated as a percentage of the VCO frequency. The jitter (in ps) can be calculated by multiplying the VCO period by the per cent jitter. The VCO jitter (in ps) applies to CCC\_OUT regardless of the output divider settings. For example, if the jitter on VCO is 300 ps, the jitter on CCC\_OUT is also 300 ps, regardless of the output divider settings.

Measurements done with LVTTL 3.3 V, 8 mA I/O drive strength, and high slew Rate. VCC/VCCPLL = 1.14 V, VQ/PQ/TQ type of packages, 20 pF load.

SSO are outputs that are synchronous to a single clock domain and have clock-to-out times that are within ±200 ps of each other. Switching I/Os are placed outside of the PLL bank. Refer to the "Simultaneously Switching Outputs (SSOs) and Printed Circuit Board Layout" section in the IGLOO FPGA Fabric User Guide.

10. For definitions of Type 1 and Type 2, refer to the PLL Block Diagram in the "Clock Conditioning Circuits in IGLOO and ProASIC3 Devices" chapter of the IGLOO FPGA Fabric User Guide.

#### 1.2 V DC Core Voltage

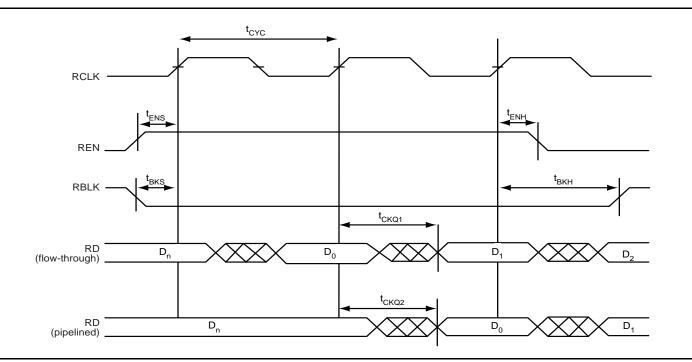

#### Table 2-193 • RAM4K9

### Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Parameter             | Description                                                                                                          | Std.  | Units |

|-----------------------|----------------------------------------------------------------------------------------------------------------------|-------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                   | 1.53  | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                    |       | ns    |

| t <sub>ENS</sub>      | REN WEN setup time                                                                                                   | 1.50  | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                   | 0.29  | ns    |

| t <sub>BKS</sub>      | BLK setup time                                                                                                       | 3.05  | ns    |

| t <sub>BKH</sub>      | BLK hold time                                                                                                        | 0.29  | ns    |

| t <sub>DS</sub>       | Input data (DIN) setup time                                                                                          | 1.33  | ns    |

| t <sub>DH</sub>       | Input data (DIN) hold time                                                                                           | 0.66  | ns    |

| t <sub>CKQ1</sub>     | Clock High to new data valid on DOUT (output retained, WMODE = 0)                                                    | 6.61  | ns    |

|                       | Clock High to new data valid on DOUT (flow-through, WMODE = 1)                                                       | 5.72  | ns    |

| t <sub>CKQ2</sub>     | Clock High to new data valid on DOUT (pipelined)                                                                     | 3.38  | ns    |

| t <sub>C2CWWL</sub> 1 | Address collision clk-to-clk delay for reliable write after write on same address – Applicable to Closing Edge       |       | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address – Applicable to Opening Edge |       | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address – Applicable to Opening Edge |       | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to data out Low on DOUT (flow-through)                                                                     |       | ns    |

|                       | RESET Low to data out Low on DOUT (pipelined)                                                                        | 3.86  | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                        |       | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                       |       | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                            |       | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                     | 10.90 | ns    |

| F <sub>MAX</sub>      | Maximum frequency                                                                                                    | 92    | MHz   |

Notes:

1. For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

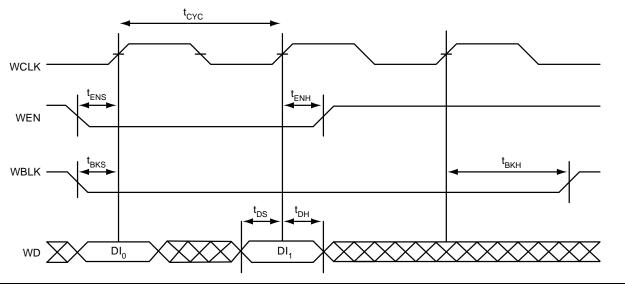

## Timing Waveforms

## Figure 2-38 • FIFO Read

### 1.2 V DC Core Voltage

#### Table 2-196 • FIFO

## Worst Commercial-Case Conditions: $T_J = 70^{\circ}C$ , VCC = 1.14 V

| Parameter            | Description                                       | Std.  | Units |

|----------------------|---------------------------------------------------|-------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 4.13  | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.31  | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.47  | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00  | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 1.56  | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.49  | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 6.80  | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 3.62  | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 7.23  | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 6.85  | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 26.61 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 7.12  | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 26.33 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on RD (flow-through)    | 4.09  | ns    |

|                      | RESET Low to Data Out Low on RD (pipelined)       | 4.09  | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 1.23  | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 6.58  | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 1.18  | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 10.90 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 92    | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

## Microsemi

Package Pin Assignments

| QN132                      |               |  |  |

|----------------------------|---------------|--|--|

| Pin Number AGL030 Function |               |  |  |

| C17                        | IO47RSB1      |  |  |

| C18                        | NC            |  |  |

| C19                        | ТСК           |  |  |

| C20                        | NC            |  |  |

| C21                        | VPUMP         |  |  |

| C22                        | VJTAG         |  |  |

| C23                        | NC            |  |  |

| C24                        | NC            |  |  |

| C25                        | NC            |  |  |

| C26                        | GDB0/IO34RSB0 |  |  |

| C27                        | NC            |  |  |

| C28                        | VCCIB0        |  |  |

| C29                        | IO28RSB0      |  |  |

| C30                        | IO25RSB0      |  |  |

| C31                        | IO24RSB0      |  |  |

| C32                        | IO21RSB0      |  |  |

| C33                        | NC            |  |  |

| C34                        | NC            |  |  |

| C35                        | VCCIB0        |  |  |

| C36                        | IO13RSB0      |  |  |

| C37                        | IO10RSB0      |  |  |

| C38                        | IO07RSB0      |  |  |

| C39                        | IO03RSB0      |  |  |

| C40                        | IO00RSB0      |  |  |

| D1                         | GND           |  |  |

| D2                         | GND           |  |  |

| D3                         | GND           |  |  |

| D4                         | GND           |  |  |

## Microsemi

Package Pin Assignments

|            | VQ100            |            | VQ100           | VQ100      |                 |

|------------|------------------|------------|-----------------|------------|-----------------|

| Pin Number | AGL125 Function  | Pin Number | AGL125 Function | Pin Number | AGL125 Function |

| 1          | GND              | 36         | IO93RSB1        | 72         | IO42RSB0        |

| 2          | GAA2/IO67RSB1    | 37         | VCC             | 73         | GBA2/IO41RSB0   |

| 3          | IO68RSB1         | 38         | GND             | 74         | VMV0            |

| 4          | GAB2/IO69RSB1    | 39         | VCCIB1          | 75         | GNDQ            |

| 5          | IO132RSB1        | 40         | IO87RSB1        | 76         | GBA1/IO40RSB0   |

| 6          | GAC2/IO131RSB1   | 41         | IO84RSB1        | 77         | GBA0/IO39RSB0   |

| 7          | IO130RSB1        | 42         | IO81RSB1        | 78         | GBB1/IO38RSB0   |

| 8          | IO129RSB1        | 43         | IO75RSB1        | 79         | GBB0/IO37RSB0   |

| 9          | GND              | 44         | GDC2/IO72RSB1   | 80         | GBC1/IO36RSB0   |

| 10         | GFB1/IO124RSB1   | 45         | GDB2/IO71RSB1   | 81         | GBC0/IO35RSB0   |

| 11         | GFB0/IO123RSB1   | 46         | GDA2/IO70RSB1   | 82         | IO32RSB0        |

| 12         | VCOMPLF          | 47         | TCK             | 83         | IO28RSB0        |

| 13         | GFA0/IO122RSB1   | 48         | TDI             | 84         | IO25RSB0        |

| 14         | VCCPLF           | 49         | TMS             | 85         | IO22RSB0        |

| 15         | GFA1/IO121RSB1   | 50         | VMV1            | 86         | IO19RSB0        |

| 16         | GFA2/IO120RSB1   | 51         | GND             | 87         | VCCIB0          |

| 17         | VCC              | 52         | VPUMP           | 88         | GND             |

| 18         | VCCIB1           | 53         | NC              | 89         | VCC             |

| 19         | GEC0/IO111RSB1   | 54         | TDO             | 90         | IO15RSB0        |

| 20         | GEB1/IO110RSB1   | 55         | TRST            | 91         | IO13RSB0        |

| 21         | GEB0/IO109RSB1   | 56         | VJTAG           | 92         | IO11RSB0        |

| 22         | GEA1/IO108RSB1   | 57         | GDA1/IO65RSB0   | 93         | IO09RSB0        |

| 23         | GEA0/IO107RSB1   | 58         | GDC0/IO62RSB0   | 94         | IO07RSB0        |

| 24         | VMV1             | 59         | GDC1/IO61RSB0   | 95         | GAC1/IO05RSB0   |

| 25         | GNDQ             | 60         | GCC2/IO59RSB0   | 96         | GAC0/IO04RSB0   |

| 26         | GEA2/IO106RSB1   | 61         | GCB2/IO58RSB0   | 97         | GAB1/IO03RSB0   |

| 27         | FF/GEB2/IO105RSB | 62         | GCA0/IO56RSB0   | 98         | GAB0/IO02RSB0   |

|            | 1                | 63         | GCA1/IO55RSB0   | 99         | GAA1/IO01RSB0   |

| 28         | GEC2/IO104RSB1   | 64         | GCC0/IO52RSB0   | 100        | GAA0/IO00RSB0   |

| 29         | IO102RSB1        | 65         | GCC1/IO51RSB0   |            |                 |

| 30         | IO100RSB1        | 66         | VCCIB0          |            |                 |

| 31         | IO99RSB1         | 67         | GND             |            |                 |

| 32         | IO97RSB1         | 68         | VCC             |            |                 |

| 33         | IO96RSB1         | 69         | IO47RSB0        |            |                 |

| 34         | IO95RSB1         | 70         | GBC2/IO45RSB0   |            |                 |

| 35         | IO94RSB1         | 71         | GBB2/IO43RSB0   |            |                 |

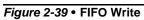

## FG144

Note: This is the bottom view of the package.

#### Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

## Microsemi

Package Pin Assignments

| FG484                      |                   |  |  |

|----------------------------|-------------------|--|--|

| Pin Number AGL400 Function |                   |  |  |

| V15                        | IO85RSB2          |  |  |

| V16                        | GDB2/IO81RSB2     |  |  |

| V17                        | TDI               |  |  |

| V18                        | NC                |  |  |

| V19                        | TDO               |  |  |

| V20                        | GND               |  |  |

| V21                        | NC                |  |  |

| V22                        | NC                |  |  |

| W1                         | NC                |  |  |

| W2                         | NC                |  |  |

| W3                         | NC                |  |  |

| W4                         | GND               |  |  |

| W5                         | IO126RSB2         |  |  |

| W6                         | FF/GEB2/IO133RSB2 |  |  |

| W7                         | IO124RSB2         |  |  |

| W8                         | IO116RSB2         |  |  |

| W9                         | IO113RSB2         |  |  |

| W10                        | IO107RSB2         |  |  |

| W11                        | IO105RSB2         |  |  |

| W12                        | IO102RSB2         |  |  |

| W13                        | IO97RSB2          |  |  |

| W14                        | IO92RSB2          |  |  |

| W15                        | GDC2/IO82RSB2     |  |  |

| W16                        | IO86RSB2          |  |  |

| W17                        | GDA2/IO80RSB2     |  |  |

| W18                        | TMS               |  |  |

| W19                        | GND               |  |  |

| W20                        | NC                |  |  |

| W21                        | NC                |  |  |

| W22                        | NC                |  |  |

| Y1                         | VCCIB3            |  |  |

| Y2                         | NC                |  |  |

| Y3                         | NC                |  |  |

| Y4                         | NC                |  |  |

| Y5                         | GND               |  |  |

| Y6                         | NC                |  |  |

| FG484                       |           |  |  |

|-----------------------------|-----------|--|--|

| Pin Number AGL1000 Function |           |  |  |

| AA15                        | NC        |  |  |

| AA16                        | IO122RSB2 |  |  |

| AA17                        | IO119RSB2 |  |  |

| AA18                        | IO117RSB2 |  |  |

| AA19                        | NC        |  |  |

| AA20                        | NC        |  |  |

| AA21                        | VCCIB1    |  |  |

| AA22                        | GND       |  |  |

| AB1                         | GND       |  |  |

| AB2                         | GND       |  |  |

| AB3                         | VCCIB2    |  |  |

| AB4                         | IO180RSB2 |  |  |

| AB5                         | IO176RSB2 |  |  |

| AB6                         | IO173RSB2 |  |  |

| AB7                         | IO167RSB2 |  |  |

| AB8                         | IO162RSB2 |  |  |

| AB9                         | IO156RSB2 |  |  |

| AB10                        | IO150RSB2 |  |  |

| AB11                        | IO145RSB2 |  |  |

| AB12                        | IO144RSB2 |  |  |

| AB13                        | IO132RSB2 |  |  |

| AB14                        | IO127RSB2 |  |  |

| AB15                        | IO126RSB2 |  |  |

| AB16                        | IO123RSB2 |  |  |

| AB17                        | IO121RSB2 |  |  |

| AB18                        | IO118RSB2 |  |  |

| AB19                        | NC        |  |  |

| AB20                        | VCCIB2    |  |  |

| AB21                        | GND       |  |  |

| AB22                        | GND       |  |  |

| B1                          | GND       |  |  |

| B2                          | VCCIB3    |  |  |

| B3                          | NC        |  |  |

| B4                          | IO06RSB0  |  |  |

| B5                          | IO08RSB0  |  |  |

|                             | IO12RSB0  |  |  |

| FG484                       |           |  |  |

|-----------------------------|-----------|--|--|

| Pin Number AGL1000 Function |           |  |  |

| B7                          | IO15RSB0  |  |  |

| B8                          | IO19RSB0  |  |  |

| B9                          | IO24RSB0  |  |  |

| B10                         | IO31RSB0  |  |  |

| B11                         | IO39RSB0  |  |  |

| B12                         | IO48RSB0  |  |  |

| B13                         | IO54RSB0  |  |  |

| B14                         | IO58RSB0  |  |  |

| B15                         | IO63RSB0  |  |  |

| B16                         | IO66RSB0  |  |  |

| B17                         | IO68RSB0  |  |  |

| B18                         | IO70RSB0  |  |  |

| B19                         | NC        |  |  |

| B20                         | NC        |  |  |

| B21                         | VCCIB1    |  |  |

| B22                         | GND       |  |  |

| C1                          | VCCIB3    |  |  |

| C2                          | IO220PDB3 |  |  |

| C3                          | NC        |  |  |

| C4                          | NC        |  |  |

| C5                          | GND       |  |  |

| C6                          | IO10RSB0  |  |  |

| C7                          | IO14RSB0  |  |  |

| C8                          | VCC       |  |  |

| C9                          | VCC       |  |  |

| C10                         | IO30RSB0  |  |  |

| C11                         | IO37RSB0  |  |  |

| C12                         | IO43RSB0  |  |  |

| C13                         | NC        |  |  |

| C14                         | VCC       |  |  |

| C15                         | VCC       |  |  |

| C16                         | NC        |  |  |

| C17                         | NC        |  |  |

| C18                         | GND       |  |  |

| C19                         | NC        |  |  |

| C20                         | NC        |  |  |

IGLOO Low Power Flash FPGAs

| Revision / Version                                                                                                                                                                                                                                                                     | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| DC & Switching, cont'd.                                                                                                                                                                                                                                                                | Table 2-49 · Minimum and Maximum DC Input and Output Levels for LVCMOS 3.3 V Wide Range is new.                                                                                                                                                                                                                                                                                                                                                                                                       | 2-39 |

| Revision 9 (Jul 2008)As a result of the Libero IDE v8.4 release, Actel now offers a wide range of convoltage support. The document was updated to change 1.2 V / 1.5 V to 1.2 V to 1.2 V to 1.2 V to 1.2 V to 1.4 V to 1.5 V.DC and Switching<br>Characteristics<br>Advance v0.31.5 V. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | N/A  |

| Revision 8 (Jun 2008)                                                                                                                                                                                                                                                                  | As a result of the Libero IDE v8.4 release, Actel now offers a wide range of core voltage support. The document was updated to change $1.2 \text{ V} / 1.5 \text{ V}$ to $1.2 \text{ V}$ to $1.5 \text{ V}$ .                                                                                                                                                                                                                                                                                         | N/A  |

| DC and Switching<br>Characteristics<br>Advance v0.2                                                                                                                                                                                                                                    | Tables have been updated to reflect default values in the software. The default I/O capacitance is 5 pF. Tables have been updated to include the LVCMOS 1.2 V I/O set.<br>DDR Tables have two additional data points added to reflect both edges for Input DDR setup and hold time.<br>The power data table has been updated to match SmartPower data rather then simulation values.<br>AGL015 global clock delays have been added.                                                                   | N/A  |

|                                                                                                                                                                                                                                                                                        | Table 2-1 • Absolute Maximum Ratings was updated to combine the VCCI and VMV parameters in one row. The word "output" from the parameter description for VCCI and VMV, and table note 3 was added.                                                                                                                                                                                                                                                                                                    | 2-1  |

|                                                                                                                                                                                                                                                                                        | Table 2-2 • Recommended Operating Conditions 1 was updated to add references to tables notes 4, 6, 7, and 8. VMV was added to the VCCI parameter row, and table note 9 was added.                                                                                                                                                                                                                                                                                                                     | 2-2  |

|                                                                                                                                                                                                                                                                                        | In Table 2-3 • Flash Programming Limits – Retention, Storage, and Operating Temperature1, the maximum operating junction temperature was changed from 110° to 100°.                                                                                                                                                                                                                                                                                                                                   | 2-3  |

|                                                                                                                                                                                                                                                                                        | VMV was removed from Table 2-4 • Overshoot and Undershoot Limits 1. The table title was modified to remove "as measured on quiet I/Os." Table note 2 was revised to remove "estimated SSO density over cycles." Table note 3 was revised to remove "refers only to overshoot/undershoot limits for simultaneous switching I/Os."                                                                                                                                                                      | 2-3  |

|                                                                                                                                                                                                                                                                                        | The "PLL Behavior at Brownout Condition" section is new.                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-4  |

|                                                                                                                                                                                                                                                                                        | Figure 2-2 • V2 Devices – I/O State as a Function of VCCI and VCC Voltage Levels is new.                                                                                                                                                                                                                                                                                                                                                                                                              | 2-5  |

|                                                                                                                                                                                                                                                                                        | EQ 2 was updated. The temperature was changed to 100°C, and therefore the end result changed.                                                                                                                                                                                                                                                                                                                                                                                                         | 2-6  |

|                                                                                                                                                                                                                                                                                        | The table notes for Table 2-9 • Quiescent Supply Current (IDD) Characteristics, IGLOO Flash*Freeze Mode*, Table 2-10 • Quiescent Supply Current (IDD) Characteristics, IGLOO Sleep Mode*, and Table 2-11 • Quiescent Supply Current (IDD) Characteristics, IGLOO Shutdown Mode were updated to remove VMV and include PDC6 and PDC7. VCCI and VJTAG were removed from the statement about IDD in the table note for Table 2-11 • Quiescent Supply Current (IDD) Characteristics, IGLOO Shutdown Mode. | 2-7  |

|                                                                                                                                                                                                                                                                                        | Note 2 of Table 2-12 • Quiescent Supply Current (IDD), No IGLOO Flash*Freeze<br>Mode1 was updated to include VCCPLL. Note 4 was updated to include PDC6<br>and PDC7.                                                                                                                                                                                                                                                                                                                                  | 2-9  |

Datasheet Information

| Revision / Version                                 | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page                    |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Revision 8 (cont'd)                                | Table 2-13 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings, Table 2-14 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings, Table 2-15 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings, and Table 2-16 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings1 were updated to change PDC2 to PDC6 and PDC3 to PDC7. The table notes were updated to reflect that power was measured on VCCI. | 2-10<br>through<br>2-11 |

|                                                    | In Table 2-19 • Different Components Contributing to Dynamic Power Consumption in IGLOO Devices, the description for PAC13 was changed from Static to Dynamic.                                                                                                                                                                                                                                                                                                                                              | 2-13                    |

|                                                    | Table 2-20 • Different Components Contributing to the Static Power Consumption<br>in IGLOO Devices and Table 2-22 • Different Components Contributing to the<br>Static Power Consumption in IGLOO Device were updated to add PDC6 and<br>PDC7, and to change the definition for PDC5 to bank quiescent power. Subtitles<br>were added to indicate type of devices and core supply voltage.                                                                                                                  | 2-14,<br>2-16           |

|                                                    | The "Total Static Power Consumption—PSTAT" section was updated to revise the calculation of P <sub>STAT</sub> , including PDC6 and PDC7.                                                                                                                                                                                                                                                                                                                                                                    | 2-17                    |

|                                                    | Footnote † was updated to include information about PAC13. The PLL Contribution equation was changed from: $P_{PLL} = P_{AC13} + P_{AC14} * F_{CLKOUT}$ to $P_{PLL} = P_{DC4} + P_{AC13} * F_{CLKOUT}$ .                                                                                                                                                                                                                                                                                                    | 2-18                    |

| <b>Revision 7 (Jun 2008)</b><br>Packaging v1.5     | The "QN132" package diagram was updated to include D1 to D4. In addition, note 1 was changed from top view to bottom view, and note 2 is new.                                                                                                                                                                                                                                                                                                                                                               | 4-28                    |

| <b>Revision 6 (Jun 2008)</b><br>Packaging v1.4     | This document was divided into two sections and given a version number, starting at v1.0. The first section of the document includes features, benefits, ordering information, and temperature and speed grade offerings. The second section is a device family overview.                                                                                                                                                                                                                                   | N/A                     |

|                                                    | Pin numbers were added to the "QN68" package diagram. Note 2 was added below the diagram.                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-25                    |

| <b>Revision 5 (Mar 2008)</b><br>Packaging v1.3     | The "CS196" package and pin table was added for AGL250.                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-12                    |

| <b>Revision 4 (Mar 2008)</b><br>Product Brief v1.0 | The "Low Power" section was updated to change "1.2 V and 1.5 V Core Voltage" to "1.2 V and 1.5 V Core and I/O Voltage." The text "(from 12 $\mu$ W)" was removed from "Low Power Active FPGA Operation."                                                                                                                                                                                                                                                                                                    | Ι                       |

|                                                    | 1.2_V was added to the list of core and I/O voltages in the "Advanced I/O" and "I/Os with Advanced I/O Standards" section sections.                                                                                                                                                                                                                                                                                                                                                                         | l, 1-7                  |

|                                                    | The "Embedded Memory" section was updated to remove the footnote reference from the section heading and place it instead after "4,608-Bit" and "True Dual-Port SRAM (except ×18)."                                                                                                                                                                                                                                                                                                                          | Ι                       |