Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                     |

|----------------------------|---------------------------------------------------------------------|

| Product Status             | Obsolete                                                            |

| Core Processor             | 56800E                                                              |

| Core Size                  | 16-Bit                                                              |

| Speed                      | 120MHz                                                              |

| Connectivity               | EBI/EMI, SCI, SPI, SSI                                              |

| Peripherals                | DMA, POR, WDT                                                       |

| Number of I/O              | 47                                                                  |

| Program Memory Size        | 80KB (40K x 16)                                                     |

| Program Memory Type        | SRAM                                                                |

| EEPROM Size                | -                                                                   |

| RAM Size                   | 24K x 16                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 1.98V                                                       |

| Data Converters            | -                                                                   |

| Oscillator Type            | External                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 144-LQFP                                                            |

| Supplier Device Package    | 144-LQFP (20x20)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/dsp56858fve |

|                            |                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Part 1 Overview

### 1.1 56858 Features

### 1.1.1 Digital Signal Processing Core

- Efficient 16-bit engine with dual Harvard architecture

- 120 Million Instructions Per Second (MIPS) at 120MHz core frequency

- Single-cycle 16 × 16-bit parallel Multiplier-Accumulator (MAC)

- Four (4) 36-bit accumulators including extension bits

- 16-bit bidirectional shifter

- Parallel instruction set with unique DSP addressing modes

- Hardware DO and REP loops

- Three (3) internal address buses and one (1) external address bus

- Four (4) internal data buses and one (1) external data bus

- Instruction set supports both DSP and controller functions

- Four (4) hardware interrupt levels

- Five (5) software interrupt levels

- Controller-style addressing modes and instructions for compact code

- Efficient C-Compiler and local variable support

- Software subroutine and interrupt stack with depth limited only by memory

- JTAG/Enhanced OnCE debug programming interface

### 1.1.2 Memory

- Harvard architecture permits up to three (3) simultaneous accesses to program and data memory

- On-Chip Memory

- $-40K \times 16$ -bit Program RAM

- 24K × 16-bit Data RAM

- $-1K \times 16$ -bit Boot ROM

- Off-Chip Memory Expansion (EMI)

- Access up to 2M words of program or 8M data memory (using chip selects)

- Chip Select Logic for glue-less interface to ROM and SRAM

## 1.1.3 56858 Peripheral Circuit Features

- General Purpose 16-bit Quad Timer\*

- Two Serial Communication Interfaces (SCI)\*

- Serial Peripheral Interface (SPI) Port\*

- Two (2) Enhanced Synchronous Serial Interface (ESSI) modules\*

- Computer Operating Properly (COP)/Watchdog Timer

- JTAG/Enhanced On-Chip Emulation (EOnCE) for unobtrusive, real-time debugging

Table 3-1 56858 Signal and Package Information for the 144-pin LQFP and MAPBGA

| Signal<br>Name | BGA<br>Pin No. | LQFP<br>Pin No. | Туре         | Description                                                                                            |

|----------------|----------------|-----------------|--------------|--------------------------------------------------------------------------------------------------------|

| D0             | H7             | 81              | Input/       | Data Bus (D0-D15)—These pins provide the bidirectional data for                                        |

| D1             | G7             | 94              | Output(Z)    | external program or data memory accesses.                                                              |

| D2             | F9             | 95              |              |                                                                                                        |

| D3             | F10            | 96              |              |                                                                                                        |

| D4             | F11            | 97              |              |                                                                                                        |

| D5             | E10            | 98              |              |                                                                                                        |

| D6             | D7             | 120             |              |                                                                                                        |

| D7             | B7             | 121             |              |                                                                                                        |

| D8             | E7             | 122             |              |                                                                                                        |

| D9             | F8             | 123             |              |                                                                                                        |

| D10            | F7             | 124             |              |                                                                                                        |

| D11            | D5             | 137             |              |                                                                                                        |

| D12            | B4             | 138             |              |                                                                                                        |

| D13            | C4             | 142             |              |                                                                                                        |

| D14            | F6             | 143             |              |                                                                                                        |

| D15            | В3             | 144             |              |                                                                                                        |

| RD             | D3             | 8               | Output       | Read Enable (RD) — is asserted during external memory read cycles.                                     |

|                |                |                 |              | This signal is pulled high during reset.                                                               |

| WR             | D4             | 9               | Output       | Write Enable (WR) —is asserted during external memory write cycles.                                    |

|                |                |                 |              | This signal is pulled high during reset.                                                               |

| CS0            | H8             | 83              | Output       | External Chip Select (CS0)—This pin is used as a dedicated GPIO.                                       |

| GPIOA0         |                |                 | Input/Output | Port A GPIO (0) —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage. |

| CS1            | H9             | 84              | Output       | External Chip Select (CS1)—This pin is used as a dedicated GPIO.                                       |

| GPIOA1         |                |                 | Input/Output | Port A GPIO (1) —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage. |

| CS2            | H11            | 85              | Output       | External Chip Select (CS2)—This pin is used as a dedicated GPIO.                                       |

| GPIOA2         |                |                 | Input/Output | Port A GPIO (2) —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage. |

| CS3            | H10            | 86              | Output       | External Chip Select (CS3)—This pin is used as a dedicated GPIO.                                       |

| GPIOA3         |                |                 | Input/Output | Port A GPIO (3)—This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage.  |

Table 3-1 56858 Signal and Package Information for the 144-pin LQFP and MAPBGA

| Signal<br>Name | BGA<br>Pin No. | LQFP<br>Pin No. | Туре                 | Description                                                                                                                                                                                                                                                                                                                                        |

|----------------|----------------|-----------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HACK           | C7             | 119             | Input                | Host Acknowledge (HACK)—When the HI08 is programmed for HRMS=0 functionality (typically used on a single-data-strobe bus), this input has two functions: (1) provide a Host Acknowledge signal for DMA transfers or (2) to control handshaking and provide a Host Interrupt Acknowledge compatible with the MC68000 family processors.             |

|                |                |                 |                      | These pins are disconnected internally during reset.                                                                                                                                                                                                                                                                                               |

| HRRQ           |                |                 | Open Drain<br>Output | Receive Host Request (HRRQ)—This signal is the Receive Host Request output when the HI08 is programmed for HRMS=1 functionality and is typically used on a double-data-strobe bus.                                                                                                                                                                 |

| GPIOB15        |                |                 | Input/Output         | <b>Port B GPIO (15)</b> —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage.                                                                                                                                                                                                                                     |

| TIO0           | В9             | 114             | Input/Output         | Timer Input/Outputs (TIO0)—This pin can be independently configured to be either a timer input source or an output flag.                                                                                                                                                                                                                           |

| GPIOG0         |                |                 | Input/Output         | Port G GPIOG0—This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as an input or output pin.                                                                                                                                                                                                                          |

| TIO1           | C9             | 112             | Input/Output         | Timer Input/Outputs (TIO1)—This pin can be independently configured to be either a timer input source or an output flag.                                                                                                                                                                                                                           |

| GPIOG1         |                |                 | Input/Output         | Port G GPIO (1)—This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as an input or output pin.                                                                                                                                                                                                                        |

| TIO2           | D9             | 111             | Input/Output         | Timer Input/Outputs (TIO2)—This pin can be independently configured to be either a timer input source or an output flag.                                                                                                                                                                                                                           |

| GPIOG2         |                |                 | Input/Output         | Port G GPIO (2)—This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as an input or output pin.                                                                                                                                                                                                                        |

| TIO3           | B10            | 110             | Input/Output         | Timer Input/Outputs (TIO3)—This pin can be independently configured to be either a timer input source or an output flag.                                                                                                                                                                                                                           |

| GPIOG3         |                |                 | Input/Output         | Port G GPIO (3)—This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as an input or output pin.                                                                                                                                                                                                                        |

| ĪRQA           | G2             | 22              | Input                | External Interrupt Request A and B—The IRQA and IRQB inputs                                                                                                                                                                                                                                                                                        |

| ĪRQB           | F5             | 23              |                      | are asynchronous external interrupt requests that indicate that an external device is requesting service. A Schmitt trigger input is used for noise immunity. They can be programmed to be level-sensitive or negative-edge-triggered. If level-sensitive triggering is selected, an external pull-up resistor is required for Wired-OR operation. |

| MODE A         | F4             | 17              | Input                | <b>Mode Select (MODE A)</b> —During the bootstrap process MODE A selects one of the eight bootstrap modes.                                                                                                                                                                                                                                         |

| GPIOH0         |                |                 | Input/Output         | Port H GPIO (0)—This pin is a General Purpose I/O (GPIO) pin after the bootstrap process has completed.                                                                                                                                                                                                                                            |

Table 3-1 56858 Signal and Package Information for the 144-pin LQFP and MAPBGA

| Signal<br>Name | BGA<br>Pin No. | LQFP<br>Pin No. | Туре                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|----------------|-----------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MISO           | B2             | 1               | Input/Output         | SPI Master In/Slave Out (MISO)—This serial data pin is an input to a master device and an output from a slave device. The MISO line of a slave device is placed in the high-impedance state if the slave device is not selected. The driver on this pin can be configured as an open-drain driver by the SPI's Wired-OR mode (WOM) bit when this pin is configured for SPI operation.                                                                                                                                                                                                                                                                  |

| GPIOF0         |                |                 | Input/Output         | Port F GPIO (0)—This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as input or output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MOSI           | C3             | 2               | Input/<br>Output (Z) | SPI Master Out/Slave In (MOSI)—This serial data pin is an output from a master device and an input to a slave device. The master device places data on the MOSI line a half-cycle before the clock edge that the slave device uses to latch the data. The driver on this pin can be configured as an open-drain driver by the SPI's WOM bit when this pin is configured for SPI operation.                                                                                                                                                                                                                                                             |

| GPIOF1         |                |                 | Input/Output         | Port F GPIO (1)—This pin is a General Purpose I/O (GPIO) pin that can be individually programmed as input or output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SCK            | C2             | 3               | Input/Output         | SPI Serial Clock (SCK)—This bidirectional pin provides a serial bit rate clock for the SPI. This gated clock signal is an input to a slave device and is generated as an output by a master device. Slave devices ignore the SCK signal unless the \$\overline{SS}\$ pin is active low. In both master and slave SPI devices, data is shifted on one edge of the SCK signal and is sampled on the opposite edge where data is stable. The driver on this pin can be configured as an open-drain driver by the SPI's WOM bit when this pin is configured for SPI operation. When using Wired-OR mode, the user must provide an external pull-up device. |

| GPIOF2         |                |                 | Input/Output         | Port F GPIO (2)—This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as input or output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SS             | D2             | 4               | Input                | SPI Slave Select (SS)—This input pin selects a slave device before a master device can exchange data with the slave device. SS must be low before data transactions and must stay low for the duration of the transaction. The SS line of the master must be held high.                                                                                                                                                                                                                                                                                                                                                                                |

| GPIOF3         |                |                 | Input/Output         | Port F GPIO (3)—This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as input or output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| XTAL           | H2             | 27              | Input/Output         | Crystal Oscillator Output (XTAL)—This output connects the internal crystal oscillator output to an external crystal. If an external clock source other than a crystal oscillator is used, XTAL must be used as the input.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| EXTAL          | G3             | 28              | Input                | <b>External Crystal Oscillator Input (EXTAL)</b> —This input should be connected to an external crystal. If an external clock source other than a crystal oscillator is used, EXTAL must be tied off. See Section 4.5.2                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CLKO           | L3             | 37              | Output               | Clock Output (CLKO)—This pin outputs a buffered clock signal. When enabled, this signal is the system clock divided by four.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## Table 3-1 56858 Signal and Package Information for the 144-pin LQFP and MAPBGA

| Signal<br>Name | BGA<br>Pin No. | LQFP<br>Pin No. | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|----------------|----------------|-----------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TCK            | L8             | 60              | Input     | <b>Test Clock Input (TCK)</b> —This input pin provides a gated clock to synchronize the test logic and to shift serial data to the JTAG/OnCE port. The pin is connected internally to a pull-down resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| TDI            | K7             | 58              | Input     | <b>Test Data Input (TDI)</b> —This input pin provides a serial input data stream to the JTAG/OnCE port. It is sampled on the rising edge of TCK and has an on-chip pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| TDO            | G6             | 57              | Output(Z) | Test Data Output (TDO)—This tri-statable output pin provides a ser output data stream from the JTAG/Enhanced OnCE port. It is driven the Shift-IR and Shift-DR controller states, and changes on the fallin edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| TMS            | J7             | 59              | Input     | Test Mode Select Input (TMS)—This input pin is used to sequence the JTAG TAP controller's state machine. It is sampled on the rising edge of TCK and has an on-chip pull-up resistor.  Note: Always tie the TMS pin to V <sub>DD</sub> through a 2.2K resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| TRST           | L7             | 56              | Input     | Test Reset (TRST)—As an input, a low signal on this pin provides a reset signal to the JTAG TAP controller. To ensure complete hardware reset, TRST should be asserted whenever RESET is asserted. The only exception occurs in a debugging environment, since the Enhanced OnCE/JTAG module is under the control of the debugger. In this case it is not necessary to assert TRST when asserting RESET. Outside of a debugging environment RESET should be permanently asserted by grounding the signal, thus disabling the Enhanced OnCE/JTAG module on the device.  Note: For normal operation, connect $\overline{\text{TRST}}$ directly to $V_{SS}$ . If the design is to be used in a debugging environment, $\overline{\text{TRST}}$ may be tied to $V_{SS}$ through a 1K resistor. |  |  |  |  |

### Table 4-4 DC Electrical Characteristics (Continued)

$Operating \ Conditions: \ V_{SS} = V_{SSIO} = V_{SSA} = 0 \ V, \ V_{DD} = 1.62 - 1.98 \\ V, \ V_{DDIO} = V_{DDA} = 3.0 - 3.6 \\ V, \ T_{A} = -40^{\circ} \ to \ +120^{\circ} \\ C, \ C_{L} \leq 50 \\ pF, \ f_{op} = 120 \\ MHz = 1.02 - 1.98 \\$

| Characteristic                                                                                             | Symbol                       | Min                     | Тур             | Max             | Unit           |

|------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------|-----------------|-----------------|----------------|

| Input current low (pullups disabled)                                                                       | I <sub>IL</sub>              | -1                      | _               | 1               | μА             |

| Input current high (pullups disabled)                                                                      | I <sub>IH</sub>              | -1                      | _               | 1               | μА             |

| Output tri-state current low                                                                               | I <sub>OZL</sub>             | -10                     | _               | 10              | μА             |

| Output tri-state current high                                                                              | I <sub>OZH</sub>             | -10                     | _               | 10              | μА             |

| Output High Voltage                                                                                        | V <sub>OH</sub>              | V <sub>DDIO</sub> – 0.7 | _               | _               | V              |

| Output Low Voltage                                                                                         | V <sub>OL</sub>              |                         | _               | 0.4             | V              |

| Output High Current                                                                                        | I <sub>OH</sub>              | 8                       | _               | 16              | mA             |

| Output Low Current                                                                                         | I <sub>OL</sub>              | 8                       | _               | 16              | mA             |

| Input capacitance                                                                                          | C <sub>IN</sub>              |                         | 8               | _               | pF             |

| Output capacitance                                                                                         | C <sub>OUT</sub>             | _                       | 12              | _               | pF             |

| $V_{DD}$ supply current (Core logic, memories, peripherals) $Run\ ^{1}$ $Deep\ Stop^{2}$ $Light\ Stop^{3}$ | I <sub>DD</sub> <sup>4</sup> | _<br>_<br>_             | 70<br>0.05<br>5 | 110<br>10<br>14 | mA<br>mA<br>mA |

| V <sub>DDIO</sub> supply current (I/O circuity) Run <sup>5</sup> Deep Stop <sup>2</sup>                    | I <sub>DDIO</sub>            | _                       | 40<br>0         | 50<br>1.5       | mA<br>mA       |

| V <sub>DDA</sub> supply current (analog circuity)  Deep Stop <sup>2</sup>                                  | I <sub>DDA</sub>             | _                       | 60              | 120             | μА             |

| Low Voltage Interrupt <sup>6</sup>                                                                         | V <sub>EI</sub>              | _                       | 2.5             | 2.85            | V              |

| Low Voltage Interrupt Recovery Hysteresis                                                                  | V <sub>EIH</sub>             | _                       | 50              | _               | mV             |

| Power on Reset <sup>7</sup>                                                                                | POR                          | _                       | 1.5             | 2.0             | V              |

**Note:** Run (operating)  $I_{DD}$  measured using external square wave clock source ( $f_{osc}$  = 4MHz) into XTAL. All inputs 0.2V from rail; no DC loads; outputs unloaded. All ports configured as inputs; measured with all modules enabled. PLL set to 240MHz out.

- 1. Running Core, performing 50% NOP and 50% FIR. Clock at 120 MHz.

- 2. Deep Stop Mode Operation frequency = 4 MHz, PLL set to 4 MHz, crystal oscillator and time of day module operating.

- 3. Light Stop Mode Operation frequency = 120 MHz, PLL set to 240 MHz, crystal oscillator and time of day module operating.

- 4. I<sub>DD</sub> includes current for core logic, internal memories, and all internal peripheral logic circuitry.

- 5. Running core and performing external memory access. Clock at 120 MHz.

- 6. When  $V_{DD}$  drops below  $V_{EI}$  max value, an interrupt is generated.

- 7. Power-on reset occurs whenever the digital supply drops below 1.8V. While power is ramping up, this signal remains active for as long as the internal 2.5V is below 1.8V no matter how long the ramp up rate is. The internally regulated voltage is typically 100 mV less than V<sub>DD</sub> during ramp up until 2.5V is reached, at which time it self-regulates.

56858 Technical Data, Rev. 6

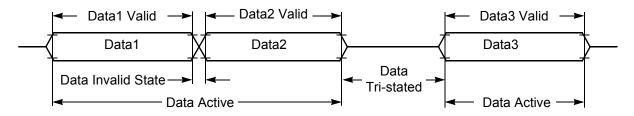

Figure 4-5 shows the definitions of the following signal states:

- Active state, when a bus or signal is driven, and enters a low impedance state

- Tri-stated, when a bus or signal is placed in a high impedance state

- Data Valid state, when a signal level has reached V<sub>OL</sub> or V<sub>OH</sub>

- $\bullet$  Data Invalid state, when a signal level is in transition between  $V_{OL}$  and  $V_{OH}$

Figure 4-5 Signal States

## 4.5 External Clock Operation

The 56858 system clock can be derived from a crystal or an external system clock signal. To generate a reference frequency using the internal oscillator, a reference crystal must be connected between the EXTAL and XTAL pins.

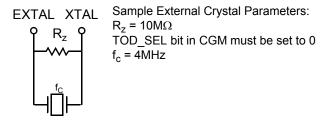

### 4.5.1 Crystal Oscillator

The internal oscillator is designed to interface with a parallel-resonant crystal resonator in the frequency range specified for the external crystal in **Table 4-6.** In **Figure 4-6** a typical crystal oscillator circuit is shown. Follow the crystal supplier's recommendations when selecting a crystal, because crystal parameters determine the component values required to provide maximum stability and reliable start-up. The crystal and associated components should be mounted as close as possible to the EXTAL and XTAL pins to minimize output distortion and start-up stabilization time.

### Crystal Frequency = 2–4MHz (optimized for 4MHz)

Figure 4-6 Crystal Oscillator

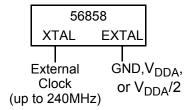

### 4.5.2 High Speed External Clock Source (> 4MHz)

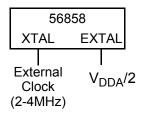

The recommended method of connecting an external clock is given in **Figure 4-7.** The external clock source is connected to XTAL and the EXTAL pin is held at ground,  $V_{DDA}$ , or  $V_{DDA}/2$ . The TOD\_SEL bit in CGM must be set to 0.

Figure 4-7 Connecting a High Speed External Clock Signal using XTAL

### 4.5.3 Low Speed External Clock Source (2-4MHz)

The recommended method of connecting an external clock is given in Figure 4-8. The external clock source is connected to XTAL and the EXTAL pin is held at  $V_{DDA}/2$ . The TOD\_SEL bit in CGM must be set to 0.

Figure 4-8 Connecting a Low Speed External Clock Signal using XTAL

## Table 4-5 External Clock Operation Timing Requirements<sup>4</sup>

$Operating \ Conditions: \ V_{SS} = V_{SSIO} = V_{SSA} = 0 \ V, \ V_{DD} = 1.62 - 1.98 \\ V, \ V_{DDIO} = V_{DDA} = 3.0 - 3.6 \\ V, \ T_{A} = -40^{\circ} \ to \ +120^{\circ} \\ C, \ C_{L} \leq 50 \\ pF, \ f_{op} = 120 \\ MHz = 1.00 \\ MHz = 1$

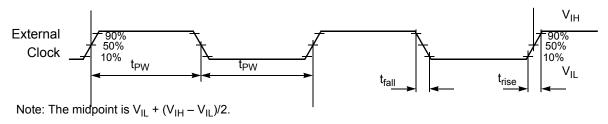

| Characteristic                                              | Symbol            | Min  | Тур | Max | Unit |

|-------------------------------------------------------------|-------------------|------|-----|-----|------|

| Frequency of operation (external clock driver) <sup>1</sup> | f <sub>osc</sub>  | 0    | _   | 240 | MHz  |

| Clock Pulse Width <sup>4</sup>                              | t <sub>PW</sub>   | 6.25 | _   | _   | ns   |

| External clock input rise time <sup>2, 4</sup>              | t <sub>rise</sub> | _    | _   | TBD | ns   |

| External clock input fall time <sup>3, 4</sup>              | t <sub>fall</sub> | _    | _   | TBD | ns   |

- 1. See Figure 4-7 for details on using the recommended connection of an external clock driver.

- 2. External clock input rise time is measured from 10% to 90%.

- 3. External clock input fall time is measured from 90% to 10%.

- 4. Parameters listed are guaranteed by design.

Figure 4-9 External Clock Timing

### **Table 4-6 PLL Timing**

Operating Conditions:  $V_{SS} = V_{SSIO} = V_{SSA} = 0 \text{ V}, V_{DD} = 1.62-1.98 \text{ V}, V_{DDIO} = V_{DDA} = 3.0-3.6 \text{ V}, T_A = -40^{\circ} \text{ to } +120^{\circ} \text{C}, C_L \le 50 \text{pF}, f_{op} = 120 \text{MHz}$

| Characteristic                                                | Symbol            | Min | Тур | Max | Unit |

|---------------------------------------------------------------|-------------------|-----|-----|-----|------|

| External reference crystal frequency for the PLL <sup>1</sup> | f <sub>osc</sub>  | 2   | 4   | 4   | MHz  |

| PLL output frequency                                          | f <sub>clk</sub>  | 40  | _   | 240 | MHz  |

| PLL stabilization time <sup>2</sup>                           | t <sub>plls</sub> | _   | 1   | 10  | ms   |

An externally supplied reference clock should be as free as possible from any phase jitter for the PLL to work correctly.

The PLL is optimized for 4MHz input crystal.

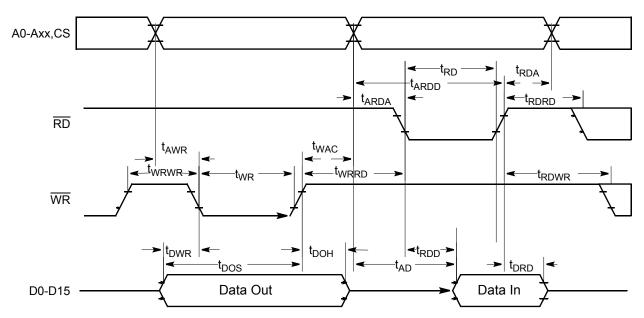

## 4.6 External Memory Interface Timing

The External Memory Interface is designed to access static memory and peripheral devices. **Figure 4-10** shows sample timing and parameters that are detailed in **Table 4-7**.

The timing of each parameter consists of both a fixed delay portion and a clock related portion; as well as user controlled wait states. The equation:

$$t = D + P * (M + W)$$

should be used to determine the actual time of each parameter. The terms in the above equation are defined as:

- t parameter delay time

- D fixed portion of the delay, due to on-chip path delays.

- P the period of the system clock, which determines the execution rate of the part (i.e. when the device is operating at 120 MHz, P = 8.33 ns).

<sup>2.</sup> This is the minimum time required after the PLL setup is changed to ensure reliable operation.

- M Fixed portion of a clock period inherent in the design. This number is adjusted to account for possible clock duty cycle derating.

- W the sum of the applicable wait state controls. See the "Wait State Controls" column of **Table 4-7** for the applicable controls for each parameter. See the EMI chapter of the 83x Peripheral Manual for details of what each wait state field controls.

Some of the parameters contain two sets of numbers. These parameters have two different paths and clock edges that must be considered. Check both sets of numbers and use the smaller result. The appropriate entry may change if the operating frequency of the part changes.

The timing of write cycles is different when WWS = 0 than when WWS > 0. Therefore, some parameters contain two sets of numbers to account for this difference. The "Wait States Configuration" column of **Table 4-7** should be used to make the appropriate selection.

Note: During read-modify-write instructions and internal instructions, the address lines do not change state.

Figure 4-10 External Memory Interface Timing

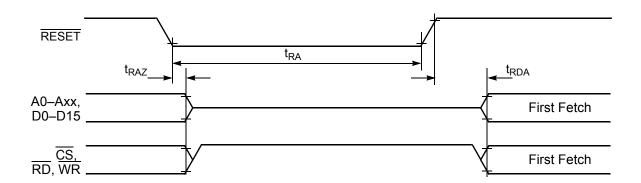

## 4.7 Reset, Stop, Wait, Mode Select, and Interrupt Timing

# Table 4-8 Reset, Stop, Wait, Mode Select, and Interrupt Timing<sup>1, 2</sup>

$Operating \ Conditions: \ V_{SS} = V_{SSIO} = V_{SSA} = 0 \ V, \ V_{DD} = 1.62 - 1.98 \\ V, \ V_{DDIO} = V_{DDA} = 3.0 - 3.6 \\ V, \ T_{A} = -40^{\circ} \ to \ + 120^{\circ} \\ C, \ C_{L} \leq 50 \\ pF, \ f_{op} = 120 \\ MHz = 1.00 \\ MHz =$

| Characteristic                                                                                         | Symbol                                                      | Min          | Max  | Unit     | See Figure  |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------|------|----------|-------------|

| RESET Assertion to Address, Data and Control Signals High Impedance                                    | t <sub>RAZ</sub>                                            | _            | 11   | ns       | Figure 4-11 |

| Minimum RESET Assertion Duration <sup>3</sup>                                                          | t <sub>RA</sub>                                             | 30           | _    | ns       | Figure 4-11 |

| RESET Deassertion to First External Address Output                                                     | t <sub>RDA</sub>                                            | _            | 120T | ns       | Figure 4-11 |

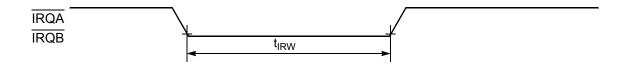

| Edge-sensitive Interrupt Request Width                                                                 | t <sub>IRW</sub>                                            | 1T + 3       | _    | ns       | Figure 4-12 |

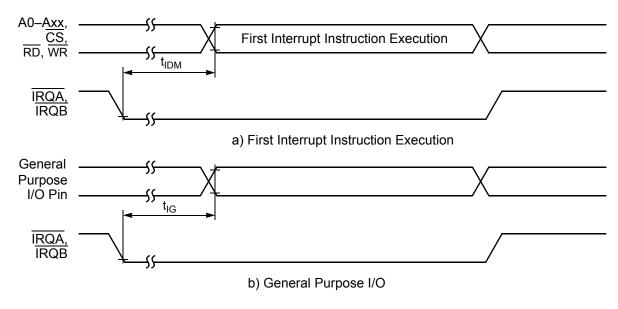

| IRQA, IRQB Assertion to External Data Memory Access Out Valid, caused by first instruction execution   | t <sub>IDM</sub>                                            | 18T          | _    | ns       | Figure 4-13 |

| in the interrupt service routine                                                                       | t <sub>IDM -FAST</sub> 14T — e Output t <sub>IG</sub> 18T — |              |      |          |             |

| IRQA, IRQB Assertion to General Purpose Output Valid, caused by first instruction execution in the     | t <sub>IG</sub>                                             | 18T          | _    | ns       | Figure 4-13 |

| interrupt service routine                                                                              | t <sub>IG -FAST</sub>                                       | 14T          | _    |          |             |

| IRQA Low to First Valid Interrupt Vector Address Out recovery from Wait State <sup>4</sup>             | t <sub>IRI</sub>                                            | 22T          | _    | ns       | Figure 4-14 |

| recovery from wait State                                                                               | t <sub>IRI -FAST</sub>                                      | 18T          | _    |          |             |

| Delay from IRQA Assertion (exiting Stop) to External Data Memory <sup>5</sup>                          | t <sub>IW</sub>                                             | 1.5T         | _    | ns       | Figure 4-15 |

| Delay from IRQA Assertion (exiting Wait) to External Data Memory Fast <sup>6</sup> Normal <sup>7</sup> | t <sub>IF</sub>                                             | 18T<br>22ET  |      | ns<br>ns | Figure 4-15 |

| RSTO pulse width <sup>8</sup> normal operation internal reset mode                                     | t <sub>RSTO</sub>                                           | 128ET<br>8ET | _    |          | Figure 4-16 |

- 1. In the formulas, T = clock cycle. For  $f_{op}$  = 120MHz operation and  $f_{ipb}$  = 60MHz, T = 8.33ns.

- 2. Parameters listed are guaranteed by design.

- 3. At reset, the PLL is disabled and bypassed. The part is then put into Run mode and  $t_{clk}$  assumes the period of the source clock,  $t_{xtal}$ ,  $t_{extal}$  or  $t_{osc}$ .

- 4. The minimum is specified for the duration of an edge-sensitive IRQA interrupt required to recover from the Stop state. This is not the minimum required so that the IRQA interrupt is accepted.

- 5. The interrupt instruction fetch is visible on the pins only in Mode 3.

- 6. Fast stop mode:

- Fast stop recovery applies when external clocking is in use (direct clocking to XTAL) or when fast stop mode recovery is requested (OMR bit 6 is set to 1). In both cases the PLL and the master clock are unaffected by stop mode entry. Recovery takes one less cycle and t<sub>clk</sub> will continue same value it had before stop mode was entered.

- 7. Normal stop mode:

- As a power saving feature, normal stop mode disables and bypasses the PLL. Stop mode will then shut down the master clock, recovery will take an extra cycle (to restart the clock), and t<sub>clk</sub> will resume at the input clock source rate.

- 8. ET = External Clock period, For an external crystal frequency of 8MHz, ET=125 ns.

Figure 4-11 Asynchronous Reset Timing

Figure 4-12 External Interrupt Timing (Negative-Edge-Sensitive)

Figure 4-13 External Level-Sensitive Interrupt Timing

## 4.8 Host Interface Port

$\begin{tabular}{ll} \textbf{Table 4-9 Host Interface Port Timing}^{1} \\ \textbf{Operating Conditions: $V_{SS} = V_{SSIO} = V_{SSA} = 0$ V, $V_{DD} = 1.62-1.98$ V, $V_{DDIO} = V_{DDA} = 3.0-3.6$ V, $T_{A} = -40^{\circ}$ to $+120^{\circ}$C, $C_{L} \le 50$ pF, $f_{op} = 120$ MHz } \\ \end{tabular}$

| Characteristic                                                                                                          | Symbol   | Min         | Max          | Unit     | See Figure   |

|-------------------------------------------------------------------------------------------------------------------------|----------|-------------|--------------|----------|--------------|

| Access time                                                                                                             | TACKDV   | _           | 13           | ns       | 4-17         |

| Disable time                                                                                                            | TACKDZ   | 3           | _            | ns       | 4-17         |

| Time to disassert                                                                                                       | TACKREQH | 3.5         | 9            | ns       | 4-17<br>4-20 |

| Lead time                                                                                                               | TREQACKL | 0           | _            | ns       | 4-17<br>4-20 |

| Access time                                                                                                             | TRADV    | _           | 13           | ns       | 4-18<br>4-19 |

| Disable time                                                                                                            | TRADX    | 5           | _            | ns       | 4-18<br>4-19 |

| Disable time                                                                                                            | TRADZ    | 3           | _            | ns       | 4-18<br>4-19 |

| Setup time                                                                                                              | TDACKS   | 3           | _            | ns       | 4-20         |

| Hold time                                                                                                               | TACKDH   | 1           | _            | ns       | 4-20         |

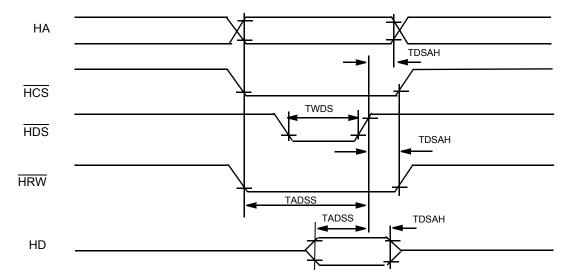

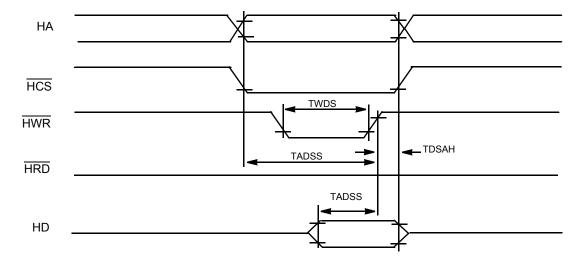

| Setup time                                                                                                              | TADSS    | 3           | _            | ns       | 4-21<br>4-22 |

| Hold time                                                                                                               | TDSAH    | 1           | _            | ns       | 4-21<br>4-22 |

| Pulse width                                                                                                             | TWDS     | 5           | _            | ns       | 4-21<br>4-22 |

| Time to re-assert 1. After second write in 16-bit mode 2. After first write in 16-bit mode or after write in 8-bit mode | TACKREQL | 4T + 5<br>5 | 5T + 9<br>13 | ns<br>ns | 4-19<br>4-20 |

<sup>1.</sup> The formulas: T = clock cycle. f ipb = 60MHz, T = 16.7ns.

39

Figure 4-21 Single Strobe Write Mode

Figure 4-22 Dual Strobe Write Mode

# 4.9 Serial Peripheral Interface (SPI) Timing

# Figure 4-23 SPI Timing <sup>1</sup>

Operating Conditions:  $V_{SS} = V_{SSIO} = V_{SSA} = 0 \text{ V}, V_{DD} = 1.62-1.98 \text{ V}, V_{DDIO} = V_{DDA} = 3.0-3.6 \text{ V}, T_A = -40^{\circ} \text{ to } +120^{\circ}\text{C}, C_L \le 50 \text{pF}, f_{op} = 120 \text{MHz}$

| Characteristic                                                    | Symbol           | Min        | Max          | Unit     | See Figure                |

|-------------------------------------------------------------------|------------------|------------|--------------|----------|---------------------------|

| Cycle time<br>Master<br>Slave                                     | t <sub>C</sub>   | 25<br>25   | =            | ns<br>ns | 4-24, 4-25,<br>4-26, 4-27 |

| Enable lead time<br>Master<br>Slave                               | t <sub>ELD</sub> | <br>12.5   | =            | ns<br>ns | 4-27                      |

| Enable lag time<br>Master<br>Slave                                | t <sub>ELG</sub> | <br>12.5   | _            | ns<br>ns | 4-27                      |

| Clock (SCLK) high time<br>Master<br>Slave                         | t <sub>CH</sub>  | 9<br>12.5  | _            | ns<br>ns | 4-24, 4-25,<br>4-26, 4-27 |

| Clock (SCLK) low time<br>Master<br>Slave                          | t <sub>CL</sub>  | 12<br>12.5 | _            | ns<br>ns | 4-27                      |

| Data set-up time required for inputs<br>Master<br>Slave           | t <sub>DS</sub>  | 10<br>2    | _            | ns<br>ns | 4-24, 4-25,<br>4-26, 4-27 |

| Data hold time required for inputs<br>Master<br>Slave             | t <sub>DH</sub>  | 0<br>2     | _            | ns<br>ns | 4-24, 4-25,<br>4-26, 4-27 |

| Access time (time to data active from high-impedance state) Slave | t <sub>A</sub>   | 5          | 15           | ns<br>ns | 4-27                      |

| Disable time (hold time to high-impedance state) Slave            | t <sub>D</sub>   | 2          | 9            | ns<br>ns | 4-27                      |

| Data valid for outputs<br>Master<br>Slave (after enable edge)     | t <sub>DV</sub>  |            | 2<br>14      | ns<br>ns | 4-24, 4-25,<br>4-26, 4-27 |

| Data invalid<br>Master<br>Slave                                   | t <sub>DI</sub>  | 0          | _            | ns<br>ns | 4-24, 4-25,<br>4-26, 4-27 |

| Rise time<br>Master<br>Slave                                      | t <sub>R</sub>   |            | 11.5<br>10.0 | ns<br>ns | 4-24, 4-25,<br>4-26, 4-27 |

| Fall time<br>Master<br>Slave                                      | t <sub>F</sub>   | _<br>_     | 9.7<br>9.0   | ns<br>ns | 4-24, 4-25,<br>4-26, 4-27 |

<sup>1.</sup> Parameters listed are guaranteed by design.

## 4.10 Quad Timer Timing

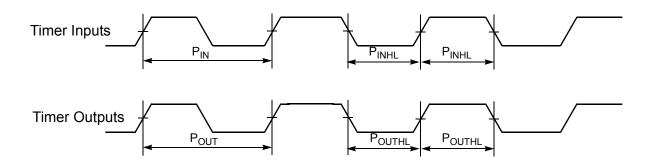

## Table 4-10 Quad Timer Timing<sup>1, 2</sup>

$Operating \ Conditions: \ V_{SS} = V_{SSIO} = V_{SSA} = 0 \ V, \ V_{DD} = 1.62 - 1.98 \\ V, \ V_{DDIO} = V_{DDA} = 3.0 - 3.6 \\ V, \ T_{A} = -40^{\circ} \ to \ +120^{\circ} \\ C, \ C_{L} \leq 50 \\ pF, \ f_{op} = 120 \\ MHz = 1.00 \\ MHz = 1$

| Characteristic               | Symbol             | Min    | Max | Unit |

|------------------------------|--------------------|--------|-----|------|

| Timer input period           | P <sub>IN</sub>    | 2T + 3 | _   | ns   |

| Timer input high/low period  | P <sub>INHL</sub>  | 1T + 3 | _   | ns   |

| Timer output period          | P <sub>OUT</sub>   | 2T - 3 | _   | ns   |

| Timer output high/low period | P <sub>OUTHL</sub> | 1T - 3 | _   | ns   |

- 1. In the formulas listed, T = clock cycle. For  $f_{op}$  = 120MHz operation and fipb = 60MHz, T = 8.33ns.

- 2. Parameters listed are guaranteed by design.

Figure 4-28 Timer Timing

## 4.11 Enhanced Synchronous Serial Interface (ESSI) Timing

### Table 4-11 ESSI Master Mode<sup>1</sup> Switching Characteristics

$Operating \ Conditions: \ V_{SS} = V_{SSIO} = V_{SSA} = 0 \ V, \ V_{DD} = 1.62 - 1.98 V, \ V_{DDIO} = V_{DDA} = 3.0 - 3.6 V, \ T_{A} = -40^{\circ} \ to \ +120^{\circ} C, \ C_{L} \leq 50 pF, \ f_{op} = 120 MHz$

| Parameter                                                  | Symbol              | Min               | Тур | Max             | Units |

|------------------------------------------------------------|---------------------|-------------------|-----|-----------------|-------|

| SCK frequency                                              | fs                  | _                 | _   | 15 <sup>2</sup> | MHz   |

| SCK period <sup>3</sup>                                    | t <sub>SCKW</sub>   | 66.7              |     | _               | ns    |

| SCK high time                                              | t <sub>SCKH</sub>   | 33.4 <sup>4</sup> | _   | _               | ns    |

| SCK low time                                               | t <sub>SCKL</sub>   | 33.4 <sup>4</sup> | _   | _               | ns    |

| Output clock rise/fall time                                |                     |                   | 4   | _               | ns    |

| Delay from SCK high to SC2 (bl) high - Master <sup>5</sup> | t <sub>TFSBHM</sub> | -1.0              | _   | 1.0             | ns    |

56858 Technical Data, Rev. 6

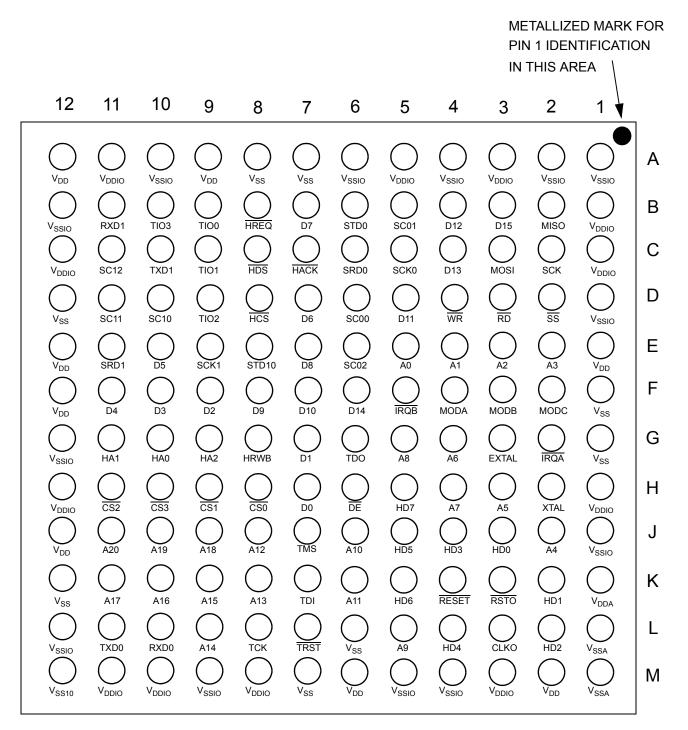

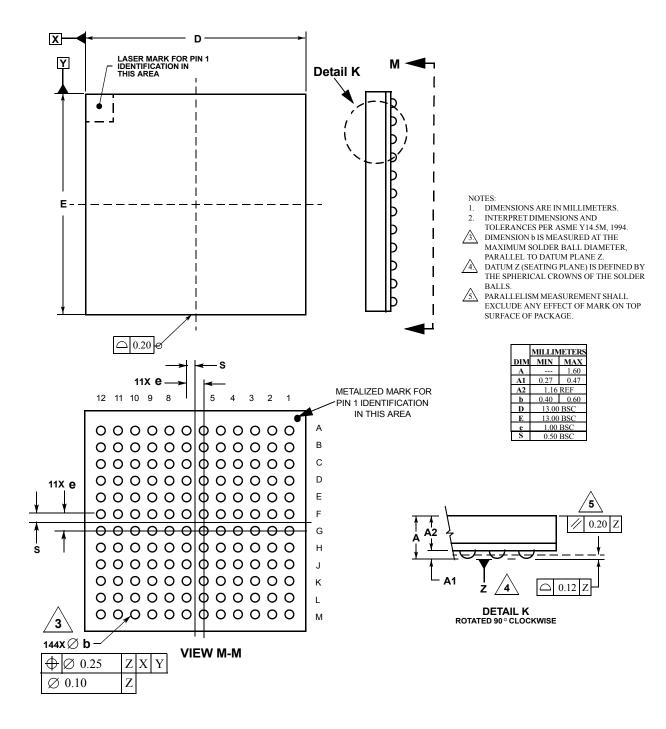

This section contains package and pin-out information for the 144-pin MAPBGA configuration of the 56858.

Figure 5-3 Bottom-View, 56858 144-pin MAPBGA Package

Table 5-2 56858 Pin Identification by Pin Number

| Pin No. | Signal Name | Pin No. | Signal Name       | Pin No. | Signal Name      | Pin No. | Signal Name       |

|---------|-------------|---------|-------------------|---------|------------------|---------|-------------------|

| E5      | A0          | F7      | D10               | D8      | HCS              | A5      | V <sub>DDIO</sub> |

| E4      | A1          | D5      | D11               | J3      | HD0              | A3      | V <sub>DDIO</sub> |

| E3      | A2          | B4      | D12               | K2      | HD1              | C1      | V <sub>DDIO</sub> |

| E2      | А3          | C4      | D13               | L2      | HD2              | M10     | V <sub>DDIO</sub> |

| J2      | A4          | F6      | D14               | J4      | HD3              | D3      | RD                |

| НЗ      | A5          | В3      | D15               | L4      | HD4              | K4      | RESET             |

| G4      | A6          | H6      | DE                | J5      | HD5              | K3      | RSTO              |

| H4      | A7          | G3      | EXTAL             | K5      | HD6              | L10     | RXD0              |

| G5      | A8          | M1      | V <sub>SSA</sub>  | H5      | HD7              | B11     | RXD1              |

| L5      | A9          | L1      | V <sub>SSA</sub>  | C8      | HDS              | D6      | SC00              |

| J6      | A10         | G1      | V <sub>SS</sub>   | В8      | HREQ             | B5      | SC01              |

| K6      | A11         | L6      | V <sub>SS</sub>   | G8      | HRWB             | E6      | SC02              |

| J8      | A12         | D12     | V <sub>SS</sub>   | G2      | ĪRQĀ             | D10     | SC10              |

| K8      | A13         | A7      | V <sub>SS</sub>   | F5      | ĪRQB             | D11     | SC11              |

| L9      | A14         | F1      | V <sub>SS</sub>   | B2      | MISO             | C11     | SC12              |

| K9      | A15         | M7      | V <sub>SS</sub>   | F4      | MODA             | C5      | SCK0              |

| K10     | A16         | K12     | V <sub>SS</sub>   | F3      | MODB             | E9      | SCK1              |

| K11     | A17         | A8      | V <sub>SS</sub>   | F2      | MODC             | C2      | SCK               |

| J9      | A18         | D1      | V <sub>SSIO</sub> | C3      | MOSI             | C6      | SRD0              |

| J10     | A19         | J1      | V <sub>SSIO</sub> | K1      | V <sub>DDA</sub> | E11     | SRD1              |

| J11     | A20         | M5      | V <sub>SSIO</sub> | E1      | V <sub>DD</sub>  | D2      | SS                |

| L3      | CLKO        | M9      | V <sub>SSIO</sub> | M6      | V <sub>DD</sub>  | В6      | STD0              |

| H8      | CS0         | L12     | V <sub>SSIO</sub> | F12     | V <sub>DD</sub>  | E8      | STD1              |

| H9      | CS1         | G12     | V <sub>SSIO</sub> | A9      | V <sub>DD</sub>  | L8      | TCK               |

Figure 5-4 144-pin MAPBGA Mechanical Information

Please see www.freescale.com for the most current case outline.

### How to Reach Us:

### Home Page:

www.freescale.com

### E-mail:

support@freescale.com

### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale ™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc. 2005. All rights reserved.

DSP56858 Rev. 6 01/2007