### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                          |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8052                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 16MHz                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                      |

| Peripherals                | PSM, Temp Sensor, WDT                                           |

| Number of I/O              | 34                                                              |

| Program Memory Size        | 62KB (62K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | 4K x 8                                                          |

| RAM Size                   | 2.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                     |

| Data Converters            | A/D 8x12b; D/A 2x12b                                            |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 56-VFQFN Exposed Pad, CSP                                       |

| Supplier Device Package    | 56-LFCSP-VQ (8x8)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc832bcpz |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Data Sheet**

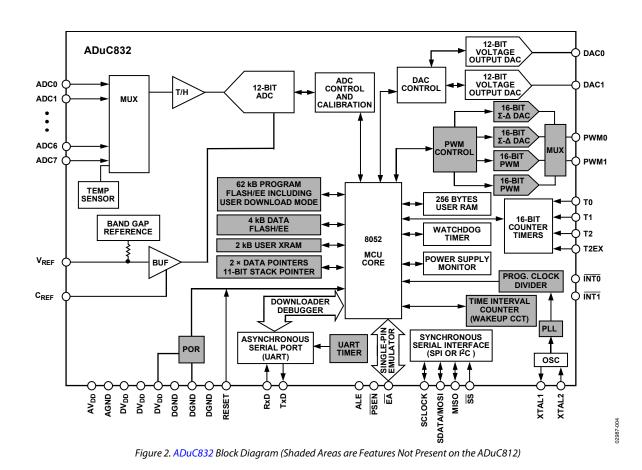

On-chip factory firmware supports in-circuit serial download and debug modes (via UART) as well as single-pin emulation mode via the EA pin. The ADuC832 is supported by QuickStart<sup>™</sup> and QuickStart Plus development systems featuring low cost software and hardware development tools. A functional block diagram of the ADuC832 is shown in Figure 1 with a more detailed block diagram shown in Figure 2.

The part is specified for 3 V and 5 V operation over the extended industrial temperature range and is available in a 52-lead metric quad flat package (MQFP) and a 56-lead lead frame chip scale package (LFCSP).

### **Data Sheet**

# **ADuC832**

| Parameter <sup>1</sup>                   | $V_{DD} = 5 V$ | $V_{DD} = 3 V$ | Unit   | Test Conditions/Comments          |  |

|------------------------------------------|----------------|----------------|--------|-----------------------------------|--|

| Power Supply Currents Power-Down Mode    |                |                |        | Core_CLK = 2.097 MHz or 16.78 MHz |  |

| DV <sub>DD</sub> Current <sup>4</sup>    | 80             | 25             | μA max | Oscillator on                     |  |

|                                          | 38             | 14             | μA typ |                                   |  |

| AV <sub>DD</sub> Current                 | 2              | 1              | μA typ |                                   |  |

| DV <sub>DD</sub> Current                 | 35             | 20             | μA max | Oscillator off                    |  |

|                                          | 25             | 12             | μA typ |                                   |  |

| Typical Additional Power Supply Currents |                |                |        | $AV_{DD} = DV_{DD} = 5 V$         |  |

| PSM Peripheral                           | 50             |                | μA typ |                                   |  |

| ADC                                      | 1.5            |                | mA typ |                                   |  |

| DAC                                      | 150            |                | μA typ |                                   |  |

<sup>1</sup> Temperature range: -40°C to +125°C.

<sup>2</sup> ADC linearity is guaranteed during normal MicroConverter core operation.

<sup>3</sup> ADC LSB size =  $V_{REF}/2^{12}$ , that is, for internal  $V_{REF} = 2.5$  V, 1 LSB = 610  $\mu$ V and for external  $V_{REF} = 1$  V, 1 LSB = 244  $\mu$ V.

<sup>4</sup> Not production tested, but are guaranteed by design and/or characterization data on production release.

<sup>5</sup> Offset error, gain error, offset error match, and gain error match are measured after factory calibration.

<sup>6</sup> Based on external ADC system components, the user may need to execute a system calibration to remove additional external channel errors and achieve these specifications.

<sup>7</sup> SNR calculation includes distortion and noise components.

<sup>8</sup> Channel-to-channel crosstalk is measured on adjacent channels.

<sup>9</sup> The temperature sensor gives a measure of the die temperature directly; air temperature can be inferred from this result.

<sup>10</sup> DAC linearity is calculated using:

Reduced code range of 100 to 4095, 0 V to VREF range.

Reduced code range of 100 to 3945, 0 V to V<sub>DD</sub> range.

DAC output load =  $10 \text{ k}\Omega$  and 100 pF.

$^{11}$  DAC differential nonlinearity specified on 0 V to  $V_{\text{REF}}$  and 0 V to  $V_{\text{DD}}$  ranges.

<sup>12</sup> DAC specification for output impedance in the unbuffered case depends on DAC code.

<sup>13</sup> DAC specifications for I<sub>SNK</sub>, voltage output settling time, and digital-to-analog glitch energy depend on external buffer implementation in unbuffered mode. DAC in unbuffered mode tested with OP270 external buffer, which has a low input leakage current.

<sup>14</sup> Measured with V<sub>REF</sub> and C<sub>REF</sub> pins decoupled with 0.1 µF capacitors to ground. Power-up time for the internal reference is determined by the value of the decoupling capacitor chosen for both the VREF and CREF pins.

15 When using an external reference device, the internal band gap reference input can be bypassed by setting the ADCCON1[6] bit. In this mode, the VREF and CREF pins need to be shorted together for correct operation.

<sup>16</sup> Flash/EE Memory reliability characteristics apply to both the Flash/EE program memory and the Flash/EE data memory.

<sup>17</sup> Endurance is qualified to 100,000 cycles as per JEDEC Std. 22 method A117 and measured at -40°C, +25°C, and +125°C. Typical endurance at 25°C is 700,000 cycles.

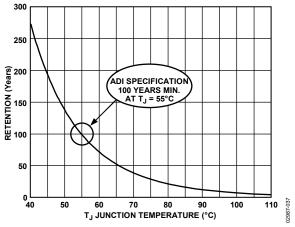

<sup>18</sup> Retention lifetime equivalent at junction temperature (T<sub>2</sub>) = 55°C as per JEDEC Std. 22 Method A117. Retention lifetime based on an activation energy of 0.6 eV

derates with junction temperature as shown in Figure 48 in the ADuC832 Flash/EE Memory Reliability section.

<sup>19</sup> Power supply current consumption is measured in normal, idle, and power-down modes under the following conditions:

Normal mode: RESET = 0.4 V, digital I/O pins = open circuit, Core\_CLK changed via the CD bits in PLLCON[2:0], core executing internal software loop.

Idle mode: RESET = 0.4 V, digital I/O pins = open circuit, Core\_CLK changed via the CD bits in PLLCON, PCON[0] = 1, core execution suspended in idle mode. Power-down mode: RESET = 0.4 V, all Port 0 pins = 0.4 V, all other digital I/O and Port 1 pins are open circuit, Core\_CLK changed via the CD bits in PLLCON, PCON[1] = 1, core execution suspended in power-down mode, oscillator turned on or off via OSC\_PD bit (PLLCON[7]).

<sup>20</sup> DV<sub>DD</sub> power supply current increases typically by 3 mA (3 V operation) and 10 mA (5 V operation) during a Flash/EE memory program or erase cycle.

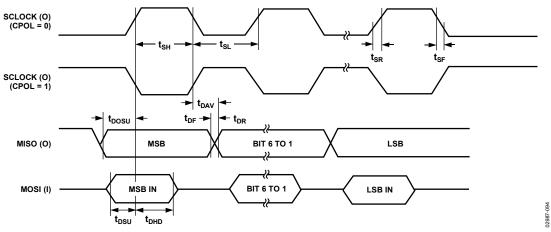

### Table 9. SPI Master Mode Timing (CPHA = 0)

| Parameter <sup>1</sup> | Description                              | Min | Тур | Мах | Unit |

|------------------------|------------------------------------------|-----|-----|-----|------|

| t <sub>sL</sub>        | SCLOCK low pulse width <sup>2</sup>      |     | 476 |     | ns   |

| t <sub>sн</sub>        | SCLOCK high pulse width <sup>2</sup>     |     | 476 |     | ns   |

| t <sub>DAV</sub>       | Data output valid after SCLOCK edge      |     |     | 50  | ns   |

| tDOSU                  | Data output setup before SCLOCK edge     |     |     | 150 | ns   |

| t <sub>DSU</sub>       | Data input setup time before SCLOCK edge | 100 |     |     | ns   |

| t <sub>DHD</sub>       | Data input hold time after SCLOCK edge   | 100 |     |     | ns   |

| t <sub>DF</sub>        | Data output fall time                    |     | 10  | 25  | ns   |

| t <sub>DR</sub>        | Data output rise time                    |     | 10  | 25  | ns   |

| t <sub>sr</sub>        | SCLOCK rise time                         |     | 10  | 25  | ns   |

| t <sub>sF</sub>        | SCLOCK fall time                         |     | 10  | 25  | ns   |

<sup>1</sup> See Figure 11. <sup>2</sup> Characterized under the following conditions: a. Core clock divider bits (CD2, CD1, and CD0 bits in PLLCON SFR) set to 0, 1, and 1, respectively, that is, core clock frequency = 2.09 MHz b. SPI bit rate selection bits (SPR1 and SPR0 bits in SPICON SFR) set to 0 and 0, respectively.

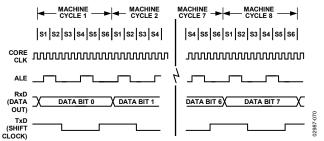

Figure 11. SPI Master Mode Timing (CPHA = 0)

# **Data Sheet**

|                          | Pin  | No.   |      |                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------|------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic                 | MQFP | LFCSP | Туре | Description                                                                                                                                                                                                                                                                                                                                             |

| P3.4/T0/PWMC/PWM0/EXTCLK | 22   | 24    | I/O  | Input/Output Port 3 (P3.4). Port 3 is a bidirectional port with internal pull-up resistors.<br>Port 3 pins that have 1s written to them are pulled high by the internal pull-up<br>resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled<br>externally low sources current because of the internal pull-up resistors. |

|                          |      |       | 1    | Timer/Counter 0 Input (T0).                                                                                                                                                                                                                                                                                                                             |

|                          |      |       | 1    | PWM Clock Input (PWMC).                                                                                                                                                                                                                                                                                                                                 |

|                          |      |       | 0    | PWM0 Voltage Output (PWM0). PWM outputs can be configured to uses<br>Port 2.6 and Port 2.7, or Port 3.4 and Port 3.3.                                                                                                                                                                                                                                   |

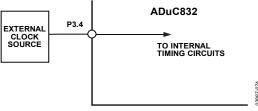

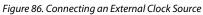

|                          |      |       | I    | Input for External Clock Signal (EXTCLK). This pin must be enabled via the CFG832 register.                                                                                                                                                                                                                                                             |

| P3.5/T1/CONVST           | 23   | 25    | I/O  | Input/Output Port 3 (P3.5). Port 3 is a bidirectional port with internal pull-up resistors.<br>Port 3 pins that have 1s written to them are pulled high by the internal pull-up<br>resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled<br>externally low sources current because of the internal pull-up resistors. |

|                          |      |       | I    | Timer/Counter 1 Input (T1).                                                                                                                                                                                                                                                                                                                             |

|                          |      |       | 1    | Active Low Convert Start Logic Input for the ADC Block When the External Convert<br>Start Function is Enabled (CONVST). A low-to-high transition on this input puts the                                                                                                                                                                                 |

| P3.6/WR                  | 24   | 26    | I/O  | track-and-hold into its hold mode and starts conversion.<br>Input/Output Port 3 (P3.6). Port 3 is a bidirectional port with internal pull-up resistors.                                                                                                                                                                                                 |

| 13.0, WI                 | 27   | 20    | 1/0  | Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled externally low sources current because of the internal pull-up resistors.                                                                                                      |

|                          |      |       | 0    | Write Control Signal, Logic Output (WR). Latches the data byte from Port 0 into the external data memory.                                                                                                                                                                                                                                               |

| P3.7/RD                  | 25   | 27    | 0    | Input/Output Port 3 (P3.7). Port 3 is a bidirectional port with internal pull-up resistors.<br>Port 3 pins that have 1s written to them are pulled high by the internal pull-up<br>resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled<br>externally low sources current because of the internal pull-up resistors. |

|                          |      |       | 0    | Read Control Signal, Logic Output (RD). Enables the external data memory to Port 0.                                                                                                                                                                                                                                                                     |

| SCLOCK                   | 26   | 28    | I/O  | Serial Clock Pin for I <sup>2</sup> C-Compatible or SPI Serial Interface Clock.                                                                                                                                                                                                                                                                         |

| SDATA/MOSI               | 27   | 29    | I/O  | User Selectable, I <sup>2</sup> C-Compatible or SPI Data Input/Output Pin (SDATA).                                                                                                                                                                                                                                                                      |

|                          |      |       | I/O  | SPI Master Output/Slave Input Data I/O Pin for SPI Interface (MOSI).                                                                                                                                                                                                                                                                                    |

| P2.0/A8/A16              | 28   | 30    | I/O  | Input/Output Port 2 (P2.0). Port 2 is a bidirectional port with internal pull-up resistors.<br>Port 2 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 2 pins being pulled externally low sources current because of the internal pull-up resistors.       |

|                          |      |       | I/O  | External Memory Addresses (A8/A16). Port 2 emits the high order address bytes during fetches from external program memory and middle and high order address bytes during accesses to the external 24-bit external data memory space.                                                                                                                    |

| P2.1/A9/A17              | 29   | 31    | I/O  | Input/Output Port 2 (P2.1). Port 2 is a bidirectional port with internal pull-up resistors.<br>Port 2 pins that have 1s written to them are pulled high by the internal pull-up<br>resistors, and in that state can be used as inputs. As inputs, Port 2 pins being pulled<br>externally low sources current because of the internal pull-up resistors. |

|                          |      |       | I/O  | External Memory Addresses (A9/A17). Port 2 emits the high order address bytes during fetches from external program memory and middle and high order address bytes during accesses to the external 24-bit external data memory space.                                                                                                                    |

| P2.2/A10/A18             | 30   | 32    | I/O  | Input/Output Port 2 (P2.2). Port 2 is a bidirectional port with internal pull-up resistors.<br>Port 2 pins that have 1s written to them are pulled high by the internal pull-up<br>resistors, and in that state can be used as inputs. As inputs, Port 2 pins being pulled<br>externally low sources current because of the internal pull-up resistors. |

|                          |      |       | I/O  | External Memory Addresses (A10/A18). Port 2 emits the high order address bytes during fetches from external program memory and middle and high order address bytes during accesses to the external 24-bit external data memory space.                                                                                                                   |

| P2.3/A11/A19             | 31   | 33    | I/O  | Input/Output Port 2 (P2.3). Port 2 is a bidirectional port with internal pull-up resistors.<br>Port 2 pins that have 1s written to them are pulled high by the internal pull-up<br>resistors, and in that state can be used as inputs. As inputs, Port 2 pins being pulled<br>externally low sources current because of the internal pull-up resistors. |

|                          |      |       | I/O  | External Memory Addresses (A11/A19). Port 2 emits the high order address bytes during fetches from external program memory and middle and high order address bytes during accesses to the external 24-bit external data memory space.                                                                                                                   |

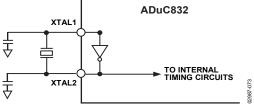

| XTAL1                    | 32   | 34    | 1    | Input to the Inverting Oscillator Amplifier.                                                                                                                                                                                                                                                                                                            |

# ADuC832

|                   | Pir  | n No. |      |                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------|------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic          | MQFP | LFCSP | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                    |

| XTAL2             | 33   | 35    | 0    | Output of the Inverting Oscillator Amplifier.                                                                                                                                                                                                                                                                                                                                                                                  |

| P2.4/A12/A20      | 36   | 39    | I/O  | Input/Output Port 2 (P2.4). Port 2 is a bidirectional port with internal pull-up resistors.<br>Port 2 pins that have 1s written to them are pulled high by the internal pull-up<br>resistors, and in that state can be used as inputs. As inputs, Port 2 pins being pulled<br>externally low sources current because of the internal pull-up resistors.                                                                        |

|                   |      |       | I/O  | External Memory Addresses (A12/A20). Port 2 emits the high order address bytes during fetches from external program memory and middle and high order address bytes during accesses to the external 24-bit external data memory space.                                                                                                                                                                                          |

| P2.5/A13/A21      | 37   | 40    | I/O  | Input/Output Port 2 (P2.5). Port 2 is a bidirectional port with internal pull-up resistors.<br>Port 2 pins that have 1s written to them are pulled high by the internal pull-up<br>resistors, and in that state can be used as inputs. As inputs, Port 2 pins being pulled<br>externally low sources current because of the internal pull-up resistors.                                                                        |

|                   |      |       | I/O  | External Memory Addresses (A13/A21). Port 2 emits the high order address bytes during fetches from external program memory and middle and high order address bytes during accesses to the external 24-bit external data memory space.                                                                                                                                                                                          |

| P2.6/PWM0/A14/A22 | 38   | 41    | I/O  | Input/Output Port 2 (P2.6). Port 2 is a bidirectional port with internal pull-up resistors.<br>Port 2 pins that have 1s written to them are pulled high by the internal pull-up<br>resistors, and in that state can be used as inputs. As inputs, Port 2 pins being pulled<br>externally low sources current because of the internal pull-up resistors.                                                                        |

|                   |      |       | 0    | PWM0 Voltage Output (PWM0). PWM outputs can be configured to use Port 2.6 and Port 2.7 or Port 3.4 and Port 3.3                                                                                                                                                                                                                                                                                                                |

|                   |      |       | I/O  | External Memory Addresses (A14/A22). Port 2 emits the high order address bytes during fetches from external program memory and middle and high order address bytes during accesses to the external 24-bit external data memory space.                                                                                                                                                                                          |

| P2.7/PWM1/A15/A23 | 39   | 42    | I/O  | Input/Output Port 2 (P2.7). Port 2 is a bidirectional port with internal pull-up resistors.<br>Port 2 pins that have 1s written to them are pulled high by the internal pull-up<br>resistors, and in that state can be used as inputs. As inputs, Port 2 pins being pulled<br>externally low sources current because of the internal pull-up resistors.                                                                        |

|                   |      |       | 0    | PWM1 Voltage Output (PWM1). See the ADuC832 Configuration SFR (CFG832) section for further information.                                                                                                                                                                                                                                                                                                                        |

|                   |      |       | I/O  | External Memory Addresses (A15/A23). Port 2 emits the high order address bytes during fetches from external program memory and middle and high order address bytes during accesses to the external 24-bit external data memory space.                                                                                                                                                                                          |

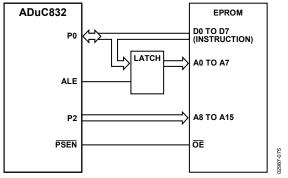

| ĒĀ                | 40   | 43    | I    | External Access Enable, Logic Input. When held high, this input enables the device to fetch code from internal program memory locations 0000H to 1FFFH. When held low, this input enables the device to fetch all instructions from external program memory. This pin should not be left floating.                                                                                                                             |

| PSEN              | 41   | 44    | 0    | Program Store Enable, Logic Output. This output is a control signal that enables the external program memory to the bus during external fetch operations. It is active every six oscillator periods except during external <u>data</u> memory accesses. This pin remains high during internal program execution. PSEN can also be used to enable serial download mode when pulled low through a resistor on power-up or reset. |

| ALE               | 42   | 45    | 0    | Address Latch Enable, Logic Output. This output is used to latch the low byte (and page byte for 24-bit address space accesses) of the address into external memory during normal operation. It is activated every six oscillator periods except during an external data memory access.                                                                                                                                        |

| P0.0/AD0          | 43   | 46    | I/O  | Input/Output Port 0 (P0.0). Port 0 is an 8-Bit Open-Drain Bidirectional I/O Port. Port 0 pins that have 1s written to them float and in that state can be used as high impedance inputs.                                                                                                                                                                                                                                       |

|                   |      |       | I/O  | External Memory Address and Data (AD0). Port 0 is also the multiplexed low order address and data bus during accesses to external program or data memory. In this application, it uses strong internal pull-ups when emitting 1s.                                                                                                                                                                                              |

| P0.1/AD1          | 44   | 47    | I/O  | Input/Output Port 0 (P0.1). Port 0 is an 8-Bit Open-Drain Bidirectional I/O Port. Port 0 pins that have 1s written to them float and in that state can be used as high impedance inputs.                                                                                                                                                                                                                                       |

|                   |      |       | I/O  | External Memory Address and Data (AD1). Port 0 is also the multiplexed low order address and data bus during accesses to external program or data memory. In this application, it uses strong internal pull-ups when emitting 1s.                                                                                                                                                                                              |

# ADuC832

# **EXPLANATION OF TYPICAL PERFORMANCE PLOTS**

The plots presented in the Typical Performance Characteristics section illustrate typical performance of the ADuC832 under various operating conditions.

Figure 16 and Figure 17 show typical ADC integral nonlinearity (INL) errors from ADC Code 0 to Code 4095 at 5 V and 3 V supplies, respectively. The ADC is using its internal reference (2.5 V) and operating at a sampling rate of 152 kHz, and the typically worst-case errors in both plots are slightly less than 0.3 LSBs.

Figure 18 and Figure 19 show the variation in worst-case positive (WCP) INL and worst-case negative (WCN) INL vs. external reference input voltage.

Figure 20 and Figure 21 show typical ADC differential nonlinearity (DNL) errors from ADC Code 0 to Code 4095 at 5 V and 3 V supplies, respectively. The ADC is using its internal reference (2.5 V) and operating at a sampling rate of 152 kHz, and the typically worst-case errors in both plots is slightly less than 0.2 LSBs.

Figure 22 and Figure 23 show the variation in worst-case positive (WCP) DNL and worst-case negative (WCN) DNL vs. external reference input voltage.

Figure 24 shows a histogram plot of 10,000 ADC conversion results on a dc input with  $V_{DD}$  = 5 V. The plot illustrates an

excellent code distribution pointing to the low noise performance of the on-chip precision ADC.

Figure 25 shows a histogram plot of 10,000 ADC conversion results on a dc input for  $V_{DD}$  = 3 V. The plot again illustrates a very tight code distribution of 1 LSB with the majority of codes appearing in one output pin.

Figure 26 and Figure 27 show typical FFT plots for the ADuC832. These plots were generated using an external clock input. The ADC is using its internal reference (2.5 V) sampling a full-scale, 10 kHz sine wave test tone input at a sampling rate of 149.79 kHz. The resultant FFTs shown at 5 V and 3 V supplies illustrate an excellent 100 dB noise floor, 71 dB or greater signal-to-noise ratio (SNR), and THD greater than –80 dB.

Figure 28 and Figure 29 show typical dynamic performance vs. external reference voltages. Again, excellent ac performance can be observed in both plots with some roll-off being observed as  $V_{\text{REF}}$  falls below 1 V.

Figure 30 shows typical dynamic performance vs. sampling frequency. SNR levels of 71 dB are obtained across the sampling range of the ADuC832.

Figure 31 shows the voltage output of the on-chip temperature sensor vs. temperature. Although the initial voltage output at 25°C can vary from part to part, the resulting slope of -2 mV/°C is constant across all parts.

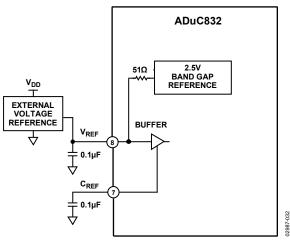

Figure 43. Using an External Voltage Reference

### **CONFIGURING THE ADC**

The successive approximation ADC of the ADuC832 is driven by a divided down version of the master clock. To ensure adequate ADC operation, this ADC clock must be between 400 kHz and 6 MHz, and optimum performance is obtained with ADC clock between 400 kHz and 4.5 MHz. Frequencies within this range can easily be achieved with master clock frequencies from 400 kHz to well above 16 MHz with the four ADC clock divide ratios to choose from. For example, set the ADC clock divide ratio to 4 (that is, ADCCLK = 16.78 MHz/8 = 2 MHz) by setting the appropriate bits in ADCCON1 (ADCCON1[5:4] = 00).

The total ADC conversion time is 15 ADC clocks, plus 1 ADC clock for synchronization, plus the selected acquisition time (one, two, three, or four ADC clocks). For the preceding example, with a three-clock acquisition time, total conversion time is 19 ADC clocks (or 9.05 sec for a 2 MHz ADC clock).

In continuous conversion mode, a new conversion begins each time the previous one finishes. The sample rate is then simply the inverse of the total conversion time previously described. In the preceding example, the continuous conversion mode sample rate would be 110.3 kHz.

If using the temperature sensor as the ADC input, the ADC should be configured to use an ADCCLK of MCLK/32 and four acquisition clocks.

Increasing the conversion time on the temperature sensor channel improves the accuracy of the reading. To further improve the accuracy, an external reference with low temperature drift should also be used.

### ADC DMA MODE

The on-chip ADC is designed to run at a maximum conversion speed of 4  $\mu$ s (247 kSPS sampling rate). When converting at this rate, the ADuC832 MicroConverter<sup>®</sup> has 4  $\mu$ s to read the ADC result and store the result in memory for further postprocessing; otherwise, the next ADC sample may be lost. In an interrupt driven routine, the MicroConverter also has to jump to the ADC

interrupt service routine, which also increases the time required to store the ADC results. In applications where the ADuC832 cannot sustain the interrupt rate, an ADC DMA mode is provided.

To enable DMA mode, Bit 6 in ADCCON2 (DMA) must be set. This allows the ADC results to be written directly to a 16 MB external static memory SRAM (mapped into data memory space) without any interaction from the ADuC832 core. This mode allows the ADuC832 to capture a contiguous sample stream at full ADC update rates (247 kSPS).

### A Typical DMA Mode Configuration Example

To set the ADuC832 into DMA mode, a number of steps must be followed:

- 1. The ADC must be powered down. This is done by ensuring MD1 is set to 0 in ADCCON1.

- 2. The DMA address pointer must be set to the start address of where the ADC results are to be written. This is done by writing to the DMA mode address pointers DMAL, DMAH, and DMAP. DMAL must be written to first, followed by DMAH, and then by DMAP.

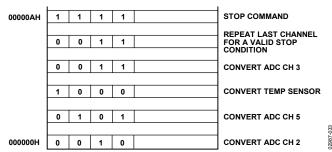

- 3. The external memory must be preconfigured. This consists of writing the required ADC channel IDs into the top four bits of every second memory location in the external SRAM, starting at the first address specified by the DMA address pointer. Because the ADC DMA mode operates independent from the ADuC832 core, it is necessary to provide it with a stop command. This is done by duplicating the last channel ID to be converted, followed by 1111 into the next channel selection field. A typical preconfiguration of external memory is as follows:

Figure 44. Typical DMA External Memory Preconfiguration

- 4. Initiate the DMA by writing to the ADC SFRs in the following sequence:

- a. ADCCON2 is written to enable the DMA mode, that is, MOV ADCCON2, #40H; DMA mode enabled.

- b. ADCCON1 is written to configure the conversion time and power-up of the ADC. It can also enable Timer 2 driven conversions or external triggered conversions if required.

- c. ADC conversions are initiated. This is done by starting single conversions, starting Timer 2, running for Timer 2 conversions, or receiving an external trigger.

### NONVOLATILE FLASH/EE MEMORY Flash/ee memory overview

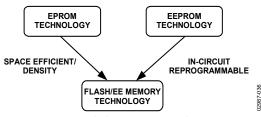

The ADuC832 incorporates Flash/EE memory technology on chip to provide the user with nonvolatile, in-circuit, reprogrammable code and data memory space. Flash/EE memory is a relatively recent type of nonvolatile memory technology and is based on a single transistor cell architecture.

This technology is basically an outgrowth of EPROM technology and was developed through the late 1980s. Flash/EE memory takes the flexible in-circuit reprogrammable features of EEPROM and combines them with the space efficient/density features of EPROM (see Figure 47).

Because Flash/EE technology is based on a single transistor cell architecture, a Flash memory array, like EPROM, can be implemented to achieve the space efficiencies or memory densities required by a given design. Like EEPROM, Flash memory can be programmed in-system at a byte level, although it must first be erased, the erase being performed in page blocks. Thus, Flash memory is often and more correctly referred to as Flash/EE memory.

Figure 47. Flash/EE Memory Development

Overall, Flash/EE memory represents a step closer to the ideal memory device that includes nonvolatility, in-circuit programmability, high density, and low cost. Incorporated in the ADuC832, Flash/EE memory technology allows the user to update program code space in-circuit, without the need to replace one-time programmable (OTP) devices at remote operating nodes.

### FLASH/EE MEMORY AND THE ADUC832

The ADuC832 provides two arrays of Flash/EE memory for user applications. There are 62 kB of Flash/EE program space provided on chip to facilitate code execution without any external discrete ROM device requirements. The program memory can be programmed in-circuit using the serial download mode provided, using conventional third party memory programmers, or via a user defined protocol that can configure it as data if required.

A 4 kB Flash/EE data memory space is also provided on chip. This can be used as a general-purpose nonvolatile scratchpad area. User access to this area is via a group of six SFRs. This space can be programmed at the byte level, although it must first be erased in 4-byte pages.

### ADUC832 FLASH/EE MEMORY RELIABILITY

The Flash/EE program and data memory arrays on the ADuC832 are fully qualified for two key Flash/EE memory characteristics, namely Flash/EE memory cycling endurance and Flash/EE memory data retention.

Endurance quantifies the ability of the Flash/EE memory to be cycled through many program, read, and erase cycles. In real terms, a single Flash/EE memory endurance cycle is composed of the following four independent, sequential events:

- Initial page erase sequence

- Read/verify sequence

- Byte program sequence

- Second read/verify sequence

In reliability qualification, every byte in both the program and data Flash/EE memory is cycled from 00H to FFH until a first fail is recorded, signifying the endurance limit of the on-chip Flash/EE memory.

As indicated in the Specifications section, the ADuC832 Flash/ EE memory endurance qualification has been carried out in accordance with JEDEC Specification A117 over the industrial temperature range of  $-40^{\circ}$ C to  $+25^{\circ}$ C and  $+85^{\circ}$ C to  $+125^{\circ}$ C. The results allow the specification of a minimum endurance value over supply and temperature of 100,000 cycles, with an endurance value of 700,000 cycles being typical of operation at 25°C.

Retention quantifies the ability of the Flash/EE memory to retain its programmed data over time. Again, the ADuC832 has been qualified in accordance with the formal JEDEC retention lifetime specification (A117) at a specific junction temperature ( $T_J = 55^{\circ}$ C). As part of this qualification procedure, the Flash/ EE memory is cycled to its specified endurance limit described previously, before data retention is characterized. This means that the Flash/EE memory is guaranteed to retain its data for its full specified retention lifetime every time the Flash/EE memory is reprogrammed. It should also be noted that retention lifetime, based on an activation energy of 0.6 eV, derates with  $T_J$ , as shown in Figure 48.

Figure 48. Flash/EE Memory Data Retention

### ADUC832 CONFIGURATION SFR (CFG832)

The CFG832 SFR contains the necessary bits to configure the internal XRAM, external clock select, PWM output selection, DAC buffer, and the extended SP. By default, it configures the user into 8051 mode; that is, extended SP is disabled and the internal XRAM is disabled.

### CFG832 (ADuC832 Configuration SFR)

| SFR Address:            | AFH |

|-------------------------|-----|

| Power-On Default Value: | 00H |

| Bit Addressable:        | No  |

### Table 24. CFG832 SFR Bit Designations

| Bit | Name   | Description                                                                                                                                                                                                                                                        |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7] | EXSP   | Extended SP enable.<br>When set to 1 by the user, the stack rolls over from SPH/SP = 00FFH to SPH/SP = 0100H.<br>When set to 0 by the user, the stack rolls over from SP = FFH to SP = 00H.                                                                        |

| [6] | PWPO   | PWM pinout selection.<br>When set to 1 by the user, the PWM output pins are selected as P3.4 and P3.3.<br>When set to 0 by the user, the PWM output pins are selected as P2.6 and P2.7.                                                                            |

| [5] | DBUF   | DAC output buffer.<br>When set to 1 by the user, the DAC output buffer is bypassed.<br>When set to 0 by the user, the DAC output buffer is enabled.                                                                                                                |

| [4] | EXTCLK | Set by the user to 1 to select an external clock input on P3.4.<br>Set by the user to 0 to use the internal PLL clock.                                                                                                                                             |

| [3] | RSVD   | Reserved. This bit should always contain 0.                                                                                                                                                                                                                        |

| [2] | RSVD   | Reserved. This bit should always contain 0.                                                                                                                                                                                                                        |

| [1] | RSVD   | Reserved. This bit should always contain 0.                                                                                                                                                                                                                        |

| [0] | XRAMEN | XRAM enable bit.                                                                                                                                                                                                                                                   |

|     |        | When set to 1 by the user, the internal XRAM is mapped into the lower 2 kB of the external address space.<br>When set to 0 by the user, the internal XRAM is not accessible and the external data memory is mapped into the lower<br>2 kB of external data memory. |

# SERIAL PERIPHERAL INTERFACE

The ADuC832 integrates a complete hardware serial peripheral interface (SPI) on chip. SPI is an industry standard synchronous serial interface that allows eight bits of data to be synchronously transmitted and received simultaneously, that is, full duplex. It should be noted that the SPI pins are shared with the I<sup>2</sup>C pins. Therefore, the user can only enable one or the other interface at any given time (see SPE in Table 28). The SPI port can be configured for master or slave operation and typically consists of four pins: MISO, MOSI, SCLOCK, and SS.

### MISO (MASTER INPUT, SLAVE OUTPUT DATA PIN)

The MISO (master input, slave output) pin is configured as an input line in master mode and an output line in slave mode. The MISO line on the master (data in) should be connected to the MISO line in the slave device (data out). The data is transferred as byte-wide (8-bit) serial data, MSB first.

### **MOSI (MASTER OUTPUT, SLAVE INPUT PIN)**

The MOSI (master output, slave input) pin is configured as an output line in master mode and an input line in slave mode. The MOSI line on the master (data out) should be connected to the MOSI line in the slave device (data in). The data is transferred as byte-wide (8-bit) serial data, MSB first.

### SCLOCK (SERIAL CLOCK I/O PIN)

The master serial clock (SCLOCK) is used to synchronize the data being transmitted and received through the MOSI and MISO data lines. A single data bit is transmitted and received in each SCLOCK period. Therefore, a byte is transmitted/received after eight SCLOCK periods. The SCLOCK pin is configured as an output in master mode and as an input in slave mode. In master mode, the bit rate, polarity, and phase of the clock are controlled by the CPOL, CPHA, SPR0, and SPR1 bits in the

SPICON SFR (see Table 28). In slave mode, the SPICON register must be configured with the phase and polarity (CPHA and CPOL) of the expected input clock. In both master and slave modes, the data is transmitted on one edge of the SCLOCK signal and sampled on the other. It is important therefore that the CPHA and CPOL are configured the same for the master and slave devices.

### **SS** (SLAVE SELECT INPUT PIN)

The slave select  $(\overline{SS})$  input pin is shared with the ADC5 input. To configure this pin as a digital input, the bit must be cleared, for example, CLR P1.5.

This line is active low. Data is only received or transmitted in slave mode when the  $\overline{SS}$  pin is low, allowing the ADuC832 to be used in single master, multislave SPI configurations. If CPHA = 1, then the  $\overline{SS}$  input may be permanently pulled low. With CPHA = 0, the  $\overline{SS}$  input must be driven low before the first bit in a byte-wide transmission or reception, and return high again after the last bit in that byte-wide transmission or reception. In SPI slave mode, the logic level on the external  $\overline{SS}$  pin can be read via the SPR0 bit in the SPICON SFR.

The following SFR registers (SPICON and SPIDAT) are used to control the SPI interface.

### SPICON (SPI Control Register)

| SFR Address:            | F8H |

|-------------------------|-----|

| Power-On Default Value: | 04H |

| Bit Addressable:        | Yes |

| Bit   | Name                                                                                                                    | Description                                                                                                                                                               |                                 |                                                                        |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------------------------------------------------------|--|--|

| [7]   | ISPI                                                                                                                    | SPI interrupt bit. Set by MicroConverter at the end of each SPI transfer. Cleared directly by user code or indirectly by reading the SPIDAT SFR.                          |                                 |                                                                        |  |  |

| [6]   | WCOL                                                                                                                    | Write collision error bit. Set                                                                                                                                            | by MicroConverter if SPIDAT is  | written to while an SPI transfer is in progress. Cleared by user code. |  |  |

| [5]   | SPE                                                                                                                     | SPI interface enable bit. Se                                                                                                                                              | et by user to enable the SPI in | nterface. Cleared by user to enable the I <sup>2</sup> C pins.         |  |  |

| [4]   | SPIM                                                                                                                    | SPI master/slave mode select bit. Set by user to enable Master Mode operation (SCLOCK is an output). Cleared by user to enable slave mode operation (SCLOCK is an input). |                                 |                                                                        |  |  |

| [3]   | CPOL <sup>1</sup>                                                                                                       | Clock polarity select bit. S                                                                                                                                              | et by user if SCLOCK idles hig  | h. Cleared by user if SCLOCK idles low.                                |  |  |

| [2]   | CPHA <sup>1</sup>                                                                                                       | Clock phase select bit. Set by user if leading SCLOCK edge is to transmit data. Cleared by user if trailing SCLOCK edge is to transmit data.                              |                                 |                                                                        |  |  |

| [1:0] | SPR[1:0]                                                                                                                | SPI bit rate select bits. These bits select the SCLOCK rate (bit rate) in master mode as follows:                                                                         |                                 |                                                                        |  |  |

|       |                                                                                                                         | SPR1                                                                                                                                                                      | SPRO                            | Selected Bit Rate                                                      |  |  |

|       |                                                                                                                         | 0                                                                                                                                                                         | 0                               | f <sub>osc</sub> /2                                                    |  |  |

|       |                                                                                                                         | 0                                                                                                                                                                         | 1                               | fosc/4                                                                 |  |  |

|       |                                                                                                                         | 1                                                                                                                                                                         | 0                               | f <sub>osc</sub> /8                                                    |  |  |

|       |                                                                                                                         | 1                                                                                                                                                                         | 1                               | fosc/16                                                                |  |  |

|       | In SPI slave mode, that is, SPIM = 0, the logic level on the external $\overline{SS}$ pin can be read via the SPR0 bit. |                                                                                                                                                                           |                                 |                                                                        |  |  |

### Table 28. SPICON SFR Bit Designations

<sup>1</sup> The CPOL and CPHA bits should both contain the same values for master and slave devices.

# **8052-COMPATIBLE ON-CHIP PERIPHERALS**

This section gives a brief overview of the various secondary peripheral circuits that are also available to the user on chip. These remaining functions are mostly 8052 compatible (with a few additional features) and are controlled via standard 8052 SFR bit definitions.

### PARALLEL I/O

The ADuC832 uses four input/output ports to exchange data with external devices. In addition to performing general-purpose I/O, some ports are capable of external memory operations whereas others are multiplexed with alternate functions for the peripheral features on the device. In general, when a peripheral is enabled, that pin cannot be used as a general-purpose I/O pin.

### PORT 0

Port 0 is an 8-bit, open-drain, bidirectional I/O port that is directly controlled via the Port 0 SFR. Port 0 is also the multiplexed low order address and data bus during accesses to external program or data memory.

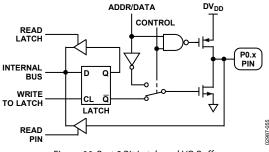

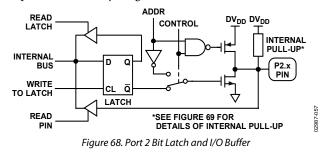

Figure 66 shows a typical bit latch and I/O buffer for a Port 0 port pin. The bit latch (one bit in the port's SFR) is represented as a Type D flip-flop, which clocks in a value from the internal bus in response to a write-to-latch signal from the CPU. The Q output of the flip-flop is placed on the internal bus in response to a read latch signal from the CPU. The level of the port pin itself is placed on the internal bus in response to a read pin signal from the CPU. Some instructions that read a port activate the read latch signal, and others activate the read pin signal. See the Read-Modify-Write Instructions section for more details.

Figure 66. Port 0 Bit Latch and I/O Buffer

As shown in Figure 66, the output drivers of Port 0 pins are switchable to an internal ADDR and ADDR/data bus by an internal control signal for use in external memory accesses. During external memory accesses, 1s are written to the P0 SFR (that is, all of its bit latches become 1). When accessing external memory, the control signal in Figure 66 goes high, enabling push-pull operation of the output pin from the internal address or data bus (ADDR/data line). Therefore, no external pull-ups are required on Port 0 for it to access external memory.

In general-purpose I/O port mode, Port 0 pins that have 1s written to them via the Port 0 SFR are configured as open drain and therefore float. In this state, Port 0 pins can be used as high impedance inputs. This is represented in Figure 66 by the

NAND gate whose output remains high as long as the control signal is low, thereby disabling the top FET. External pull-up resistors are therefore required when Port 0 pins are used as general-purpose outputs. Port 0 pins with 0s written to them drive a logic low output voltage ( $V_{OL}$ ) and are capable of sinking 1.6 mA.

### PORT 1

Port 1 is also an 8-bit port directly controlled via the P1 SFR.

Port 1 digital output capability is not supported on this device.

Port 1 pins can be configured as digital inputs or analog inputs.

By (power-on) default, these pins are configured as analog inputs, that is, 1 written in the corresponding Port 1 register bit. To configure any of these pins as digital inputs, write a 0 to these port bits to configure the corresponding pin as a high impedance digital input.

These pins also have various secondary functions described in Table 34.

| Table 34. Port 1, Alternate Pin F | unctions |

|-----------------------------------|----------|

|-----------------------------------|----------|

| Pin  | Alternate Function                                                          |  |  |

|------|-----------------------------------------------------------------------------|--|--|

| P1.0 | T2 (Timer/Counter 2 external input) or ADC0 (single-<br>ended analog input) |  |  |

| P1.1 | T2EX (Timer/Counter 2 capture/reload trigger) or ADC1                       |  |  |

| P1.5 | SS (slave select for the SPI interface) or ADC5                             |  |  |

|      |                                                                             |  |  |

|      |                                                                             |  |  |

|      |                                                                             |  |  |

|      |                                                                             |  |  |

Figure 67. Port 1 Bit Latch and I/O Buffer

### PORT 2

Port 2 is a bidirectional port with internal pull-up resistors directly controlled via the P2 SFR. Port 2 also emits the high order address bytes during fetches from external program memory and middle and high order address bytes during accesses to the 24-bit external data memory space.

As shown in Figure 68, the output drivers of Port 2 are switchable to an internal ADDR and ADDR/data bus by an internal control signal for use in external memory accesses (as for Port 0). In external memory addressing mode (control = 1), the port pins feature push-pull operation controlled by the internal address bus (ADDR line). However, unlike the P0 SFR during external memory accesses, the P2 SFR remains unchanged.

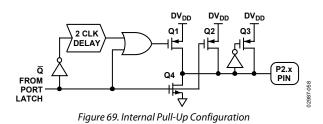

In general-purpose I/O port mode, Port 2 pins that have 1s written to them are pulled high by the internal pull-ups (see Figure 69) and, in that state, can be used as inputs. As inputs, Port 2 pins pulled externally low source current because of the internal pull-up resistors. Port 2 pins with 0s written to

# ADuC832

them drive a logic low output voltage ( $V_{\rm OL}$ ) and are capable of sinking 1.6 mA.

P2.6 and P2.7 can also be used as PWM outputs. If they are selected as the PWM outputs via the CFG832 SFR, the PWM outputs overwrite anything written to P2.6 or P2.7.

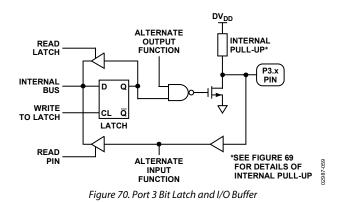

### PORT 3

Port 3 is a bidirectional port with internal pull-ups directly controlled via the P3 SFR. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and, in that state, can be used as inputs. As inputs, Port 3 pins pulled externally low source current because of the internal pull-ups. Port 3 pins with 0s written to them drive a logic low output voltage ( $V_{OL}$ ) and are capable of sinking 4 mA.

Port 3 pins also have various secondary functions described in Table 35. The alternate functions of Port 3 pins can only be activated if the corresponding bit latch in the P3 SFR contains a 1. Otherwise, the port pin is stuck at 0.

| Pin  | Alternate Function                                            |  |  |  |  |

|------|---------------------------------------------------------------|--|--|--|--|

| P3.0 | RxD (UART input pin or serial data I/O in Mode 0)             |  |  |  |  |

| P3.1 | TxD (UART output pin or serial clock output in Mode 0)        |  |  |  |  |

| P3.2 | INT0 (External Interrupt 0)                                   |  |  |  |  |

| P3.3 | INT1 (External Interrupt 1) or PWM1/MISO                      |  |  |  |  |

| P3.4 | T0 (Timer/Counter 0 external input), PWMC, PWM0, or<br>EXTCLK |  |  |  |  |

| P3.5 | T1 (Timer/Counter 1 external input) or CONVST                 |  |  |  |  |

| P3.6 | WR (external data memory write strobe)                        |  |  |  |  |

| P3.7 | RD (external data memory read strobe)                         |  |  |  |  |

P3.3 and P3.4 can also be used as PWM outputs. If they are selected as the PWM outputs via the CFG832 SFR, the PWM outputs overwrite anything written to P3.4 or P3.3.

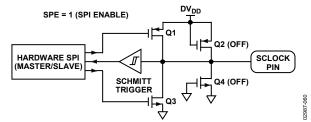

### **ADDITIONAL DIGITAL I/O**

In addition to the port pins, the dedicated SPI/I<sup>2</sup>C pins (SCLOCK and SDATA/MOSI) also feature both input and output functions. Their equivalent I/O architectures are illustrated in Figure 71 and Figure 73, respectively, for SPI operation and in Figure 72 and Figure 74 for I<sup>2</sup>C operation.

Notice that in  $I^2C$  mode (SPE, SPICON[5] = 0), the strong pullup FET (Q1) is disabled, leaving only a weak pull-up (Q2) present. By contrast, in SPI mode (SPE = 1) the strong pull-up FET (Q1) is controlled directly by SPI hardware, giving the pin push-pull capability.

In I<sup>2</sup>C mode (SPE = 0), two pull-down FETs (Q3 and Q4) operate in parallel to provide an extra 60% or 70% of current sinking capability. In SPI mode, however, (SPE = 1) only one of the pull-down FETs (Q3) operates on each pin, resulting in sink capabilities identical to that of Port 0 and Port 2 pins. On the input path of SCLOCK, notice that a Schmitt trigger conditions the signal going to the SPI hardware to prevent false triggers (double triggers) on slow incoming edges. For incoming signals from the SCLOCK and SDATA pins going to I<sup>2</sup>C hardware, a filter conditions the signals in order to reject glitches of up to 50 ns in duration.

Notice also that direct access to the SCLOCK and SDATA/MOSI pins is afforded through the SFR interface in I<sup>2</sup>C master mode. Therefore, if the SPI or I<sup>2</sup>C functions are not used, these two pins can be used to give additional high current digital outputs.

Figure 71. SCLOCK Pin I/O Functional Equivalent in SPI Mode

# TCON (Timer/Counter 0 and Timer/Counter 1 Control Register)

| SFR Address:            | 88H |

|-------------------------|-----|

| Power-On Default Value: | 00H |

| Bit Addressable:        | Yes |

# TIMER/COUNTER 0 AND TIMER/COUNTER 1 DATA REGISTERS

Each timer consists of two 8-bit registers. These can be used as independent registers or combined to be a single 16-bit register, depending on the timer mode configuration.

### TH0 and TL0

TH0 is the Timer 0 high byte and TL0 is the low byte. The SFR addresses for TH0 and TL0 are 8CH and 8AH, respectively.

### TH1 and TL1

TH1 is the Timer 1 high byte and TH0 is the low byte. The SFR addresses for TH1 and TL1 are 8DH and 8BH, respectively.

### Table 37. TCON SFR Bit Designations

| Bit | Name             | Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7] | TF1              | Timer 1 overflow flag.<br>Set by hardware on a Timer/Counter 1 overflow.<br>Cleared by hardware when the program counter (PC) vectors to the interrupt service routine.                                                                                                                                                                                                                                              |

| [6] | TR1              | Timer 1 run control bit.<br>Set by the user to turn on Timer/Counter 1.<br>Cleared by the user to turn off Timer/Counter 1.                                                                                                                                                                                                                                                                                          |

| [5] | TFO              | Timer 0 overflow flag.<br>Set by hardware on a Timer/Counter 0 overflow.<br>Cleared by hardware when the PC vectors to the interrupt service routine.                                                                                                                                                                                                                                                                |

| [4] | TRO              | Timer 0 run control bit.<br>Set by the user to turn on Timer/Counter 0.<br>Cleared by the user to turn off Timer/Counter 0.                                                                                                                                                                                                                                                                                          |

| [3] | IE11             | External Interrupt 1 (INT1) flag.<br>Set by hardware by a falling edge or zero level being applied to external interrupt Pin INT1, depending on the state of Bit IT1.<br>Cleared by hardware when the PC vectors to the interrupt service routine only if the interrupt was transition-activated. If<br>level-activated, the external requesting source controls the request flag, rather than the on-chip hardware. |

| [2] | IT1 <sup>1</sup> | External Interrupt 1 (IE1) trigger type.<br>Set by software to specify edge-sensitive detection (that is, a 1-to-0 transition).<br>Cleared by software to specify level-sensitive detection (that is, zero level).                                                                                                                                                                                                   |

| [1] | IE0 <sup>1</sup> | External Interrupt 0 (INT0) flag.<br>Set by hardware by a falling edge or zero level being applied to external interrupt Pin INT0, depending on the state of Bit IT0.<br>Cleared by hardware when the PC vectors to the interrupt service routine only if the interrupt was transition-activated.<br>If level-activated, the external requesting source controls the request flag, rather than the on-chip hardware. |

| [0] | IT0 <sup>1</sup> | External Interrupt 0 (IE0) trigger type.<br>Set by software to specify edge-sensitive detection (that is, 1-to-0 transition).<br>Cleared by software to specify level-sensitive detection (that is, zero level).                                                                                                                                                                                                     |

<sup>1</sup> These bits are not used in the control of Timer/Counter 0 and Timer/Counter 1, but are used instead in the control and monitoring of the external INT0 and INT1 interrupt pins.

### **TIMER/COUNTER 2**

### **T2CON (TIMER/COUNTER 2 CONTROL REGISTER)**

SFR Address:C8HPower-On Default Value:00HBit Addressable:Yes

**TIMER/COUNTER 2 DATA REGISTERS**

Timer/Counter 2 also has two pairs of 8-bit data registers associated with it. These are used as both timer data registers and timer capture/reload registers.

### TH2 and TL2

TH2 is the Timer 2 data high byte and TL2 is the low byte. The SFR addresses for TH2 and TL2 are CDH and CCH, respectively.

### RCAP2H and RCAP2L

RCAP2H is the Timer 2 capture/reload high byte and RCAP2L is the low byte. The SFR addresses for RCAP2H and RCAP2L are CBH and CAH, respectively.

| Table 38. T2CON SFR Bit Designat | ions |

|----------------------------------|------|

|----------------------------------|------|

| Bit | Name  | Description                                                                                                                                                                                                                                                                                                                                                    |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7] | TF2   | Timer 2 overflow flag.<br>Set by hardware on a Timer 2 overflow. TF2 is not set when either RCLK = 1 or TCLK = 1.<br>Cleared by user software.                                                                                                                                                                                                                 |

| [6] | EXF2  | Timer 2 external flag.<br>Set by hardware when either a capture or reload is caused by a negative transition on T2EX and EXEN2 = 1.<br>Cleared by user software.                                                                                                                                                                                               |

| [5] | RCLK  | Receive clock enable bit.<br>Set by the user to enable the serial port to use Timer 2 overflow pulses for its receive clock in serial port Mode 1 and Mode 3.<br>Cleared by the user to enable Timer 1 overflow to be used for the receive clock.                                                                                                              |

| [4] | TCLK  | Transmit clock enable bit.<br>Set by the user to enable the serial port to use Timer 2 overflow pulses for its transmit clock in serial port Mode 1 and<br>Mode 3. Cleared by the user to enable Timer 1 overflow to be used for the transmit clock.                                                                                                           |

| [3] | EXEN2 | Timer 2 external enable flag.<br>Set by the user to enable a capture or reload to occur as a result of a negative transition on T2EX if Timer 2 is not being used<br>to clock the serial port.<br>Cleared by the user for Timer 2 to ignore events at T2EX.                                                                                                    |

| [2] | TR2   | Timer 2 start/stop control bit.<br>Set by the user to start Timer 2.<br>Cleared by the user to stop Timer 2.                                                                                                                                                                                                                                                   |

| [1] | CNT2  | Timer 2 timer or counter function select bit.<br>Set by the user to select counter function (input from external T2 pin).<br>Cleared by the user to select timer function (input from on-chip core clock).                                                                                                                                                     |

| [0] | CAP2  | Timer 2 capture/reload select bit.<br>Set by the user to enable captures on negative transitions at T2EX if EXEN2 = 1.<br>Cleared by the user to enable autoreloads with Timer 2 overflows or negative transitions at T2EX when EXEN2 = 1. When<br>either RCLK = 1 or TCLK = 1, this bit is ignored and the timer is forced to autoreload on Timer 2 overflow. |

# **UART SERIAL INTERFACE**

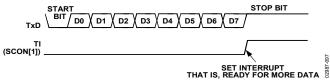

The serial port is full duplex, meaning it can transmit and receive simultaneously. It is also receive-buffered, meaning it can commence reception of a second byte before a previously received byte has been read from the receive register. However, if the first byte still has not been read by the time reception of the second byte is complete, the first byte is lost. The physical interface to the serial data network is via the RXD and TXD pins, and the SFR interface to the UART is comprised of SBUF and SCON.

### SBUF

The serial port receive and transmit registers are both accessed through the SBUF SFR (SFR address = 99H). Writing to SBUF loads the transmit register and reading SBUF accesses a physically separate receive register.

### SCON (UART SERIAL PORT CONTROL REGISTER)

| SFR Address:            | 98H |

|-------------------------|-----|

| Power-On Default Value: | 00H |

| Bit Addressable:        | Yes |

### Table 40. SCON SFR Bit Designations

| Bit   | Name    | Description                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                               |  |  |  |  |

|-------|---------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| [7:6] | SM[0:1] | [0:1] UART serial mode select bits. These bits select the serial port operating mode as follows: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                               |  |  |  |  |

|       |         | SM0                                                                                              | SM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Selected Operating Mode                                                                       |  |  |  |  |