Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c62b-04-sp |

#### 2.2.2.5 PIR1 REGISTER

This register contains the individual flag bits for the Peripheral interrupts.

Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-5: PIR1 REGISTER (ADDRESS 0Ch)

| U-0      | R/W-0                                                    | U-0       | U-0       | R/W-0     | R/W-0        | R/W-0       | R/W-0  |                                                                            |

|----------|----------------------------------------------------------|-----------|-----------|-----------|--------------|-------------|--------|----------------------------------------------------------------------------|

| _        | ADIF <sup>(1)</sup>                                      | 1         | 1         | SSPIF     | CCP1IF       | TMR2IF      | TMR1IF | R = Readable bit                                                           |

| bit7     |                                                          |           |           |           |              |             | bit0   | W = Writable bit U = Unimplemented bit, read as '0' n = Value at POR reset |

| bit 7:   | Unimpler                                                 | nented: R | ead as '0 | ,         |              |             |        |                                                                            |

| bit 6:   | <b>ADIF</b> <sup>(1)</sup> : A<br>1 = An A/<br>0 = The A | D convers | ion compl | eted (mus | t be cleared | d in softwa | re)    |                                                                            |

| bit 5-4: | Unimpler                                                 | nented: R | ead as '0 | ,         |              |             |        |                                                                            |

Note:

- SSPIF: Synchronous Serial Port Interrupt Flag bit bit 3:

- 1 = The transmission/reception is complete (must be cleared in software)

- 0 = Waiting to transmit/receive

- CCP1IF: CCP1 Interrupt Flag bit bit 2:

#### Capture Mode

- 1 = A TMR1 register capture occurred (must be cleared in software)

- 0 = No TMR1 register capture occurred

#### Compare Mode

- 1 = A TMR1 register compare match occurred (must be cleared in software)

- 0 = No TMR1 register compare match occurred

#### **PWM Mode**

Unused in this mode

- bit 1: TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

- 1 = TMR2 to PR2 match occurred (must be cleared in software)

- 0 = No TMR2 to PR2 match occurred

- bit 0: TMR1IF: TMR1 Overflow Interrupt Flag bit

- 1 = TMR1 register overflowed (must be cleared in software)

- 0 = TMR1 register did not overflow

- Note 1: The PIC16C62B does not have an A/D module. This bit location is reserved on these devices. Always maintain this bit clear.

### PIC16C62B/72A

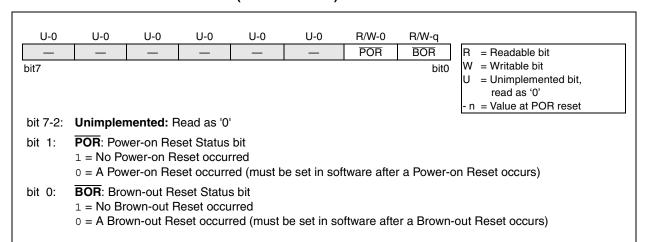

#### 2.2.2.6 PCON REGISTER

The Power Control register (PCON) contains flag bits to allow differentiation between a Power-on Reset (POR), Brown-Out Reset (BOR) and resets from other sources. .

Note: On Power-on Reset, the state of the BOR bit is unknown and is not predictable.

If the BODEN bit in the configuration word is set, the user must first set the BOR bit on a POR, and check it on subsequent resets.

If BOR is cleared while POR remains set, a Brown-out reset has occurred.

If the BODEN bit is clear, the BOR bit may be ignored.

#### REGISTER 2-6: PCON REGISTER (ADDRESS 8Eh)

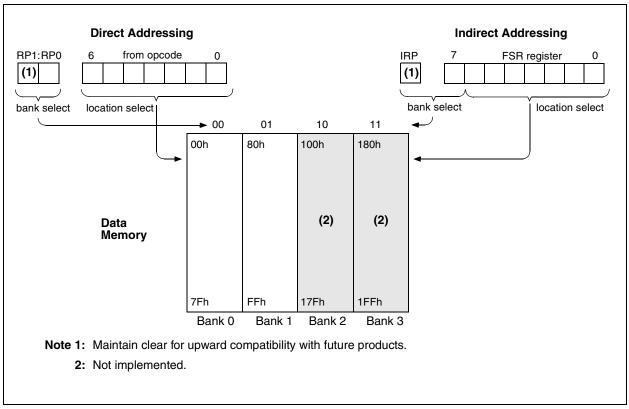

# 2.5 <u>Indirect Addressing, INDF and FSR</u> <u>Registers</u>

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a pointer).

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-1.

# EXAMPLE 2-1: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

movlw 0x20 ;initialize pointer

movwf FSR ; to RAM

NEXT clrf INDF ;clear INDF register

incf FSR ;inc pointer

btfss FSR,4 ;all done?

goto NEXT ;NO, clear next

CONTINUE

: ;YES, continue

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-3. However, IRP is not used in the PIC16C62B/72A.

#### FIGURE 2-3: DIRECT/INDIRECT ADDRESSING

#### 3.0 I/O PORTS

Some I/O port pins are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the  $PIC^{@}$  MCU Mid-Range Reference Manual, (DS33023).

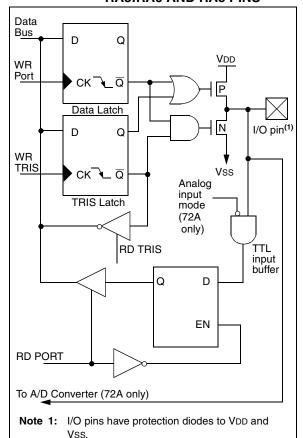

#### 3.1 PORTA and the TRISA Register

PORTA is a 6-bit wide bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (=1) will make the corresponding PORTA pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISA bit (=0) will make the corresponding PORTA pin an output, (i.e., put the contents of the output latch on the selected pin).

The PORTA register reads the state of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

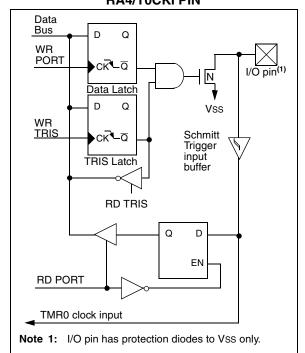

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

Pin RA5 is multiplexed with the SSP to become the RA5/SS pin.

On the PIC16C72A device, other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

**Note:** On a Power-on Reset, pins with analog functions are configured as analog inputs with digital input buffers disabled. A digital read of these pins will return '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

# FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

FIGURE 3-2: BLOCK DIAGRAM OF RA4/T0CKI PIN

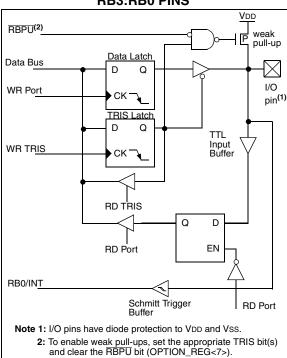

#### 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an input, (i.e., put the corresponding output driver in a hi-impedance mode). Clearing a TRISB bit (=0) will make the corresponding PORTB pin an output, (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

**FIGURE 3-3: BLOCK DIAGRAM OF RB3:RB0 PINS**

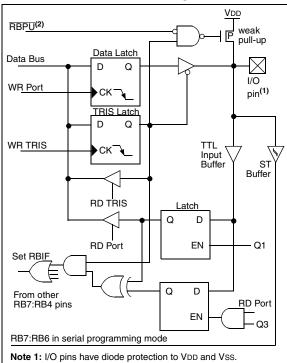

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- Any read or write of PORTB. This will end the mismatch condition.

- Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

RB0/INT is an external interupt pin and is configured using the INTEDG bit (OPTION\_REG<6>). RB0/INT is discussed in detail in Section 10.10.1.

FIGURE 3-4: **BLOCK DIAGRAM OF RB7:RB4 PINS**

2: To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (OPTION\_REG<7>).

## PIC16C62B/72A

TABLE 3-3 PORTB FUNCTIONS

| Name    | Bit# | Buffer                | Function                                                                                                            |

|---------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming data.  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

### TABLE 3-4 SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name       | Bit 7   | Bit 6          | Bit 5     | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|------------|---------|----------------|-----------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 06h     | PORTB      | RB7     | RB6            | RB5       | RB4   | RB3   | RB2   | RB1   | RB0   | xxxx xxxx                | uuuu uuuu                 |

| 86h     | TRISB      | PORTB I | Data Direction | on Regist | er    |       |       |       |       | 1111 1111                | 1111 1111                 |

| 81h     | OPTION_REG | RBPU    | INTEDG         | T0CS      | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

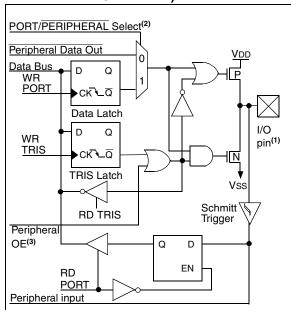

#### 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (=1) will make the corresponding PORTC pin an input, (i.e., put the corresponding output driver in a hi-impedance mode). Clearing a TRISC bit (=0) will make the corresponding PORTC pin an output, (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override maybe in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

FIGURE 3-5: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

- Note 1: I/O pins have diode protection to VDD and Vss.

- 2: Port/Peripheral select signal selects between port data and peripheral output.

- **3:** Peripheral OE (output enable) is only activated if peripheral select is active.

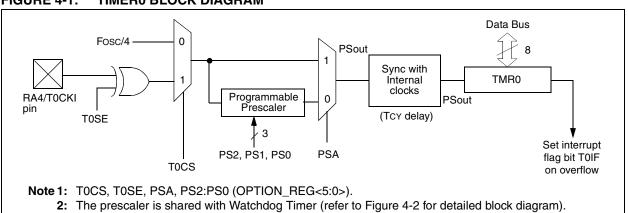

#### 4.0 TIMERO MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Read and write

- INT on overflow

- · 8-bit software programmable prescaler

- · INT or EXT clock select

- EXT clock edge select

Figure 4-1 is a simplified block diagram of the Timer0 module.

Additional information on timer modules is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

#### 4.1 <u>Timer0 Operation</u>

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization. Additional information on external clock requirements is available in the Electrical Specifications section of this manual, and in the PIC® MCU Mid-Range Reference Manual, (DS33023).

#### 4.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 4-2). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. There is only one prescaler available which is shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The prescaler is not readable or writable.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

Setting bit PSA will assign the prescaler to the Watchdog Timer (WDT). When the prescaler is assigned to the WDT, prescale values of 1:1, 1:2, ..., 1:128 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

**Note:** Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment or ratio.

FIGURE 4-1: TIMERO BLOCK DIAGRAM

### PIC16C62B/72A

#### 8.3.1.1 ADDRESSING

Once the SSP module has been enabled, it waits for a START condition to occur. Following the START condition, 8 bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The buffer full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) on the falling edge of the ninth SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal

'1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7- 9 for slave-transmitter:

- Receive first (high) byte of Address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of Address (clears bit UA and releases the SCL line).

- Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- Receive second (low) byte of Address (bits SSPIF, BF, and UA are set).

- Update the SSPADD register with the first (high) byte of Address, if match releases SCL line, this will clear bit UA.

- Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive repeated START condition.

- Receive first (high) byte of Address (bits SSPIF and BF are set).

- Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

TABLE 8-2 DATA TRANSFER RECEIVED BYTE ACTIONS

|    | ts as Data<br>s Received |                    |                    | Set bit SSPIF                     |

|----|--------------------------|--------------------|--------------------|-----------------------------------|

| BF | SSPOV                    | $SSPSR \to SSPBUF$ | Generate ACK Pulse | (SSP Interrupt occurs if enabled) |

| 0  | 0                        | Yes                | Yes                | Yes                               |

| 1  | 0                        | No                 | No                 | Yes                               |

| 1  | 1                        | No                 | No                 | Yes                               |

| 0  | 1                        | Yes                | No                 | Yes                               |

Note: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

#### 10.2 Oscillator Configurations

#### 10.2.1 OSCILLATOR TYPES

The PIC16CXXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

LP Low Power CrystalXT Crystal/Resonator

HS High Speed Crystal/Resonator

RC Resistor/Capacitor

### 10.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

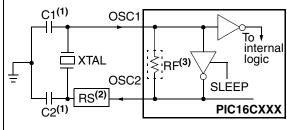

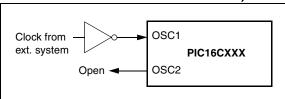

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 10-2). The PIC16CXXX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can use an external clock source to drive the OSC1/CLKIN pin (Figure 10-3).

FIGURE 10-2: CRYSTAL/CERAMIC

RESONATOR OPERATION

(HS, XT OR LP

OSC CONFIGURATION)

**Note1:** See Table 10-1 and Table 10-2 for recommended values of C1 and C2.

- A series resistor (RS) may be required for AT strip cut crystals.

- 3: RF varies with the crystal chosen.

FIGURE 10-3: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

TABLE 10-1 CERAMIC RESONATORS

| Ranges Tested: |                                                |                      |             |  |

|----------------|------------------------------------------------|----------------------|-------------|--|

| Mode           | Freq                                           | OSC1                 | O\$C2       |  |

| XT             | 455 kHz                                        | 68 - 100 pF          | 68 - 100 pF |  |

|                | 2.0 MHz                                        | 15 - 68 pF 🤇         | 15 - 68 pF  |  |

|                | 4.0 MHz                                        | 15 - 68 pF           | 15 - 68 pF  |  |

| HS             | 8.0 MHz                                        | 10 - 68/pF           | 10 - 68 pF  |  |

|                | 16.0 MHz                                       | 10,-22.pF            | 10 - 22 pF  |  |

| The            | These values are for design guidance only. See |                      |             |  |

|                | es at bottom of                                |                      |             |  |

| Resonator      | rs Used: 🚫                                     |                      |             |  |

| 455 kHz        | Panasonie E                                    | FO-A455K04B          | ± 0.3%      |  |

| 2.0 MHz        | Murata Erie (                                  | CSA2.00MG            | ± 0.5%      |  |

| 4.0 MHz        | Murata Erie CSA4.00MG ± 0.5%                   |                      |             |  |

| 8.0 MHz        | Murata Erie CSA8.00MT ± 0.5%                   |                      |             |  |

| 16.0 MHz       | Murata Erie CSA16.00MX ± 0.5%                  |                      |             |  |

| Resona         | ators did not hav                              | ve built-in capacito | ors.        |  |

TABLE 10-2 CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq | Cap. Range<br>C1           | Cap. Range<br>C2 |

|----------|-----------------|----------------------------|------------------|

| LP       | 32 kHz          | 33 pF                      | 33 pF            |

|          | 200 kHz         | 15 pF                      | 15/AF            |

| XT       | 200 kHz         | 47-68 pF                   | 47-68 pF         |

|          | 1 MHz           | 15 pF <                    | √ 15 pF          |

|          | 4 MHz           | 15 pF                      | 15 pF            |

| HS       | 4 MHz           | 15 pt                      | 15 pF            |

|          | 8 MHz           | 15-33 pE                   | 15-33 pF         |

|          | 20 MHz          | 15-33 pF                   | 15-33 pF         |

|          | values are      | for design guidar<br>page. | nce only. See    |

|          | Crys            | tals Used                  |                  |

| 32 kHz   | Epson C-00      | )1R32.768K-A               | ± 20 PPM         |

| 200 kHz  | SÝÓ XTL 2       | 00.000KHz                  | ± 20 PPM         |

| 1 MHz    | ECS ECS-1       | 10-13-1                    | ± 50 PPM         |

| 4 MHz    | ECS ECS-4       | 10-20-1                    | ± 50 PPM         |

| 8 MHz    | EPSON CA        | -301 8.000M-C              | ± 30 PPM         |

| 20 MHz   | EPSON CA        | x-301 20.000M-C            | ± 30 PPM         |

- **Note 1:** Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- **3:** Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- 4: Oscillator performance should be verified when migrating between devices (including PIC16C62A to PIC16C62B and PIC16C72 to PIC16C72A)

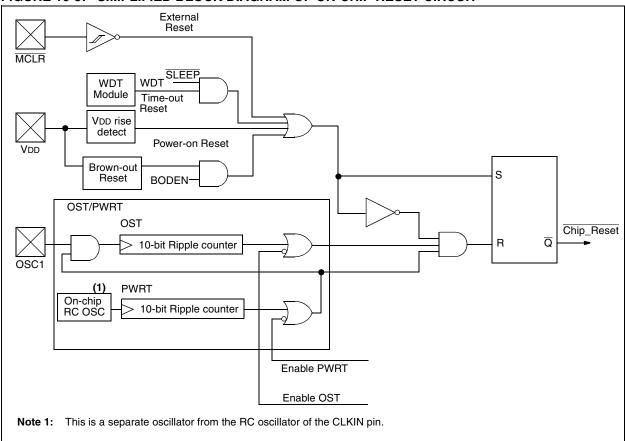

### FIGURE 10-5: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

TABLE 10-6 INITIALIZATION CONDITIONS FOR ALL REGISTERS

| Register             | Appli<br>Dev | cable<br>ices | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|----------------------|--------------|---------------|------------------------------------|--------------------------|---------------------------------|

| W                    | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| INDF                 | 62B          | 72A           | N/A                                | N/A                      | N/A                             |

| TMR0                 | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCL                  | 62B          | 72A           | 0000h                              | 0000h                    | PC + 1 <b>(2)</b>               |

| STATUS               | 62B          | 72A           | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu(3)                    |

| FSR                  | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PORTA <sup>(4)</sup> | 62B          | 72A           | 0x 0000                            | 0u 0000                  | uu uuuu                         |

| PORTB <sup>(5)</sup> | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PORTC <sup>(5)</sup> | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCLATH               | 62B          | 72A           | 0 0000                             | 0 0000                   | u uuuu                          |

| INTCON               | 62B          | 72A           | 0000 000x                          | 0000 000u                | uuuu uuuu(1)                    |

| DID4                 | 62B          | 72A           | 0000                               | 0000                     | uuuu(1)                         |

| PIR1                 | 62B          | 72A           | -0 0000                            | -0 0000                  | -u uuuu(1)                      |

| TMR1L                | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| TMR1H                | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| T1CON                | 62B          | 72A           | 00 0000                            | uu uuuu                  | uu uuuu                         |

| TMR2                 | 62B          | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| T2CON                | 62B          | 72A           | -000 0000                          | -000 0000                | -uuu uuuu                       |

| SSPBUF               | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| SSPCON               | 62B          | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| CCPR1L               | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR1H               | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCP1CON              | 62B          | 72A           | 00 0000                            | 00 0000                  | uu uuuu                         |

| ADRES                | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON0               | 62B          | 72A           | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |

| OPTION_REG           | 62B          | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISA                | 62B          | 72A           | 11 1111                            | 11 1111                  | uu uuuu                         |

| TRISB                | 62B          | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISC                | 62B          | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| DIE                  | 62B          | 72A           | 0000                               | 0000                     | uuuu                            |

| PIE1                 | 62B          | 72A           | -0 0000                            | -0 0000                  | -u uuuu                         |

| PCON                 | 62B          | 72A           | 0q                                 | uq                       | uq                              |

| PR2                  | 62B          | 72A           | 1111 1111                          | 1111 1111                | 1111 1111                       |

| SSPADD               | 62B          | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| SSPSTAT              | 62B          | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| ADCON1               | 62B          | 72A           | 000                                | 000                      | uuu                             |

$\mbox{Legend:} \quad \mbox{$u$} \ = \mbox{unchanged,} \quad \mbox{$x$} \ = \mbox{unknown,} \quad \mbox{$-$=$ unimplemented bit, read as '0', $q$ = value depends on condition }$

Note 1: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

<sup>2:</sup> When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

<sup>3:</sup> See Table 10-5 for reset value for specific condition.

<sup>4:</sup> On any device reset, these pins are configured as inputs.

<sup>5:</sup> This is the value that will be in the port output latch.

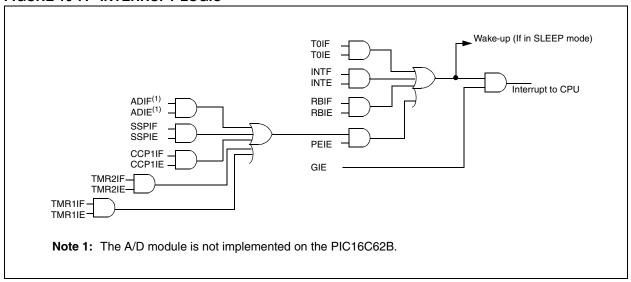

#### 10.10 Interrupts

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

Note: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

A global interrupt enable bit, GIE (INTCON<7>) enables or disables all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt flag bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit, which reenables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupts, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine, the source of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles, depending on when the interrupt event occurs. The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit

#### FIGURE 10-7: INTERRUPT LOGIC

| COMF             | Complement f                                                                                                                                   | GOTO             | Unconditional Branch                                                                                                                                                              |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] COMF f,d                                                                                                                             | Syntax:          | [ label ] GOTO k                                                                                                                                                                  |

| Operands:        | $0 \leq f \leq 127$                                                                                                                            | Operands:        | $0 \leq k \leq 2047$                                                                                                                                                              |

|                  | $d \in [0,1]$                                                                                                                                  | Operation:       | $k \rightarrow PC < 10:0 >$                                                                                                                                                       |

| Operation:       | $(\bar{f}) \to (destination)$                                                                                                                  |                  | $PCLATH<4:3> \rightarrow PC<12:11>$                                                                                                                                               |

| Status Affected: | Z                                                                                                                                              | Status Affected: | None                                                                                                                                                                              |

| Description:     | The contents of register 'f' are complemented. If 'd' is 0, the result is stored in W. If 'd' is 1, the result is stored back in register 'f'. | Description:     | GOTO is an unconditional branch. The eleven bit immediate value is loaded into PC bits <10:0>. The upper bits of PC are loaded from PCLATH<4:3>. GOTO is a two cycle instruction. |

| DECF             | Decrement f                                                                                                                          | INCF             | Increment f                                                                                                                                                |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECF f,d                                                                                                                     | Syntax:          | [ label ] INCF f,d                                                                                                                                         |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                   | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                         |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                  | Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                        |

| Status Affected: | Z                                                                                                                                    | Status Affected: | Z                                                                                                                                                          |

| Description:     | Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. | Description:     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                             | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                 | Syntax:          | [ label ] INCFSZ f,d                                                                                                                                                                                                                                                                         |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                 | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                           |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                         | Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                                                                               | Status Affected: | None                                                                                                                                                                                                                                                                                         |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. If the result is 1, the next instruction, is executed. If the result is 0, then a NOP is executed instead making it a 2TCY instruction. | Description:     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. If the result is 1, the next instruction is executed. If the result is 0, a NOP is executed instead making it a 2TCY instruction. |

| RETFIE           | Return from Interrupt                      |

|------------------|--------------------------------------------|

| Syntax:          | [ label ] RETFIE                           |

| Operands:        | None                                       |

| Operation:       | $TOS \rightarrow PC$ , $1 \rightarrow GIE$ |

| Status Affected: | None                                       |

| RLF              | Rotate Left f through Carry                                                                                                                                                                       |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ label ] RLF f,d                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                |  |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                             |  |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are rotated one bit to the left through the Carry Flag. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |  |  |  |  |

|                  | C Register f                                                                                                                                                                                      |  |  |  |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETLW k                                                                                                                                                         |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                     |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                            |

| Status Affected: | None                                                                                                                                                                    |

| Description:     | The W register is loaded with the eight bit literal 'k'. The program counter is loaded from the top of the stack (the return address). This is a two cycle instruction. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                       |  |  |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [ label ] RRF f,d                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are rotated one bit to the right through the Carry Flag. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |  |  |  |  |  |  |  |  |

|                  | C → Register f                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                         |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] RETURN                                                                                                                               |

| Operands:        | None                                                                                                                                           |

| Operation:       | $TOS \to PC$                                                                                                                                   |

| Status Affected: | None                                                                                                                                           |

| Description:     | Return from subroutine. The stack is POPed and the top of the stack (TOS) is loaded into the program counter. This is a two cycle instruction. |

| SLEEP            |                                                                                                                                                                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                                            |

| Operands:        | None                                                                                                                                                                                                                                                     |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow \text{WDT,} \\ \text{0} \rightarrow \text{WDT prescaler,} \\ \text{1} \rightarrow \overline{\text{TO}}, \\ \text{0} \rightarrow \overline{\text{PD}} \end{array}$                                               |

| Status Affected: | TO, PD                                                                                                                                                                                                                                                   |

| Description:     | The power-down status bit, $\overline{PD}$ is cleared. Time-out status bit, $\overline{TO}$ is set. Watchdog Timer and its prescaler are cleared.  The processor is put into SLEEP mode with the oscillator stopped. See Section 10.13 for more details. |

### 13.0 ELECTRICAL CHARACTERISTICS

### Absolute Maximum Ratings (†)

| Ambient temperature under bias                                     | 55°C to +125°C       |

|--------------------------------------------------------------------|----------------------|

| Storage temperature                                                | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4) | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                                 | 0.3V to +7.5V        |

| Voltage on MCLR with respect to Vss (Note 2)                       | 0V to +13.25V        |

| Voltage on RA4 with respect to Vss                                 | 0V to +8.5V          |

| Total power dissipation (Note 1)                                   | 1.0W                 |

| Maximum current out of Vss pin                                     | 300 mA               |

| Maximum current into VDD pin                                       |                      |

| Input clamp current, IIK (VI < 0 or VI > VDD)                      | ±20 mA               |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                     | ±20 mA               |

| Maximum output current sunk by any I/O pin                         | 25 mA                |

| Maximum output current sourced by any I/O pin                      | 25 mA                |

| Maximum current sunk by PORTA and PORTB (combined)                 | 200 mA               |

| Maximum current sourced by PORTA and PORTB (combined)              | 200 mA               |

| Maximum current sunk by PORTC                                      | 200 mA               |

| Maximum current sourced by PORTC                                   | 200 mA               |

**Note 1:** Power dissipation is calculated as follows: Pdis = VDD x {IDD -  $\sum$  IOH} +  $\sum$  {(VDD-VOH) x IOH} +  $\sum$ (VOI x IOL)

2: Voltage spikes below Vss at the  $\overline{\text{MCLR}/\text{VPP}}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100 $\Omega$  should be used when applying a "low" level to the  $\overline{\text{MCLR}/\text{VPP}}$  pin, rather than pulling this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 13.4.3 TIMING DIAGRAMS AND SPECIFICATIONS

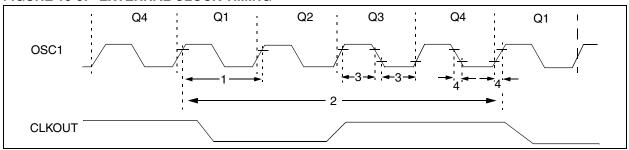

#### FIGURE 13-5: EXTERNAL CLOCK TIMING

TABLE 13-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                  | Min | Тур† | Max    | Units | Conditions          |

|--------------|-------|---------------------------------|-----|------|--------|-------|---------------------|

| 1A           | Fosc  | External CLKIN Frequency        |     | _    | 4      | MHz   | RC and XT osc modes |

|              |       | (Note 1)                        | DC  | _    | 4      | MHz   | HS osc mode (-04)   |

|              |       |                                 | DC  | _    | 20     | MHz   | HS osc mode (-20)   |

|              |       |                                 | DC  |      | 200    | kHz   | LP osc mode         |

|              |       | Oscillator Frequency            | DC  |      | 4      | MHz   | RC osc mode         |

|              |       | (Note 1)                        | 0.1 | _    | 4      | MHz   | XT osc mode         |

|              |       |                                 | 4   | _    | 20     | MHz   | HS osc mode         |

|              |       |                                 | 5   |      | 200    | kHz   | LP osc mode         |

| 1            | Tosc  | External CLKIN Period           | 250 | _    | _      | ns    | RC and XT osc modes |

|              |       | (Note 1)                        | 250 | _    | _      | ns    | HS osc mode (-04)   |

|              |       |                                 |     | _    | _      | ns    | HS osc mode (-20)   |

|              |       |                                 | 5   | _    |        | μS    | LP osc mode         |

|              |       | Oscillator Period (Note 1)      | 250 | _    | _      | ns    | RC osc mode         |

|              |       |                                 | 250 | _    | 10,000 | ns    | XT osc mode         |

|              |       |                                 | 250 | _    | 250    | ns    | HS osc mode (-04)   |

|              |       |                                 | 50  | _    | 250    | ns    | HS osc mode (-20)   |

|              |       |                                 | 5   |      |        | μS    | LP osc mode         |

| 2            | TCY   | Instruction Cycle Time (Note 1) | 200 |      | DC     | ns    | Tcy = 4/Fosc        |

| 3*           | TosL, | External Clock in (OSC1) High   | 100 | _    | _      | ns    | XT oscillator       |

|              | TosH  | or Low Time                     | 2.5 | _    |        | μS    | LP oscillator       |

|              |       |                                 | 15  |      |        | ns    | HS oscillator       |

| 4*           | TosR, | External Clock in (OSC1) Rise   | _   | _    | 25     | ns    | XT oscillator       |

|              | TosF  | or Fall Time                    | _   | _    | 50     | ns    | LP oscillator       |

|              |       |                                 | _   | _    | 15     | ns    | HS oscillator       |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin.

When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

T0CKI T1OSO/T1CKI 48 TMR0 or TMR1 Note: Refer to Figure 13-4 for load conditions.

FIGURE 13-9: TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS

**TABLE 13-5:** TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       |                     | Characteristic                                                                      |                | Min                                       | Typ† | Max | Units | Conditions                         |

|--------------|-----------|---------------------|-------------------------------------------------------------------------------------|----------------|-------------------------------------------|------|-----|-------|------------------------------------|

| 40*          | Tt0H      |                     |                                                                                     | No Prescaler   | 0.5Tcy + 20                               | _    | _   | ns    | Must also meet                     |

|              |           |                     |                                                                                     | With Prescaler | 10                                        | _    | _   | ns    | parameter 42                       |

| 41*          | TtOL      | T0CKI Low Pulse W   | idth                                                                                | No Prescaler   | 0.5Tcy + 20                               | _    | _   | ns    | Must also meet parameter 42        |

|              |           |                     |                                                                                     | With Prescaler | 10                                        | _    | _   | ns    |                                    |

| 42*          | Tt0P      | T0CKI Period        |                                                                                     | No Prescaler   | Tcy + 40                                  | _    | _   | ns    |                                    |

|              |           |                     |                                                                                     | With Prescaler | Greater of:<br>20 or <u>TCY + 40</u><br>N | _    | _   | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H      | T1CKI High Time     | Synchronous, Pr                                                                     | rescaler = 1   | 0.5Tcy + 20                               | _    | _   | ns    | Must also meet                     |

|              |           |                     | Synchronous,                                                                        | PIC16CXX       | 15                                        | _    | _   | ns    | parameter 47                       |

|              |           |                     | Prescaler = 2,4,8                                                                   | PIC16LCXX      | 25                                        | _    | _   | ns    |                                    |

|              |           |                     | Asynchronous                                                                        | PIC16CXX       | 30                                        | _    | _   | ns    |                                    |

|              |           |                     |                                                                                     | PIC16LCXX      | 50                                        | _    | _   | ns    |                                    |

| 46*          | Tt1L      | T1CKI Low Time      | Synchronous, Pr                                                                     | rescaler = 1   | 0.5Tcy + 20                               | _    | _   | ns    | Must also meet                     |

|              |           |                     | Synchronous,<br>Prescaler =<br>2,4,8                                                | PIC16CXX       | 15                                        | _    | _   | ns    | parameter 47                       |

|              |           |                     |                                                                                     | PIC16LCXX      | 25                                        | _    | _   | ns    |                                    |

|              |           |                     | Asynchronous                                                                        | PIC16CXX       | 30                                        | _    | _   | ns    |                                    |

|              |           |                     |                                                                                     | PIC16LCXX      | 50                                        | _    | _   | ns    |                                    |

| 47*          | Tt1P      | T1CKI input period  | Synchronous                                                                         | PIC16CXX       | GREATER OF:<br>30 OR <u>TCY + 40</u><br>N |      | _   | ns    | N = prescale value (1, 2, 4, 8)    |

|              |           |                     |                                                                                     | PIC16LCXX      | GREATER OF:<br>50 OR TCY + 40<br>N        |      |     |       | N = prescale value (1, 2, 4, 8)    |

|              | Asynchro  |                     | Asynchronous                                                                        | PIC16CXX       | 60                                        | _    | _   | ns    |                                    |

|              |           |                     |                                                                                     | PIC16LCXX      | 100                                       | _    | _   | ns    |                                    |

|              | Ft1       |                     | Timer1 oscillator input frequency range (oscillator enabled by setting bit T1OSCEN) |                | DC                                        | _    | 200 | kHz   |                                    |

| 48           | TCKEZtmr1 | Delay from external | 2Tosc                                                                               | _              | 7Tosc                                     | _    |     |       |                                    |

<sup>\*</sup> These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

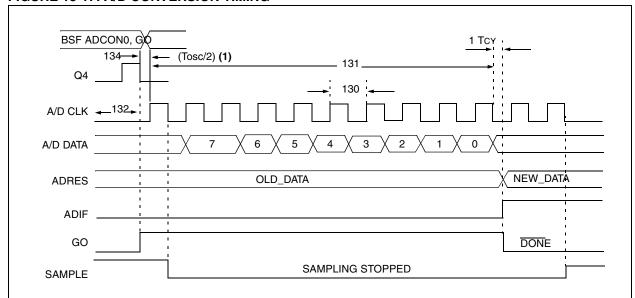

#### FIGURE 13-17: A/D CONVERSION TIMING

**Note 1:** If the A/D clock source is selected as RC, a time of TcY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.

**TABLE 13-14: A/D CONVERSION REQUIREMENTS**

| Param<br>No. | Sym  | Characteristic                      |                                               | Min    | Тур†   | Max | Unit<br>s | Conditions                                                                                                                                                                                                  |

|--------------|------|-------------------------------------|-----------------------------------------------|--------|--------|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period                    | PIC16CXX                                      | 1.6    | _      | _   | μS        | Tosc based, VREF ≥ 3.0V                                                                                                                                                                                     |

|              |      |                                     | PIC16LCXX                                     | 2.0    |        |     | μS        | Tosc based, VREF full range                                                                                                                                                                                 |

|              |      |                                     | PIC16CXX                                      | 2.0    | 4.0    | 6.0 | μS        | A/D RC Mode                                                                                                                                                                                                 |

|              |      |                                     | PIC16LCXX                                     | 3.0    | 6.0    | 9.0 | μS        | A/D RC Mode                                                                                                                                                                                                 |

| 131          | TCNV | Conversion time (not time) (Note 1) | including S/H                                 | 11     | _      | 11  | TAD       |                                                                                                                                                                                                             |

| 132          | TACQ | Acquisition time                    |                                               | Note 2 | 20     | _   | μS        |                                                                                                                                                                                                             |

|              |      |                                     |                                               | 5*     | 1      |     | μѕ        | The minimum time is the amplifier settling time. This may be used if the "new" input voltage has not changed by more than 1 LSb (i.e., 20.0 mV @ 5.12V) from the last sampled voltage (as stated on CHOLD). |

| 134          | TGO  | Q4 to A/D clock start               |                                               | _      | Tosc/2 | _   | _         | If the A/D clock source is selected as RC, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                            |

| 135          | Tswc | Switching from conve<br>time        | $\operatorname{ert} 	o \operatorname{sample}$ | 1.5    |        | 1   | TAD       |                                                                                                                                                                                                             |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: ADRES register may be read on the following TcY cycle.

2: See Section 9.1 for min conditions.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

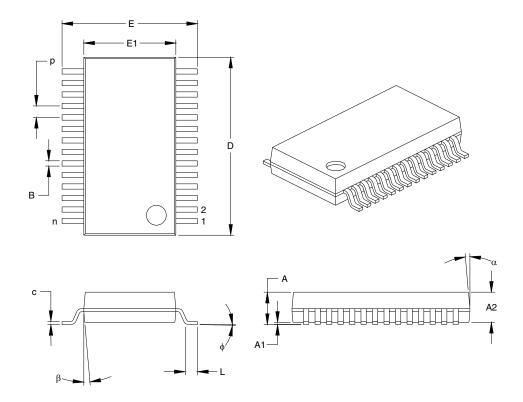

#### 28-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP) 15.5

|                          | Units  |      | INCHES |      | MILLIMETERS* |        |        |  |

|--------------------------|--------|------|--------|------|--------------|--------|--------|--|

| Dimension                | Limits | MIN  | NOM    | MAX  | MIN          | NOM    | MAX    |  |

| Number of Pins           | n      |      | 28     |      |              | 28     |        |  |

| Pitch                    | р      |      | .026   |      |              | 0.66   |        |  |

| Overall Height           | Α      | .068 | .073   | .078 | 1.73         | 1.85   | 1.98   |  |

| Molded Package Thickness | A2     | .064 | .068   | .072 | 1.63         | 1.73   | 1.83   |  |

| Standoff                 | A1     | .002 | .006   | .010 | 0.05         | 0.15   | 0.25   |  |

| Overall Width            | E      | .299 | .309   | .319 | 7.59         | 7.85   | 8.10   |  |

| Molded Package Width     | E1     | .201 | .207   | .212 | 5.11         | 5.25   | 5.38   |  |

| Overall Length           | D      | .396 | .402   | .407 | 10.06        | 10.20  | 10.34  |  |

| Foot Length              | L      | .022 | .030   | .037 | 0.56         | 0.75   | 0.94   |  |

| Lead Thickness           | С      | .004 | .007   | .010 | 0.10         | 0.18   | 0.25   |  |

| Foot Angle               | ф      | 0    | 4      | 8    | 0.00         | 101.60 | 203.20 |  |

| Lead Width               | В      | .010 | .013   | .015 | 0.25         | 0.32   | 0.38   |  |

| Mold Draft Angle Top     | α      | 0    | 5      | 10   | 0            | 5      | 10     |  |

| Mold Draft Angle Bottom  | β      | 0    | 5      | 10   | 0            | 5      | 10     |  |

| *O                       |        |      |        |      |              |        |        |  |

<sup>\*</sup>Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MS-150

Drawing No. C04-073